### Load Balancing of Pseudo-random Workloads on Heterogeneous Systems

### **Anders Wenhaug**

Master of Science in Computer Science

Submission date: August 2017

Supervisor: Anne Cathrine Elster, IDI Co-supervisor: Jan Christian Meyer, IDI

Norwegian University of Science and Technology Department of Computer Science

## **Problem description**

Pseudo-random workloads and branch divergence present load balancing challenges to heterogeneous systems using GPUs as accelerators. A method to partition an irregular workload between host system processors and accelerators should be developed, and compared to conventional load balancing methods from the literature.

### **Abstract**

Heterogeneous computing systems using one or more graphics processing units (GPUs) as accelerators present unique load balancing challenges due to the architecture of the GPUs. Assigning a part of the workload proportional to the throughput of the GPU is unlikely to achieve the peak theoretical performance of the GPU, partly because of branch divergence. Additionally, for workloads depending on pseudorandom numbers, the branch divergence may appear unpredictable, making it hard to work around.

In this thesis we present an approach for reorganizing pseudo-random work-loads before execution on the GPU, with the goal of reducing the branch divergence. In our experiments, the method achieves a speedup in kernel execution time of up to 1.45 on a real application. We also show that the method may be faster even if the overhead of it is accounted for. Additionally, a method for estimating the resulting reduction in execution time is developed, which can be used for determining whether or not to apply the reorganization.

A graph based method for task balancing is also presented, which is able to select the optimal task sequence in over 96% of the tested cases. This task graph doubles as a model for the throughput of the GPU, and the estimates are used by a load balancer to partition the workload between the central processing unit (CPU) and GPU.

### Sammendrag

Heterogene systemer som bruker grafikkprosessorer (GPUer) som akseleratorer medfører unike problemer med tanke på lastbalansering på grunn av arkitekturen til GPUer. Å tildele en mengde arbeid som er proposjonal med ytelsen til en GPU fører sjelden til at man oppnår optimal ytelse på GPUen, noe som delvis skyldes ytelsestap på grunn av tråddivergens. Arbeidslaster som er avhengige av pseudo-tilfeldige tall er spesielt vanskelige, fordi tråddivergensen kan være tilsynelatende tilfeldig, noe som gjør det vanskelig å redusere tråddivergensen.

I denne oppgaven presenterer vi en metode for å omorganisere pseudo-tilfeldige arbeidslaster før de kjører på GPUen, med mål om å redusere tråddivergens. Våre eksperimenter viser at metoden medfører en ytelsesøkning på opptil 1.45 for en ekte applikasjon. Vi viser også at metoden kan være raskere selv om tiden som brukes til å omorganisere lasten er tatt med. I tillegg til dette utvikler vi en metode for å estimere reduksjonen i kjøretid, som kan brukes for å bestemme om omorganiseringen skal gjøres eller ikke.

En graf-basert metode for balansering av oppgaver blir også presentert. Denne metoden velger den optimale rekkefølgen av oppgaver i 96% av tilfellene som ble testet. Denne oppgavegrafen fungerer også som en modell for ytelsen til GPUen, og estimatene blir brukt av en lastbalanserer for å dele arbeidslasten mellom prosessoren (CPUen) og GPUen.

### Acknowledgements

I would like to thank my supervisor **Anne Cathrine Elster** and my co-supervisor **Jan Christian Meyer** for their support and guidance throughout this thesis. Our discussions have been very interesting.

To my parents, **Kristin** and **Geir**, I am eternally grateful for your emotional and unconditional support.

I would also like to thank my girlfriend and family, **Silje**, **Marius**, **Vilde**, **Øystein**, **Marie**, **Ola**, **Kjersti** and **Milo**. I am very lucky to have you as my girlfriend, family and step dog.

A special thanks to my grandparents, **Oddrun**, **Steinar**, **Eli** and **Sverre**. I am very lucky to have you as my grandparents.

Last, but not in the slightest least, I would like to express my sincere appreciation to my friend **Bjarne Grimstad**. Your friendship, guidance and knowledge have had an immensely positive impact on my life. I am truly grateful.

## **Table of Contents**

| Pı | roblem description                   | 1  |

|----|--------------------------------------|----|

| Ał | ostract                              | 3  |

| Sa | ammendrag                            | 5  |

| Ac | cknowledgements                      | 7  |

| Ta | able of Contents                     | 9  |

| Li | st of Tables                         | 15 |

| Li | st of Figures                        | 19 |

| Li | st of Source Code                    | 21 |

| Li | st of Abbreviations and Nomenclature | 23 |

| 1  | Introduction                         | 27 |

|    | 1.1 Motivation                       | 28 |

|    | 1.2 Thesis scope                     | 30 |

|   |     | 1.2.1   | Assumptions                                   | 30 |

|---|-----|---------|-----------------------------------------------|----|

|   |     | 1.2.2   | Research question                             | 31 |

|   | 1.3 | Struct  | rure of the thesis                            | 31 |

| 2 | Bac | kgrour  | nd                                            | 33 |

|   | 2.1 | Pseud   | o-random number generators                    | 34 |

|   | 2.2 | CUDA    | <b>\</b>                                      | 35 |

|   |     | 2.2.1   | GPU topology                                  | 35 |

|   |     | 2.2.2   | Grid, thread block and warp                   | 36 |

|   |     | 2.2.3   | Memory hierarchy                              | 37 |

|   | 2.3 | Branc   | h divergence on GPUs                          | 38 |

|   | 2.4 | Irregu  | lar workloads                                 | 40 |

|   | 2.5 | Boots   | trap                                          | 41 |

|   |     | 2.5.1   | The stationary bootstrap                      | 42 |

|   | 2.6 | Spline  | es                                            | 45 |

|   |     | 2.6.1   | The penalized spline (P-spline)               | 46 |

|   | 2.7 | Relate  | ed work                                       | 49 |

|   |     | 2.7.1   | Static load balancing approaches              | 49 |

|   |     | 2.7.2   | Dynamic load balancing approaches             | 51 |

| 3 | Met | hodolo  | ogy                                           | 53 |

|   | 3.1 | Perfor  | mance modelling                               | 55 |

|   | 3.2 | Partiti | oning of workload in the GPU                  | 56 |

|   |     | 3.2.1   | Irregular workload in stationary bootstrap    | 57 |

|   |     | 3.2.2   | Reorganization of workload                    | 59 |

|   |     | 3.2.3   | Generation of seed to iteration count mapping | 60 |

|   | 3.3 | Task g  | graph                                         | 61 |

| TΑ | ABLE | OF CO          | ONTENTS                                                               | 11       |

|----|------|----------------|-----------------------------------------------------------------------|----------|

|    | 3.4  | 3.3.1<br>CPU a | Optimal execution path                                                | 62<br>64 |

| 4  | Imp  | lemen          | atation                                                               | 69       |

|    | 4.1  | Tools          | and hardware                                                          | 70       |

|    | 4.2  | Measi          | uring execution time                                                  | 71       |

|    | 4.3  | The b          | ootstrap program                                                      | 72       |

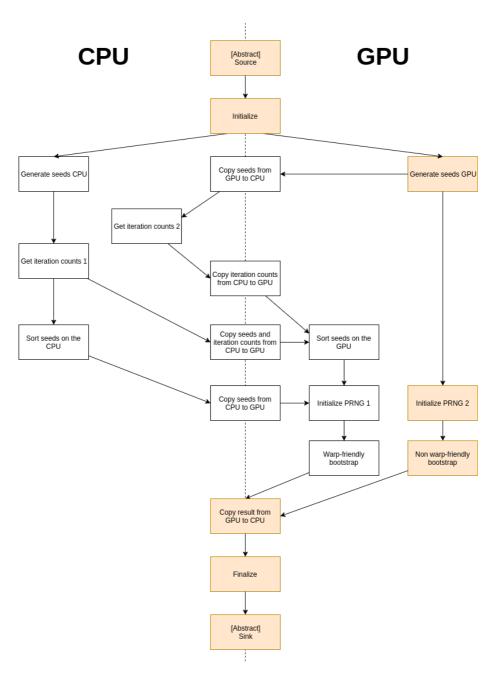

|    |      | 4.3.1          | Program flow                                                          | 73       |

|    |      | 4.3.2          | Command line arguments                                                | 73       |

|    |      | 4.3.3          | Recorded statistics                                                   | 74       |

|    |      | 4.3.4          | Histogram of iteration counts                                         | 75       |

|    | 4.4  | Statio         | nary bootstrap implementations                                        | 75       |

|    |      | 4.4.1          | General optimizations                                                 | 75       |

|    |      | 4.4.2          | GPU kernels                                                           | 77       |

|    |      | 4.4.3          | CPU implementation                                                    | 80       |

|    |      | 4.4.4          | Sources of branch divergence in the GPU kernels $\ldots\ldots$        | 81       |

|    | 4.5  | CPU ł          | pootstrap module                                                      | 82       |

|    | 4.6  | GPU l          | bootstrap module                                                      | 82       |

|    |      | 4.6.1          | Warp-friendly and non warp-friendly bootstrap                         | 82       |

|    |      | 4.6.2          | Implemented operations of the task graph $\ \ldots \ \ldots \ \ldots$ | 83       |

| 5  | Test | cases          |                                                                       | 89       |

|    | 5.1  | Reorg          | anization of the workload                                             | 91       |

|    |      | 5.1.1          | Warp execution efficiency                                             | 91       |

|    |      | 5.1.2          | Execution time                                                        | 91       |

|    |      | 5.1.3          | Seeds to iterations file load time                                    | 93       |

|    | 5.2  | Task g         | graph                                                                 | 94       |

|   |      | 5.2.1   | Execution path selection                                                                                                                        |

|---|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 5.2.2   | Determining optimal execution path time 94                                                                                                      |

|   | 5.3  | Load    | balancer                                                                                                                                        |

|   |      | 5.3.1   | Optimization time                                                                                                                               |

|   |      | 5.3.2   | Estimated execution time                                                                                                                        |

|   |      | 5.3.3   | $Actual\ execution\ time\ \dots\dots\dots\dots 96$                                                                                              |

|   |      | 5.3.4   | Actual and estimated ratios $\dots \dots \dots$ |

|   |      | 5.3.5   | Balanced and unbalanced execution time 97                                                                                                       |

| 6 | Resi | ults    | 99                                                                                                                                              |

| • | 6.1  |         | anization of the workload                                                                                                                       |

|   | 0.1  |         |                                                                                                                                                 |

|   |      | 6.1.1   | Warp execution efficiency                                                                                                                       |

|   |      | 6.1.2   | Execution time                                                                                                                                  |

|   |      | 6.1.3   | Seeds to iterations file load time                                                                                                              |

|   | 6.2  | Task g  | graph                                                                                                                                           |

|   |      | 6.2.1   | Execution path selection                                                                                                                        |

|   |      | 6.2.2   | Determining optimal execution path time                                                                                                         |

|   | 6.3  | Load    | balancer                                                                                                                                        |

|   |      | 6.3.1   | Optimization time                                                                                                                               |

|   |      | 6.3.2   | Estimated execution time                                                                                                                        |

|   |      | 6.3.3   | Actual execution time                                                                                                                           |

|   |      | 6.3.4   | Actual and estimated ratios                                                                                                                     |

|   |      | 6.3.5   | Balanced and unbalanced execution time                                                                                                          |

| 7 | Disc | cussion | 119                                                                                                                                             |

|   | 7.1  |         | ty of the method                                                                                                                                |

|   |      |         |                                                                                                                                                 |

|   | 1.2  | Comp    | parison to other approaches                                                                                                                     |

| TABLE OF CONTENTS | 13 |

|-------------------|----|

|                   |    |

|   |     | 7.2.1 Reorganization of workload                                                                                                                                  | 21 |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 7.2.2 Task graph                                                                                                                                                  | 22 |

|   |     | 7.2.3 Load balancer                                                                                                                                               | 23 |

|   | 7.3 | Reorganization of workload                                                                                                                                        | 24 |

|   |     | 7.3.1 Warp execution efficiency                                                                                                                                   | 24 |

|   |     | 7.3.2 Execution time                                                                                                                                              | 25 |

|   |     | 7.3.3 Overhead of the warp-friendly bootstrap $\dots \dots \dots$ | 25 |

|   |     | 7.3.4 Feasibility of reorganizing the workload                                                                                                                    | 29 |

|   | 7.4 | Task graph                                                                                                                                                        | 30 |

|   |     | 7.4.1 Execution path selection                                                                                                                                    | 30 |

|   |     | 7.4.2 Time usage                                                                                                                                                  | 31 |

|   | 7.5 | Load balancer                                                                                                                                                     | 31 |

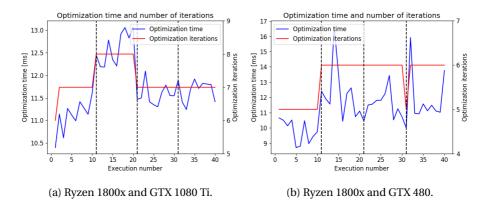

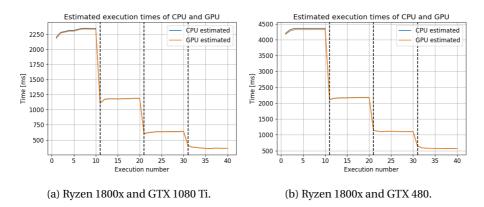

|   |     | 7.5.1 Optimization time and load balancing result                                                                                                                 | 31 |

|   |     | 7.5.2 Actual execution time                                                                                                                                       | 33 |

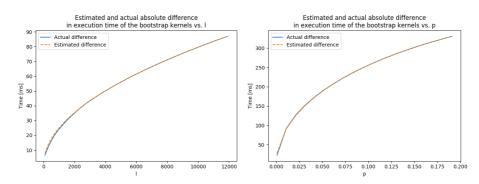

|   | 7.6 | Estimating the reduction in execution time                                                                                                                        | 34 |

| 8 | Con | clusion 1:                                                                                                                                                        | 39 |

| 9 | Fut | ure work 14                                                                                                                                                       | 41 |

|   | 9.1 | Static seeds                                                                                                                                                      | 41 |

|   | 9.2 | Persistent seeds to iterations mapping on GPU $\ \ldots \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                       | 42 |

|   | 9.3 | Force uniform workload per warp $\ \ldots \ 1$                                                                                                                    | 42 |

|   | 9.4 | Other applications                                                                                                                                                | 43 |

|   | 9.5 | Compression of seeds to iteration counts file                                                                                                                     | 43 |

|   | 9.6 | Scheduling large workloads on the CPU                                                                                                                             | 43 |

|   | 9.7 | Load balancer improvement                                                                                                                                         | 44 |

| 14 | TABLE OF CONTENTS |

|----|-------------------|

| Bi | bliography                    | 144 |

|----|-------------------------------|-----|

| Аŗ | ppendices                     | 151 |

| A  | Figures                       | 153 |

| В  | Source code listings          | 159 |

| C  | Running the bootstrap program | 167 |

|    | C.1 Compilation               | 167 |

|    | C.2 Running                   | 168 |

## **List of Tables**

| 4.1 | Hardware configuration #1                                       |

|-----|-----------------------------------------------------------------|

| 4.2 | Hardware configuration #2                                       |

| 4.3 | Hardware configuration #3                                       |

| 4.4 | Some of the command line arguments of the bootstrap program 74  |

| 4.5 | Table of all operations                                         |

|     |                                                                 |

| 6.1 | Load seeds to iterations file timings with 32 GiB of memory 112 |

| 6.2 | Load seeds to iterations file timings with 16 GiB of memory 112 |

| 6.3 | Optimal and selected paths statistics 1/2                       |

| 6.4 | Optimal and selected paths statistics 2/2                       |

| 6.5 | Determine optimal execution path timings                        |

| 6.6 | Balanced and unbalanced execution time 1/2                      |

| 6.7 | Balanced and unbalanced execution time 2/2                      |

16 LIST OF TABLES

## **List of Figures**

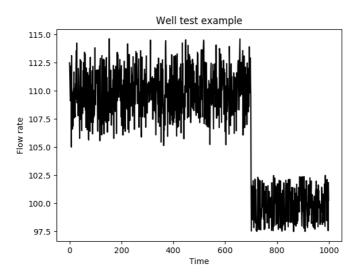

| 1.1 | Example of flow rate before and after closing a well                                  | 29  |

|-----|---------------------------------------------------------------------------------------|-----|

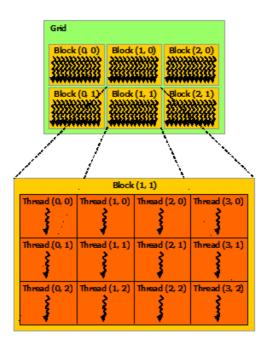

| 2.1 | CUDA grid, thread block and threads [NVI17c]                                          | 36  |

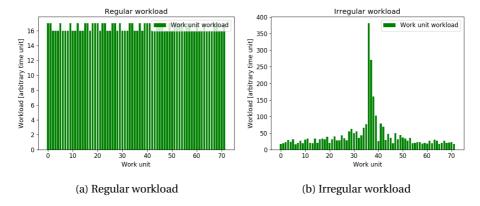

| 2.2 | Comparison of regular and irregular workloads                                         | 41  |

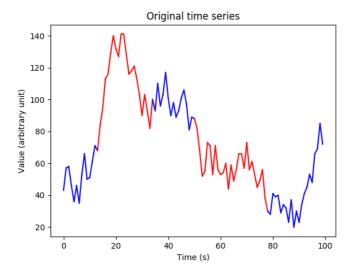

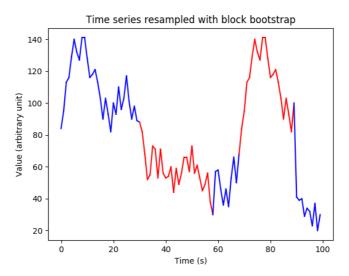

| 2.3 | Original time series.                                                                 | 43  |

| 2.4 | One of the possible resampled time series                                             | 44  |

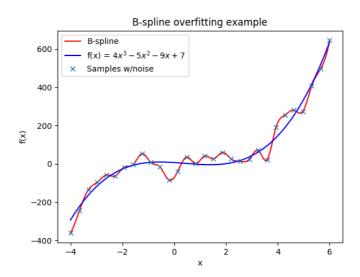

| 2.5 | Example of a B-spline overfitting a data set                                          | 47  |

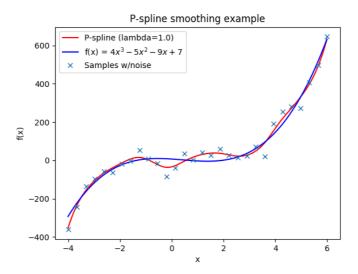

| 2.6 | Fitting the same data set with a penalized spline.                                    | 48  |

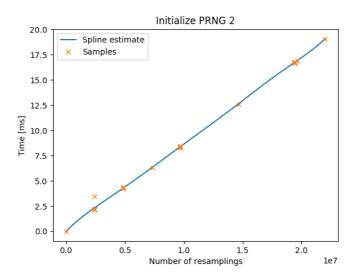

| 3.1 | The estimator for the operation $\it Initialize PRNG 2$ after 40 executions           | 56  |

| 3.2 | Workload distribution for $l \in [12000, 20000]$ and $p \in \{0.001, 0.005, 0.01\}$ . | 57  |

| 3.3 | Workload distribution as a function of the time series length and p. $$ . $$ .        | 58  |

| 3.4 | Thread activity before and after reorganization of workload                           | 60  |

| 3.5 | Constructed example of load balancer objective function                               | 66  |

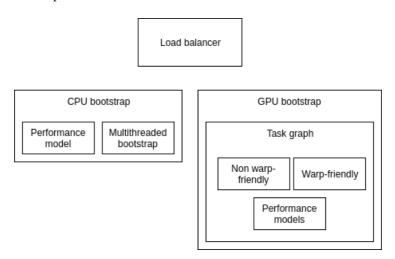

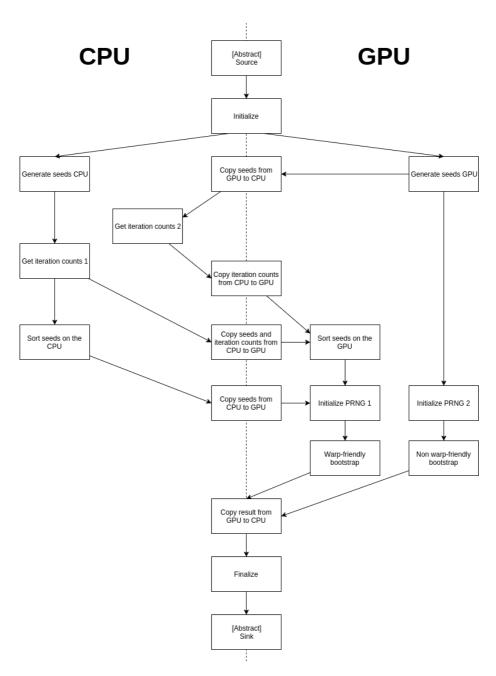

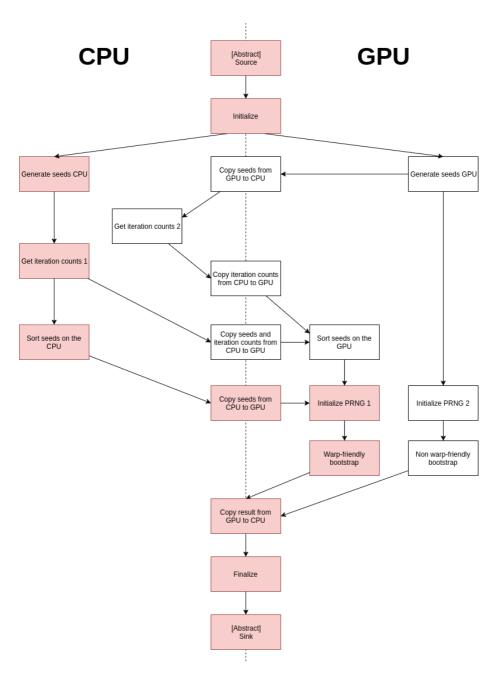

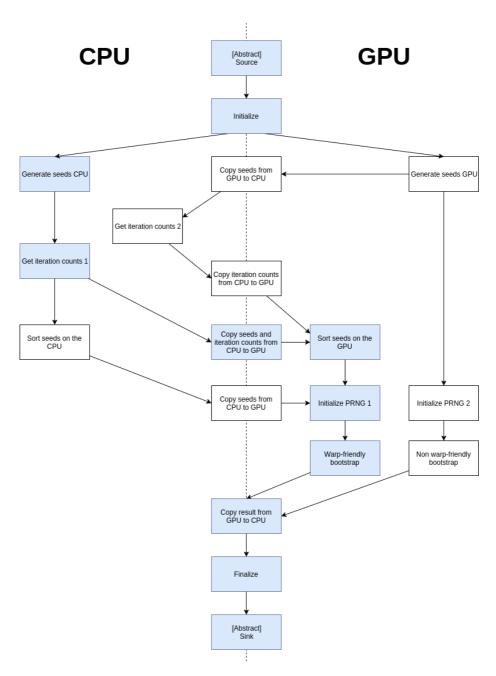

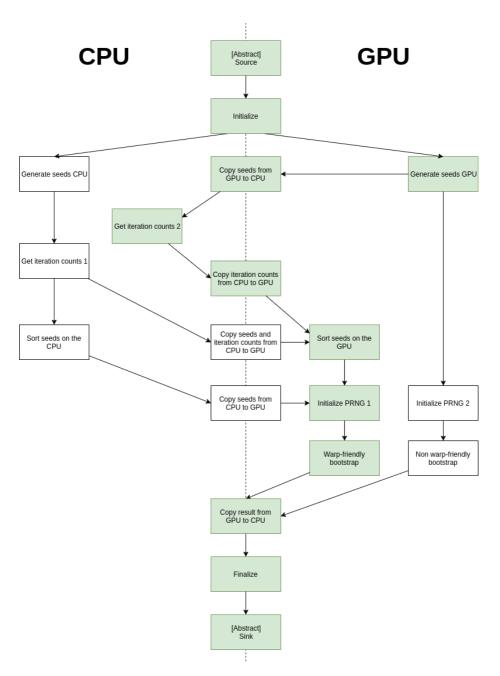

| 4.1 | High level structure of the bootstrap program                                         | 72  |

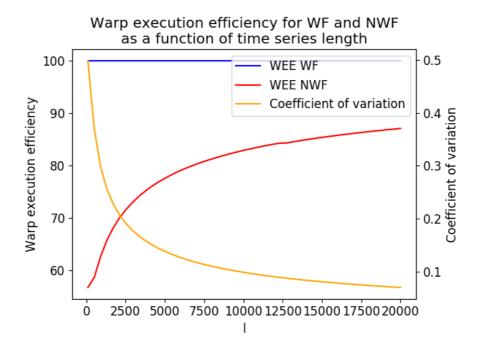

| 6.1 | Warp execution efficiency and coefficient of variation as a function of $\it l.$      | 100 |

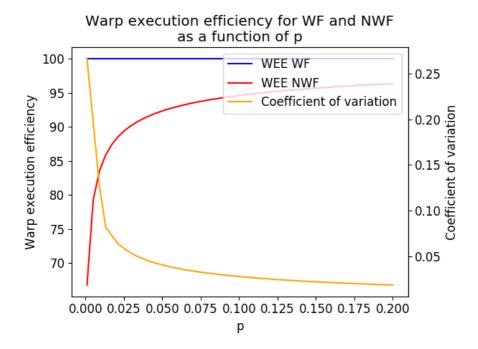

| 6.2 | Warp execution efficiency and coefficient of variation as a function of $p$ .         | 101 |

18 LIST OF FIGURES

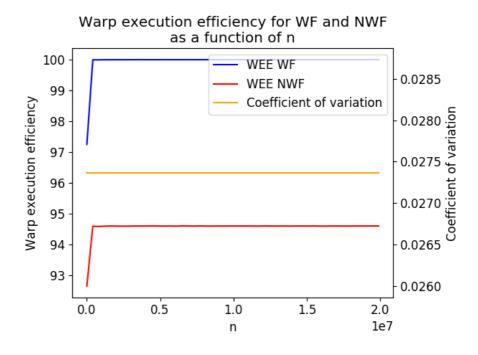

| 6.3  | Warp execution efficiency and coefficient of variation as a function of $n.102$ |

|------|---------------------------------------------------------------------------------|

| 6.4  | Kernel execution times with and without reorganization, vs $l$ 103              |

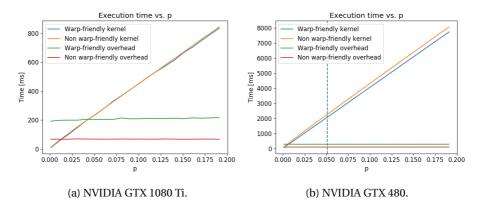

| 6.5  | Kernel execution times with and without reorganization, vs $p$ 104              |

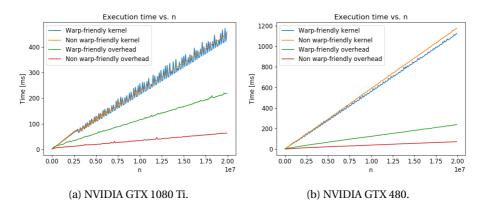

| 6.6  | Kernel execution times with and without reorganization, vs $n$ 105              |

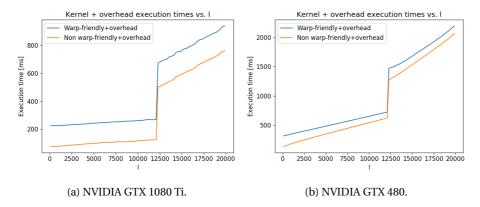

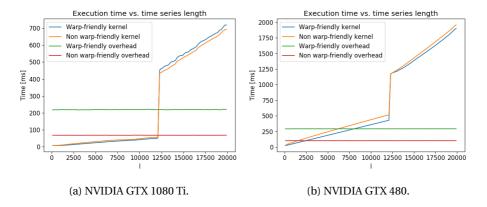

| 6.7  | Kernel execution times and overheads as $l$ is increased 105                    |

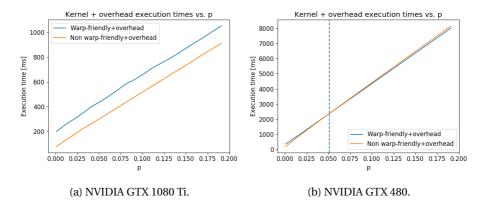

| 6.8  | Kernel execution times and overheads as $p$ is increased 106                    |

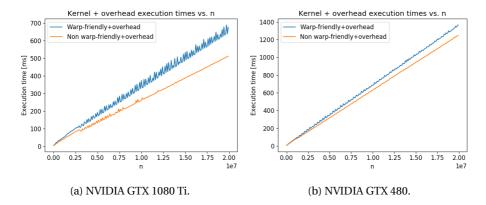

| 6.9  | Kernel execution times and overheads as $n$ is increased 106                    |

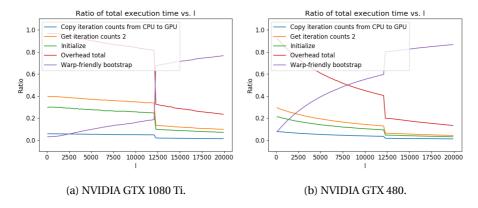

| 6.10 | Most time consuming operations vs. $l.$                                         |

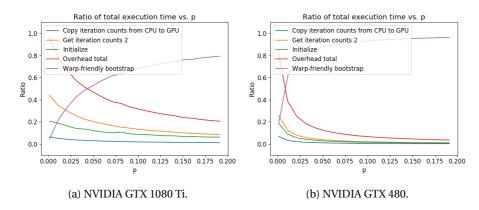

| 6.11 | Most time consuming operations vs. $p$                                          |

| 6.12 | Most time consuming operations vs. $n$                                          |

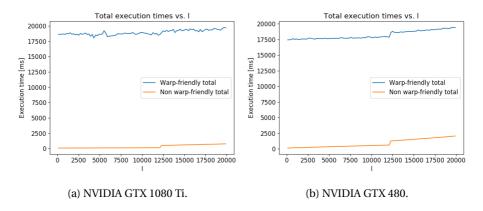

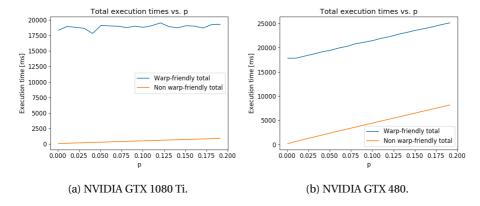

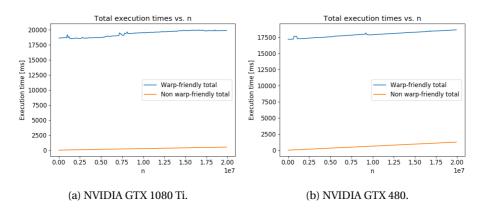

| 6.13 | Total execution time vs $l.$                                                    |

| 6.14 | Total execution time vs $p$                                                     |

| 6.15 | Total execution time vs $n$                                                     |

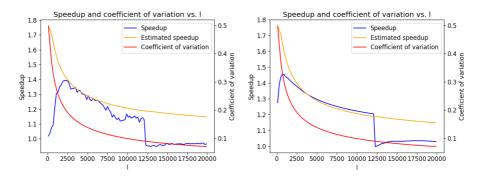

| 6.16 | Speedup of reorganization vs. $l.$                                              |

| 6.17 | Speedup of reorganization vs. $p$                                               |

| 6.18 | Speedup of reorganization vs. $n$                                               |

| 6.19 | Load balancer time and number of iterations for each run                        |

| 6.20 | Load balancer estimated execution time                                          |

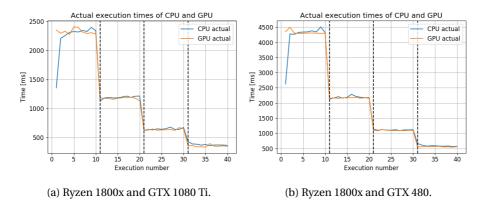

| 6.21 | Load balancer actual execution time                                             |

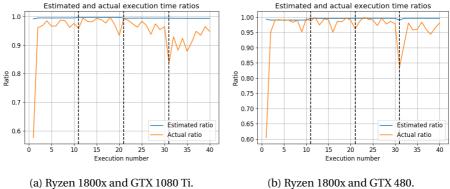

| 6.22 | Load balancer estimated and actual ratios                                       |

| 6.23 | The CPU bootstrap estimator before and after the first run                      |

| Δ1   | Complete task graph of the bootstrap program                                    |

|      | Execution path 1/4                                                              |

|      | -                                                                               |

|      | Execution path 2/4                                                              |

| A.4  | Execution path 3/4                                                              |

| LIST OF FIGURES        | 19    |

|------------------------|-------|

| A.5 Execution path 4/4 | . 158 |

20 LIST OF FIGURES

## **List of Source Code**

| 2.1 | Branch divergence example 1                    |

|-----|------------------------------------------------|

| 2.2 | Branch divergence example 2                    |

| 3.1 | Load balancer optimization                     |

| B.1 | Bootstrap kernel using shared memory           |

| B.2 | Bootstrap kernel for long time series          |

| В.3 | Kernel for getting iteration counts            |

| B.4 | Generate seeds on the GPU                      |

| B.5 | C++ implementation of the stationary bootstrap |

# List of Abbreviations and Nomenclature

#### **Abbreviations**

CPU = Central processing unit

GPU = Graphics processing unit

FLOPS = Floating point operations per second

KiB = Kibibyte (1024B)

MiB = Mibibyte (1024KiB)

GiB = Gibibyte (1024MiB)

PRNG = Pseudo-random number generator

WF = Warp-friendly

NWF = Non warp-friendly

DAG = Directed acyclic graph

WEE = Warp execution efficiency

PCI = Peripheral Component Interconnect

#### **Nomenclature**

l = Time series length

p = p-parameter of the geometric distribution

n = Number of resamplings

Warp-friendly = When stationary bootstrap is run using reorganized workload

Non warp-friendly = When stationary bootstrap is run without reorganization

### Chapter 1

### Introduction

Heterogeneous systems composed of multi-core central processing units (CPU) and accelerators such as graphics processing units (GPU) are becoming increasingly popular for data-parallel applications. GPUs were originally produced for accelerating demanding graphical tasks, but is now being used for general purpose computing because of the high performance it offers relative to the CPU. Programming toolkits such as CUDA<sup>1</sup> [NVI17c] have been developed to make it easier to develop and run programs on GPUs. However, achieving the best performance on a heterogeneous system requires the workload to be partitioned such that the devices get a workload relative to their performance. This remains a main challenge.

In this thesis, we will look at how data-parallel applications can be partitioned across the CPU and GPU. A system for determining the optimal partitioning of a specific application with irregular workloads (workloads where the amount of work per work unit varies) will be implemented. Additionally, a novel method for balancing

$<sup>^{1}</sup>$ CUDA used to be an abbreviation for *Compute Unified Device Architecture*, but was later renamed to just CUDA.

the workload internally in the GPU is also presented, implemented and studied.

Load balancing is the process of determining the portions of the total workload to run on each device. Typically, it is desired to minimize the total execution time of the program. To achieve this, each device must be assigned a workload such that the execution time of all devices are equal, and finish computing at the same time. Failing to find a good partition means that the devices that finish first must wait for the slowest to finish, effectively wasting the computational resources of the devices that must wait.

#### 1.1 Motivation

In subsea oil production, there are typically a number of wells where oil and gas is extracted from. These wells are often connected to a single large pipe that the oil and gas are transported through to the oil platform or production ship at the *top-side*. The result of this is that only the cumulative production of all wells is known by measuring the rate of flow at the top-side, and the production of each individual well is unknown. For optimizing the valve settings with the objective of maximizing the oil and gas rates, it is very useful to know the production of each well.

One of the commonly used methods for determining the production of a single well is to fully close the valves on the well. Then, the delta in cumulative production is measured at the top-side. Because of noise and oscillations in the flow, the well must remain closed for a period of time until the true production of the well can be known with a certain confidence. Each second the well is closed leads to lower total production and therefore less income for the oil production company. It is therefore important to be able to determine the production of the well as fast as possible, so that the valve choke can be reopened and the full production potential regained.

1.1. MOTIVATION 29

Figure 1.1: Example of flow rate before and after closing a well.

Figure 1.1 shows a fictional example of a drop in the total flow rate when one well is closed at t=700.

A method called stationary bootstrap can be applied to give an estimate of the mean production of the well. The time series of the rate of flow is resampled many times and the arithmetic mean of each resampling can be used to build a histogram of means, which in turn can be used to compute a confidence interval for the true mean of the time series. It is imperative for the method to be fast, so that the well can be reopened as soon as possible. In this project we will look at methods for achieving this.

#### 1.2 Thesis scope

The scope of this thesis is to develop a method for partitioning irregular pseudorandom workloads on heterogeneous systems using GPUs as accelerators. Workload partitioning is traditionally interpreted as determining a partition of the workload that minimizes execution time when run on a heterogeneous system. In this thesis, we will include the partitioning of the workload internally in the GPU, that is, between the cores of the GPU, as part of the study.

The scope is thus divided into two main parts: Developing a method for partitioning the total workload between the CPU and GPU, and developing a method for partitioning the workload internally in the GPU. The methods will be compared to traditional methods found in the literature.

We focus our attention to applications that execute a single data-parallel kernel with *pseudo-random irregular workloads*. Pseudo-random irregular workloads are applications where the workload of each data point is partially determined by the output of a pseudo-random number generator (PRNG).

#### 1.2.1 Assumptions

- A single GPU will be used for all test cases. Both the approach taken for partitioning the workload between the CPU and GPU, and the approach for the workload partitioning internally in the GPU should be valid for multi-GPU setups as well. Multi-GPU setups is therefore considered to be out of scope for this thesis.

- The majority of the workload per data point occurs in a loop, and the number of iterations of the loop must be partially determined by the output of a PRNG.

31

#### 1.2.2 Research question

Determine the feasibility of reorganizing the workload to increase the performance of GPUs on irregular pseudo-random workloads, and if so, for which cases one can expect decreased execution time.

#### 1.3 Structure of the thesis

The thesis is organized into nine chapters. The first chapter gives a brief introduction to heterogeneous systems and load balancing, motivates the work done in this thesis, and defines the scope of the thesis. Chapter 2 aims to provide the reader with the theoretical background that is necessary to follow the rest of the thesis, along with a review of existing load balancing approaches that are found in the literature. In Chapter 3, we describe the methods we have developed for workload partitioning. Chapter 4 gives a detailed description of the implementation of our methods, followed by Chapter 5 where the experiments and metrics we use are described. In Chapter 6, the results of the experiments are presented, and then discussed in Chapter 7. Finally, we present our conclusions in Chapter 8, and provide recommendations for further research in Chapter 9.

### Chapter 2

### **Background**

The purpose of this chapter is to provide an overview of the key concepts and technologies that is used in this thesis. To fully understand the rest of the thesis, it is necessary to understand the concepts described here.

We start with a description of pseudo-random number generators, followed by a brief overview of the GPU programming toolkit called CUDA. An introduction to branch divergence on GPUs is then given, and followed by a short description of regular and irregular workloads. Next, the application that is used for evaluating our methods, the stationary bootstrap, is introduced. We then provide an overview of splines, which are used for building regression models. Finally, an overview of existing workload partitioning approaches that we found interesting and relevant to this thesis is presented.

#### 2.1 Pseudo-random number generators

Generation of random numbers in computers is often done using pseudo-random number generators (PRNGs). The "pseudo" in the name stems from the fact that the sequence of generated numbers is not really random, but designed so that it will seem random to any external observers [Mon94].

PRNGs consist of an internal state, a state transition function and an output function [Mon94]. When a random number is to be generated, the internal state of the generator is computed by the state transition function, with the *current state* as input. The output function is then used, with the *new state* as input. The output of this function is the random number.

$$x_{n+1} = (ax_n + b) \mod m, 0 \le x_0 < m, n \ge 0$$

(2.1)

A simple example of a random number generator is the linear recursive congruential method [Hef86]. Here, the internal state is the variable x, the state transition function is the congruence in Equation (2.1), and the output function is the identity function.

A very important property of PRNGs is that both the state transfer and output functions are deterministic. Therefore, given an initial state  $x_0$ , the entire sequence of numbers generated is predictable. This initial state is called the *seed*. For example, using Equation (2.1) with parameters a = 73, b = 87, m = 93, and setting the initial state (seeding the generator)  $x_0 = 59$ , these are the first ten pseudo-random numbers: 23, 92, 14, 86, 41, 11, 53, 50, 17, 26. There is no more input to the PRNG than the parameters and the seed, so the exact same sequence will be generated for those same initial conditions.

A consequence of this determinism is that, while providing sufficient random-

2.2. CUDA 35

ness for many use cases, the use of PRNGs make experiments reproducible. As long as the initial seed is known, any experiment that depend on a PRNG for randomness will be reproducible, assuming the rest of the experiment is deterministic.

#### **2.2** CUDA

CUDA is NVIDIA's general purpose programming model for GPUs. It was introduced in 2006 [NVI17c], and features a compiler, library and runtime to enable developers to create programs to be executed on NVIDIA GPUs. One of the programming languages used by CUDA is C++, with a few extensions. Programs written for CUDA are first compiled using NVIDIAs compiler, nvcc, which separates the GPU specific code from the rest and compiles it. The CPU specific code is compiled using a standard C++ compiler, and the results combined into the same binary.

CUDA programs typically mix normal serial CPU code with code that runs on the GPU. Special directives are used for marking functions that can be run on the GPU or CPU, or both. These functions are called kernels. Running a kernel is called launching it, and a special syntax element has been added to the normal function call syntax to enable some additional configuration parameters.

# 2.2.1 GPU topology

NVIDIA GPUs consist of a number of *streaming multiprocessors* (SM). In each SM, there is a number of CUDA cores. The amount of CUDA cores and SMs differ between GPU generations, and also between GPUs of the same generation. For instance, the Pascal generation NVIDIA GTX 1080 Ti has 128 CUDA cores in each of the 28 SMs, for a total of 3584 CUDA cores.

Each streaming multiprocessor on the GPU has one instruction unit per 32 CUDA

cores. The CUDA cores are simple and relatively slow compared to a CPU core. They feature no out-of-order or speculative execution, and there is no branch prediction.

## 2.2.2 Grid, thread block and warp

Figure 2.1: CUDA grid, thread block and threads [NVI17c].

When a CUDA kernel is launched, a specified number of threads are spawned. Each thread executes the same kernel with the same parameters, except for a few implicit parameters that can be used to calculate the threads unique id. The threads are organized into thread blocks (sometimes just called blocks), which can be 1, 2 or 3-dimensional. The blocks are organized into a grid of blocks, which can also be 1, 2 or 3-dimensional. Figure 2.1 shows an example of a 2-dimensional block of threads

2.2. CUDA 37

in a 2-dimensional grid of blocks.

Each block is assigned to a single SM, and each SM can have multiple blocks assigned to it. When executing, groups of 32 threads from the same block are executed simultaneously. These groups of 32 threads are called warps. Because there is only one instruction unit per 32 CUDA cores, threads that belong to the same warp must always execute the same instruction at any time.

## 2.2.3 Memory hierarchy

There are several types of memories in CUDA GPUs. The fastest, and smallest, are located on the GPU chip, while the largest and slowest are located off the chip.

### Registers

Registers are the fastest type of memory in CUDA. They are used for thread local storage, and are located in each SM. There are typically thousands of registers per SM.

#### **Shared memory**

Each SM has a fast memory type that is called shared memory. Shared memory is local to each thread block, and the amount of shared memory is configurable. Shared memory can typically store on the order of tens of kibibytes.

#### L1 cache

Similarly to shared memory, there is an L1 cache in each SM. The amount is configurable per kernel, so the amount of L1 cache can be increased at the expense of less shared memory, and vice versa.

#### L2 cache

L2 is the largest memory that is located on chip, at a few mibibytes of size. It is used for caching accesses to local or global memory.

#### **Texture memory**

Texture memory is located off chip in global memory, but has a special cache on the chip that optimizes for spatial locality accesses.

#### **Local memory**

Local memory is also located off chip in global memory, and is used for storing thread local data that does not fit in the registers of a thread.

#### **Constant memory**

Constant memory is used for read only data, and has a special cache associated with it in each SM. Data can only be written to constant memory from the CPU. It is located off chip in global memory.

#### **Global memory**

Global memory is the largest of the memory types in CUDA GPUs. It can be both read from and written to, but is very slow compared to on chip memories. The size of the global memory may be tens of gibibytes.

# 2.3 Branch divergence on GPUs

GPUs implement the single instruction, multiple threads (SIMT) architecture. In this architecture, there is only one instruction unit per n cores (n = 32 in newer

CUDA cards). Statements that may cause threads to execute different control flows is therefore an issue, as the threads no longer will share instruction stream. This is called branch divergence.

Listing 2.1: Branch divergence example 1.

In listing 2.1, a CUDA kernel which exhibits branch divergence is shown. Threads with odd ids will enter the true part of the if statement, while threads with an even id will enter the false part. Because of the restriction of only one instruction per warp at a time, the GPU may solve this by first executing the true part with only the relevant threads marked active, and then doing the opposite for the false part. The result of this is that the total execution time becomes the sum of the execution times in both branches, as opposed to being the maximum of the two had there been two (or more) instruction units.

Listing 2.2: Branch divergence example 2.

Listing 2.2 shows another type of branch divergence, which is when the number of iterations in a loop is not equal for all threads. In this example the loop condition is what causes this, but it could just as well had been something else, like the amount the induction variable i is incremented each iteration. In this particular example, the id's of the threads of a warp will be strictly increasing by one from the lowest id to the highest. The number of iterations of the loop will match the id of a thread, so for each iteration, one less thread will be executing, and waiting instead. The end results is that approximately half of the "thread-time" will have been spent waiting for the other threads to finish (assuming  $0 \le id \le 31$  for all id's).

# 2.4 Irregular workloads

Parallel workloads can be divided into regular and irregular workloads [She+13]. Regular workloads are applications where all the work units are approximately of the same size, *i.e.* they take approximately the same amount of time to finish on the same hardware. Irregular workloads does not have this property, and the amount of work per work unit may vary by a lot.

2.5. BOOTSTRAP 41

Figure 2.2: Comparison of regular and irregular workloads

Figure 2.2a shows an example of an application with a regular workload. Such applications may perform well without modifications when run on the GPU. An example of a regular workload is (dense) matrix multiplication.

Figure 2.2b shows an example of an application with an irregular workload. If run on a GPU without modifications, one can expect to see a large fraction of inactive threads to active threads, due to some threads being assigned a very time consuming workload compared to the other threads in the same warp. An example of an irregular workload is ray tracing [She+13], where each ray represents a work unit. The work unit size per ray may differ because of a variable time step, which may be dependent on simulation conditions.

# 2.5 Bootstrap

Statistical bootstrap [Efr79] is a method of estimating properties of the sampling distribution of a random sample. Such properties may be the mean, variance and median or higher order moments. In this work, the arithmetic mean is of particular

interest, so the method will be described with a focus on it, yet the same method applies to the other properties as well.

Given a random sample  $X = (x_0, x_1, ... x_m)$ , the mean can be estimated using the bootstrap method as follows: A new sample  $X_1$  is generated by sampling with replacement from X m+1 times, such that  $X_1$  is of the same size as X. The statistic of interest is then computed from the new random sample  $X_1$ . This process is repeated n times, for sufficiently large n. The results from those computations are n means, which can be grouped into bins to form a histogram. This histogram is the resulting estimate of the mean, and can be used to compute such values as the confidence interval of the mean.

## 2.5.1 The stationary bootstrap

The stationary bootstrap is a special case of the bootstrap, introduced by D. Politis and J. Romano [NP94]. It attempts to address the issue that regular bootstrap fails to capture the dependency between adjacent samples in the data, if there is such a dependency. The stationary bootstrap is applicable to stationary, weakly dependent time series [ECO]. The stationary property means that the sampling distribution is static, and the weakly dependent property means that the correlation between two samples tends to 0 sufficiently quickly as the distance between them (in time) grows.

The stationary bootstrap differs from the regular bootstrap in how it resamples the data. To capture the dependence between samples, it does not draw samples one-by-one, but selects all samples that fall within some window. The start of this window is drawn from a uniform distribution, and the size of the window is drawn from a geometric distribution (with parameter p). If the start of the window, plus the size of it, should exceed the size of the time series, the windows wraps around and continues from the beginning of the time series. This process is continued until

2.5. BOOTSTRAP 43

the new time series is the same size as the original. If a window is selected such that the size of the new time series will be larger than the original time series, the size of the window is shrunk until this is no longer the case.

Figure 2.3: Original time series.

Figure 2.4: One of the possible resampled time series.

Figure 2.3 shows an example of a time series. The red parts are two examples of windows that were selected for "transfer" to the new, resampled time series. In Figure 2.4, the same windows of samples have also been marked red, to make them easier to identify. Note that the entire resampled time series is made up of such windows, but only two of those are marked in red. The first red part from the original time series can be found near the end in the resampled time series, where it has also been marked red. The other red part, which can be found in the original time series at 50 < Time < 80, appears in the resampled time series at 30 < Time < 60.

2.6. SPLINES 45

# 2.6 Splines

Splines are mathematical functions defined by piecewise continuous polynomials. They have a high degree of smoothness, meaning that, for all x at the interval bounds of the piecewise functions  $f_i$ , the sum

$$\sum_{i=0}^{n-1} (f_i'(x) - f_{i+1}'(x))^2 \tag{2.2}$$

is minimized.

Splines can be defined for multivariate functions  $f: \mathbb{R}^m \to \mathbb{R}^n$ , but in this project only the univariate spline with a single output is needed  $(f: \mathbb{R} \to \mathbb{R})$ , so this explanation will focus on the univariate spline. In particular the basis spline (B-spline), which defines splines using a recurrence relation, will be presented here.

A B-spline is defined in terms of a vector of basis functions, with a coefficient for each basis function which adjusts the contribution from each basis function. Mathematically a spline f can be defined as follows [GS16]:

$$f(x) = \sum_{i=0}^{n} c_i b_i(x),$$

(2.3)

where b is the vector of basis functions, and c are the coefficients. Two of the parameters to the basis functions have been skipped here; The interval it is defined on (t), and its degree p. All basis functions, except those of degree p = 0, are defined in terms of two other basis functions of degree one less than itself. The basis functions b can thus be defined by a recurrence relation (p parameter included, t being implicit):

$$b_{i,p} = \frac{x - t_i}{t_{i+p} - t_i} b_{i,p-1}(x) + \frac{t_{i+1+p} - x}{t_{i+1+p} - t_{i+1}} b_{i+1,p-1}(x)$$

(2.4)

with the special case for basis functions of degree p = 0:

$$b_{i,0} = \begin{cases} 1, & \text{if } t_i \le x < t_{i+1}. \\ 0, & \text{otherwise.} \end{cases}$$

(2.5)

The vector t is often called the knot vector of the spline. Each basis function of degree p=0 is 1 inside one such interval, and 0 everywhere else. This *local support* property of the p=0 degree basis function means that the basis function that is defined in terms of the zero degree basis function also has local support, but on one additional interval. So, for a p=3 degree basis function, it is defined in terms of p+1=4 zero degree basis functions, and by extension p+1=4 intervals. Spline implementations on computers can exploit this property to only evaluate the basis functions that contribute to the value of the spline at each point, for example by using de Boor's algorithm [Boo72]. Because the basis functions are defined as a convex combination, the evaluation of a spline is numerically stable.

## 2.6.1 The penalized spline (P-spline)

There are several ways of fitting a spline to a data set, one of which is to minimize Equation (2.6) to get an interpolating spline.

$$\sum_{i=0}^{n} (y_i - f(x_i))^2 \tag{2.6}$$

The coefficients and knot vector of interpolating splines are chosen so as to minimize Equation (2.6), while retaining the smoothness property of the spline. For some datasets, minimizing Equation (2.6) may lead to a phenomenon known as overfitting, where the spline ends up fitting noise instead of capturing the informa-

2.6. SPLINES 47

tion in the data. Interpolating splines may therefore have suboptimal performance on regression problems.

Penalized splines (P-splines) may reduce the problem of overfitting. When building a P-spline, a term is added to Equation (2.6) (resulting in Equation (2.7)) to penalize large second derivatives of the spline.

$$\sum_{i=0}^{n} (y_i - f(x_i))^2 + \lambda \int_{x_i}^{x_{i+1}} f''(x)^2 dx$$

(2.7)

The parameter  $\lambda \in [0,\infty)$  controls the amount to penalize large f''(x). A  $\lambda = 0$  yields an interpolating spline, while  $\lambda = \infty$  will yield behaviour equal to linear least squares regression.

Figure 2.5: Example of a B-spline overfitting a data set.

Figure 2.6: Fitting the same data set with a penalized spline.

Figures 2.5 and 2.6 demonstrate how a B-spline may overfit a data set, and how a penalized spline may be used to capture the underlying information in the data better. In this case, the underlying function is a third degree function with Gaussian noise ( $\mu = 0, \sigma = 70$ ) applied to the 30 samples that were used for building the splines.  $\lambda = 1.0$  were used for building the P-spline. At x = 0 we see the worst case of overfitting, the actual value of the function is f(0) = 7, but due to the noisy sample, the B-spline predicts a value of around -100. The P-spline has a far better prediction, at around -40. Fitting the sample at x = 0 would require a large second derivative at the local minimum, which would add a large penalty to the spline, and is therefore avoided.

2.7. RELATED WORK 49

## 2.7 Related work

In the literature, there is a division of load balancing methods into static and dynamic load balancing. Static load balancing is when the balance is determined once - typically based on performance models - and is not changed during computation. Dynamic load balancing is when the balance may change during execution, for example as a consequence of observing the relative performance of the devices. The types of load balancers are further divided into balancing data-parallel and task-parallel applications. We focus our study on data-parallel load balancers as they fit our scope, but include an interesting approach to task-parallel load balancing that may be used for data-parallel applications with minor changes, and another approach to task-parallel load balancing using a task graph.

## 2.7.1 Static load balancing approaches

In static load balancing approaches, a performance model of the devices is often used to predict their relative performance [She+13; She+16; FE16], and then selecting a partition based on the estimated throughput of each device.

#### Workload reshaping

[She+13] introduced an approach to static load balancing of *irregular* workloads that is applicable to applications with kernels consisting of one or more loops. The workload distribution is sampled, where the output from the samples is the number of iterations of these loops. They then apply a technique they call *workload reshaping*, in which they build a model of the workload distribution using the samples, and sort the workloads by the number of iterations of the loops. The distribution is then analyzed to determine the shape of it, *e.g.* find flat areas and areas with peaks. Using

execution times from previous runs, a partition point that minimizes the difference between the CPU and GPU execution times is determined. Flat areas are scheduled to run on the GPU, and areas with peaks are scheduled to run on the CPU. The reasoning for this scheduling is that flat areas is thought to have less branch divergence.

### Machine learning based models

[FE16] proposed an approach to static load balancing of *regular* workloads based on machine learning. In their method, a device is selected to be the main device. Then, for each additional device, a model is built using machine learning that takes hardware counters from the main device as input, and the throughput of another device as output. The models are trained in an offline phase by running the program with many different parameters. At run time, a small input is run on the main device, and the hardware counters used as input for all the models. The output is then used as an estimate for the execution time of each additional device, and the workload is distributed so that each device gets a workload that is proportional to their estimated throughput.

#### Linear regression models

[She+16] proposes two approaches for modelling the throughput of the devices. The first uses offline profiling, where the throughput of each device, and the transfer time from CPU memory to GPU memory, are recorded for different input sizes. The throughputs are then used to build linear regression models for each device and the data transfer. They divide the problem range into several sets, where each set fits into a different physical memory type. This means that they build one linear regression model for problem sizes that fit in L1 cache memory, one regression model for problems that fit in L2 cache memory, etc. For online profiling, they run a very small

2.7. RELATED WORK 51

input on each device and record the throughputs and data transfer time. Similarly to [She+13], they apply workload reshaping to facilitate division of the workload into flat and peak areas. In this method, however, the programmer is required to manually model the shape of the workload.

## 2.7.2 Dynamic load balancing approaches

### Increasing chunk size

[Boy+13] developed a dynamic load balancer that works by initially assigning a small workload, called chunks, to each device. As the devices finish computing the initial chunks, a new, larger chunk is assigned to them. When all devices have finished executing a set number of chunks,  $\gamma$ , the throughputs of the previous runs are used to partition the remaining work into n chunks, where n is the number of devices.

#### Persistent kernel

[Che+10] offers an interesting approach to balance task-parallel applications. They launch one persistent kernel with *B* thread blocks for each GPU, where *B* can be as large as the maximum number of concurrently executing thread blocks on each device. One or more task queues are created, to which the CPU thread submits tasks. One thread in each thread block polls the queue(s) for a task to execute. When a task is received by the thread, the thread block executes the task. This process continues until a special HALT task is submitted to the queue(s), causing the kernel(s) to halt execution.

We argue that this approach can be used for balancing data-parallel applications by splitting the input into many small tasks, and submitting these to the task queue for processing by the GPU(s).

## Task graph

StarPU is a runtime system introduced by [Aug11]. Tasks are submitted by the application to the StarPU scheduler, which selects the next task to run and on which device, based on a scheduling policy. Each task has a *codelet*, which contains an implementation of the functionality of the task for one or more devices. When a task is selected for execution, the scheduler uses the estimated execution time of running the codelet on each device to determine the device the codelet should be run on.

The tasks in StarPU may have dependencies on other tasks. StarPU automatically builds a task graph from these dependencies, and handles transfer of the input and output data from and to each device. Special functions called *filters* can be used to partition the data into *blocks*. A task is generated for each block of data, and the data is combined to the final result when all the tasks have finished executing.

# Chapter 3

# Methodology

The purpose of this chapter is to provide a description of the methods used for partitioning the workload both between the CPU and GPU, and internally in the GPU.

Throughout this chapter and the following chapters, the variables l, p and n will be used extensively. Where not specified otherwise, they are meant to denote the length of the time series, the p-parameter of the geometric distribution used in the stationary bootstrap, and the number of resamplings to perform, respectively.  $n_{cpu}$  and  $n_{gpu}$  are used to denote the number of resamplings assigned to the CPU and GPU, respectively.

The structure of the chapter is as follows: First, the method used for modelling the execution time of different processes is described. Then, a presentation of the methodology for reducing branch divergence in the GPU kernels is provided, along with a short review of the irregularity of the workload in stationary bootstrap. A method for automatically determining the optimal execution path of the GPU process is then presented, and finally our method for workload partitioning across the

CPU and GPU is described.

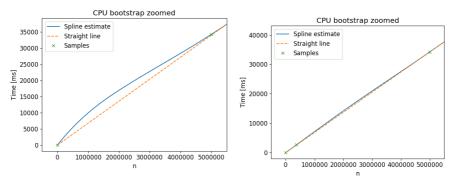

# 3.1 Performance modelling

The execution time of different processes are modelled by a one dimensional P-spline of degree 3 with  $\lambda=0.1$ , or, in the case of the model of the CPU execution time,  $\lambda=0.001$ . Every time the process is executed, the execution time is recorded and used to update the spline with the new data. The execution time of most processes depend on 3 variables: l, p and n. The version of SPLINTER [Gri+15] we use require the samples to form a regular grid. This means that building a spline with multiple input dimensions require a number of samples that is exponential in the number of dimensions, and can therefore quickly become very large. To avoid having to sample the input space in many points, the dimensionality has been reduced to 1 by constructing a new spline for each pair of l and p.

A P-spline of degree 3 requires at least 4 unique samples to be built. For inputs where the number of unique samples is less than this number, the estimate is reported as 0. The same is also true for n that lie outside of the estimator support, which limits the use of the estimator to interpolation, and avoids extrapolation.

At program exit the splines are saved to disk. When estimates for some pair of l and p is required, the relevant splines are loaded and used.

Figure 3.1: The estimator for the operation *Initialize PRNG 2* after 40 executions.

Figure 3.1 shows the recorded data points and the spline estimate for a range of values of n. We can see that the penalty of the P-spline ensures that the spline does not overfit by interpolating the sample at  $n \approx 2,500,000$ .

# 3.2 Partitioning of workload in the GPU

Our approach to partition the workload on the GPU aims to reduce the branch divergence of the kernels, and thereby achieve a reduction in the execution time of the kernel by spending less time in divergent branches.

We start by providing a short analysis of the irregularity of the workload in stationary bootstrap, which is followed by a description of the method we use to reduce branch divergence.

## 3.2.1 Irregular workload in stationary bootstrap

#### Distribution of workload

The stationary bootstrap uses a geometric distribution for selecting the sizes of the windows. The geometric distribution has a parameter,  $p \in (0,1]$ . The expected value of the distribution is  $\mu_{\text{geometric distribution}} = \frac{1}{p}$ . For a time series of size l, the expected number of windows to be drawn is therefore  $\mu_{\text{#windows}} = \frac{l}{\mu_{\text{geometric distribution}}} = lp$ . In this thesis, we use the term *number of windows* or *number of iterations* extensively to denote the number of windows that must be selected to fully resample a time series, which is equivalent to the number of iterations of the loop that performs the resampling. This metric is our measure of the workload of each resampling.

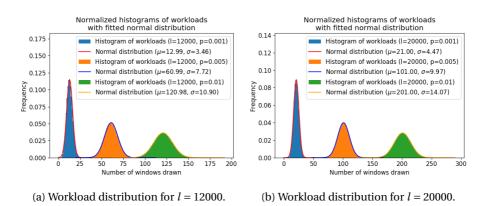

Figure 3.2: Workload distribution for  $l \in [12000, 20000]$  and  $p \in \{0.001, 0.005, 0.01\}$ .

Figure 3.2a shows the frequency of each iteration count / number of windows for l = 12000 and three different values of p. Figure 3.2b shows the distribution of the same ps for l = 20000. We can see that as p is increased, the expected number of windows increases, but so does the variation. The workload also increases as l is

increased. The workloads appear to be approximately normally distributed for all sets of parameters, with a worse fit for when the expected value is low.

#### Coefficient of variation

The coefficient of variation is a metric for showing the relative variation of a population with respect to the expected value. It is defined as

$$c_{\nu} = \frac{\sigma}{\mu} \tag{3.1}$$

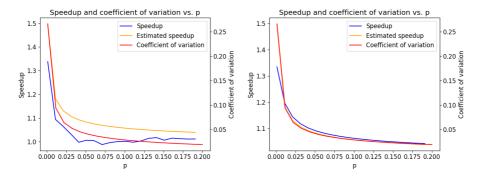

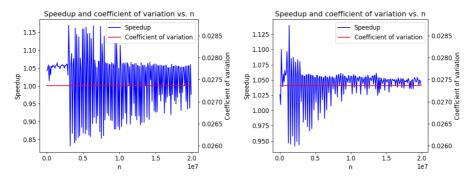

The metric proves to be a very useful metric for determining the speedup that is achievable by reorganizing the workload. In the figures below we show how the coefficient of variation varies for the stationary bootstrap as l or p is changed.

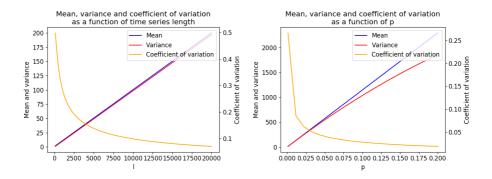

Figure 3.3: Coefficient of variation, mean and variance as a function of the time series length and p, separately.

We can see that the mean and variance of the workload distribution grows as l or p is increased, while the coefficient of variation decreases.

## 3.2.2 Reorganization of workload

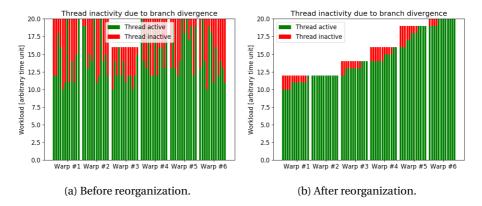

In our implementation of the stationary bootstrap on the GPU, each thread performs one resampling of the time series. There is a separate PRNG for each thread, and each PRNG is seeded with a randomly drawn seed. Taking inspiration from the workload reshaping of [She+16], we apply a sorting of the PRNG seeds based on the resulting main loop iteration count. Figure 3.4a shows a fictional example of the workloads per work unit, divided into warps of size 12 (for illustrative purposes). The green bars are where a thread is active, and the red bars are where a thread is marked inactive, thus wasting resources. Because of branch divergence, the longest green bar determines the execution time of each warp. The bigger the variation in work unit size, the more thread-time is wasted by threads waiting for the thread with the largest work unit to finish. Figure 3.4b shows the exact same workload as figure 3.4a, but where the work units are sorted based on their size. The amount of wasted thread-time has been reduced from 338 to 62, or from 24% of the total execution time to 6% of the total execution time. There is even a warp where no thread is marked inactive at all.

Figure 3.4: Thread activity before and after reorganizing the workload by the amount of work per work unit.

#### PRNG seed as predictor for iteration count

In some problems, such as the stationary bootstrap described later, the seed of the PRNG is a perfect predictor for the number of iterations of the main loop in the kernel. The PRNG that implements the geometric distribution is a deterministic function of the seed, which makes the sequence of window sizes deterministic, and therefore the number of iterations needed by the loop to reach the stopping condition. When saying that a seed uniquely determines the size of a work unit, it is implied that l and p are not varied.

# 3.2.3 Generation of seed to iteration count mapping

To be able to sort the seeds based on their respective workloads, a mapping from all possible PRNG seeds to the iteration counts they result in is needed. Mathematically, there is an infinite number of different seeds to the PRNG, which renders this task impossible. Due to technical constraints, however, there is a finite set of seeds.

3.3. TASK GRAPH 61

On some systems, the seed is represented by a 32-bit integer, which can represent  $2^{32}$  different values. A mapping from  $2^{32}$  different seeds to iteration counts may be represented by an array where the index is the seed, and the value is the resulting iteration count if the PRNG is seeded with that seed. Assuming the values need to be represented by a 32-bit integer, this array would take  $2^{32} \times 4B = 16$  GiB of memory. To be able to load this array into memory for fast access, we have halved the amount of seeds we generate, by not computing the mapping for seeds where the most significant bit is 1. Our mapping is therefore a mapping from  $2^{31}$  seeds to iteration counts, and occupies 8GiB on disk / memory.

Section 3.2.2 notes that the iteration counts depends on the PRNG seed in addition to l and p. Therefore, we precompute and store the mappings each time a new unique pair of l and p is encountered.

# 3.3 Task graph

The GPU bootstrap process is represented by a set of *operations*. An operation is a function that operates on some input, and has either side effects or outputs, or both. Each operation has some preconditions that must be true before it can execute, and postconditions that must be true after its execution. The postconditions of some operations are the preconditions of other operations, so that each operation has one or more operations that must be executed before it itself can be executed. An operation is statically assigned to either the GPU or the CPU at compile time. The execution time of each operation is modelled using the method presented in Section 3.1.

A task graph of the program is then made by constructing a directed acyclic graph (DAG) of the operations. The nodes in the DAG represents an operation, and an edge from node A to node B represents that the operation represented by node

A must be executed before the operation represented by node B. If a node has more than one ancestor, one and only one of the operations represented by the ancestor nodes must be executed before it. The complete task graph of the program can be seen in figure A.1 in the appendix.

The task graph has a single top node (source) and a single leaf node (sink), where both represent null operations. Executing all operations along a path from the source to the sink results in a valid execution of the program. The possible paths of the task graph can be seen in figures A.2, A.3, A.4 and A.5 in the appendix.

The underlying function of an operation is not necessarily unique. As in the case of the *Initialize PRNG 1* and *Initialize PRNG 2* operations, they are distinct operations but the underlying function is the same. This makes it possible to distinguish between the two in the task graph, which is important as the two have different preconditions. As an example, one of the preconditions of the *Initialize PRNG 1* is that the seeds are reorganized so that the iteration counts are monotonically increasing, which is one of the postconditions of the sorting operations. The *Initialize PRNG 2* does not have this precondition.

Resources may be allocated in an operation, and not released by the same operation. An operation later in the task graph will handle the release of the resource. Memory leaks and segmentation faults are avoided by carefully inspecting the preand postconditions of each operation. For example, the precondition of an operation may be that memory has been allocated for a variable, which is a postcondition of an earlier operation.

# 3.3.1 Optimal execution path

At run time, the task graph is used with the execution time models of each operation to determine the optimal path through the program. Using the estimated time of

3.3. TASK GRAPH 63

each operation, we find the path that is estimated to take the least amount of time to execute.

The task graph is used directly for finding the shortest path. The weight of each edge is defined to be the estimate of the operation at the end of the edge. A shortest path algorithm is then used for finding the *optimal execution path*, and returns it as a linked list of the operations. Because the operations have estimators that depend on the set of inputs to the program (see 3.1), the optimal path through the program depends on these parameters as well. If there exists some point in the parameter space where the optimal path changes, then the program will automatically change execution path to that path, assuming perfect estimators.

It is useful to be able to force execution through one path, for example if we want to compare one execution path to another. To achieve this, the estimator of an operation can be forced to report a large negative number. Because of this, the Bellman-Ford algorithm [Shi54] is used for finding the shortest path, because it works correctly with negative edge weights. Introducing negative edges can lead to negative cycles, which is not handled correctly by the algorithm. This is not an issue, as there are no cycles in the task graph. This knowledge of no (negative) cycles has been exploited to optimize the Bellman-Ford algorithm, by removing the check for negative cycles.

A new and untrained task graph will have operations where no estimators have been built yet. When the program has selected the same path 4 times, the estimators of the operations in that path will be built. The path will then have a non-zero estimate, while the other paths still estimates 0 execution time, except for the operations they have in common with the "trained" path. This will force the program to select one of the paths that has not yet been tested sufficiently to build a model. The same is true if parameters outside the support of the underlying splines are selected.

# 3.4 CPU and GPU workload partitioning

We treat load balancing between the CPU and GPU as an optimization problem, where the objective is to minimize the total execution time of the program. The execution time is defined to be the maximum of the execution time of the CPU and the GPU. The objective function to be minimized is therefore

$$\max(t_{\text{cpu}}(nf_{\text{cpu}}), t_{\text{gpu}}(nf_{\text{gpu}})) \tag{3.2}$$

where

$t_{\mathrm{cpu}}(x)$  is the estimated execution time of running x resamplings on the CPU,  $t_{\mathrm{gpu}}(x)$  is the estimated execution time of running x resamplings on the GPU,  $f_{\mathrm{cpu}}$  is the fraction of the total amount of resamplings to be run on the CPU,  $f_{\mathrm{gpu}}$  is the fraction of the total amount of resamplings to be run on the GPU, n is the total number of resamplings.

The optimization is subject to the constraint

$$f_{\text{cpu}} + f_{\text{gpu}} = 1 \tag{3.3}$$

There are two decision variables in this optimization problem:  $f_{cpu}$  and  $f_{gpu}$ . Rewriting the constraint in Equation (3.3), we can eliminate one of the decision variables:

$$f_{\text{cpu}} = 1 - f_{\text{gpu}} \tag{3.4}$$

The objective function then becomes

$$\max(t_{\text{cpu}}(nf_{\text{cpu}}), t_{\text{gpu}}(n(1 - f_{\text{cpu}}))) \tag{3.5}$$

with the original constraint in Equation (3.3) replaced by

$$0 \le f_{\text{cpu}} \le 1 \tag{3.6}$$

For clarity, the optimization problem is presented in its entirety below.

$$\begin{aligned} & \underset{f_{\text{cpu}}}{\text{min}} \quad t_{\text{cpu}}(nf_{\text{cpu}}), t_{\text{gpu}}(n(1-f_{\text{cpu}})) \\ & \text{s.t.} \quad 0 \leq f_{\text{cpu}} \leq 1 \end{aligned} \tag{3.7}$$

The objective function is minimized using gradient descent [Rud16]. The gradient descent is started at  $f_{\rm cpu}^0 = 0.5$ , and in each iteration x,  $t_{\rm cpu}(nf_{\rm cpu}^x)$  and  $t_{\rm gpu}(n(1-f_{\rm cpu}^x))$  are computed. The derivative of the max function is the derivative of the larger of its arguments, so if  $t_{\rm cpu}(nf_{\rm cpu}^x)$  is larger than  $t_{\rm gpu}(n(1-f_{\rm cpu}^x))$ ,  $f_{\rm cpu}^{x+1}$  is updated according to Equation (3.8). If  $t_{\rm gpu}(n(1-f_{\rm cpu}^x))$  is the larger of the two values,  $f_{\rm cpu}^{x+1}$  is updated according to Equation (3.9).

$$f_{\text{cpu}}^{x+1} = f_{\text{cpu}}^{x} - \gamma \frac{\partial t_{\text{cpu}}(n f_{\text{cpu}}^{x})}{\partial n},$$

(3.8)

$$f_{\text{cpu}}^{x+1} = f_{\text{cpu}}^{x} - \gamma \frac{\partial t_{\text{gpu}}(n(1 - f_{\text{cpu}}^{x}))}{\partial n},$$

(3.9)

In our experiments, we have found that  $\gamma = 0.7$  balances the trade-off between convergence rate and accuracy well. The optimization continues while the number of iteration is less than 100 and Inequality (3.10) is true. In the optimal point, the

left-hand side of Inequality (3.10) is equal to 1.

$$\frac{\min(t_{\rm cpu}(nf_{\rm cpu}^x), t_{\rm gpu}(n(1-f_{\rm cpu}^x)))}{\max(t_{\rm cpu}(nf_{\rm cpu}^x), t_{\rm gpu}(n(1-f_{\rm cpu}^x)))} < 0.99$$

(3.10)

The gradient descent algorithm is started at a single point, rather than multiple, because the execution time models have been experimentally verified to be monotonically increasing, and therefore have no local minima - except the global minimum - that the algorithm can get stuck in. The discontinuity of the derivative of the objective function in the optimal point is not a problem, because the optimization terminates at that point.

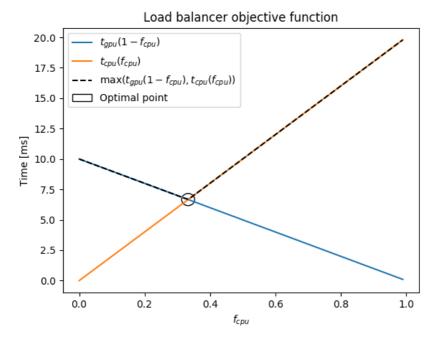

Figure 3.5: Constructed example of load balancer objective function.

Figure 3.5 shows a synthetic example of the behaviour of the  $t_{\rm cpu}$  and  $t_{\rm gpu}$  functions. The max function of the two functions would be equal to  $t_{\rm gpu}$  from  $f_{\rm cpu}=0$  to  $f_{\rm cpu}\approx 0.33$ , and equal to  $t_{\rm cpu}$  from  $f_{\rm cpu}\approx 0.33$  to  $f_{\rm cpu}=1$ , in this case. The derivative of the max of these functions is therefore equal to the derivative of the larger of the two.

Algorithm 3.1: Load balancer optimization.

```

input: int n

output: float f_{\text{cpu}}, float f_{\text{gpu}}

begin

f_{\rm cpu} \leftarrow 0.5

i ← 0

\gamma \leftarrow 0.7

\textit{while} \;\; i \; < \; 100 \;\; \textit{and} \;\; \frac{\min(t_{cpu}(nf_{cpu}),t_{gpu}(n(1-f_{cpu})))}{\max(t_{cpu}(nf_{cpu}),t_{gpu}(n(1-f_{cpu})))} \; < \; 0.99 \;\; \textit{do}

if t_{cpu}(nf_{cpu}) > t_{gpu}(n(1-f_{cpu})) then

f_{\text{cpu}} \leftarrow f_{\text{cpu}} - \gamma \frac{\partial t_{\text{cpu}}(nf_{\text{cpu}})}{\partial n}

else

f_{\text{cpu}} \leftarrow f_{\text{cpu}} - \gamma \frac{\partial t_{\text{gpu}}(n(1 - f_{\text{cpu}}))}{\partial n}

11

f_{\text{gpu}} \leftarrow 1 - f_{\text{cpu}}

i \leftarrow i + 1

13

return f_{cpu}, f_{gpu}

end

```

Algorithm 3.1 shows the pseudocode of the load balancer optimization process.

# Chapter 4

# **Implementation**

In this chapter we present a detailed description of the program that was implemented to evaluate our methods. Of the sections in this chapter, only Section 4.4 and 4.6.1 are required reading to be able to follow the rest of the thesis. The other sections describe implementation details which are included for the sake of reproducibility.

The chapter starts with an overview of the program, followed by a description of the program flow. Next, an overview of some command line parameters, followed by a note on the statistics that are recorded during execution. The different stationary bootstrap implementations are then presented, along with a general optimization that is applied to all implementations. Finally, a short presentation of the CPU and GPU modules. The description of the GPU module includes a short description of each of the implemented operations of the task graph.

# 4.1 Tools and hardware

Program code is written in C++11 and CUDA C, and is compiled using nvcc v8.0.61 with GCC version 5.4.0 as the back-end compiler used by nvcc. SPLINTER version 3-0 [Gri+15] is used for constructing, evaluating, saving and loading splines, and nlohmann::json [Loh17] is used for outputting statistics and results to the JSON format, which is easy for humans to parse as well as for machines. Python 3.5.1 is used for analyzing stats and, using matplotlib version 2.0.0, generating figures. All experiments have been run on Ubuntu 16.04 with Linux kernel 4.10.

The hardware configurations used are listed below:

| CPU         | AMD Ryzen 1800x             |

|-------------|-----------------------------|

| GPU         | NVIDIA GTX 1080 Ti 11GiB    |

| Motherboard | ASUS Crosshair VI Hero      |

| Memory      | 16 GiB                      |

| Storage     | Samsung 750 EVO 232 GiB SSD |

Table 4.1: Hardware configuration #1

| CPU         | AMD Ryzen 1800x             |

|-------------|-----------------------------|

| GPU         | NVIDIA GTX 480 1.5GiB       |

| Motherboard | ASUS Crosshair VI Hero      |

| Memory      | 16 GiB                      |

| Storage     | Samsung 850 EVO 232 GiB SSD |