# Suggested Methods for Preventing Core Saturation Instability in HVDC Transmission Systems

Ian Norheim,

Norwegian University of Science and Technology Faculty of Information Technology, Mathematics, and Electrical Engineering N-7491 TRONDHEIM, NORWAY

February 18, 2002

URN:NBN:no-2111

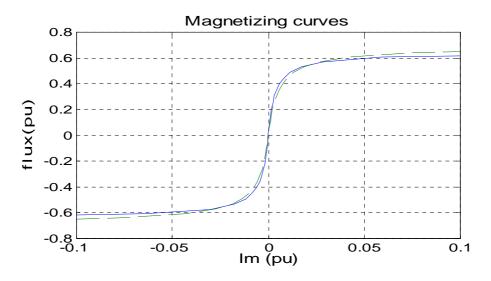

## Acknowledgements

This thesis was carried out under the supervision of Professor Tore M. Undeland, The Department of Electrical Power Engineering, Norwegian University of Science and Technology. I want to thank him for his valuable help during my work. I also appreciate that he allowed me to travel quite a lot during my work.

I would also like to thank Magnar Hernes and Thor Henriksen at SINTEF Energy Research for their good advice in the areas of power electronics and transformers.

I also appreciate the advice during the English editing of this thesis given by Stewart Clark at the Norwegian University of Science and Technology.

Several friends have also been a great help for me as I have worked on this thesis. Especially, I want to thank the Hauglands for their great support in the time before and after my mother passed away.

My wife Hilde has been a great encouragement and comforter to me as I have worked my way steadily through this thesis. I am deeply grateful to her.

Trondheim, February 2002

Ian Norheim

URN:NBN:no-2111

# **Summary**

In this thesis a study of the HVDC related phenomenon core saturation instability and methods to prevent this phenomenon is performed. It is reason to believe that this phenomenon caused disconnection of the Skagerrak HVDC link 10 August 1993. Internationally, core saturation instability has been reported at several HVDC schemes and thorough complex studies of the phenomenon has been performed. This thesis gives a detailed description of the phenomenon and suggest some interesting methods to prevent the development of it.

Core saturation instability and its consequences can be described in a simplified way as follows:

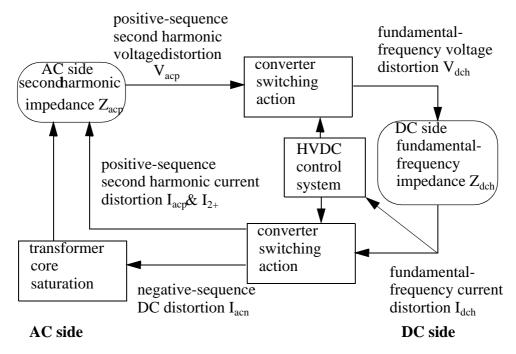

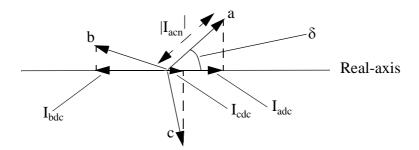

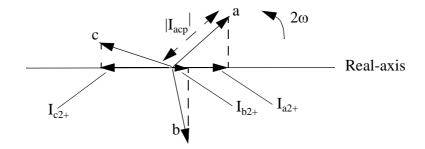

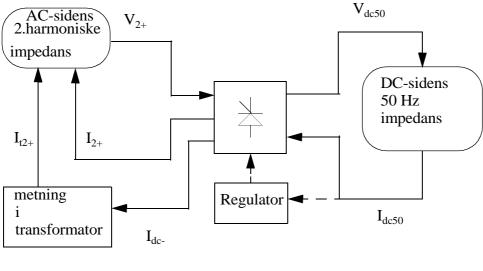

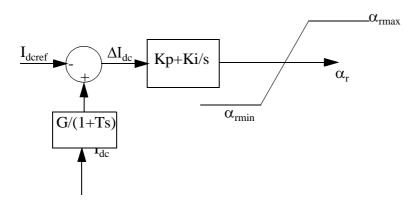

It is now assumed that a fundamental harmonic component is present in the DC side current. Due to the coupling between the AC side and the DC side of the HVDC converter, a subsequent second harmonic positive-sequence current and DC currents will be generated on the AC side. The DC currents will cause saturation in the converter transformers. This will cause the magnetizing current to also have a second harmonic positive-sequence component. If a high second harmonic impedance is seen from the commutation bus, a high positive-sequence second harmonic component will be present in the commutation voltages. This will result in a relatively high fundamental frequency component in the DC side voltage. If the fundamental frequency impedance at the DC side is relatively low the fundamental component in the DC side current may become larger than it originally was. In addition the HVDC control system may contribute to the fundamental frequency component in the DC side voltage, and in this way cause a system even more sensitive to core saturation instability. The large magnetizing currents that eventually will flow on the AC side cause large zero-sequence currents in the neutral conductors of the AC transmission lines connected to the HVDC link. This may result in disconnection of the lines. Alternatively, the harmonics in the large magnetizing currents may cause overheating of filters or other components. This may also cause disconnection.

In this thesis, several ways to reduce/eliminate the core saturation instability problem are described and most of them are also demonstrated by simulations on a modified CIGRE HVDC benchmark model in PSCAD/EMTDC version 3. PSCAD/EMTDC version 3 is a powerful simulation tool which perform simulations in the time domain and offers detailed models for transformers, power electronic switches etc. To understand and have confidence in the simulation results, the transformer models, the model for the on-line frequency scanner, and models for power electronic switches are evaluated in detail.

The suggested initiatives that were successfully simulated are listed below:

1) Stabilizing loops in the control system of the HVDC link.

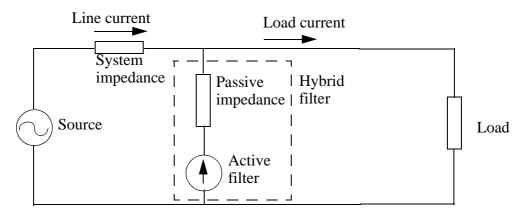

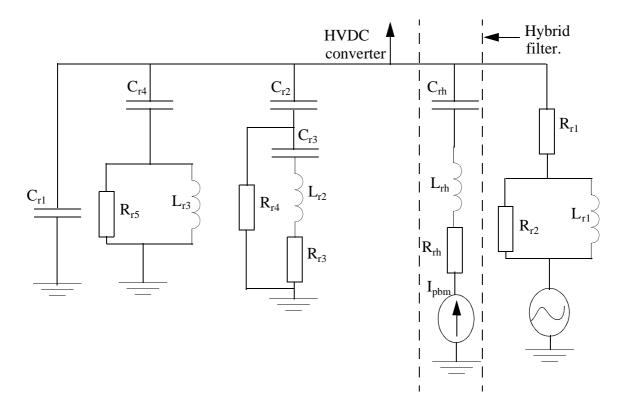

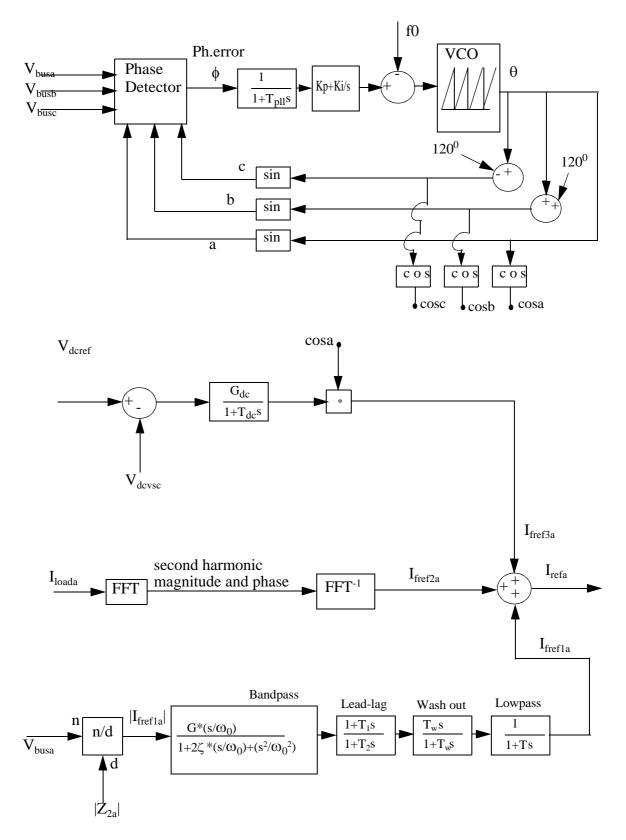

These loops diminish the influence of the HVDC control system on core saturation instability. Some of the loops suggested are believed to give improvements in applications where it is required that the stabilizing loop are only active for a small band of frequencies. 2) A hybrid shunt filter connected to the commutation bus on the AC side.

The hybrid filter consists of a PWM converter in addition to a passive circuit of components. It is superior to the plain passive filter because it does not cause any resonances with the AC grid and because it is not as sensitive to component drifting as passive filters. The hybrid filter prevents most of the second harmonic current generated by the HVDC converter to flow into the AC grid. This way the second harmonic component in the commutation voltages is significantly decreased.

3) A passive shunt filter connected to the commutation bus on the AC side.

Functions the same way as the hybrid shunt filter, but it may create resonances with the AC net. In addition it is more sensitive for changes in the component values than the hybrid filter.

4) A blocking LC filter between the low voltage potential and earth on the DC side

This filter blocks any fundamental frequency current from flowing on the DC side at the same time as it allows the DC component in the DC side current to flow through it. By placing the filter between the low voltage potential and earth on the DC side it does not have to sustain the DC side voltage.

It is 1) that represent the most preferable solution. It does not introduce any new components in the AC or DC grid, and it is inexpensive compared to the other solutions. The solutions in 2), 3), and 4) requires large and expensive components. However, it might be that in future schemes hybrid filters replaces passive filters on the AC side. Then it might be inexpensive and convenient to use the hybrid filters to prevent core saturation instability.

URN:NBN:no-2111

URN:NBN:no-2111

| 1     | Introduction                                                                            | 1  |

|-------|-----------------------------------------------------------------------------------------|----|

| 2     | Theory about HVDC transmission                                                          | 3  |

| 2.1   | Advantages of HVDC transmission                                                         | 3  |

| 2.2   | Principles of HVDC transmission                                                         | 4  |

| 2.2.1 | Typical HVDC schemes                                                                    | 5  |

|       | Converter operation                                                                     | 6  |

|       | Harmonics                                                                               | 14 |

| 2.3   | The HVDC control system                                                                 | 22 |

| 2.3.1 | Typical control strategies                                                              | 22 |

| 3     | Theory about core saturation instability                                                | 31 |

| 3.1   | Harmonic interaction                                                                    | 31 |

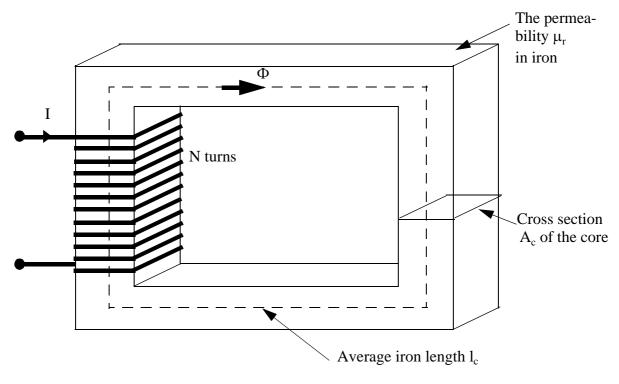

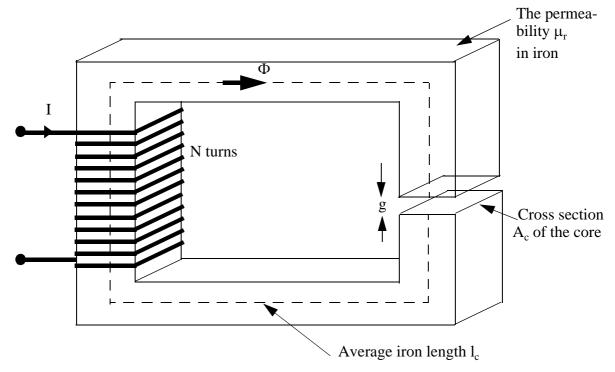

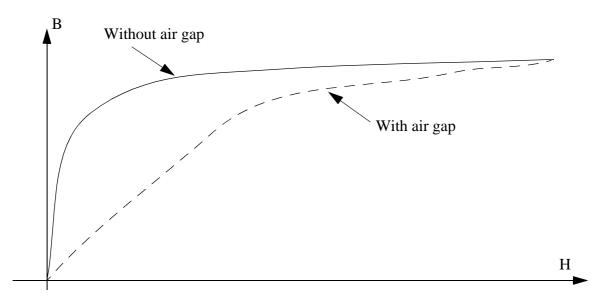

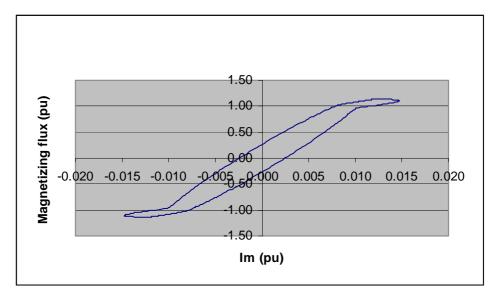

| 3.2   | The magnetizing of a transformer                                                        | 36 |

| 3.2.1 | The B-H curve                                                                           | 36 |

| 3.3   | Resonances on the AC and DC sides of an HVDC converter                                  | 42 |

|       | Parallel resonance                                                                      | 42 |

|       | Series resonance                                                                        | 44 |

| 3.4   | The HVDC control system                                                                 | 46 |

| 3.5   | Core saturation instability                                                             | 46 |

|       | The mechanism of core saturation instability                                            | 47 |

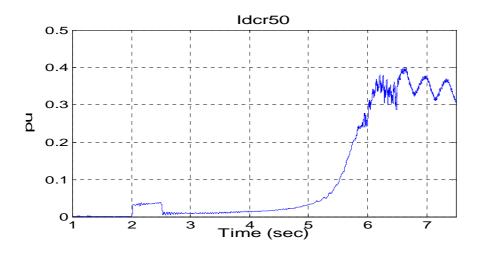

| 3.5.2 | The implications of core saturation instability                                         | 50 |

| 4     | Theory about methods to prevent                                                         |    |

|       | core saturation instability                                                             | 53 |

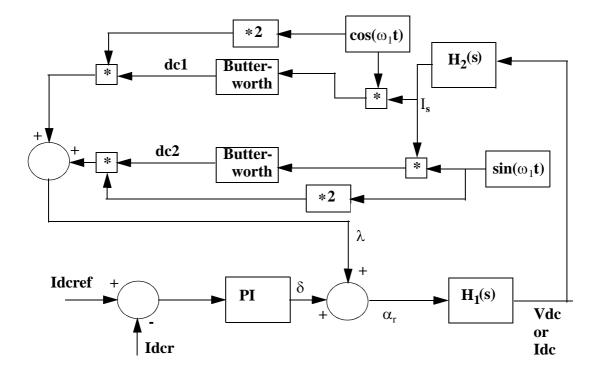

| 4.1   | Stabilizing loop that eliminates the fundamental harmonic in the rectifier's fire angle | 53 |

| 4.2   | Passive and hybrid filtering on the AC side                                             | 59 |

| 4.2.1 | Passive filtering                                                                       | 59 |

| 4.2.2 | Hybrid filtering                                                                        | 59 |

| 4.3   | Using a low magnetizing impedance in the converter transformers                         | 60 |

| 4.3.1 | Theoretical background                                                                  | 60 |

| 4.4   | A blocking LC filter between the low potential converter and earth on the DC side       | 64 |

| 4.5   | Series compensated HVDC converters (CCC HVDC converters)                                | 65 |

| 4.6   | Fire angle modulation based on the DC currents on the secondary side of                 |    |

|       | the converter transformers                                                              | 66 |

|                                                                                   | Simulation tools and models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                                          |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 5.1                                                                               | Converter transformer models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68                                                                          |

| 5.1.1                                                                             | The transformer model with saturation modelled as a current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 68                                                                          |

| 5.1.2                                                                             | The UMEC transformer model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70                                                                          |

| 5.1.3                                                                             | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79                                                                          |

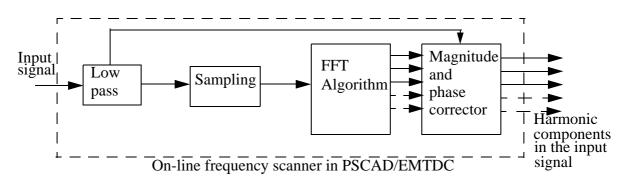

| 5.2                                                                               | The on-line Fast Fourier Transform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80                                                                          |

| 5.2.1                                                                             | The on-line frequency scanner used in PSCAD/EMTDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80                                                                          |

| 5.2.2<br>5.3                                                                      | Conclusions<br>Devue electronic componente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100<br>101                                                                  |

| 5.3.1                                                                             | Power electronic components<br>The thyristor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 101                                                                         |

| 5.3.2                                                                             | The IGBT (or GTO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 101                                                                         |

| 6                                                                                 | Simulation of core saturation instability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 105                                                                         |

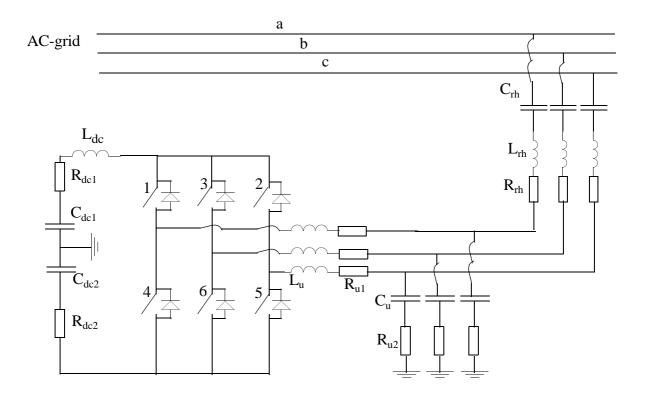

| 6.1                                                                               | The CIGRE HVDC benchmark model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105                                                                         |

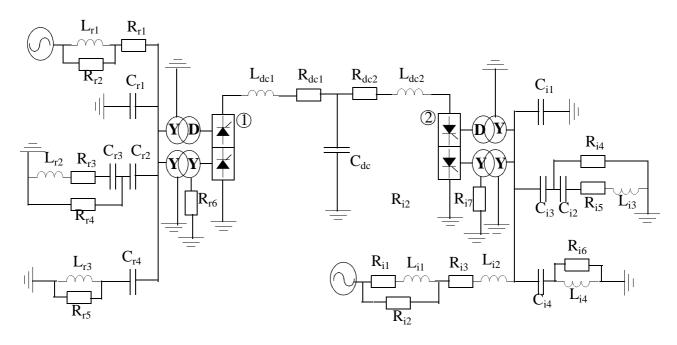

| 6.1.1                                                                             | Electric system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 105                                                                         |

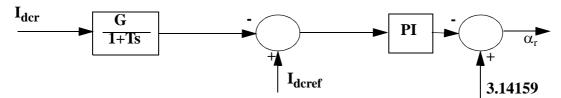

| 6.1.2                                                                             | Rectifier control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 106                                                                         |

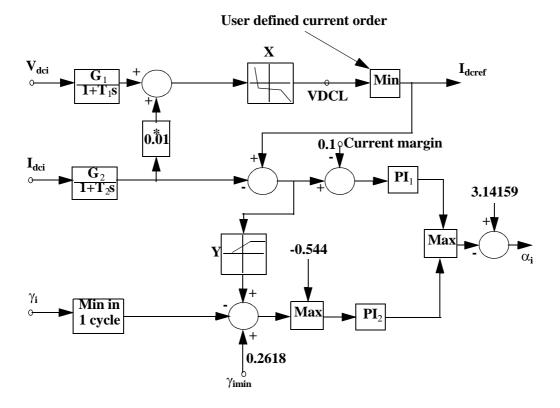

| 6.1.3                                                                             | The inverter control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 106                                                                         |

| 6.1.4                                                                             | Characteristics of the CIGRE HVDC benchmark model and simulation results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 107                                                                         |

| 6.2                                                                               | The modified CIGRE HVDC benchmark model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 112                                                                         |

| 6.2.1                                                                             | Characteristics of the CIGRE HVDC benchmark model and simulation results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 112                                                                         |

| 7                                                                                 | Simulation of methods that prevent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |

| -                                                                                 | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                             |

| -                                                                                 | core saturation instability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 117                                                                         |

| 7.1                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>117</b><br>117                                                           |

| -                                                                                 | core saturation instability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                             |

| 7.1<br>7.2<br>7.3                                                                 | <b>core saturation instability</b><br>A passive filter on the AC side of the rectifier<br>A hybrid shunt filter on the AC side of the rectifier<br>Stabilizing feedback loop from the DC side current of the rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 117<br>121<br>130                                                           |

| 7.1<br>7.2<br>7.3<br>7.3.1                                                        | <b>core saturation instability</b><br>A passive filter on the AC side of the rectifier<br>A hybrid shunt filter on the AC side of the rectifier<br>Stabilizing feedback loop from the DC side current of the rectifier<br>Analog bandpass filter in the stabilizing loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 117<br>121                                                                  |

| 7.1<br>7.2<br>7.3                                                                 | <b>core saturation instability</b><br>A passive filter on the AC side of the rectifier<br>A hybrid shunt filter on the AC side of the rectifier<br>Stabilizing feedback loop from the DC side current of the rectifier<br>Analog bandpass filter in the stabilizing loop<br>Analog bandpass filter combined with a FFT function in the                                                                                                                                                                                                                                                                                                                                                                                                                                    | 117<br>121<br>130<br>130                                                    |

| 7.1<br>7.2<br>7.3<br>7.3.1<br>7.3.2                                               | <b>core saturation instability</b><br>A passive filter on the AC side of the rectifier<br>A hybrid shunt filter on the AC side of the rectifier<br>Stabilizing feedback loop from the DC side current of the rectifier<br>Analog bandpass filter in the stabilizing loop<br>Analog bandpass filter combined with a FFT function in the<br>stabilizing feedback loop                                                                                                                                                                                                                                                                                                                                                                                                       | 117<br>121<br>130<br>130                                                    |

| 7.1<br>7.2<br>7.3<br>7.3.1                                                        | <b>core saturation instability</b><br>A passive filter on the AC side of the rectifier<br>A hybrid shunt filter on the AC side of the rectifier<br>Stabilizing feedback loop from the DC side current of the rectifier<br>Analog bandpass filter in the stabilizing loop<br>Analog bandpass filter combined with a FFT function in the<br>stabilizing feedback loop<br>Analog bandpass filter combined with FFT functions and sinusoidal functions in                                                                                                                                                                                                                                                                                                                     | 117<br>121<br>130<br>130<br>132                                             |

| 7.1<br>7.2<br>7.3<br>7.3.1<br>7.3.2<br>7.3.3                                      | <b>core saturation instability</b><br>A passive filter on the AC side of the rectifier<br>A hybrid shunt filter on the AC side of the rectifier<br>Stabilizing feedback loop from the DC side current of the rectifier<br>Analog bandpass filter in the stabilizing loop<br>Analog bandpass filter combined with a FFT function in the<br>stabilizing feedback loop<br>Analog bandpass filter combined with FFT functions and sinusoidal functions in<br>stabilizing feedback loop                                                                                                                                                                                                                                                                                        | 117<br>121<br>130<br>130                                                    |

| 7.1<br>7.2<br>7.3<br>7.3.1<br>7.3.2                                               | <ul> <li>core saturation instability</li> <li>A passive filter on the AC side of the rectifier</li> <li>A hybrid shunt filter on the AC side of the rectifier</li> <li>Stabilizing feedback loop from the DC side current of the rectifier</li> <li>Analog bandpass filter in the stabilizing loop</li> <li>Analog bandpass filter combined with a FFT function in the</li> <li>stabilizing feedback loop</li> <li>Analog bandpass filter combined with FFT functions and sinusoidal functions in stabilizing feedback loop</li> <li>Analog bandpass filter combined with sinusoidal functions in the</li> </ul>                                                                                                                                                          | 117<br>121<br>130<br>130<br>132<br>the<br>134                               |

| 7.1<br>7.2<br>7.3<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.3                             | <b>core saturation instability</b><br>A passive filter on the AC side of the rectifier<br>A hybrid shunt filter on the AC side of the rectifier<br>Stabilizing feedback loop from the DC side current of the rectifier<br>Analog bandpass filter in the stabilizing loop<br>Analog bandpass filter combined with a FFT function in the<br>stabilizing feedback loop<br>Analog bandpass filter combined with FFT functions and sinusoidal functions in<br>stabilizing feedback loop<br>Analog bandpass filter combined with sinusoidal functions in the<br>stabilizing feedback loop                                                                                                                                                                                       | 117<br>121<br>130<br>130<br>132<br>the<br>134<br>137                        |

| 7.1<br>7.2<br>7.3<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.3<br>7.3.4<br>7.4             | <b>core saturation instability</b><br>A passive filter on the AC side of the rectifier<br>A hybrid shunt filter on the AC side of the rectifier<br>Stabilizing feedback loop from the DC side current of the rectifier<br>Analog bandpass filter in the stabilizing loop<br>Analog bandpass filter combined with a FFT function in the<br>stabilizing feedback loop<br>Analog bandpass filter combined with FFT functions and sinusoidal functions in<br>stabilizing feedback loop<br>Analog bandpass filter combined with sinusoidal functions in the<br>stabilizing feedback loop<br>Analog bandpass filter combined with sinusoidal functions in the<br>stabilizing feedback loop<br>A blocking LC filter between the low potential converter and earth on the DC side | 117<br>121<br>130<br>130<br>132<br>the<br>132<br>134<br>134<br>137<br>e 139 |

| 7.1<br>7.2<br>7.3<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.3                             | <b>core saturation instability</b><br>A passive filter on the AC side of the rectifier<br>A hybrid shunt filter on the AC side of the rectifier<br>Stabilizing feedback loop from the DC side current of the rectifier<br>Analog bandpass filter in the stabilizing loop<br>Analog bandpass filter combined with a FFT function in the<br>stabilizing feedback loop<br>Analog bandpass filter combined with FFT functions and sinusoidal functions in<br>stabilizing feedback loop<br>Analog bandpass filter combined with sinusoidal functions in the<br>stabilizing feedback loop                                                                                                                                                                                       | 117<br>121<br>130<br>130<br>132<br>the<br>134<br>137                        |

| 7.1<br>7.2<br>7.3<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.3<br>7.3.4<br>7.4<br><b>8</b> | <b>core saturation instability</b><br>A passive filter on the AC side of the rectifier<br>A hybrid shunt filter on the AC side of the rectifier<br>Stabilizing feedback loop from the DC side current of the rectifier<br>Analog bandpass filter in the stabilizing loop<br>Analog bandpass filter combined with a FFT function in the<br>stabilizing feedback loop<br>Analog bandpass filter combined with FFT functions and sinusoidal functions in<br>stabilizing feedback loop<br>Analog bandpass filter combined with sinusoidal functions in the<br>stabilizing feedback loop<br>Analog bandpass filter combined with sinusoidal functions in the<br>stabilizing feedback loop<br>A blocking LC filter between the low potential converter and earth on the DC side | 117<br>121<br>130<br>130<br>132<br>the<br>132<br>134<br>134<br>137<br>e 139 |

# **1** Introduction

This thesis focuses on an HVDC-related phenomenon called core saturation instability. The motivation for this is the problems Statnett (the Norwegian transmission system operator) has experienced on the Skagerrak HVDC link. Also internationally, several incidences of core saturation instability have been reported [12, p.180]. The aim of this thesis is to give a simple but detailed description of the phenomenon, and on the basis of this suggest methods that may prevent these occurrences.

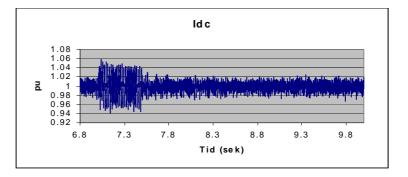

The Skagerrak HVDC link connects the power systems in Denmark and Norway. It consists of three cables and is able to transfer about 1000 MW across the Skagerrak. On 10 August 1993 the Skagerrak HVDC link was disconnected twice. The first time the Kristiansand-Arendal AC line feeding the Norwegian station in Kristiansand failed due to the switching in of a 400 kV shunt reactor in the Danish station Tjele. It was the earth fault protection that tripped the line. As the HVDC link was disconnected transient recorders were started. The recordings showed a 35 A, 50 Hz current superimposed on the DC current flowing across Skagerrak. Later on the day an identical trip occurred but without any relation to any known event. The measured 35 A, 50 Hz current on the DC side and the disconnection because of large zero-sequence currents gives reason to believe that the problems were rooted in a phenomenon experienced in the operation of different HVDC links around the world. This phenomenon is termed core saturation instability [1]. An effort has been made by Statnett to recreate the incidents at the Skagerrak HVDC link 10 August 1993 in the simulation program PSCAD/EMTDC version 2. However, this was not successful.

In this thesis a study of core saturation is performed. To do this it is necessary to have a theoretic understanding of HVDC transmission. This is why Chapter 2 is about theory on HVDC transmission. In Chapter 3 the different factors that interact to create the phenomenon and the implications of it are described theoretically. Methods to decrease the probability of the phenomenon occurring are suggested in Chapter 4.

A simulation program, PSCAD/EMTDC version 3, has been used to simulate core saturation instability and the suggested initiatives to prevent it. Core saturation instability is a phenomenon that requires a strong time domain simulation tool with good models for switches, transformers, and control systems. Chapter 5 focuses on certain models used in PSCAD/EMTDC that are important in order to achieve successful simulation of core saturation instability and the methods that are proposed to prevent it.

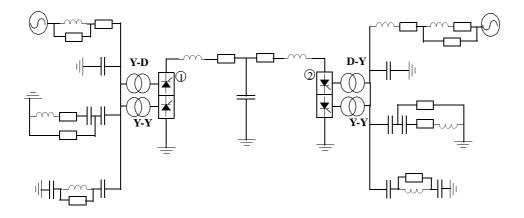

The CIGRE HVDC benchmark model [26] has been used as a starting point for the simulations. It was necessary to make some modifications to this model in order to simulate core saturation instability and initiatives to prevent it. These issues are covered in Chapter 6.

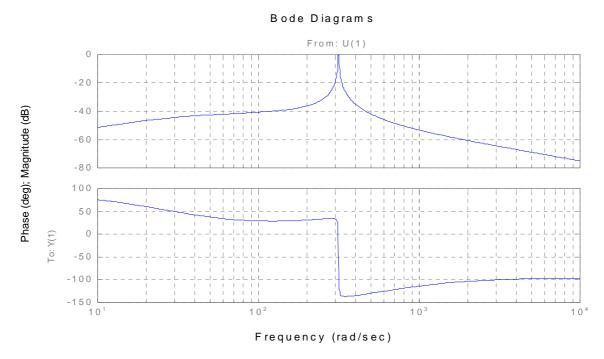

In Chapter 7 it is verified by simulations that the different methods that are suggested in Chapter 4 to prevent core saturation instability really work. The models of the control systems or components used to eliminate core saturation instability are described in detail.

The conclusions of the thesis are in Chapter 8.

The appendices contain data used in the CIGRE HVDC benchmark model, simulation results and a report written for a seminar held by Norsk Elektroteknisk Forening in November 2000.

# 2 Theory about HVDC transmission

This chapter considers how an HVDC transmission is built up, how it works and how it is controlled. To put HVDC transmission into a context, it is also explained why and in which cases it is used.

# 2.1 Advantages of HVDC transmission

Historically the availability of transformers, the advent of the steam turbine as a prime mover for the generation of power, and the development of induction motors have favoured AC transmission [2]. This is why the power systems around the world are mainly AC systems. However, there are cases where HVDC transmission are necessary or preferable. In the following some elements that are positive with HVDC transmission are mentioned.

- 1) In the case of transmitting large amounts of power across large bodies of water it is a necessity to use HVDC transmission. Long AC cables will require too much current to charge their large capacitance. When transferring a DC current in a cable, the capacitance of the cable has no influence on the current.

- 2) When transferring DC the lines require no reactive compensation. However, when transferring AC there is a need for series or shunt compensation to reduce the voltage drops and line losses.

- 3) When transferring DC there are no skin effects in the lines. Thus, the use of the conductor cross section is better than when transferring AC. The earth impedance is also low for DC.

- 4) HVDC transmission can make connection between power systems that are not synchronized or operate at different frequencies possible.

- 5) The fast control of HVDC links makes it possible to use an HVDC link to improve the stability in the interconnected AC systems.

- 6) AC interconnections always reduce the overall system impedance and in this way cause an increase in the short circuit levels. The capability of existing circuit breakers may be exceeded. This is avoided with an HVDC interconnection.

- 7) The DC voltage on the DC line is the effective voltage. For AC lines the effective voltage is  $1/\sqrt{2}$  times the peak AC voltage. Thus, more DC power can be transmitted if the AC line and DC line have the same insulation level.

- 8) Less conductors are required in DC transmission than in AC transmission.

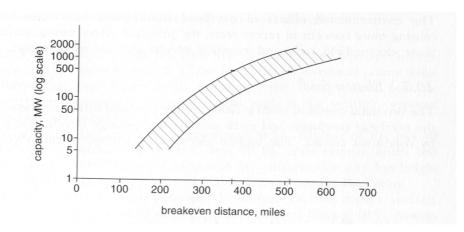

The negative aspect of using HVDC transmission is the high cost of the converter stations. However, DC lines are less expensive to build than AC lines (see points 3 and 8 above). Therefore there will be a break-even distance where the cost of building AC transmission is equal to the cost of building DC transmission. Figure 2.1 shows the relation between the transferred power and the break-even distance.

Figure 2.1 Break-even distance for HVDC transmission and AC transmission [2]

One can conclude from Figure 2.1 that HVDC lines are favourable to use when the distance between the produced electricity and the load centre are very far. There are several examples of HVDC links being used to feed load centres from distant generators. In India for instance, an HVDC link is used to transfer bulk power from Rihand-Singrauli thermal power generating complex to the load centre around Delhi [2,p.93]. The nominal power is 1500 MW and it is transferred over a distance of 814 km at  $\pm$ 500 kV.

If one or more submarine or underground cables are used for the transmission, the break-even distance is much less than when overhead lines are used. AC cable systems that are longer than 50 km are not practical to consider, while DC cable systems might be used for distances of more than 600 km [3]. Therefore, in the cases where the only alternative is to transport the power in long cables, HVDC transmission must be used. An example of an HVDC link using submarine cables is the Skagerrak link between Norway and Denmark. The Skagerrak link has three converter stations that provide up to 1000 MW. The three submarine cables are about 130 km.

HVDC is the obvious option if it is desirable to connect power systems with different frequencies or power systems which are not synchronized. The Sakuma interconnection in Japan connects a 50 Hz and a 60 Hz power system. It is a back-to-back interconnection that interchange up to 300 MW at  $\pm 125$  kV. The intention of the link was to improve the stability in the power systems and to transfer power between the systems [2].

## 2.2 Principles of HVDC transmission

The aim of this section is to give an basic understanding of how an HVDC link operates. Topics which are considered are:

- Rectifier operation

- Inverter operation

- Control systems

- Harmonics

- Filtering

### 2.2.1 Typical HVDC schemes

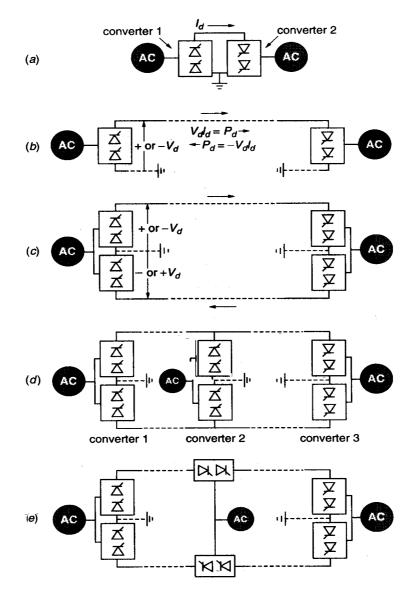

Figure 2.2 Basic HVDC transmission configuration [2].

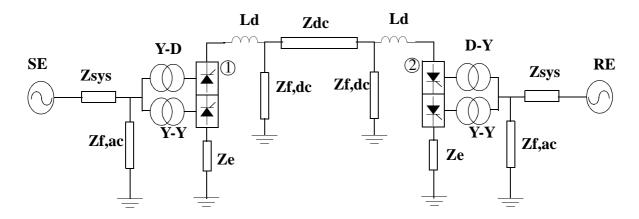

Figure 2.2 a) shows the back-to-back interconnection. The two twelve-pulse thyristor converters are built on the same site and there are no transmission lines between them. The back-to-back interconnection may be used to interconnect AC grids with different frequencies.

The monopolar link in Figure 2.2 b) consists of two twelve-pulse thyristor converters which are joined by a single conductor line. The earth or the sea is used as the return conductor. This requires two electrodes that are able to carry the full current in the HVDC link. In this thesis the simulations and studies are done on a monopolar link. This saves time when simulating (simulating on a more complex system like a bipolar link would have required longer simulation time) and is sufficient to make a study of core saturation instability and methods to prevent it.

Figure 2.2 c) shows the bipolar link. The bipolar link consists of two monopolar link combined such that one has positive and the other negative polarity with respect to earth. When the two monopolar systems have equal current they cancel each other's earth currents to zero. Thus, the earth conductor is only used when one pole is temporarily out of service.

Figure 2.2 d) and e) shows two cases of multiterminal HVDC transmission. If converter 1 and 2 in Figure 2.2 d) operate as rectifiers, then converter 3 must be operated as an inverter. The opposite of this is also the case. Mechanical switches are necessary to achieve other rectifier-inverter combination. The series connection in Figure 2.2 e) makes it possible to tap a smaller amount of the total line power without building the high cost parallel tapping alternative.

### 2.2.2 Converter operation

Since the models used for simulation of HVDC transmission in this thesis consists of thyristor converters, only this type of converter is analysed. Rectifiers/inverters using GTO/IGBT are under development. Schemes using force commutated switches and with rated power up to 300 MW are being built [4].

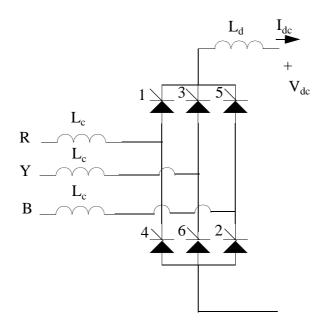

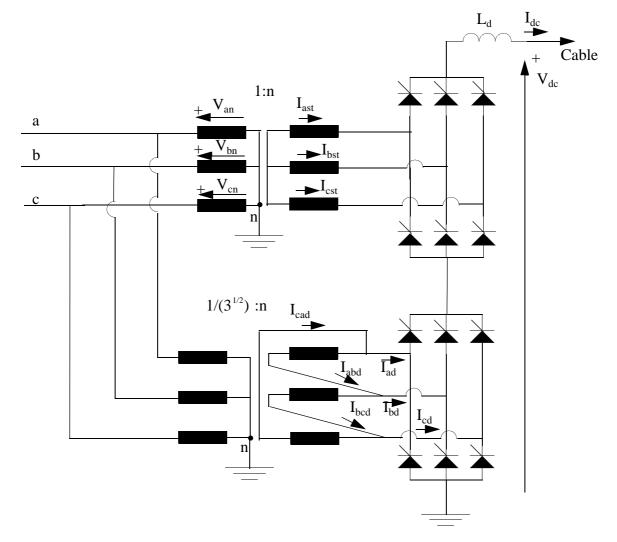

A 6-pulse thyristor converter is shown in Figure 2.3

Figure 2.3 Three-phase thyristor converter

#### The firing angle is zero

To understand the three-phase bridge it is an advantage to start with the ideal case where the bridge is connected to an infinitely strong power system, and diode operation of the bridge. It is also assumed that  $L_d$  is very large, so that it is justified that the DC current is constant. Under these conditions the commutation is instantaneous. Figure 2.4 shows the switching sequence and the rectified voltage waveform.

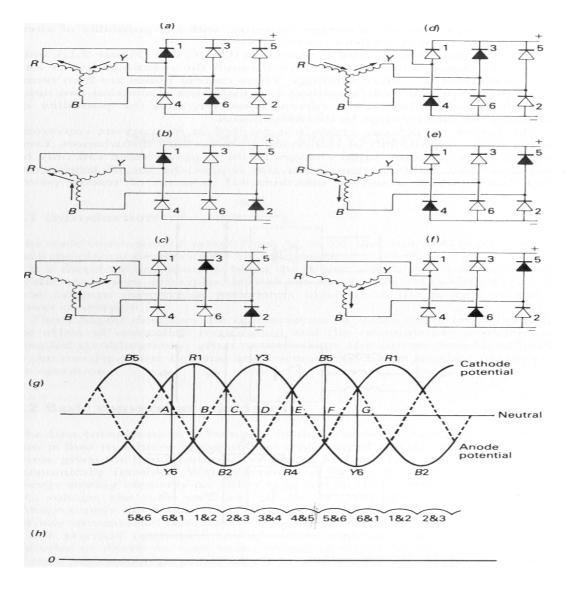

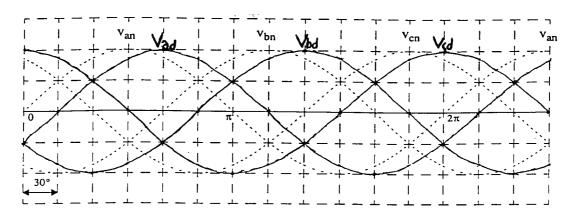

Figure 2.4 Conducting sequence of the bridge and DC voltage waveforms [2]

From Figure 2.4 it can be seen that after instant A, valves 1 and 6 will conduct and a current will flow in phase R and phase Y. At point B valve 2 becomes forward-biased, and the current  $I_{dc}$  commutates from valve 6 to valve 2. Every 60<sup>0</sup> a new valve becomes forward biased and the current  $I_{dc}$  commutates to this valve. Table 2.1 below shows which valves that conduct between the commutation instants.

**Table 2.1 Conducting sequence**

| Time is between instant   | A & B | B & C | C & D | D & E | E & F | F & G | G & H |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|

| The conducting valves are | 6 & 1 | 1 & 2 | 2 & 3 | 3 & 4 | 4 & 5 | 5&6   | 6&1   |

It is clear from Table 2.1 that each valve carries the current  $I_{dc}$  for one third of a fundamental cycle of the applied voltages on the AC side.

The output voltage  $V_o$  (i.e. the voltage of the positive pole with respect to the negative pole) waveform on the DC side of the rectifier is shown in Figure 2.4 h).  $V_o$  has a harmonic frequency of six times the main frequency

#### The firing angle is larger than zero

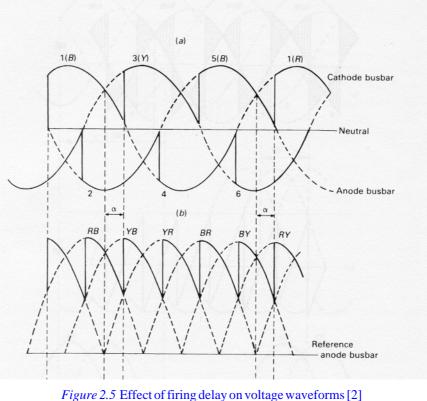

*Figure 2.5* Effect of firing delay on voltage waveforms [2] a) Common-anode and common-cathode voltages b) Direct voltage

It is seen from Figure 2.5 that the mean of  $V_o$  is reduced because of the contribution from the firing angle  $\alpha$  compared with the case where  $\alpha=0^0$  (See Figure 2.4). The following analyses how  $V_o$  changes as  $\alpha$  changes:

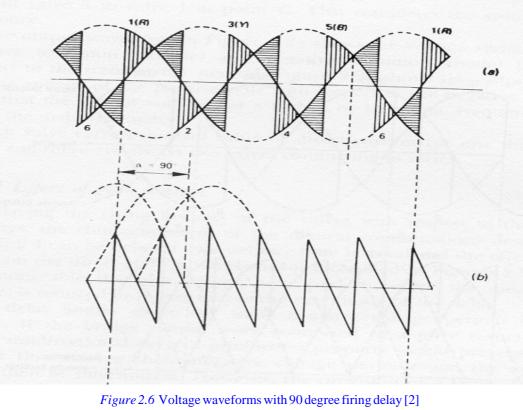

When  $\alpha$  increases the mean value of V<sub>o</sub> decreases. If  $60^{\circ} < \alpha < 90^{\circ}$  the instantaneous value of V<sub>o</sub> in some periods becomes negative. If the DC side was connected to a pure resistive load, the unidirectional current conduction properties of the valves would prevent reverse current flow during these negative periods, and the operation of the bridge would have been intermittent. However, the large smoothing reactor maintains positive current flow during the negative periods of V<sub>o</sub>. This means that when V<sub>o</sub> is negative, power is transferred from the DC side to the AC side. If  $\alpha$ =90<sup>o</sup> the negative cycle of V<sub>o</sub> equals the positive cycle of V<sub>o</sub>, and the mean value of V<sub>o</sub> becomes zero (see Figure 2.6). This means that no energy is transferred from the AC side to the DC side or from the DC side to the AC side during a period of V<sub>o</sub>. If  $\alpha$ >90<sup>o</sup> the mean value of V<sub>o</sub> becomes negative and thus the average power (the active power) is transferred from the DC side to the AC side to the AC side. The converter therefore acts as an inverter when  $\alpha$ >90<sup>o</sup>.

*igure 2.6* Voltage waveforms with 90 degree firing delay [2] a) Common-anode and common-cathode voltages. b) Direct voltage V<sub>0</sub>.

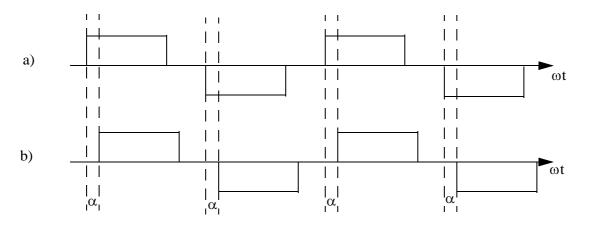

It is important to notice that even though there is a change in the direct voltage waveform due to the firing delay, the current waveform in each phase on the AC side of the converter is still the same as it was without the firing delay. The only difference between the currents in these modes is that they are shifted by the fire angle. This is illustrated in Figure 2.7.

When  $\alpha = 180^{\circ}$  full inversion is achieved, and V<sub>o</sub> will be at the same size but with opposite sign than when  $\alpha = 0^{\circ}$ .

#### The real commutation process

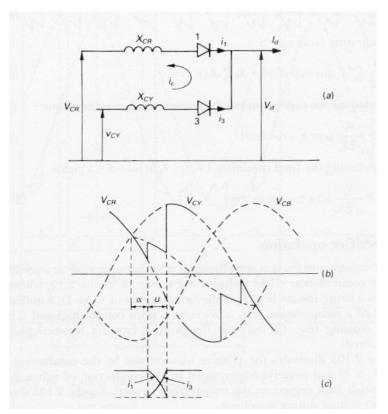

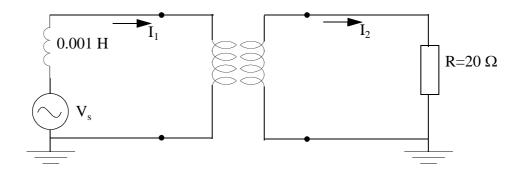

Because of the AC network inductance and the leakage reactance of the converter transformers, the commutation between the valves in the converter is not instantaneous. The commutation process between two valves is shown below in Figure 2.8.

The mathematical expressions of the DC side current  $I_d$  and the mean DC side voltage  $V_d$  are derived in the following.

Using Figure 2.8, the commutation current  $i_c$  is derived:

Uses:

$$X_{C} = X_{CR} = X_{CY}, i_{c} = i_{3} - i_{1}, v_{CY} - v_{CR} = 2 \left(\frac{X_{C}}{\omega}\right) \frac{di_{c}}{dt} = \sqrt{2} V_{C} \sin \omega t$$

(2.1)

$X_C$ ,  $X_{CR}$ , and  $X_{CY}$  are the commutation reactances.  $v_{CY}$ , and  $v_{CR}$  are phase voltages in phase Y and phase R respectively.  $V_C$  is the rms value of the line voltage in the AC network.

From the relations above the instantaneous value of the commutation current can be derived to be:

$$i_c = \frac{V_C}{\sqrt{2}X_C} (\cos\alpha - \cos\omega t)$$

(2.2)

When the commutation is done,  $i_c$  equals the DC current  $I_d$  of the converter. Thus,  $I_d$  can be expressed as:

$$I_d = \frac{V_C}{\sqrt{2}X_C} (\cos\alpha - \cos(\alpha + u))$$

(2.3)

u is the commutation angle.

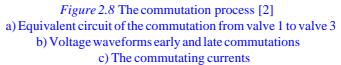

The mean direct voltage  $V_d$  is found using Figure 2.9:

Figure 2.9 Typical six-pulse rectifier operation [2] a) Positive and negative direct voltages with respect to the transformer neutral b) Direct bridge voltage V<sub>d</sub> and voltage across valve 1 c), d) Valve currents i<sub>1</sub> to i<sub>6</sub> e) AC line current of phase R

Suppose the time is zero at the crossing point C1 in Figure 2.9. The direct voltage as a function of time  $V_{dt}$  is expressed in the following way for the next  $120^{0}$  (this is derived from Figure 2.9 a) and b)):

$$V_{dt} = \sqrt{2} V_c \cos\left(\omega t + \frac{\pi}{6}\right) \quad \text{for } 0 < \omega t < \alpha \tag{2.4}$$

$$V_{dt} = \sqrt{2}V_c \cdot \cos\left(\omega t + \frac{\pi}{6}\right) + \frac{1}{2} \cdot \sqrt{2}V_c \sin\omega t = \frac{\sqrt{6}}{2}V_c \cos\omega t , \alpha < \omega t < \alpha + u$$

(2.5)

$$V_{dt} = \sqrt{2}V_c \cos\left(\omega t - \frac{\pi}{6}\right) \text{ for } \alpha + u < \omega t < \frac{\pi}{3}$$

(2.6)

The mean DC side voltage  $V_d$  is given by:

$$V_{d} = \frac{1}{\pi/3} \int_{0}^{\pi/3} V_{dt} d\omega t$$

(2.7)

If Equations (2.4), (2.5), and (2.6) are inserted in Equation (2.7) and the integral in Equation (2.7) is calculated the result becomes:

$$V_d = \frac{3\sqrt{2}}{2\pi} V_c [\cos(\alpha + u) + \cos\alpha]$$

(2.8)

The value of the commutation angle is often unknown and must be estimated. Thus it is preferable to express  $V_d$  as a function of  $I_d$  which is easy to measure directly. By combining information in Equations (2.3) and (2.8),  $V_d$  can be expressed by  $I_d$ :

$$V_d = V_{do} \cos \alpha - \frac{3X_C}{\pi} I_d \quad \text{where} \quad V_{do} = \frac{3\sqrt{2}}{\pi} V_c \tag{2.9}$$

Equations (2.8) and (2.9) are also valid for inverter mode. If  $V_d$  is expressed by the extinction angle the following expressions are found:

$$V_d = V_{\rm do} \cos\gamma - \frac{3X_C}{\pi} I_d \tag{2.10}$$

$$V_d = V_{do}[\cos(\gamma + u) + \cos\gamma]$$

(2.11)

In practice  $\alpha$  is more than 5<sup>0</sup> to secure successful turn on of the valves. If  $\alpha$  is too small, a voltage distortion could cause the voltage across the incoming valve to be lower than the voltage across the valve that is already conducting in the moment the control system gives the firing pulse. The result would be that the attempt to turn on the valve failed. Also  $\gamma$  has an lower limit. Usually it is required that  $\gamma$  is greater than 15<sup>0</sup> because of the uncertainty in the commutation angle. If, for

instance,  $\gamma$  is small and the commutation angle is varying (for instance due to variation in the AC side voltage of the inverter) a valve could suddenly fail to turn off and the valve would conduct its rated current for a longer time than it is designed for. This could damage the valve and increase the harmonic content in currents and voltages both on the DC side and AC side. By increasing  $\gamma$ , this is in many cases avoided.

#### **Power Factor**

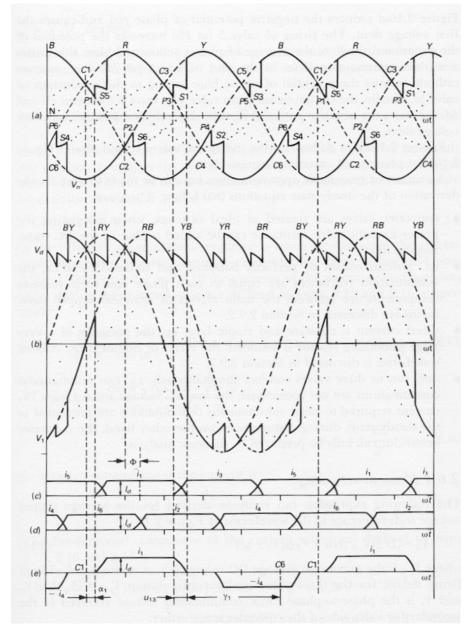

Both in rectifier mode and inverter mode the current in each phase lags the phase voltage. This is illustrated in Figure 2.10 below.

Figure 2.10 Phasor diagrams of current and power [2]. Suffix R for rectification and I for inversion.

From Figure 2.10 it can be seen that both the rectifier mode and the inverter mode consume reactive power. It is desirable to minimize the consumption of reactive power because this has a positive influence due to losses, and compensation. It can be shown that the extinction angle for inverter mode, and the firing angle for rectifier mode should be as small as possible to obtain the optimal power factor. This is done below with the assumptions of perfect filtering (no harmonic currents are injected into the AC network), and losses neglected in the converter.

The active power P is the same on the AC side as the DC side:

$$P = \sqrt{3}V_c I \cos\varphi = V_d I_d \tag{2.12}$$

The power factor  $\cos \phi$  is thus:

$$\cos\phi = \frac{V_d I_d}{\sqrt{3} V_c I} \tag{2.13}$$

The fundamental component in the AC current I can be found by Fourier analysis. It turns out that:

$$I = \frac{\sqrt{6}}{\pi} I_d \tag{2.14}$$

By using expressions for  $V_d$ ,  $I_d$  in Equation (2.13) the power factor can be approximated to:

$$\cos\varphi = \frac{\cos(\alpha) + \cos(\alpha + u)}{2} = -\frac{\cos(\gamma) + \cos(\gamma + u)}{2}$$

(2.15)

In rectifier mode  $\cos\varphi$  is closest to one when  $\alpha$  is at its minimum, and in inverter mode  $\cos\varphi$  is closest to minus one when  $\gamma$  is at its minimum.

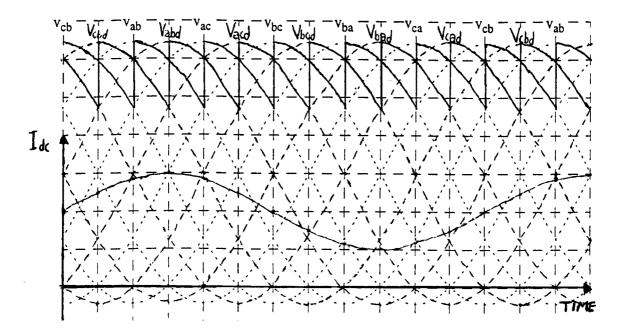

### 2.2.3 Harmonics

Harmonics are defined as sinusoidal components of a repetitive waveform which consists exclusively of frequencies that are exact multiples of the fundamental frequency [2]. The full set of harmonics gives a Fourier series which completely represents the original waveform. As seen from the waveform of the current per phase the converters in an HVDC link delivers to the AC grid (Figure 2.9 e)) it is clear that it is not sinusoidal but it has the same period time as the AC voltage. Figure 2.4 h) shows that DC side voltage of a six-pulse converter is repetitive with a certain frequency. Therefore, these signals can be represented by Fourier series. A comprehensive presentation of theory on Fourier series can be found in [5].

Harmonic components of currents and voltages may cause extra losses, overheating, and interference with nearby electronic systems [30]. In the case of resonances in the grid, even small harmonic components may cause serious problems. It is therefore very important to represent currents and voltages by Fourier series and find ways to filter the harmonics. In this section harmonics from a typical HVDC scheme is considered.

Much of the theory in this section is based on [6].

#### Harmonics due to HVDC converters

Mainly, HVDC converters generate harmonic voltages on the DC side and harmonic currents on the AC side. The harmonics generated are usually separated in two parts, termed characteristic harmonics and non-characteristic harmonics. The twelve-pulse converter is the most common in HVDC systems and therefore the harmonics due to this converter are the focus in this section.

#### **Characteristic harmonics**

The characteristic harmonics are the harmonics related to the pulse number of the converter configuration. They are derived on the following assumptions:

(a) The AC side voltages of the converter are displaced exactly one third of a period in time and consist only of the fundamental frequency.

- (b) The DC drossel has infinite inductance, and therefore the DC current is smooth and constant.

- (c) The time interval between each firing instant is constant and corresponds to the numbers of

valves in the converter.

(d) The commutation impedances are the same in the three phases.

With these assumptions a converter configuration with p valves generates voltage harmonics of orders pk on the DC side, and current harmonics of orders  $pk \pm 1$  on the AC side (k is an integer).

#### Non-characteristic harmonics

The non-characteristic harmonics are the harmonics related to the non-ideal conditions when operating the HVDC converters. In practice these must be considered when choosing the different components (filters, protection, valves etc.) in an HVDC system. The orders of the non-characteristic harmonics are those not covered by the orders of the characteristic harmonics. Non-characteristic harmonics are caused by:

- (a) Firing errors

- (b) Asymmetrical AC voltages

(c) DC current modulation. (The harmonics on the AC side and the DC side are mutually connected. Consequently a small error which causes non-characteristic harmonics on the DC side causes non-characteristic harmonics on the AC side)

(d) Unequal commutation reactances in the phases on the AC side

#### Harmonics transferred from the AC side to the DC side of a twelve-pulse converter

There is a general relationship between the harmonics on the AC side and the DC side of a twelve-pulse HVDC bridge. If a positive-sequence harmonic multiple k+1, or a negative-sequence harmonic multiple k-1 appears in the otherwise perfectly symmetrical commutation voltages on the AC side of the 12 pulse HVDC bridge then the frequency  $f_{DCk}$  of the harmonic voltages which appears on the DC side can be written as:

$$f_{DCk} = (12n \pm k)f_0 \tag{2.16}$$

$f_0$  is the fundamental frequency of the commutation voltages.

$n \in (0, 1, 2, 3, \dots)$

Equation (2.16) is valid also for inter- and sub-harmonics (i.e. when k is not an integer)

The magnitude of the DC voltage with harmonic multitude k is switched across the converter in the same ratio as the fundamental voltage is, except that the fire angle delay does not reduce the magnitude of the DC harmonic voltage but merely phase shifts this voltage. Nevertheless, there might be a modification of the DC side harmonic level by up to ten per cent and also a phase shift up to 0.3 radians. This is due to that the AC voltage distortion is affecting the commutation period. By direct transfer the higher order DC voltage non-characteristic harmonics (the

harmonics when  $n \ge 1$  in Equation (2.16)) are approximately reduced by a factor 1/(12n) compared to the non-characteristic harmonic corresponding to n=0 in Equation (2.16), if the switching instants remains unaffected by the distortion. However, also these harmonics in the DC voltage may be modified. The spectrum which appears as a result of commutation variation does not reduce nearly as quickly as a factor of 1/(12n). Thus, for DC side harmonic voltages of order  $12\pm k$ , the commutation-period variation is contributing substantially (maybe 50 %). The contribution from the commutation period variation becomes a more and more important factor in the DC side harmonic voltages as the frequency increases. Because of this, the level of the higher order DC side voltage harmonics can be substantially different reduced than by a factor of 1/(12n).

From Equation (2.16) it is clear that if k=0 than the DC side harmonics will have the frequency:

$$f_{DCk} = 12nf_0 \tag{2.17}$$

These are the characteristic harmonics on the DC side. They are the only harmonics present when the twelve-pulse bridge are operated under idealized conditions. The higher order harmonics in the DC side voltage will under idealized conditions be reduced compared to the DC component. The relationship on how they get reduced as a function of the frequency is given by a quite complex formula ([6], p.25). This formula also depends on the commutation angle, the fire angle, and the maximum averaged rectified voltage.

#### Harmonics transferred from the DC side to the AC side of a twelve-pulse converter

If a harmonic current source which generates a harmonic current with harmonic multiple k exists on the DC side of the twelve-pulse bridge under otherwise idealized operation of the bridge, then the frequencies  $f_{ack+}$  and  $f_{ack-}$  of the generated harmonic currents on the AC side can be expressed as in the following:

$$f_{ack+} = ((12n+1) \pm k) \cdot f_0 \tag{2.18}$$

$$f_{ack-} = ((12n-1) \pm k) \cdot f_0 \tag{2.19}$$

Equations (2.18) and (2.19) are also valid for inter- and sub-harmonics (i.e. when k is not an integer).

If the DC component of the DC side current is 2 kA and the fundamental component of the AC side current is 2.5 kA, then the harmonic currents of harmonic multiple k+1 and k-1 generated on the AC side, will have magnitude equal to  $0.5 \cdot \frac{2.5}{2}$  times the harmonic current of harmonic

multiple k on the DC side. However, the DC current distortion is affecting the commutation period. Therefore the level of the AC side harmonic currents might be modified up to 15 % and their phase angle can be modified up to 0.2 radians.

If the switching instants remain unaffected by the distortion, the higher order non-characteristic AC side harmonics (the harmonics corresponding to  $n \ge 1$  in Equations (2.18) and (2.19)) are reduced by a factor approximately  $1/(12n \pm 1)$  compared to the non characteristic harmonics corresponding to n=0 in Equations (2.18) and (2.19). However, these harmonics are influenced by the effect of the DC current distortion on the commutation period. The spectrum caused by

the variation in the commutation period reduces more quickly than that for the DC voltage (see the section above on harmonics transferred from the AC side to the DC side), but not as quickly as the characteristic harmonics. Thus, the commutation period variation is contributing substantially to the AC side harmonic currents of order  $(12n+1)\pm k$  and  $(12n-1)\pm k$ . The contribution from the commutation period variation becomes a more and more important factor in the AC side harmonic currents as the frequency increases.

If k=0 in Equations (2.18) and (2.19) then:

$$f_{ack+} = (12n+1) \cdot f_0 \tag{2.20}$$

$$f_{ack-} = (12n-1) \cdot f_0 \tag{2.21}$$

The harmonics on the AC side with frequencies given by Equations (2.20) and (2.21) are the characteristic harmonics on the AC side. They are the only harmonics present on the AC side under idealized conditions.

#### Harmonics in a twelve-pulse converter due to switching instant variation

Assume there is a sinusoidal variation with harmonic order k in the fire angle order to an HVDC converter and otherwise idealized conditions. Then there will be generated harmonic DC voltages with frequencies given by:

$$f_{DCk} = (12n \pm k)f_0 \tag{2.22}$$

Equation (2.22) is also valid when k is not an integer.

This will cause positive- and negative-sequence harmonics in the AC side current. The frequencies of these currents are given by:

$$f_{ack+} = ((12n+1) \pm k)f_0 \tag{2.23}$$

$$f_{ack-} = ((12n-1) \pm k)f_0 \tag{2.24}$$

The generated harmonics diminishes with increasing frequency as explained in earlier in this section.

#### Effects on the harmonics due to non-ideal conditions

Non-characteristic harmonics will always be present in a real HVDC scheme. In the following effects of different causes to the non-characteristic harmonics are evaluated.

a) Effects of firing errors:

Consider the ideal  $120^{\circ}$  rectangular pulse in Figure 2.7. This is the pulse of one of the phase currents in a AC line which is connected to a six-pulse thyristor bridge via a star-star connected transformer. The commutation angle is neglected. If one of the valves in the bridge somehow fails to fire at the instant it is meant to fire but have an extra delay of for instance  $2^{\circ}$  before firing

one of the pulses in the per phase currents will not last for  $120^{0}$  but only for  $118^{0}$ . Because of this the phase current not can be written as a function f(t) where f(t) = -f(t+T/2). This means that the phase current will also contain elements of even harmonics and triple harmonics.

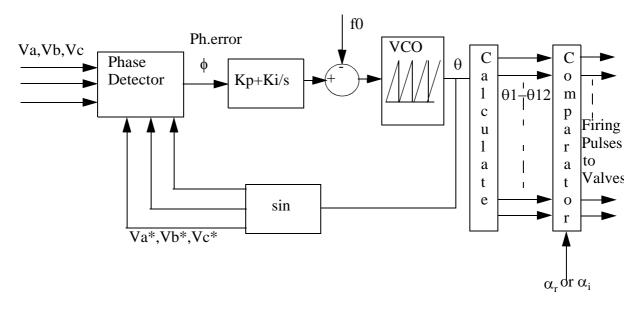

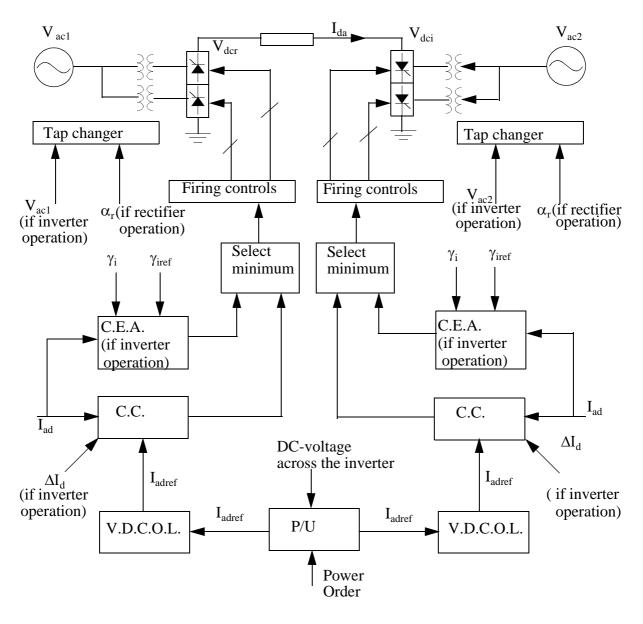

In a twelve-pulse HVDC converter, firing errors in a similar way as just described may destroy the half-wave symmetry of the phase currents and thus create even and triple harmonic phase currents. To include the commutation angle in the consideration above is not likely to change this statement. In modern HVDC control systems, the effect of distorted commutation voltages on the fire angle is almost eliminated because of the phase-locked loop (see Figure 2.24) used to find the right firing instances.

b) Effects of distorted and/or asymmetric AC voltages:

Distorted AC voltages can create harmonics due to firing errors. As mentioned earlier, the phase-locked loop in the firing controllers in modern HVDC links have minimized this problem.

A problem which the firing controllers not are able to deal with is unbalanced amplitudes on the AC voltages. For instance, if the AC voltage in one of the phases has a considerably lower amplitude than the AC voltages in two of the other phases, the DC voltage will get a second harmonic component which will cause a second harmonic current on the DC side. Due to coupling between the harmonics in the DC current and in the AC currents, the AC currents will get a third harmonic component in the positive-sequence and a fundamental harmonic component in the negative-sequence. With unfavourable impedances in the AC and DC grid this might cause a problem.

c) Effect of direct current modulation:

Even though the AC voltages are perfectly balanced and the firing errors are eliminated through the firing controllers, non-characteristic components in the AC currents may exist. This is due to the coupling between the harmonic components in the DC current and in the AC currents. For example, if for some reason a low order harmonic component in the DC current of order n is generated, this component will be mirrored to the AC side current as harmonic components of orders n+1 in the positive system and n-1 in the negative system.

d) Effect of asymmetric commutation reactances:

The effect of unequal commutation reactances are odd non-characteristic AC harmonic currents, and even non-characteristic DC harmonic voltages. The size of these depend on the mean of the commutation reactances, the differences in the commutation reactances, the firing angle, and the overlap angle.

#### **Harmonic filters**

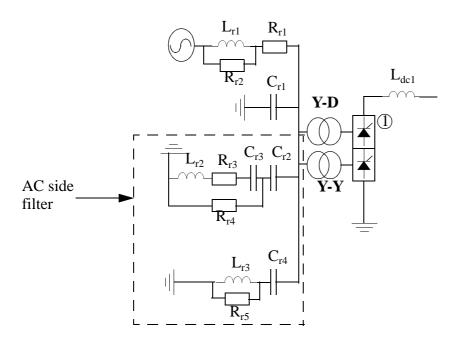

Figure 2.11 shows an example of an HVDC converter and its filters (there are only filters on the AC side in this figure).

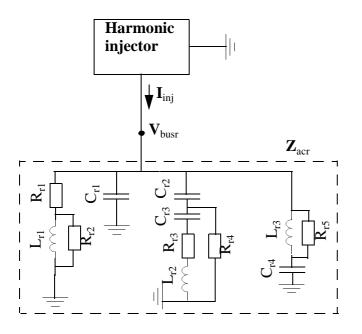

Figure 2.11 Example of an HVDC converter and its filters.

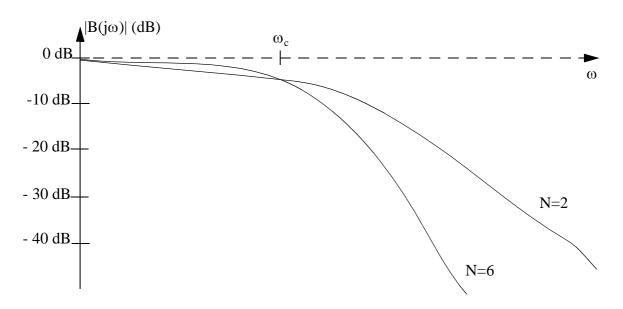

As stated earlier, harmonics may cause extra losses, overheating, and interference with nearby electronic systems. There may also be equipment that is sensitive and should be protected from harmonics. Harmonic filters limit or eliminate the damage harmonic currents or voltages can cause. The idea with harmonic filters is to create a low impedance path to earth for the harmonic currents. In this way they will be prevented from flowing into the AC or DC grid. In addition the AC side filters of an HVDC transmission often have a secondary function. This is to provide reactive power to the HVDC converter [2]. Figure 2.12 shows typical filter configurations and impedance characteristics of filters used in HVDC transmission.

| TYPE                      | CIRCUIT                                                                                                                                                      | Z VS FREQUENCY |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

| INGLE TUNED               |                                                                                                                                                              | R<br>f,h       |  |  |

| OUBLE TUNED               | $C_{2} = C_{1}$ $C_{3}$                                      |                |  |  |

| SECOND ORDER<br>HIGH PASS |                                                                                                                                                              |                |  |  |

| HIGH PASS<br>'C' TYPE     | $ \begin{array}{c} C_{1} \stackrel{\circ}{\xrightarrow{1}}\\ L \stackrel{\circ}{\xrightarrow{1}}\\ C_{2} \stackrel{\circ}{\xrightarrow{1}}\\ \end{array} R $ |                |  |  |

Figure 2.12 Configurations and impedance characteristics of typical filters for HVDC links [7].

The single tuned filter is designed to filter out characteristic harmonics of a single frequency. For instance, when filtering harmonics from a twelve-pulse bridge the single tuned filter may be used to filter out the twelfth harmonic on the DC side.

The double tuned filter is used to filter out two specific frequencies. Reference [7] claims that the double tuned filter has less power loss at the fundamental frequency than two single tuned filters. In addition only one inductor will be subject to full line impulse voltage. The double tuned filter may be used to filter out the eleventh and thirteenth harmonics from a twelve-pulse bridge.

The second order high pass and high pass 'C' type filters are both used to filter out higher harmonics. The 'C' type filter has less loss at fundamental frequency than the second order high pass filter [7].

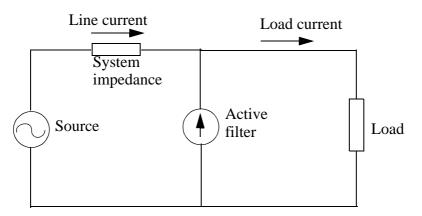

The development of power electronic components gives new possibilities in the filtering of

harmonics [8]. An example of this is an active shunt filter [9]. An active shunt filter is a device that actively generate harmonic components of the load current and this way prevent these components to flow in the AC grid. Figure 2.13 shows a simplified circuit diagram of an active shunt filter.

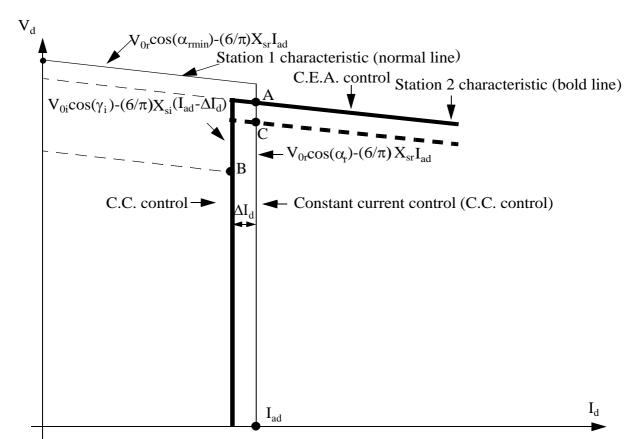

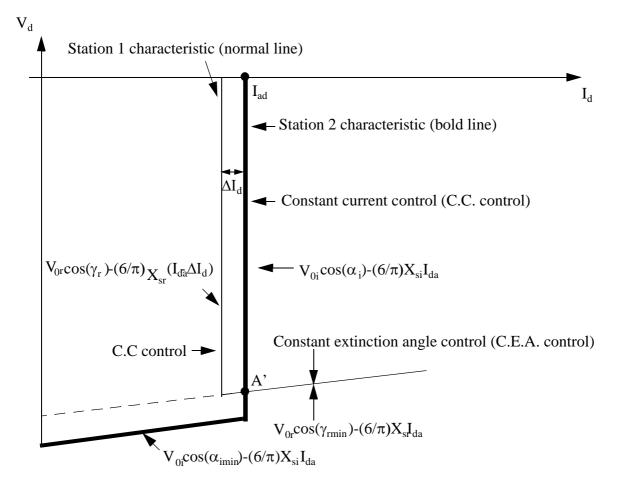

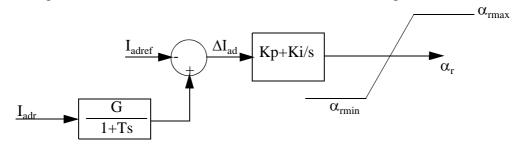

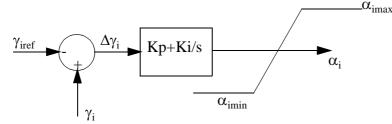

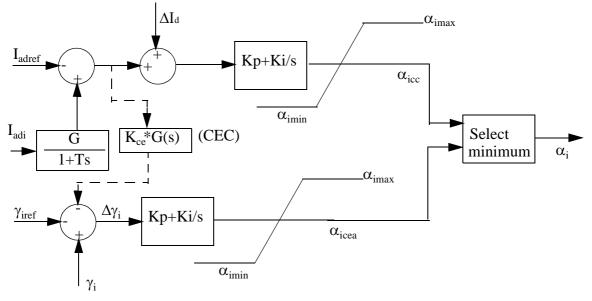

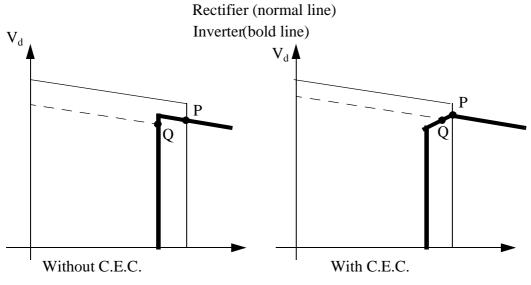

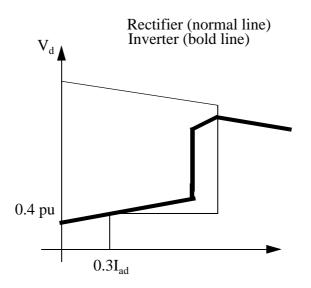

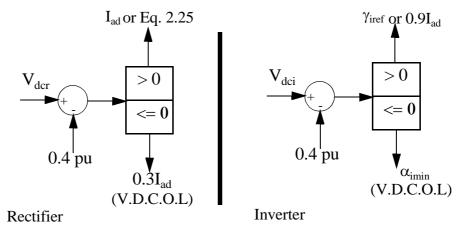

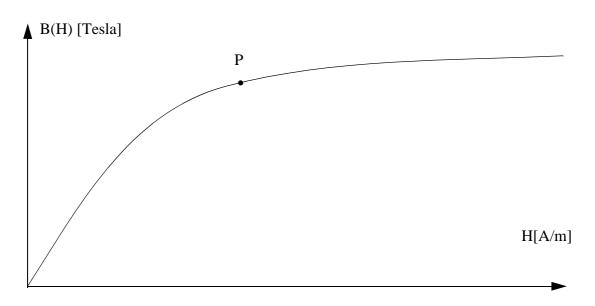

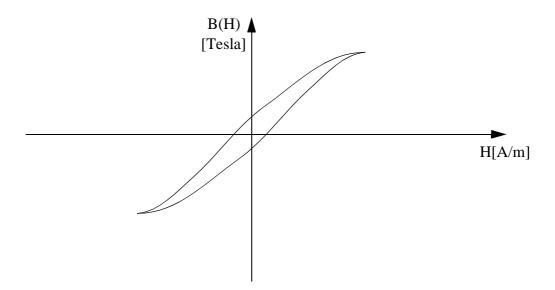

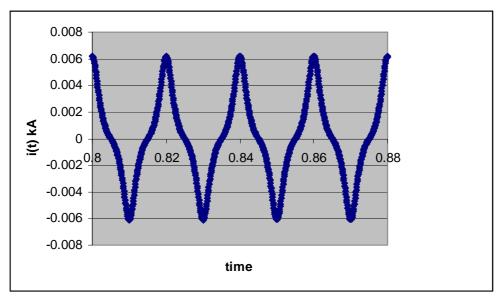

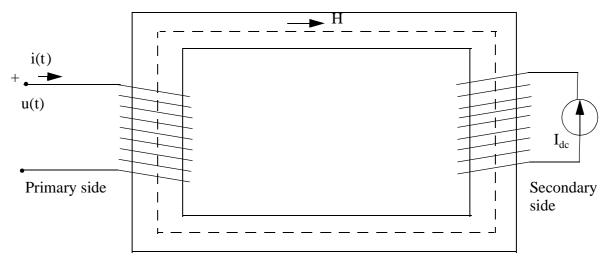

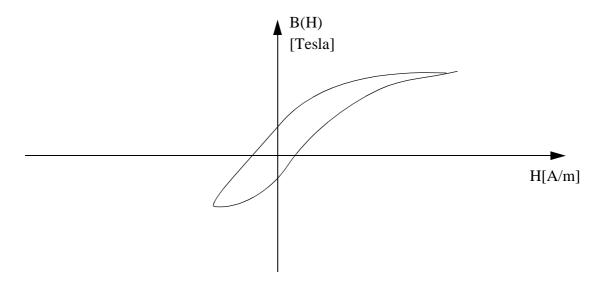

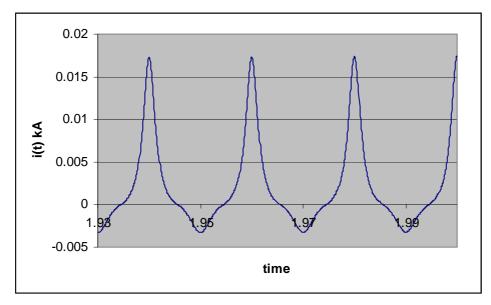

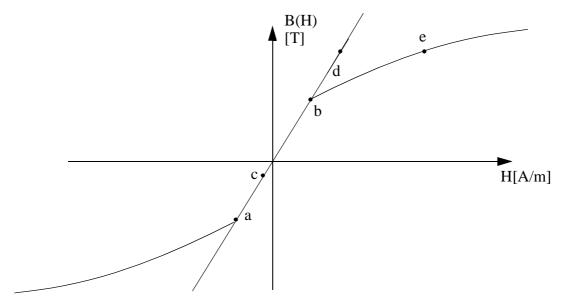

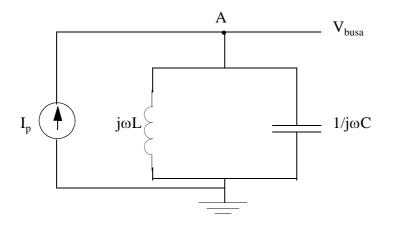

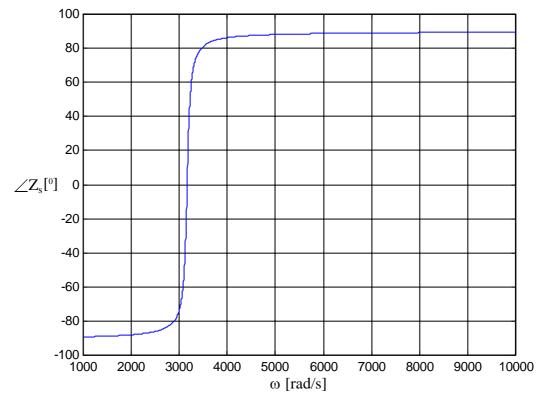

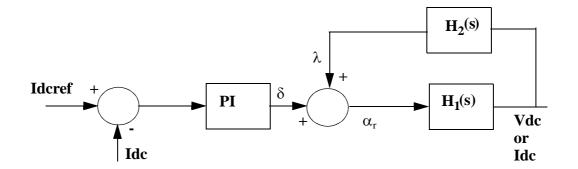

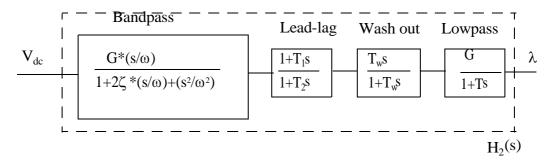

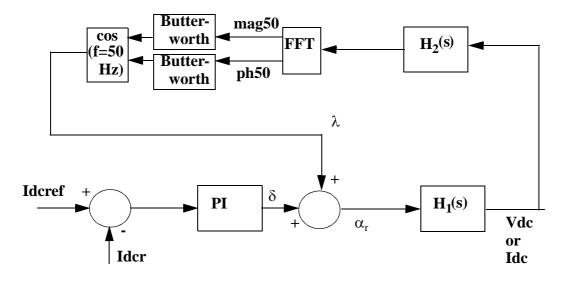

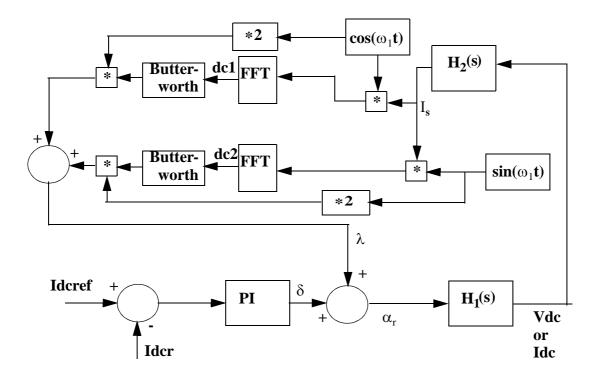

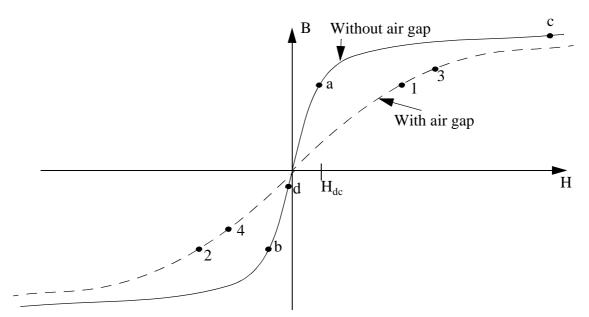

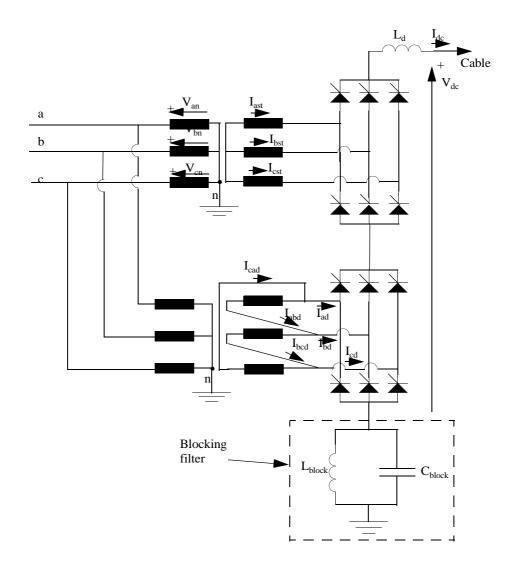

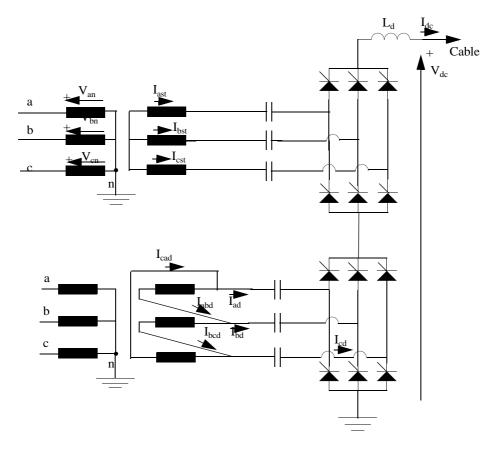

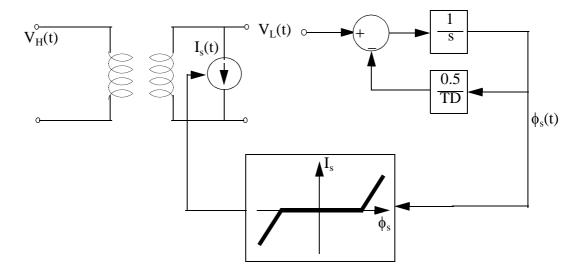

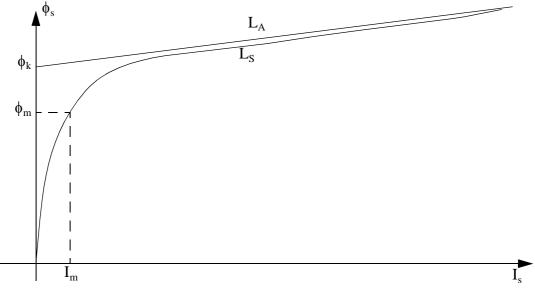

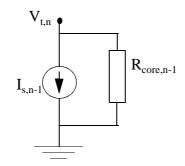

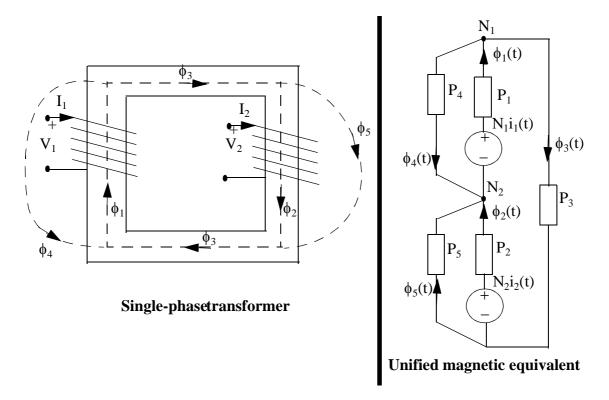

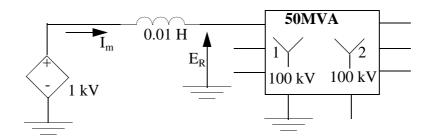

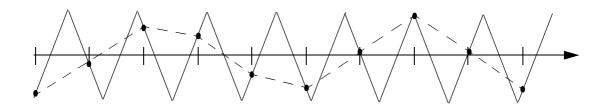

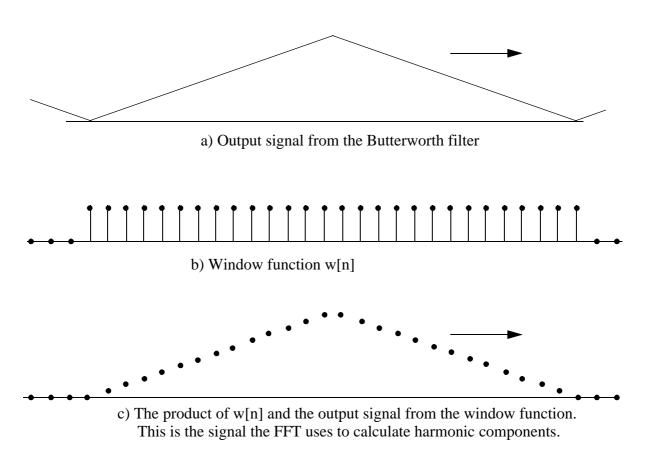

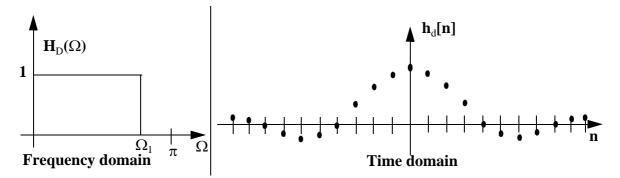

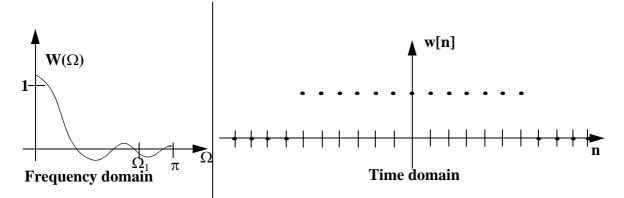

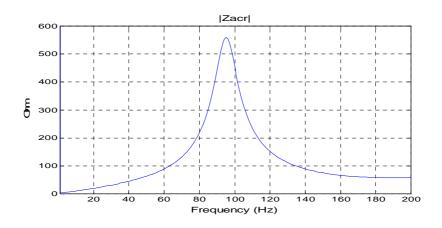

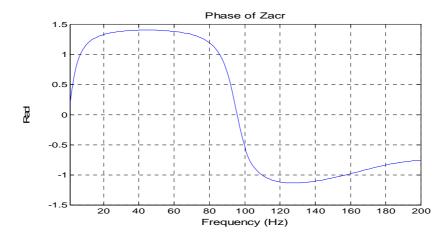

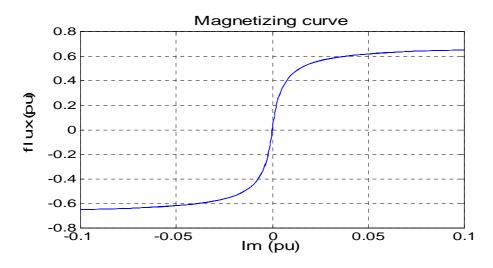

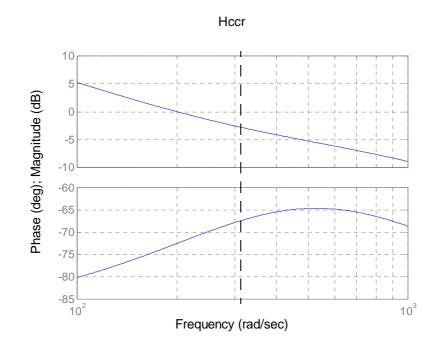

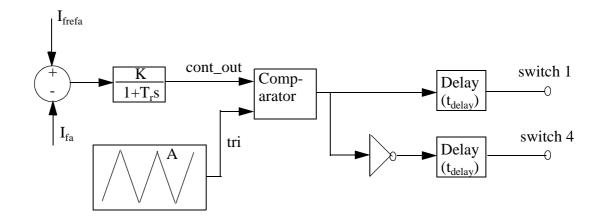

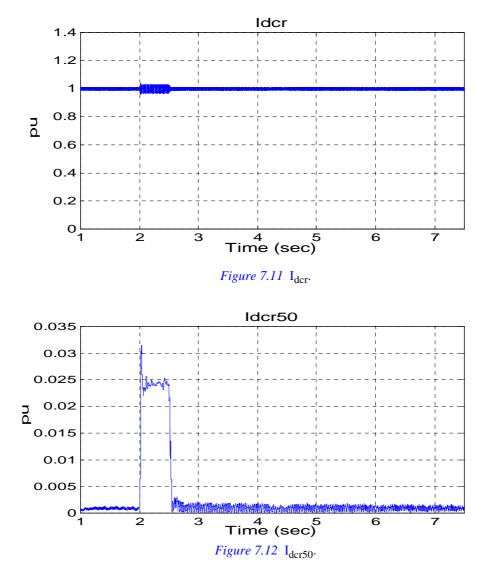

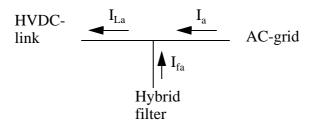

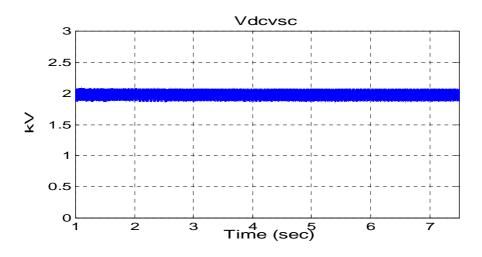

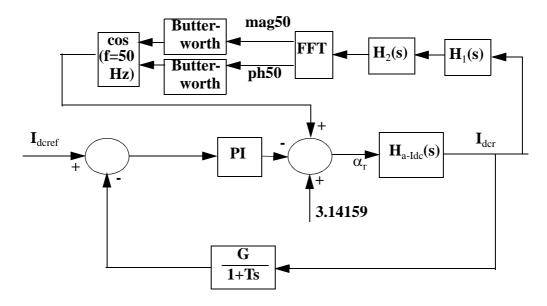

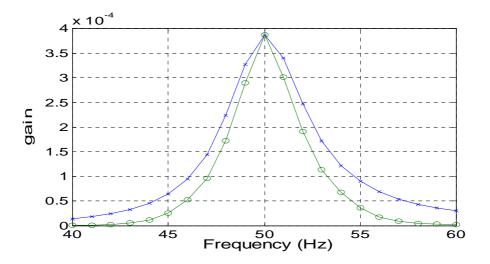

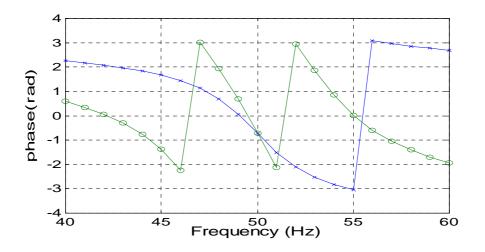

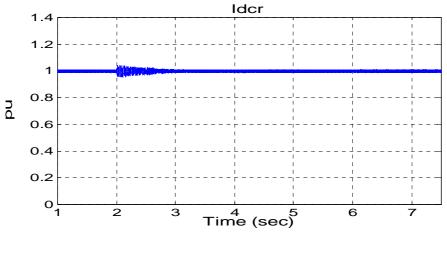

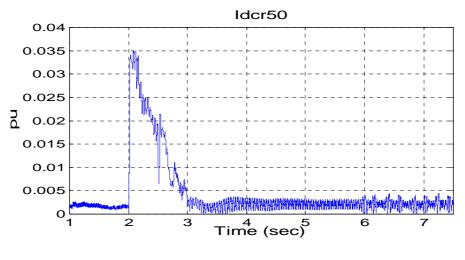

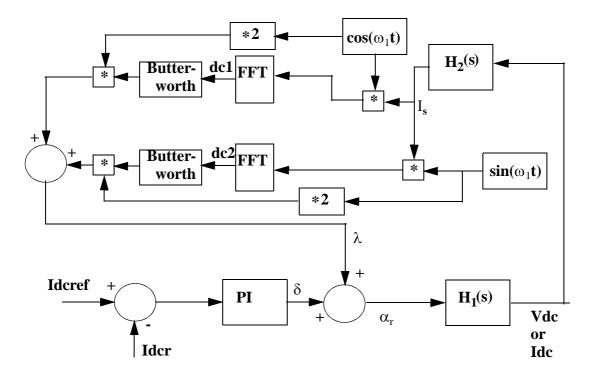

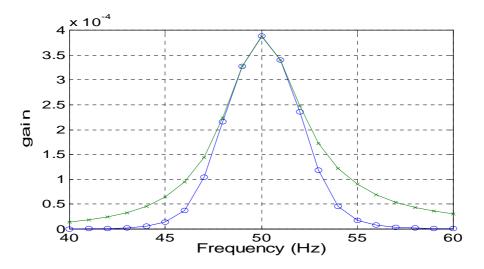

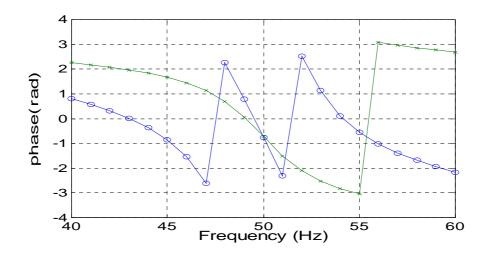

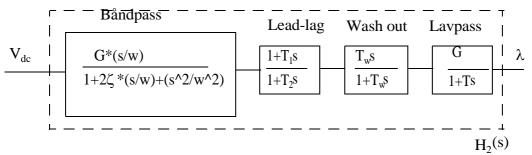

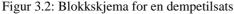

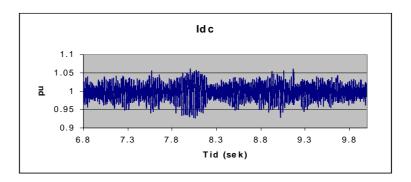

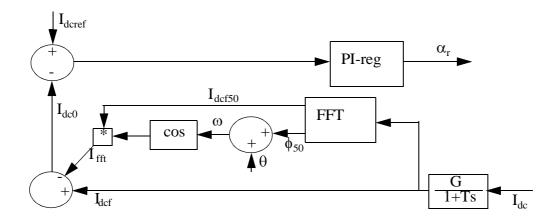

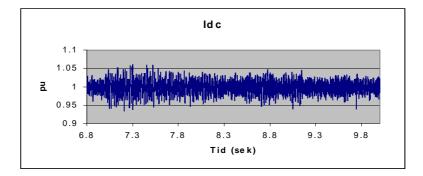

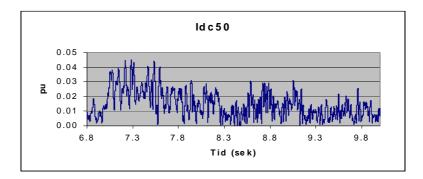

Figure 2.13 Simplified circuit diagram of an active filter that compensates for harmonics in the load current.