# Electrical Characterization of Silicon Cores from Glass-Cladded Fibres

Kyle Lapointe

Condensed Matter Physics Submission date: May 2014 Supervisor: Ursula Gibson, IFY

Norwegian University of Science and Technology Department of Physics

# Electrical Characterization of Silicon Cores from Glass-Cladded Fibres

Kyle Andrew Lapointe

Master of Science in Condensed Matter Physics Submission date: May 2014 Supervisor: Professor Ursula Gibson, IFY

Norwegian University of Science and Technology Department of Physics Trondheim, Norway

"If I could explain it to the average person, it wouldn't have been worth the Nobel Prize"

-Richard Feynman

#### NORWEGIAN UNIVERSITY OF SCIENCE AND TECHNOLOGY

#### Electrical Characterization of Silicon Cores from Glass-Cladded Fibres

#### Abstract

#### Department of Physics

#### Master of Science in Condensed Matter Physics

Semiconductor core fibres represent an emerging technology with potential applications in many areas, including photovoltaics and optical transmission. Recent advances in fibre manufacturing techniques has allowed long, continuous silicon core fibres to be produced in commercial draw towers. The effect of the molten core fibre fabrication method on the electrical properties of silicon cores from glass-clad fibres have been studied. Fibres with core diameters ranging from 60 to 300 µm were produced using a CaO interface modifier between the core and cladding. Five silicon material types with increasing phosphorus doping levels were analysed before and after the drawing process using four point probe technique. supplemented with microscopy and compositional analysis. Novel techniques for preparing and measuring fibre samples were developed, which is suitable for a range of fibre diameters. Cores produced from lightly doped materials showed a large increase in conductivity, while cores produced from a relatively highly doped material showed a small decrease in conductivity. The results suggest that the manufacturing process has introduced significant amount of impurities to the silicon core, which corresponds to additional charge carriers.

## Preface

This master's thesis was written during the fall of 2013 to the spring of 2014 and submitted in partial fulfilment towards a master's degree in physics at the Norwegian University of Science and Technology, NTNU. The experimental work was performed at the Department of Physics and at the Department of Material Science and Engineering. The work was carried out under supervision of Professor Ursula Gibson.

I would like to thank those who devoted their time to assist me throughout my time at NTNU; Fredrik Martinsen, who is equally as persistent and stubborn as I with the development of preparation methods; the staff at the NTNU Nanolab for being such a valuable resource throughout my project; Eric Karhu for not only his help with laboratory equipment but also his interesting conversations about science, politics, and life in general. Special thanks to Andrew Dibbs and Erlend Nordstrand for creating a solid foundation for fibre fabrication and my supervisor, Ursula Gibson for the help, direction, and overall enthusiasm.

This thesis includes a thorough coverage of the introduction, background, and methods sections in hopes that future students and those unfamiliar with fibre production may use this information for their benefit in their professional lives or simply for their curiosity.

Trondheim, May 2014

Kyle Andrew Lapointe

# Contents

| Abs    | tract       |       |                                   |   |        | iii  |

|--------|-------------|-------|-----------------------------------|---|--------|------|

| Pref   | face        |       |                                   |   |        | v    |

| Tab    | le of       | Figur | 2S                                |   |        | xi   |

| List   | of A        | bbrev | ations and Constants              |   |        | xvii |

| 1.     | Intr        | oduct | ion                               |   |        | 1    |

| 1      | .1.         | Brie  | history of Silicon                |   |        | 1    |

| 1      | .2.         | Mot   | vation and Scope                  |   |        | 2    |

| 2.     | Bac         | kgrou | nd                                |   |        | 5    |

| 2      | .1.         | Silic | on                                |   |        | 5    |

|        | 2.1.        | 1.    | Silicon Production                |   |        | 6    |

| 2.1.2. |             | 2.    | Silicon: The Material             |   |        | 8    |

| 2.1.3. |             | 3.    | Photovoltaics and Silicon's Role  |   |        | 18   |

| 2      | .2.         | Fibr  | es and Fabrication                |   |        | 23   |

|        | 2.2.        | 1.    | Current Techniques                |   |        | 24   |

| 2      | .3.         | Met   | l to Semiconductor Junctions.     |   |        | 28   |

| 2      | .4.         | Cha   | acterization Techniques           |   |        | 35   |

|        | 2.4.        | 1.    | Four Point Probe (4PP)            |   |        | 35   |

|        | 2.4.<br>Spe |       | Scanning Electron Microsopy (EDS) | - | ( ) 30 | •    |

| 2      | .5.         | Opti  | cal Lithography                   |   |        | 39   |

| 2      | .6.         | Phys  | ical Vapour Deposition (PVD)      |   |        | 42   |

|        | 2.6.        | 1.    | Sputtering                        |   |        | 43   |

|        | 2.6.        | 2.    | Evaporation                       |   |        | 45   |

| 3.     | Met         | thods | and Materials                     |   |        | 48   |

|    | 3.1.  | Fibr   | e Fabrication                        | 48 |

|----|-------|--------|--------------------------------------|----|

|    | 3.1.  | 1.     | Coating                              | 48 |

|    | 3.1.2 | 2.     | Preform                              | 50 |

|    | 3.1.3 | 3.     | Fibre Drawing                        | 51 |

|    | 3.2.  | Sam    | ple Preparation                      | 53 |

|    | 3.2.  | 1.     | Bulk Samples                         | 53 |

|    | 3.2.2 | 2.     | Fibre-on-Silicon (FOS) Planarization | 54 |

|    | 3.2.3 | 3.     | Etched Fibre-on-Glass (EFOG)         | 56 |

|    | 3.2.4 | 4.     | Lithography                          | 59 |

|    | 3.2.  | 5.     | Deposition                           | 69 |

|    | 3.3.  | Sam    | ple Measurement                      | 73 |

|    | 3.3.  | 1.     | 4PP                                  | 73 |

|    | 3.3.2 | 2.     | SEM-EDS                              | 75 |

|    | 3.3.3 | 3.     | Anisotropic Etching                  | 76 |

| 4. | Res   | ults   |                                      | 78 |

|    | 4.1.  | 4PP    |                                      | 78 |

|    | 4.1.1 | 1.     | Bulk Samples                         | 78 |

|    | 4.1.5 | 2.     | Fibre Samples                        | 80 |

|    | 4.2.  | KOI    | H Etching                            | 84 |

|    | 4.3.  | SEM    | I-EDS Imaging                        | 86 |

| 5. | Disc  | cussio | n                                    | 90 |

|    | 5.1.  | Coat   | ting & Fibre Drawing                 | 90 |

|    | 5.2.  | Sam    | ple Preparation                      | 91 |

|    | 5.3.  | 4PP    |                                      | 92 |

| 6. | Con   | clusio | on                                   | 96 |

| 7. | Fur   | ther V | Work                                 | 98 |

| References             |  |

|------------------------|--|

| A. Appendices          |  |

| A.1 Fibre Pulling Rig  |  |

| A.2 Error Calculations |  |

### **Table of Figures**

Figure 2.1: Periodic table of elements emphasizing silicon, modified from [10]..... 5 Figure 2.2: Schematic of Bell jar Siemens reactor. EGS silicon is 'grown' on the Ushaped bridge inside the reactor [13].....7 Figure 2.3: Left) Standard FCC unit cell. Atoms are present on the corners and faces of the cubic cell [14] *Right*) Silicon diamond-cubic lattice. Easily visualized by Figure 2.4: Illustration of (100) crystal plane and select directions in the diamond Figure 2.5: Schematic of solidification of a liquid into a polycrystalline structure from initial nuclei to crystalline structure. Grain boundaries occur at the interfaces of misaligned crystals. Time progression (a)-(b)-(c) [17]......10 Figure 2.6: Illustration showing formation of bands in a semiconductor w.r.t. atomic distance. Grey areas are continuous energy levels, while the white areas are forbidden. The creation of a bandgap due to a discontinuity in energy levels, denoted by E<sub>g</sub>. Modified from [18].....11 Figure 2.7: Electronic band structure of silicon E(k), marked by Brillouin zone directions. Energy is relative to the top of the VB. Excitation is assisted by a defect Figure 2.8: Excitation of an electron from the VB to CB from a photon with E >Figure 2.9: Left) As dopant in Si crystal producing an extra delocalized electron (e ) Right Boron dopant in Si crystal producing a hole (h<sup>+</sup>) [17].....14 Figure 2.10: Excitation of dopant atoms (As and B) at a concentration of 1ppb in Figure 2.11: Relationship between n and p type impurity concentration and resistivity of silicon showing a general decline in resistivity with increasing donor Figure 2.12: a) Polycrystalline material with grain boundaries. b) Charge distribution in material at grain boundaries. c) Resulting energy band structure

with energy wells shifted by value  $E_{b}$ , the trap levels are marked by  $E_{t}$ ; modified Figure 2.13: Simple PN junction system. Upon contact, electrons from the n-type material diffuse into the p-type due to a concentration gradient. The initially neutral material is now charged near the interface, forming an electric field in Figure 2.14: List of top efficiencies vs. year for various types PV technology; Figure 2.15: Left) Conventional silicon based planar solar cell.  $n^+$  and  $p^+$  regions serve to reduce minority carrier surface recombination. Silver fingers collect electrons generated from absorption of light. Anti-reflection coating improves absorption by reducing reflectance of incident light. Right) Radial PN junction Figure 2.17: Commercial fibre drawing process for conventional silica based fibres. A preform is heated and pulled. The diameter is monitored in-situ by a sensor. The process is continuous and can be tailored to produce fibres of a certain length and Figure 2.18: Powder-in-Tube method used by Scott et al. A vacuum d preform is Figure 2.21: Left) Ohmic I-V behaviour. Right) Schottky I-V behaviour (arbitrary Figure 2.22: Work functions of various metals compared to electron affinity of Si Figure 2.23: Band Diagrams of Ohmic metal-semiconductor contacts a.) n-type (separated) b.) n-type (in contact) c.) p-type (separated) d.) p-type (in contact). Figure 2.24: Positive and Negative bias of a metal-semiconductor (n-type) junction. A applied potential bends the band edges to form either a depletion or accumulation Figure 2.25: Left) Diagram of 4-terminal head on a semi-infinite sample illustrating head spacing. Right) Equivalent electrical circuitry of a 4PP setup. Rs represents measured resistance, while  $R_c$  is the contact resistance on the active current heads

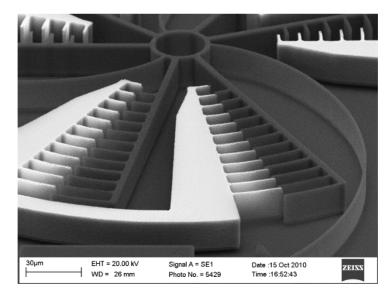

| Figure 2.19: SEM image of Archimedes spiral spring MEMS produced using optical                    |

|---------------------------------------------------------------------------------------------------|

| lithography and anisotropic etching                                                               |

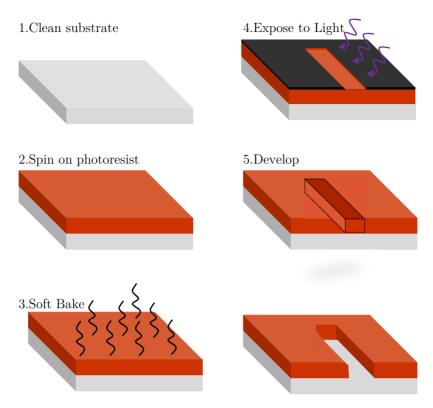

| Figure 2.20: Sample lithography patterning process with a positive photoresist. The               |

| exposed areas become soluble and are removed by the developer41                                   |

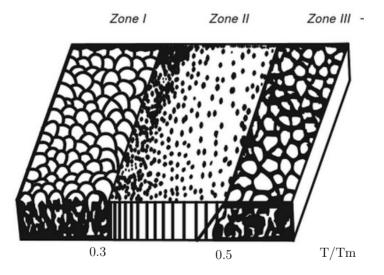

| Figure 2.26: Structure zone model according to Movchan and Demchishin as a                        |

| function of substrate temperature (T) and melting temp (Tm). Zone 1 shows large                   |

| isotropic grains vertically oriented; Zone 2 is tightly packed columns from improved              |

| diffusion; Zone 3 shows isotropic grain structure from annealing. Modified from $\left[42\right]$ |

|                                                                                                   |

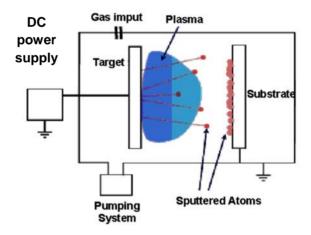

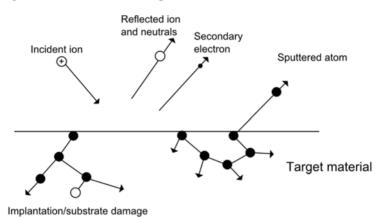

| Figure 2.27: Simple schematic of a diode sputter process. Plasma formed from an                   |

| inert gas (Ar) strikes a target material and ejects atoms. The atoms drift towards                |

| and coat the substrate43                                                                          |

| Figure 2.28: Sputter target processes. Incident ions will generate artefacts including            |

| secondary electrons and reflected ions, and sputtered atoms                                       |

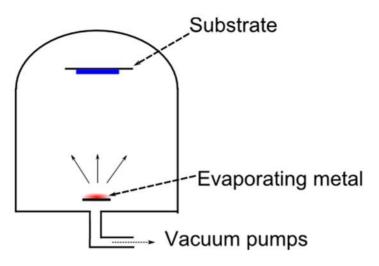

| Figure 2.29: Schematic showing simple evaporator system. A resistive heating                      |

| element causes a sample to melt and evaporate                                                     |

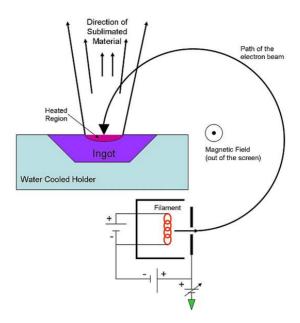

| Figure 2.30: Illustration showing the principle of e-beam evaporation. A magnetic                 |

| field (shown coming out of the screen) bends the electron beam due to the Lorentz                 |

| force. The electron beam strikes the sample causing heating and evaporation in a                  |

| confined region [43]                                                                              |

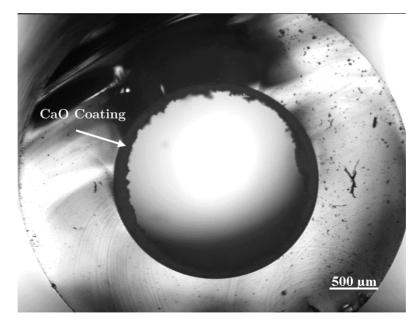

| Figure 3.1: Image of CaO coated quartz tube before packing with Si cores49                        |

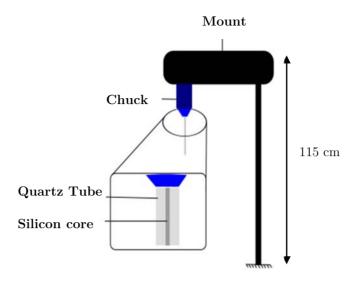

| Figure 3.2: Schematic of preform mounting system for pulling (not to scale). The                  |

| loaded preform is inserted into the chuck and held in place. The mount is composed                |

| of a drill press motor and rotates for even heating51                                             |

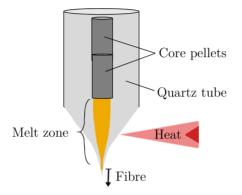

| Figure 3.3: Schematic of preform during pulling process. Heat is produced by the                  |

| oxyacetylene torch. The fibre is drawn from the bottom of the melt zone52 $$                      |

| Figure 3.4: Polished 'Bulk' Sample. Bulk cores were mounted in epoxy and ground                   |

| to reveal a planar surface                                                                        |

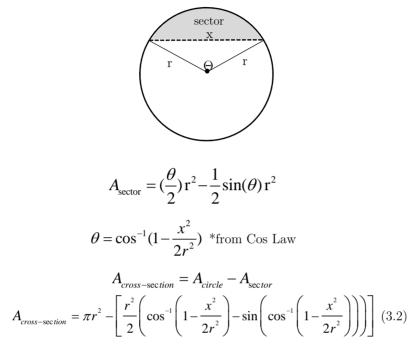

| Figure 3.5: Illustration of polishing procedure. Coarse grinding is done until the                |

| surface of the core is revealed, then fine grinding paper is used to carefully remove             |

| the remaining core material                                                                       |

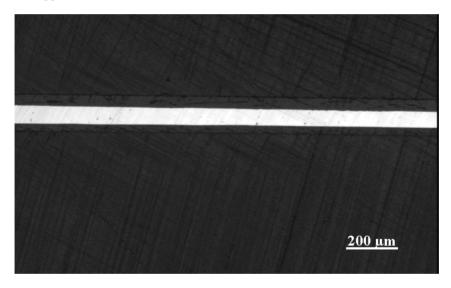

| Figure 3.6: $Left$ ) Before FOS preparation $Right$ ) After FOS preparation, the fibre            |

| was ground to reveal approx. its full diameter                                                    |

| Figure 3.7: FOS Sample surface after polishing. The fibre surface shows grinding                  |

| streaks but remains un-fractured56                                                                |

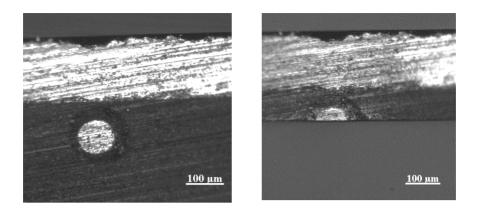

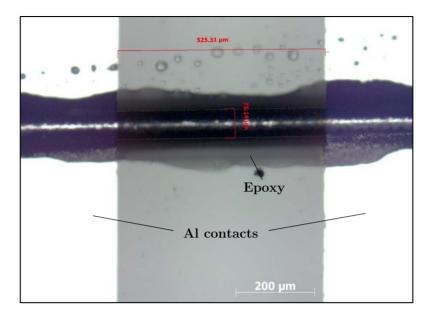

| Figure 3.8: Optical microscopy image of EFOG sample after curing showing epoxy          |

|-----------------------------------------------------------------------------------------|

| encasing the sides of the fibre                                                         |

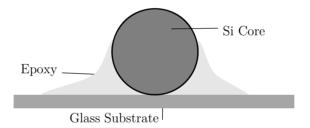

| Figure 3.9: Cross section schematic of 'ideal' EFOG sample after step 3                 |

| Figure 3.10: Angled BSE image of D429 EFOG fibre indicating fibre surface is            |

| exposed                                                                                 |

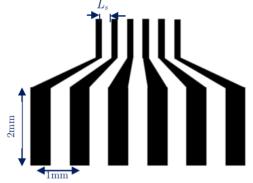

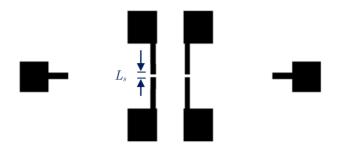

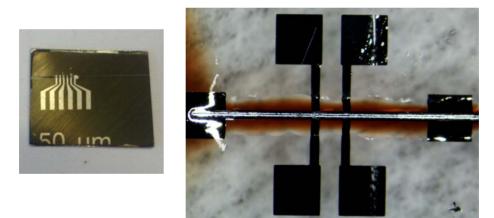

| Figure 3.11: Photolithography 4PP mask pattern                                          |

| Figure 3.12: Photolithography Hall mask pattern                                         |

| Figure 3.13: Left) Development of 4PP pattern on Epoxofix Epoxy Right)                  |

| Development of 4PP pattern on Epoxobond 110 Epoxy. Note the stark contrast              |

| between the quality of patterns on the two surfaces                                     |

| Figure 3.14: Ag pattern on O212 FOS sample after low intensity US lift-off in           |

| Ethanol. The Ag layer has been removed from the contact near the fibre                  |

| Figure 3.15: Repaired O212 FOS sample with silver paste added to bridge the             |

| contact leads with the fibre core                                                       |

| Figure 3.16: O212 FOS sample after lift-off in ethanol                                  |

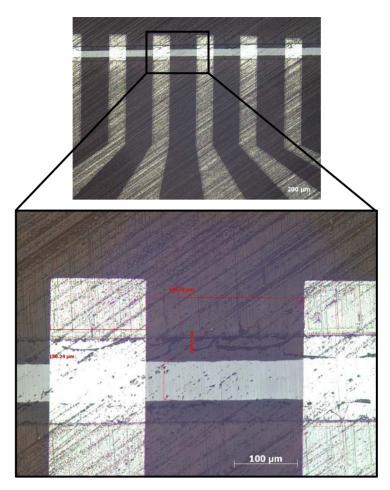

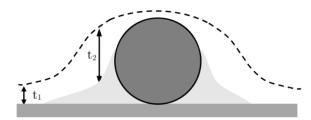

| Figure 3.17: Resist profile over EFOG sample                                            |

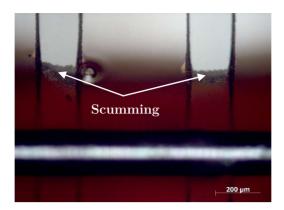

| Figure 3.18: Resist scumming on developed EFOG sample indicating unexposed              |

| resist                                                                                  |

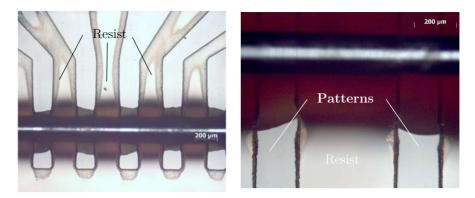

| Figure 3.19: Examples of successful development on EFOG samples (note the               |

| difference with Figure 3.18)                                                            |

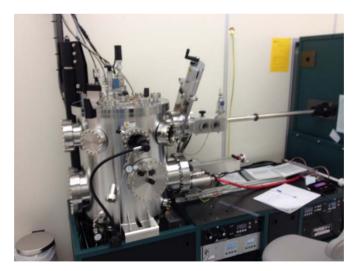

| Figure 3.20: AJA Sputter and Evaporator used for depositing contacts                    |

| Figure 3.21: Left) Shadow mask used for evaporation. Right) EFOG sample after           |

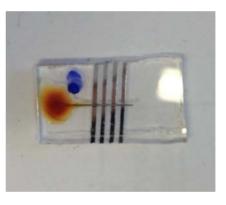

| e-beam evaporation of Al                                                                |

| Figure 3.22: Optical microscope image of finished EFOG (O212) sample71                  |

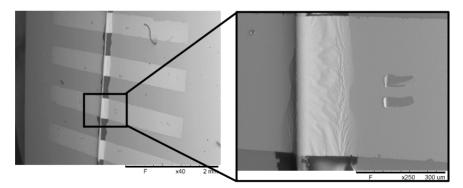

| Figure 3.23: SEM images showing deposited Al contacts overtop of an EFOG                |

| sample                                                                                  |

| Figure 3.24: Left) Successful lift-off of 4PP pattern on FOS sample. Right)             |

| Successful lift-off of Hall pattern on EFOG sample72                                    |

| Figure 3.25: $Left$ ) OM image of 4PP contact patterned with Al using e-beam. $Right$ ) |

| OM image of 4PP contact patterned with Al using sputtering. The pattern caused          |

| a short circuit during measurement                                                      |

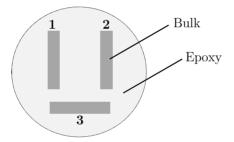

| Figure 4.1: Layout of bulk core samples in epoxy                                        |

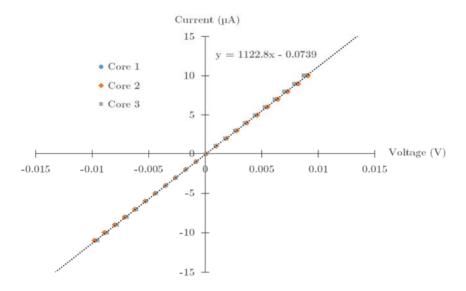

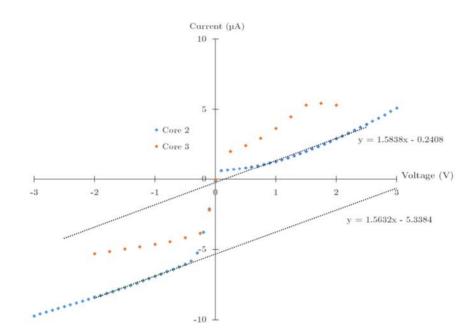

| Figure 4.2: IV curve for E944 bulk cores' 1, 2, and 3                                   |

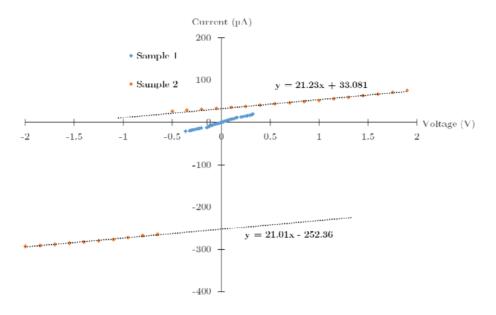

| Figure 4.3: 4PP results of intrinsic 3169 bulk material                                 |

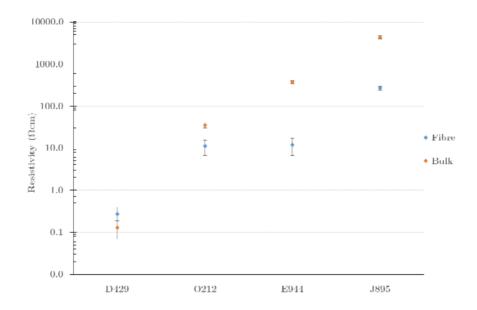

| Figure 4.4: Bulk resistivity results plotted against fibre resistivity for doped samples |

|------------------------------------------------------------------------------------------|

| on log <sub>10</sub> scale                                                               |

| Figure 4.5: 4PP results from EFOG J895 sample 1 and 2 illustrating the                   |

| discontinuity in I-V in sample 2                                                         |

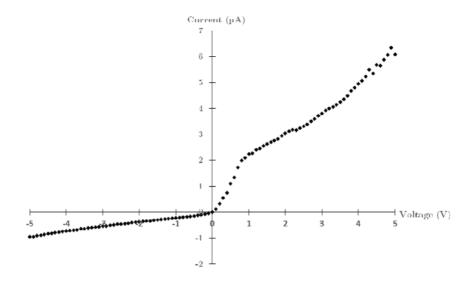

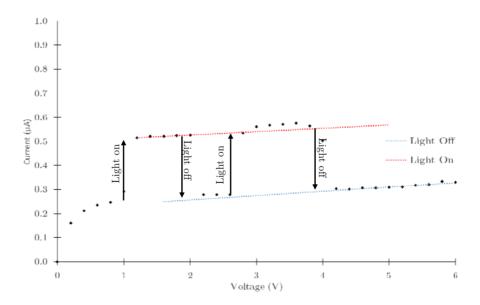

| Figure 4.6: Current sweep on 3169 EFOG sample illustrating Schottky style curve          |

|                                                                                          |

| Figure 4.7: Voltage sweep on 3169 EFOG sample illustrating photosensitivity. The         |

| lighting test was performed in situ and shows one data set                               |

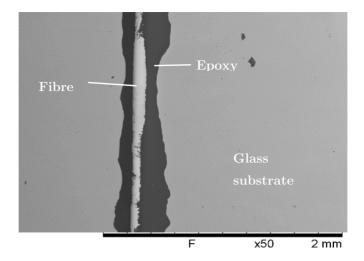

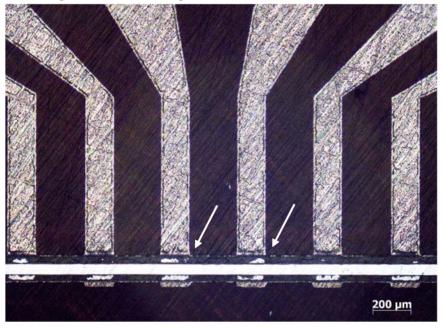

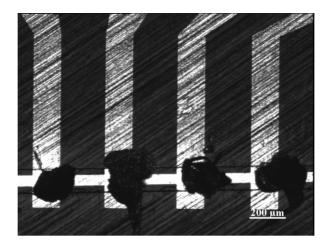

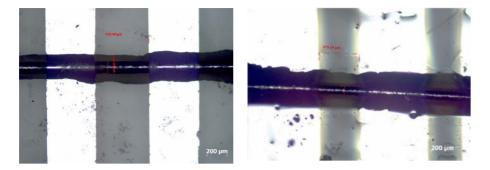

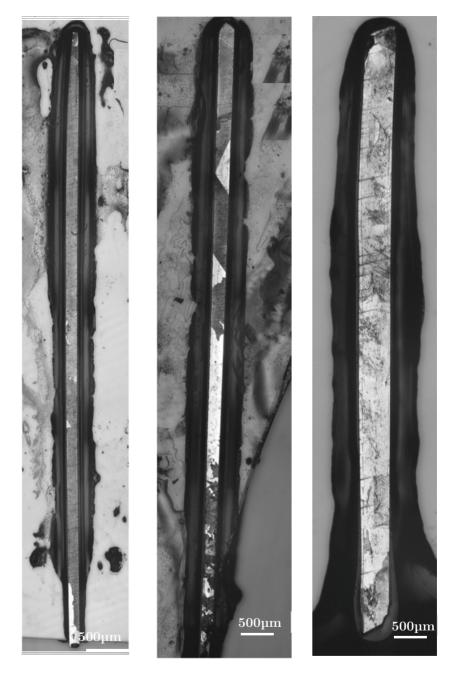

| Figure 4.8: a) Optical micrograph of EFOG D429 b) Optical micrograph of EFOG             |

| J895 $c)$ Optical micrograph of EFOG 3169. All samples etched with KOH solution          |

| for 2 minutes revealing grain structure                                                  |

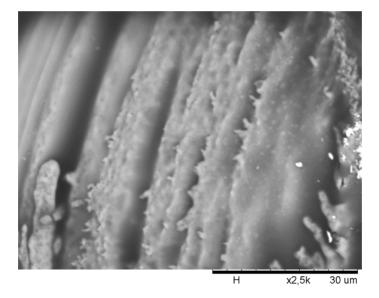

| Figure 4.9: SEM image of J895 fibre core surface showing rough and highly irregular      |

| surface features                                                                         |

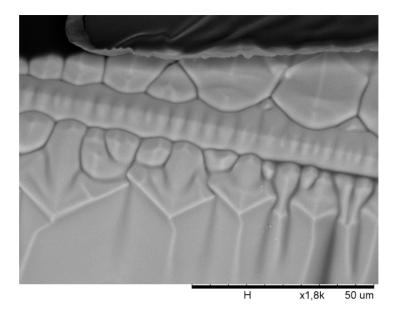

| Figure 4.10: SEM image of the longitudinal face of J895 fibre core surface showing       |

| smooth dendritic features                                                                |

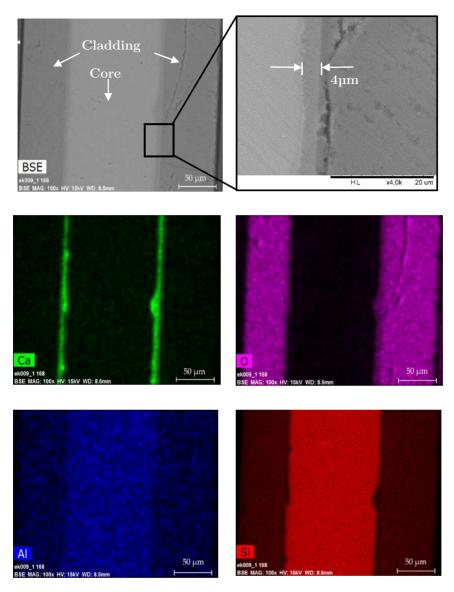

| Figure 4.11: SEM-EDS results from O212 FOS fibre highlighting Ca, O, Al, and Si          |

| distribution                                                                             |

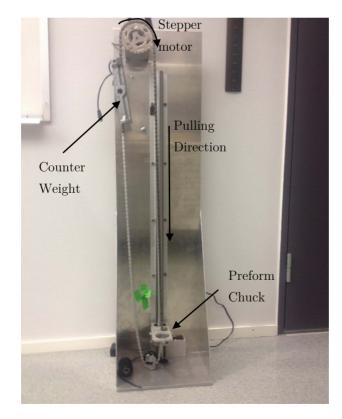

| Figure.A.1: Custom built fibre pulling machine powered by stepper motor106               |

# List of Abbreviations and Constants

| 4PP             | 4 Point Probe                                    |  |  |

|-----------------|--------------------------------------------------|--|--|

| BSE             | Back Scattered Electron                          |  |  |

| CVD             | Chemical Vapour Deposition                       |  |  |

| $\mathbf{CZ}$   | Czochralski                                      |  |  |

| DI              | Deionized Water                                  |  |  |

| e-beam          | Electron beam                                    |  |  |

| EFOG            | Etched Fibre-on-Glass                            |  |  |

| EGS             | Electronic Grade Silicon                         |  |  |

| FOS             | Fibre-on-Silicon                                 |  |  |

| IC              | Integrated Circuit                               |  |  |

| ID              | Inner Diameter                                   |  |  |

| I-V             | Current-Voltage                                  |  |  |

| MEMS            | Micro-electromechanical Systems                  |  |  |

| MFP             | Mean Free Path                                   |  |  |

| MGS             | Metallurgical Grade Silicon                      |  |  |

| MOF             | Micro-structured Optical Fibre                   |  |  |

| NREL            | National Renewable Energy Laboratory             |  |  |

| NTNU            | Norwegian University of Science and Technology   |  |  |

| OD              | Outer Diameter                                   |  |  |

| PPB             | Parts per billion                                |  |  |

| $\mathbf{PPM};$ | Parts per million                                |  |  |

| $\mathbf{PV}$   | Photovoltaic                                     |  |  |

| PVD             | Physical Vapour Deposition                       |  |  |

| RPM             | Revolutions per minute                           |  |  |

| SC Si           | Single Crystal Silicon                           |  |  |

| SE              | Secondary electron                               |  |  |

| SEM-EDS         | Scanning Electron Microscope-Electron Dispersive |  |  |

|                 | Spectroscopy                                     |  |  |

| SOI             | Silicon-on-insulator                             |  |  |

### 1. Introduction

#### 1.1. Brief history of Silicon

Silicon has become synonymous with the photovoltaic (PV) and electronic industries, yet this association has only been a relatively recent development. Silicon's rise in commercial use has its roots in the rapid industrial expansion in the 1950s, entwined with the production of iron/steel for commercial and military purposes [1]. Along with chromium, manganese, and nickel, silicon became increasingly popular in the late 1800s as it was observed that one, can in part, gain control over many material properties by using alloying agents including strength, toughness, ductility, and corrosion; silicon has a positive effect in steel as it decreases the stability of carbides [2]. Due to the natural abundance of silicon present in its oxide form, silica (SiO<sub>2</sub>), it was once known as the "poor man's alloying agent" [1]. During this time, there was a strong drive to lower manufacturing costs and create more efficient processes to purify silicon for various metallurgical purposes. Once it became readily available, other uses and effects were discovered, for instance it became known that silicon as an alloying element reduced magnetic hysteresis losses in steel [1].

Silicon's popularity in the electronics industry arose from its semiconducting characteristics. Its ability to rectify current in a diode, leading to the creation of one of most important devices for modern day electronics in 1954: the solid-state transistor. Silicon has had a substantial impact on the PV industry as it serves as a substrate for conventional PV cells as well as other integrated circuit (IC) electronics, such as in computer processers. These types of uses require ultra-pure silicon with impurities in the single ppb range in order to these devices to function efficiently. For IC applications, a purity or (99.9999999%) or otherwise known as 9N (9 nines) is common and usually referred to as electronic-grade silicon (EGS). In addition, silicon is normally manufactured in large single crystals. These requirements are a result from the high sensitivity of electrical properties and ever decreasing dimensions of devices: Intel currently incorporates 22nm gate lengths (~100 Si atoms) in their Ivy-bridge processors, emphasising the importance of purity [3]. Production of EGS

silicon is relatively energy intensive and costly, therefore only used for applications that require precision control. Though still relatively pure, a slightly lower purity silicon usually around 6-7N is used in PV industries, referred to as Solar-grade silicon (SGS). The reduction of purity is attributed to the low benefit to cost ratio of employing ultra-pure silicon. Silicon used in both industries is produced using the similar methods through a number of refining steps starting with silica, otherwise known as 'sand'. It has since spurred a technological advancement in the production methods of high quality silicon, namely the *Siemens Process, Czochralski,* and *Float zone* growth methods, which has lowered the cost considerable compared to 20 years ago. Silicon demand has risen exponentially over the last 10 years, however, it can be shown that the majority of silicon is still used in the metallurgical industry [1].

#### 1.2. Motivation and Scope

The past hundred years has represented a golden-age in advancement of our understanding of light and many of its intrinsic properties, spawning entirely new applications. Optical fibres have transformed the many technological areas including communication, electronics, medicine, and of course optics. Optical fibres act as the communication backbone of the planet, providing a framework for the internet, telephone, and other telecommunication services. They represent the most efficient commercialized method to transmit light over long distances; a typical loss for commercially available fibres is on the order of 0.1dB/km [4]. Many niche applications have evolved as well, for instance, optical fibres are routinely used in lasers and sensors. Fibres can be manufactured from a variety of elements and materials, which can be found as exotic combinations of elements or relatively simple commonly found materials. The majority of optical fibres used today are silica based fibres and thus have become a well-established technology.

The development of solar and electronic industries has triggered an enormous leap in usage and applications of silicon. There is always interest to improve our understanding of materials and more importantly, the depth of applications they can be used for. Silicon's dominating role in conventional PV and electronics markets' suggest it will remain a well-used material for some time. Improved manufacturing methods have steadily decreased the cost of high purity silicon.

Silicon core fibres have recently come into the scientific spotlight, spawning interest in research from groups across the world. The economic suitability and transmission properties of silicon in the mid-infrared (IR) spectral range has sparked interest in the biomedical, and energy industries where they may be used for power delivery, infrared sensors, and high frequency waveguide structures [5]. Due to their small dimensions, these fibres has spurred entirely new research into crystal growth. There has been a large effort in recent years to develop alternatives to conventional silicon solar technology in order to reduce the cost per kW. There is current interest in application of fibres in renewable energy. Radial PN junctions in the form of widearray solar cells have sparked interest as an alternative technology for photovoltaics (PV) due to a reduced cost of manufacturing and high absorbance cross section [6]. Silicon based fibres radial PN junctions may have many advantages over conventional silicon solar cells, yet represent a largely unexplored area. Currently effort is being put into improving the manufacturing process of such fibres, wires, and rods. There have been recent advancements in the semiconductor core fibres manufacturing methods used that have produced record low loses of  $\sim 5 dB/cm$  [7]. Recent exploration into various new geometries of silicon, such as bundled fibres may lead to new commercial applications.

However, little is known about the how fibre production process affects the electrical properties from the starting material to the fibre, which is extremely important in most applications, especially PV. This work explores the molten core method of silicon-core fibre production using the alkaline interface modifier CaO. This work carries on from previously established work by Andrew Dibbs and Erlend Nordstrand who laid a solid foundation in silicon core fibre production [8]. This investigation focuses on the electrical properties of manufactured fibres in effort to determine and clarify effects the production method has on the material Carrier diffusion length greatly contributes to the efficacy of PV and is strongly dependant on the resistivity.

Starting materials comprised of sectioned, single-crystal Si ingots manufactured using the CZ pulling process with varying levels of phosphorus doping are studied by using a specialized preparation process in order to characterize fibres using a custom-built four point probe (4PP). In addition, characterization of the fibres by SEM-EDS and optical microscopy supplement the 4PP results. The results are compiled into a comparison of electrical properties before and after the pulling process.

### 2. Background

This section includes a detailed literature review on relevant topics related to the production of silicon core fibres and background to procedures used in this work.

#### 2.1. Silicon

The work presented involves the production and characterization of silicon core fibres. Approximately 27% of the Earth's crust is composed of silicon, found in its oxide form SiO<sub>2</sub>. Its abundance has lead it to become one of the most widely used materials the semiconductor industry and as a natural consequence, one of the most researched. As a semiconductor, it displays properties of a both a conductor and an insulator depending on an external stimulus, such as light or an electric field. Its tetravalent nature mimics the behaviour of carbon, but at a substantially less reactive level. Silicon is very reactive with oxygen and will spontaneously produce a thin natural oxide layer approximately 2 nm in thickness [1]. Like water, silicon shows a positive thermal expansion coefficient upon solidification, which is roughly equal to 9% by volume [9]. This can cause difficulty in applications with phase changes from liquid to solid, such as in producing silicon based fibres.

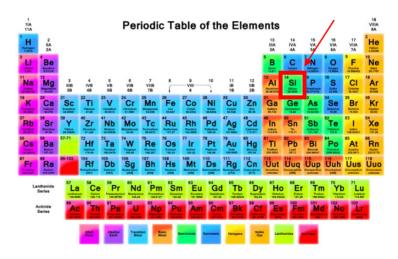

Figure 2.1: Periodic table of elements emphasizing silicon, modified from [10].

#### 2.1.1. Silicon Production

The silicon refining process is one of the major contributors and silicon's commercial success. The refining process is responsible for achieving many of silicon's material properties, such as conductivity. The starting material for metallurgical grade silicon (MGS) and electronic grade silicon (EGS) is silica (SiO<sub>2</sub>). Pure MGS is produced industrially by the reduction of silicon dioxide by carbon electrodes in large arc furnaces; the overall reaction being [11]:

$$SiO_{2(s)} + 2C_{(s)} \leftrightarrow Si_{(s)} + 2CO_{(g)}$$

(2.1)

Equation (2.1) is referred to as the Carbothermic process. In reality, there are many by-products including SiO, SiC, CO2, and micro-  $SiO_2$ , which reduces the overall yield and increases the complexity of the process. This process is highly energy intensive and requires approx. 11-13MWh per metric ton of MGS silicon [11]. The product of this reaction is still too impure to use in electronic applications and is roughly 98% silicon by this stage.

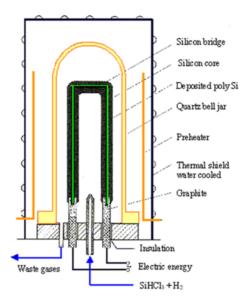

The Siemens Process is most widely used to further refine silicon into high purity from MGS. In this process, MGS silicon is crushed into small pieces and reacted with HCl to produce Trichlorosilane ( $SiHCl_{3(g)}$ ), following the reaction [12]:

$$Si_{(s)} + 3HCl_{(g)} \leftrightarrow SiHCl_{3(g)} + H_{2(g)} + \Delta H$$

(2.2)

Trichlorosilane is then reduced by the addition of hydrogen gas.

$$2SiHCl_{3(g)} + 2H_{2(g)} \leftrightarrow 2Si_{(s)} + 6HCl_{(g)}$$

$$(2.3)$$

The silicon product from equation (2.3) is very pure, reaching 9N purity. This represents a carbon contamination of less than 2 ppm and less than 1 ppb of group III and IV elements, which are critical doping elements for silicon. Figure 2.2 is a schematic of a conventional Siemens reactor for production of high grade silicon. There are other types of reactors using a modified Siemens process, such as fluidized bed reactor (FBR), which runs as a continuous process rather than a batch process.

Figure 2.2: Schematic of Bell jar Siemens reactor. EGS silicon is 'grown' on the U-shaped bridge inside the reactor [13].

The end stage of this process produces high grade poly silicon EGS. For many applications that require monocrystalline silicon, one more step is involved. The most common way to produce single crystal (SC) silicon on a commercial scale is the Czochralski method [12]. This method involved melting down fragments of EGS, and solidify the liquid silicon into a preferred crystal orientation. The method uses a 'seed' crystal of SC silicon with the desired orientation. While rotating, the seed is dipped into the Si melt and slowly pulled upwards. Liquid Si is pulled upwards with the seed by surface tension forming a thin layer, which can transfer heat away. Solid Si nucleates onto the seed with the same orientation. The temperature, pull rate, rotational speed, and surrounding atmosphere are carefully controlled in order to ensure the Si solidifies as desired. This process can produce relatively large ingot diameters, exceeding 30cm [12]. The process is sensitive to impurity contamination from the diffusion of impurities from the refractory crucible, usually made of silicon nitride. Oxygen is unwanted as it reacts with metallic impurities. In addition, nonhomogeneous distribution of desired impurities such as group III and V elements is also a concern. Doping is usually achieved by mixing in the correct ratio of dopant material into the Si before the CZ process [12]. Over the years doping has been subjective in nature, changing in nomenclature. In order to clarify, dopant nomenclature in this work will follow Table 2.1.

|        |      | Concentration $(atoms/cm^3)$ |                     |                     |                |

|--------|------|------------------------------|---------------------|---------------------|----------------|

| Dopant | Type | $< 10^{14}$                  | $10^{14} - 10^{16}$ | $10^{16} - 10^{19}$ | $> 10^{19}$    |

|        |      | Very lightly doped           | Lightly doped       | Doped               | Heavily doped  |

| V      | n    | n <sup></sup>                | n                   | n                   | $n^+$          |

| III    | р    | p                            | p                   | р                   | $\mathbf{p}^+$ |

Table 2.1: Dopant nomenclature for Silicon [12].

#### 2.1.2. Silicon: The Material

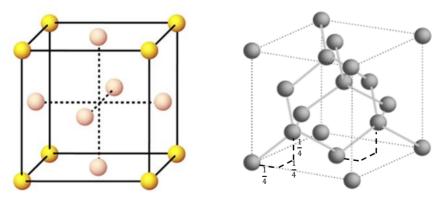

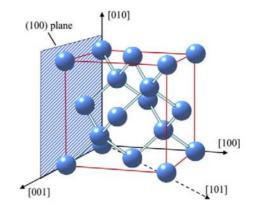

Most of silicon's properties and behaviours can be better understood from an overview of its atomic behaviour. All crystalline solids exhibit an ordered structure of atoms. The smallest repeating unit volume of atoms is referred to as a unit cell. Pure silicon arranges itself in a diamond-cubic crystal structure, which as its name suggests is the same structure as carbon based diamond. It can be visualized as two interpenetrating face-centred cubic (FCC) lattices with the second lattice shifted  $(\frac{1}{4}, \frac{1}{4}, \frac{1}{4})$  relative to the first: See Figure 2.3. Its structure is a result of the sp<sup>3</sup> hybridization of electron orbitals, allowing bonding with 4 atoms.

Figure 2.3: *Left*) Standard FCC unit cell. Atoms are present on the corners and faces of the cubic cell [14] *Right*) Silicon diamond-cubic lattice. Easily visualized by  $(\frac{1}{4}, \frac{1}{4}, \frac{1}{4})$  [15] transformation from an FCC cell.

Silicon's structure is highly symmetric being cubic in nature and displays a high degree of mechanical anisotropy, easily cleaving along the (100) plane. The atomic structure differs with regards to sp<sup>3</sup> orbital orientations, leading to electrical

anisotropy. Most BCC and FCC based materials will show at least some anisotropy due to differences in atomic packing. For example, the electrical conductivity and etching of silicon with potassium hydroxide significantly differs between the (100), (111), and (110) crystal planes.

Figure 2.4: Illustration of (100) crystal plane and select directions in the diamond cubic lattice [16].

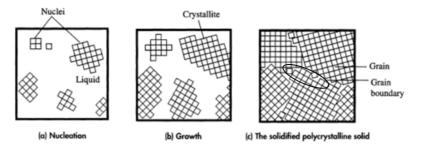

The above is only valid in a monocrystalline structure. In reality, it is quite difficult to produce SC silicon. Only under highly controlled processes such as in CZ pulling will silicon solidify into a single crystal structure. Due to thermodynamic and kinetic considerations, silicon will preferably solidify (like all other crystalline materials) into in a local ordered, but randomly oriented domains called grains. Heterogeneous nucleation requires less energy to initiate compared to homogeneous nucleation and is more likely to begin on surrounding walls and inclusions, essentially any liquid-solid interfaces. This process begins simultaneously at different places in the melt, forming small 'seeds' distributed around the melt. The solidification interfaces expand in different orientations forming regions of varying crystalline orientation, such a material is referred to as polycrystalline. These grains have a large impact on mechanical and electrical properties of the material. Grain boundaries are relatively high energy regions due to mismatch of atomic lattice; the atomic spacing is strained relative to their equilibrium positions. Boundaries create extra resistance for electrons, acting as a high energy barrier. Fractures are more likely to occur at the grain boundaries as well. Figure 2.5 highlights the development of a polycrystalline material.

Figure 2.5: Schematic of solidification of a liquid into a polycrystalline structure from initial nuclei to crystalline structure. Grain boundaries occur at the interfaces of misaligned crystals. Time progression (a)-(b)-(c) [17].

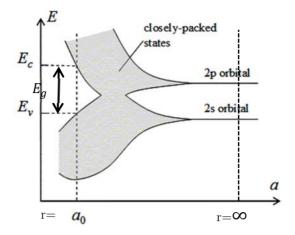

Band Theory is an important tool to distinguish a semiconductor's electronic band structure and is critical to the understanding of semiconductors electronic properties. This fundamental property can only be realized when examining electronic properties at the atomic level using quantum theory. As electrons are fermions and obey the *Pauli Exclusion Principle*, in which each electron in an orbital around the atom's nucleus is at a unique energy level. Considering a one atom case, the orbitals exist at distinct quanta of energy. In the case of many close packed atoms, as in a crystal, orbitals begin to overlap and interact with surrounding atoms creating new energy states. A 'band' is formed from the continuity of allowable energy states of atoms' electrons over a range of energy. An example of this effect is illustrated in Figure 2.6:  $r=\infty$  implies an isolate atom, while  $r=a_0$  represents a solid with atoms at its equilibrium spacing

Figure 2.6: Illustration showing formation of bands in a semiconductor w.r.t. atomic distance. Grey areas are continuous energy levels, while the white areas are forbidden. The creation of a bandgap due to a discontinuity in energy levels, denoted by  $E_g$ . Modified from [18].

Semiconductors and insulators display a forbidden zone: an energy range where electrons cannot exist. This zone is referred to as a bandgap gap in energy level creating distinct bands. The bandgap is represented as a relative difference from the highest occupied molecular orbital, otherwise known as the valence band (VB) edge, and the lowest unoccupied molecular orbital, otherwise known as the conduction band (CB) edge, denoted as  $E_V$  and  $E_C$  respectively. In a general sense, the difference between the semiconductors and insulators is the size of the bandgap. Exact definitions are contested, but for simplicity an insulator is usually defined as a material with a bandgap greater than 3.3 eV [2]. However, this value is arbitrary as some 'semiconductors' display a bandgap of over 3eV, for example ZnO and ZnS. Metals do not have this gap in energy and thus usually display conducting properties.

A materials bandgap is responsible for many of its electrical and optical properties. In simple terms, an external stimulus, such as an incoming photon with an energy equal to the bandgap will excite an electron in the VB to the CB. This process leaves behind an empty bond, seen as positively charged charge pseudo-particle, called a 'hole'. An excitation of the electron though the bandgap is said to create an electron/hole ( $e^{-}/h^{+}$ ) pair. Once in the CB, an electron is free to move in the material in a delocalized state, this is the key to transforming a semiconductor into a conducting state. Electronic bands fluctuate relative to the direction in

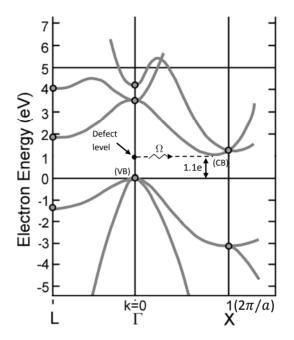

momentum space denoted by k. In technical terms, k is related to the Fourier transform of crystal spatial domain into the frequency domain. Silicon's electronic band structure is displayed in Figure 2.7.

Figure 2.7: Electronic band structure of silicon E(k), marked by Brillouin zone directions. Energy is relative to the top of the VB. Excitation is assisted by a defect level and phonon  $(\Omega)$ . Data from [19].

Silicon is an indirect bandgap semiconductor, that is, the VB and CB edges do not lay in the same k-space. An excitation of an electron requires an assistance of a phonon to transfer momentum in k-space for the electron to reach the CB. A phonon is a quantum of lattice vibration. For simplicity, silicon's band structure is usually given without k dependency when not directly referring to k dependence of energy such as in Figure 2.8. Silicon's bandgap is generally reported as  $\sim 1.1 \text{eV}$ corresponding to a wavelength of  $1.13\mu$ m (infrared). The associated between energy and photon wavelength is given by:

$$E(\lambda) = \frac{hc}{\lambda} = hv \tag{2.4}$$

Where h is Plank's constant  $(6.62607 \times 10^{-34} Js), c$  is the speed of light in vacuum  $(2.99792 \times 10^8 m/s)$ , and  $\lambda$  is the wavelength of the photon.

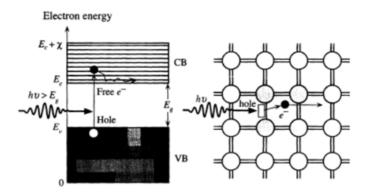

Figure 2.8: Excitation of an electron from the VB to CB from a photon with  $E > E_g$ , showing the creation of an e<sup>-</sup>/h<sup>+</sup> pair [17].

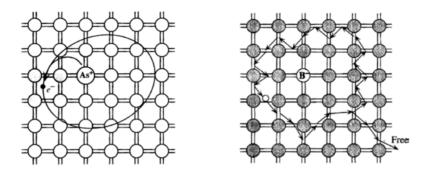

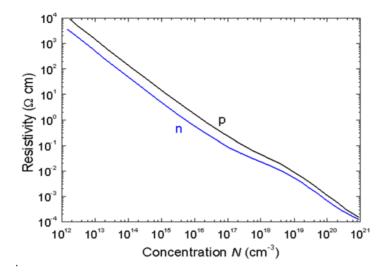

Semiconductors electrical properties are highly sensitive to doping, that is intentionally mixing in impurity atoms into the lattice to produce changes in the quantity of charge carriers i.e. electrons or holes. With the knowledge of doping levels one can estimate the electrical behaviour of a semiconductor, and vice versa. Impurities have a relative difference of electrons in their valence shell, producing local changes to the electronic structure of the host semiconductor by adding or removing an electron to the semiconductor's lattice. For an example, arsenic contains five valence electrons, 1 more compared to silicon's 4 valence electrons. When arsenic is introduced into the silicon lattice, it binds to Si, but the extra electron is loosely bound to the As atom. This final material is referred to as n-type while As is a donor atom. Oppositely, boron contains 3 valence electrons. When it binds to silicon, the fewer amount of electrons leaves one bond unsatisfied. This absence of a bond is referred to as a hole and carries a positive charge  $(h^+)$ . The resulting material is classified as p-type and boron as an acceptor atom. Both of these particles are loosely bound to their host and thermal energy is usually sufficient free these particles by causing an excitation. An illustration of this effect is shown in Figure 2.9.

Figure 2.9: *Left)* As dopant in Si crystal producing an extra delocalized electron (e<sup>-</sup>) *Right)* Boron dopant in Si crystal producing a hole (h<sup>+</sup>) [17].

The relationship between temperature and thermal energy  $(E_T)$  is given by:

$$E_T = V_T q = k_B T \tag{2.5}$$

Where  $V_T$  is the thermal voltage, q is the magnitude of the electronic charge  $(1.602 \times 10^{-19} C)$ ,  $k_B$  is Boltzmann's constant  $(8.617 \times 10^{-5} eVK^{-1})$ , and T is the temperature in K. For example, the equivalent energy at room temperature (298 K) is ~0.03 eV. Where  $1 \text{ eV} = 1.602 \times 10^{-19} J$ . In terms of the electronic band structure, the acceptor and donor atoms lay just above and below the band edges.

Figure 2.10: Excitation of dopant atoms (As and B) at a concentration of 1ppb in silicon. [17]

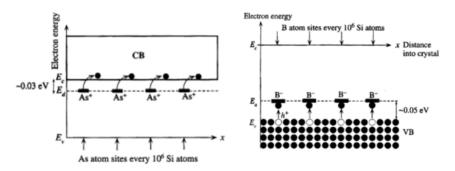

The introduction of charge carriers have a large impact on the electronic properties of the semiconductor. Even low concentrations of p- and n-type impurities change the conductivity significantly due to extra charge carriers. The conductivity of the semiconductor depends not just on the amount of the carriers, but also the carrier's mobility  $\mu_{n/h}$ , which is a measure of its ability to move through the atomic lattice. Conductivity can be estimated by:

$$\sigma \equiv \frac{1}{\rho} = qn\mu_n + qp\mu_h \tag{2.6}$$

Where  $\rho$  is the resistivity, *n* is the donor concentration, *p* is the acceptor concentration,  $\mu_{n/h}$  represents the mobility of the carrier (usually expressed in  $cm^2/Vs$ , and *q* the unit charge of the carrier. The mobility in turn is can be estimated by its scattering time, and the effective mass. This is treated by the classical Drude model. The carrier mobility is estimated by [17]:

$$\mu_{e/h} = \frac{q\tau_{e/h}}{m_{e/h}^*} \tag{2.7}$$

Where  $\tau_{e/h}$  is the mean lifetime before scattering of the carrier and  $m_{e/h}^*$  is the effective mass of the carrier (where n/h indicated the carrier type). It is a strange notion that holes have a mass, in this sense mass represents a resistance to acceleration. The positive nuclei within the lattice acts as a force against the positively charged hole, giving it 'mass'. The relationship between impurity concentration and conductivity of silicon has been well documented and experimentally researched. Figure 2.11 shows quantitatively, the relationship between impurity concentration and conductivity of silicon.

Figure 2.11: Relationship between n and p type impurity concentration and resistivity of silicon showing a general decline in resistivity with increasing donor density [17].

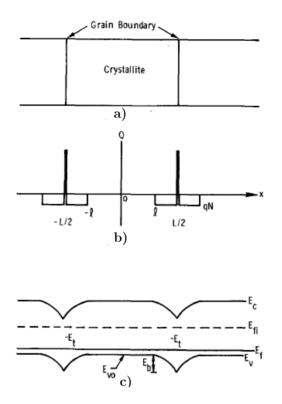

The true effect of grain boundaries on conductivity can be interpreted as energy traps in the band structure. The high energy acts to create energy levels located in the forbidden bandgap that effectively trap electrons in the conduction and valence bands. Overall, this effect reduces the amount of free electrons in the conduction band, which increases resistivity. This effect is realized as a reduction in diffusion length, carrier lifetimes, and carrier mobility. An illustration of the effect of grain boundaries on the band structure is shown in Figure 2.12.

Figure 2.12: a) Polycrystalline material with grain boundaries. b) Charge distribution in material at grain boundaries. c) Resulting energy band structure with energy wells shifted by value  $E_b$ , the trap levels are marked by  $E_t$ ; modified from [20].

It is important to note that the electronic band structure is not as simple as is expressed in this work. For a more detailed treatment of band models and doping, see reference [21]. Table 2.2 is a summary of some important properties of crystalline silicon.

| Property                                                 | Value         |

|----------------------------------------------------------|---------------|

| Density $[g/cm^3]$                                       | 2.32          |

| $Bandgap \; [eV]$                                        | 1.13          |

| Crystal Structure                                        | Diamond-Cubic |

| Lattice constant [nm]                                    | 0.54305       |

| Melting Temperature [°C]                                 | 1417          |

| Intrinsic Resistivity <sup><i>a</i></sup> [ $\Omega$ cm] | $2.3x10^{5}$  |

| Coefficient of thermal expansion $[{\rm cm/cmK}]$        | $2.6x10^{-6}$ |

| Thermal Conductivity $[Wm^{-1}K^{-1}]$                   | 150           |

| Index of refraction                                      | 1.54          |

Table 2.2: Summary of important properties of silicon [1, 17].

$^{\rm a}$  At 300K

#### 2.1.3. Photovoltaics and Silicon's Role

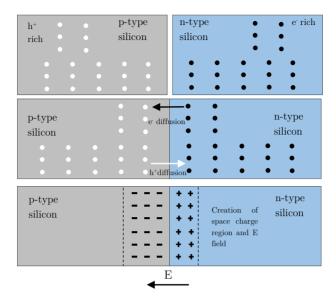

Silicon's role in PV has its roots in the discovery of a PN junction. The PN junction, as it suggests is a junction created between p-type and n-type semiconductor sections. The donors and acceptors of the two sections interact to form a small intrinsic electric field. An incident photon with  $E > E_g$  will produce an e<sup>-</sup>/h<sup>+</sup> pair, normally this pair's life is short lived recombining immediately releasing heat. However, the electric field inside the PN junction acts to separate the two charge carriers, reducing the probability of recombination. For illustration of this effect see Figure 2.13.

Figure 2.13: Simple PN junction system. Upon contact, electrons from the n-type material diffuse into the p-type due to a concentration gradient. The initially neutral material is now charged near the interface, forming an electric field in opposition to the diffusion flow.

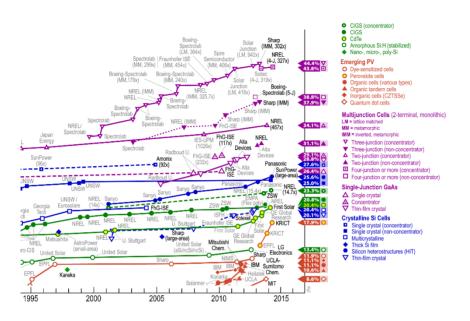

Silicon's bandgap is coincidently suited for the solar spectrum here on earth, which also contributes to silicon's popularity in PV. Conventional silicon based PV has been well established for more than 3 decades. A clear trend indicates efficiency of PV is increasing considerably impart due to an increase in research. Research into improving efficiency, improving product lifetimes, and reducing cost of manufacturing is still ongoing and has explored new geometries and compositions of silicon PV. To date, the record efficiency for a silicon based solar cell is approx. 25% by Amonix achieved using concentrated sunlight. The maximum efficiency of a single junction cell is given by the Shocklev–Queisser limit and is around 29% [21]. Figure 2.14 is an excerpt from National Renewable Energy Laboratory (NREL) list of efficiencies for various types of PV from 1995 onwards. It is important to note that the maximum theoretical limit of a solar cell  $\sim$ 86.6%, predicted for a solar cell with an infinite number of junctions [21]: i.e. 86.6% of incoming photon energy is the maximum amount of that could ever be converted into electrical energy. What Figure 2.14 does not show is the cost per kW. Technologies such as multijunction and metamorphic solar cells has certainly pushed the limits of efficiency in PV, but the majority of a high performance technologies are only realized on a laboratory scale as it is too expensive for commercialization. The motivation to

reduce cost but retain reasonable efficiencies has so far explored primarily high impurity or high defect materials, such as amorphous silicon [22].

Figure 2.14: List of top efficiencies vs. year for various types PV technology; tabulated by NREL, modified from [23].

By definition efficiency,  $\eta$  is:

$$\eta \equiv \frac{P_{out}}{P_{in}}$$

The physical expression for efficiency of solar cells is [21]:

$$\eta = \frac{V_{oc} \cdot J_{sc} \cdot FF}{P_{in}}$$

(2.8)

Where  $V_{oc}$  is the open circuit voltage (voltage produced at zero current),  $J_{sc}$  is the short circuit current (current at no load), FF is the fill factor, and  $P_{in}$  is the radiant power from the sun. The fill factor is a term representing the maximum power that

can be harnessed from a particular system. The current output from a solar cell can be estimated by [21]:

$$J = J_{sc} - J_0 \left[ \exp\left(\frac{qV}{K_B T}\right) - 1 \right]$$

(2.9)

And the open circuit voltage leads to:

$$V_{oc} = \frac{K_B T}{q} \ln\left[\left(\frac{J_{sc}}{J_0}\right) + 1\right] \approx \frac{K_B T}{q} \ln\left(\frac{J_{sc}}{J_0}\right)$$

(2.10)

Where  $J_0$  is the diode current (assuming an ideal diode). The diffusion length,  $L_{n/h}$  (subscript indicating carrier type) is defined as the average length a carrier travels before recombining [6]. Thus,  $V_{oc}$ ,  $J_{sc}$ , and FF are influenced heavily by diffusion length of the carriers, the lower diffusion length, the higher recombination rate, both  $J_{sc}$ , and  $V_{oc}$  drop.

$$L_n = \sqrt{D_n \tau_n} = \sqrt{\left(\frac{K_B T}{q} \mu_n\right) \tau_n}$$

(2.11)

Where  $D_n$  is the diffusivity constant, estimated by the *Einstein Relation*,  $\mu_n$  is the electron mobility, and  $\tau_n$  is the average carrier lifetime. Eq. (2.11) represents diffusion length of electron carriers, holes abide very similarly.  $J_{sc}$  can be viewed as the amount of photogenerated current produced across the material.  $J_{sc}$  will increase as  $L_n$  increases until a limiting point where,  $L_n$  becomes larger than the cell thickness, or the optical thickness; Kayes defines the optical thickness as  $1/\alpha$ , where  $\alpha$  is the attenuation coefficient considering the entire solar spectrum [6]. As an arbitrary definition,  $t = 1/\alpha$  is when 90% of the incoming light has been absorbed, given by an integration over all wavelengths using *Beer-Lamberts Law*. The optical thickness dictates how thick a material should be in order to absorb the incoming energy of light.

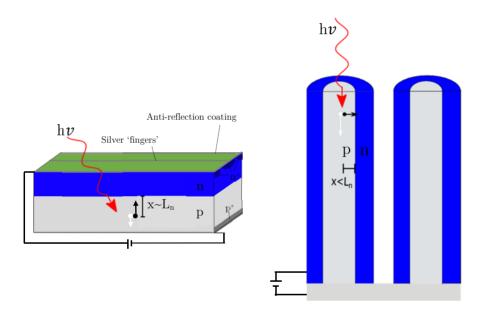

An array of radial PN junction fibres will act as a solar cell and has recently become an idea as an alternative to conventional cells. One major advantage is that the dimensions of the fibres act to reduce the length (x) carriers must travel such that  $x < L_n$ . The use of fibres also has the capacity to vastly increase the effective surface area for absorption. Incorporating silicon based materials is an obvious choice due its availability cost and manufacturing technology. Figure 2.15 illustrates the idea using a radial PN junction as a solar cell. However, not much is known of how the manufacturing processes of fibres effect their electrical properties. The majority of research has been on laboratory grown silicon nanowires through a variety of methods such as vapour-liquid-solid, laser ablation, chemical vapour deposition (CVD) and molecular beam epitaxy (MBE), or lithographic methods on SOI wafers, all of which produce high quality single crystal samples [24].

Figure 2.15: *Left*) Conventional silicon based planar solar cell.  $n^+$  and  $p^+$  regions serve to reduce minority carrier surface recombination. Silver fingers collect electrons generated from absorption of light. Anti-reflection coating improves absorption by reducing reflectance of incident light. *Right*) Radial PN junction based solar cell (concept).

## 2.2. Fibres and Fabrication

Waveguides are one of the major applications of fibres. Waveguides serve as infrastructure for communication around the planet, with most high bandwidth connections facilitated by optical fibres. Optical fibres have also become very useful in many other areas, including sensors, lasers, and lighting. They have advanced our understanding of light and ability to manipulate light. This section will provide a brief overview on optical fibres and current production techniques of semiconductor core fibres.

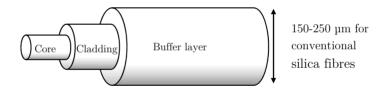

Fibres are commonly known to be thin multi-layered concentric cylindrical wires. At the simplest level a difference in refractive indexes between the core and layer surrounding the core known as the cladding is responsible for the waveguide effect. A simple fibre illustrating the different layers of components is shown in Figure 2.16.

Figure 2.16: Schematic of the different layers within a conventional fibre.

The key mechanism behind the propagation of light in an optical fibre is the relative difference in refractive index. Conventional fibres are almost completely produced from silica due to the commercial availability, established manufacturing processes, and its performance in the mid-IR range [2]. Although complex compositions are used as well depending on the application and wavelength used. Propagation of light is mostly confined to the core although some of the field binds to the cladding. Commercial fibres are protected from weathering and given increased strength by a buffer layer on the outside. Fibres produced as a part of this research do not include a buffer coating.

Semiconductor core fibres share its structural makeup with that of silica optical fibres. Incorporating semiconductors in fibres have only been recently explored and made possible by constantly improving manufacturing processes of optical fibres. Silicon core fibres have become popular in research after the ability to draw continuous fibres with relatively low attenuation [25]. One advantage of combining semiconductors and optical fibres is the possibility of new integrated electronic optical devices; currently there is a disconnect between the transport and the processing of light. In addition, silicon core fibres may have applications in PV.

#### 2.2.1. Current Techniques

To date focus has been on Si and Ge core optical fibres. Silicon has the potential to define a new class of optical fibres focusing on IR transmission and non-linear optics due its transparency in the mid-IR [25]; research into these fibres have focused on transmission at 1.55µm as it is within the silicon's transmission window. The wavelength appears promising for research with silicon fibres because of the availability of optical components and lasers developed for telecommunications [26]. This section explores methods of silicon core fibre fabrication.

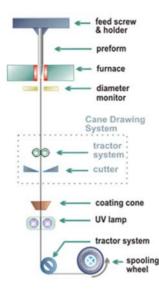

#### 2.2.1.1. Molten Core Drawing

The molten core drawing method is similar to the method used to pull conventional optical fibres. A preform consisting fibre materials scaled to larger dimensions is placed into a furnace. The furnace is heated to around to near the melting temperature of the glass (between 1900°C and 2200°C) [2]. At this point the silica will become soft enough to start stretching under its own weight, known as 'creeping'. When this initial deformation has stretched far enough, the mass at the end is stopped and the heat is turned off. The end is fed through a set of rollers. The rollers enable the pulling force to be changed while controlling the slack. Other equipment consists of a laser measurement system, polymer coater and UV curing stages. The preform is heated again, and when it has reached the correct temperature the rollers being to pull causing a fibre to form. The molten core drawing method is a batch process, limited by the dimensions of preform and conservation of mass. Hundreds of kilometres of fibre can be drawn from a single preform. This pulling method is illustrated in Figure 2.17.

Figure 2.17: Commercial fibre drawing process for conventional silica based fibres. A preform is heated and pulled. The diameter is monitored in-situ by a sensor. The process is continuous and can be tailored to produce fibres of a certain length and diameter [27].

Ballato et al. from Clemson University has developed and progressed research into fabricating solid silicon core optical fibres using the 'molten-core' crucible method; the method is the main method of fibre production for this work. The molten-core method involved placing a poly or monocystalline rod inside the hollow core of a glass rod and drawing while heating the preform. There is nothing fundamentally limiting about this technique in the application of semiconductor cored fibres, however, small dimensional photonic crystals are not possible due to diffusion issues [25]. The production of fibres relies on localized heating of the preform and pulling near the draw temperature. Silicon melts at 1414°C whereas, silica draws at about 1950°C. Theoretically, matching the cladding draw and the core melt temps would alleviate some issues with fibre production that results from the thermal expansion of silicon into the surrounding silica cladding. However, silica remains popular as it is commercially available and has high tensile strength. One benefit of having such a low viscosity melt (large difference in the cladding draw temperature and the core melting temp temperature) is that the core material flows easier, which produces turbulence within the core. It conforms to the shape of the container and can produce good continuity [5]. The oxygen content in the core was found to correlate to core diameter, with greater oxygen content occurring with smaller diameter cores [5]. The dissolution of cladding into the Si core has been a problem in previous research that has shown relatively high oxygen content in some cases [5, 28]. There is a large negative free energy change corresponding with  $SiO_2$  formation as shown in an Ellingham diagram, which means that silicon oxidizes with a greater driving force than other elements. However, certain oxides (i.e. Ca and Mg) exhibit even lower free energy change. Previous characterization of silicon core fibres show an interesting feature in elemental distribution, a relatively flat profile for each element, whereas a more gradual change in composition would be suspected due to compositional gradients. The homogenization is thought to arise from: [25]

- Turbulent flow during the pull

- Chemical gradient due to the diffusion of oxygen in the cladding

- Thermal gradient from the small size of the heat zone

- Flow induced gradient arising from the pull

Nordstrand et al. has suggested that incorporating a modifying layer at the silica/silicon interface inhibits dissolution the cladding layer and relieves some thermal stress by forming a eutectic between CaO and Si [29]. Mechanical behaviour of fibres produced using this method seem to show improved toughness.

X-ray diffraction on the fibre cores showed a high degree of crystalline and phase purity; crystallinity was estimated to be >67% for silicon fibres produced by the molten core method [25]. Thermodynamics is thought to govern this process, rather than kinetics to produce the degree of crystallinity found in the core. Small oxygen precipitates should disrupt the solidification process and nucleate different orientations of Si in the core, suggesting that the majority of the core solidified by homogenous nucleation [25]. The molten core method is associated with relatively high growth rates. Growth rates of some crystal growth methods are included for completeness in Table 2.3.

| Crystal Growth Technique            | Growth Rate   | Relative Rate    |

|-------------------------------------|---------------|------------------|

| Hydrothermal                        | $\sim mm/day$ | ~1               |

| Czochralski                         | ~mm/h         | ~25              |

| Micro-pull                          | $\sim mm/min$ | ~1000            |

| Laser-heated pedestal growth (LHPG) | ~mm/min       | ~1500            |

| Molten Core (thick)                 | $\sim$ m/min  | $\sim 1 500 000$ |

| Molten Core (thin)                  | ~m/sec        | ~20 000 000      |

Table 2.3: Relative growth rates for various crystal growth methods [25].

#### 2.2.1.2. Micro-structured Optical Fibre (MOF)

Work from Penn state and South Hampton University used a silane/helium mix to deposit Si into hollow silica in a pressurized chemical vapour deposition (CVD) process, which creates micro-structured optical fibres (MOF) [25]. Their method produces highly amorphous silicon on the silica boundary. High loses at 50dB/cm at a wavelength of 1550nm were reported for the amorphous sample. However, loses improved with high temperature annealing and larger wavelengths. The lowest loss was around 5dB/cm at 1550nm [25]. The process to create these fibres are complex and difficult, thus it is desirable to employ a less complicated route.

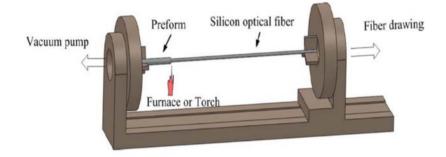

#### 2.2.1.3. Powder-in-Tube Method

Scott et al. has experimented with the powder-in-tube method to produce silicon cored fibres [30]. The powder-in-tube method involves crushing silicon using pestleand-mortar into small pieces, essentially creating a Si powder and using it as the main source of silicon. The powder is loaded into a hollow silica tube and evacuated prior to pulling to limit Si oxidation. The preform is heated while rotating to produce uniform heating. Once the drawing temperature of ~1600°C was reached, the preform was pulled to produce a fibre. Interestingly, Energy dispersive spectroscopy (EDS) showed that the core was comprised mainly of silicon, with very little oxygen while the cladding consisted of a silicon and oxygen mix [30]. However, the fibre products suffered high losses that are thought to be caused by thermal expansion induced micro-cracks and large grained polycrystallinity along the fibre axis. It showed loses ranging from 4-5.5 dB/cm[30]. Previous work from Dibbs et al. has found that the process incorporates impurities into the fibres, raising the uncertainty of commercial viability [29]. Figure 2.18 shows the pulling method used by Scott et al..

Figure 2.18: Powder-in-Tube method used by Scott et al. A vacuumed preform is heated while rotating and pulled to produce a silicon core fibre [30].

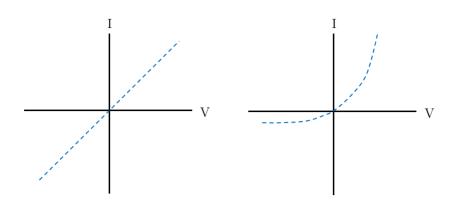

# 2.3. Metal to Semiconductor Junctions

Ohmic contacts are important in situations where current rectification is undesirable, such as measuring electrical properties of a material. Ohmic constant occurs when the majority carrier is allowed to pass unimpeded through an interfacial region regardless of current direction, i.e., contacts do not limit the current and follow Ohm's law. This is in contrast to rectified, Schottky type contacts that allow a carrier to pass in only one direction, such as in diodes. An Ohmic contact gives a linear I-V relationship regardless of current direction. The only current present during reverse bias in a Schottky contact is due to minority carrier drift. Figure 2.19 shows a qualitative difference between Ohmic and Schottky I-V relationship.

Figure 2.19: Left) Ohmic I-V behaviour. Right) Schottky I-V behaviour (arbitrary units).

Contacts are extremely important in the context of metal-semiconductor interfaces as there is a mismatch between the Fermi level and carrier bands. When in contact, the valence and conduction bands of the semiconductor will undergo 'bending' to achieve potential energy equilibrium with the metal. According to the Schottky model Ohmic contact is formed when there is a zero or negative Schottky barrier height,  $\Phi_{B}$ . The model predicts the type of contact between a metal and a semiconductor, which is independent of the semiconductor doping concentration. The Schottky barrier height is defined as the relative difference between the work function of the metal and the work function of the semiconductor. That is [31]:

$$\Phi_{B} = \Phi_{M} - \chi_{SC} \tag{2.12}$$

Where  $\Phi_M$  is the work function of the metal and  $\chi_{SC}$  is the electron affinity of the semiconductor. (2.12) is commonly known as the Schottky-Mott Rule. Schroder has devised a naming convention for the different contact types according to the Schottky Model [31]:

- Accumulation:  $\chi_{sc} > \Phi_{M}$ . Preferred for Ohmic contact

- Neutral:  $\chi_{SC} \sim \Phi_M$

- Depletion:  $\chi_{SC} < \Phi_M$  preferred for Schottky contacts.

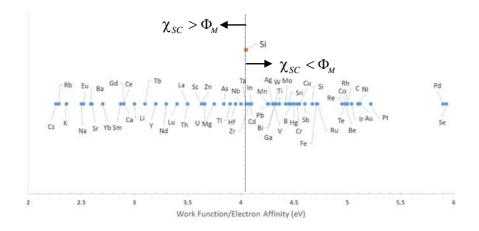

A list of work functions for some common metals is elements is shown in Figure 2.20.

Figure 2.20: Work functions of various metals compared to electron affinity of Si [32].

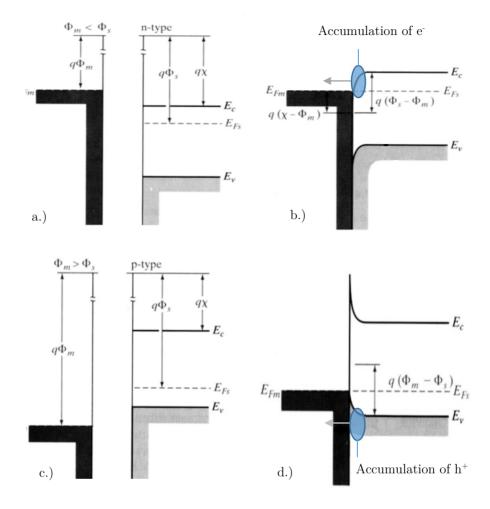

The effect on conduction and valence bands at a metal/semiconductor interface for and n- and p-type materials assuming accumulation type contact is displayed in Figure 2.21.

Figure 2.21: Band Diagrams of Ohmic metal-semiconductor contacts a.) n-type (separated) b.) n-type (in contact) c.) p-type (separated) d.) p-type (in contact). Modified from [19].

Upon contact, the electrostatic potential of the semiconductor develops an equilibrium with the metal, which aligns the Fermi level. In both cases, there is an accumulation of the majority carrier near the interface that allows the carrier to cross the boundary. This is because the carrier concentration is higher than that of the bulk, which causes the resistance in the contact region to be low [33]. Thus, there is little or no potential barrier in either direction.

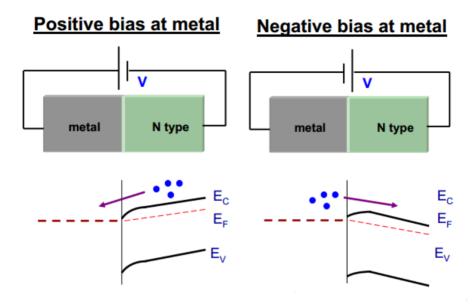

In applications such as resistivity measurements, a potential bias is applied that changes the behaviour of the bands slightly. An application of a potential will bend the bands towards the potential. An example of positive and negative bias applied to a metal-semiconductor (n-type) is shown in Figure 2.22.

Figure 2.22: Positive and Negative bias of a metal-semiconductor (n-type) junction. A applied potential bends the band edges to form either a depletion or accumulation region for the majority carrier [33].

A positive bias will cause both carriers to easily cross the boundary. However, an application of negative bias will create an electron reservoir at the interface that creates a region of high concentration, which allows the carriers to flow over the boundary due to diffusional energy. The case shown in Figure 2.22 involving an n-type system. The same scenario will be true given a p-type system, however the relationships will be reversed.

The above discussion involves creating accumulation type contacts. In many situations  $\Phi_M > \chi_{SC}$ , yet an Ohmic contact is still desired. In this situation, a depletion region is formed near the interface. Positive charges from uncompensated donor ions within the semiconductor moves toward negative charges in the metal forming a small electric field near the interface, which bends the bands, forming the depletion region [19]. One practical method to alleviate this issue is by heavy doping

near the semiconductor interface.  $\Phi_{\scriptscriptstyle B}$  may be positive and still show an Ohmic relationship if, the depletion region is small enough to allow carrier tunnelling. The width of the region is inversely proportional to the donor concentration:  $W \propto \frac{1}{\sqrt{N_{_{D/4}}}}$  [33]. Where  $N_{_{D/A}}$  is the donor or acceptor concentration. This effect

is naturally realized for aluminium contacts deposited on p-type silicon after an high temperature annealing process. The aluminium acts as an acceptor type dopant in silicon, effectively causing a p<sup>+</sup> interfacial layer.

It has been experimentally observed that the barrier height of some semiconductors including Si, Ge, GaAs and other III-V compound materials are largely independent of the metal work function and doping density; however, as stated previously, barrier width does depend on doping density [31]. Interface states are created inside the bandgap of the semiconductor, effectively pinning the Fermi level: Referred to as "Fermi-level pinning" [19]. These types of contacts are generally form depletion type contacts, which means there is a positive  $\Phi_B$ . It is believed that imperfections at the material surface causing a large increase of surface states, but the true nature of barrier formation is still contested [31]. Depletion contacts are formed on both pand n-type materials are experimentally determined to be [34]:

$$\Phi_{Bn} \approx \frac{2E_g}{3} \tag{2.13}$$

$$\Phi_{Bp} \approx \frac{E_s}{3} \tag{2.14}$$

$E_g$  represents the band gap of the material. For silicon,  $\Phi_{Bn}\approx$  0.74eV and  $\Phi_{Bp}\approx$  0.37eV.

To complicate things, the true barrier heights have been shown to vary with natural oxide thickness and are dependent on many other factors, such as surface quality. Card et al. showed that the native oxide on silicon pins the Fermi level, effectively lowering  $\Phi_{Bn}$  to ~0.4eV, low enough to potentially allow tunnelling through the junction [35];  $\Phi_{Bn}$  is shown to decrease with increasing oxide thickness (up to 20nm), while  $\Phi_{Bn}$  has been shown to increase with oxide thickness. This behaviour

was shown for samples that were not heat-treated using a high temperature anneal process. In high temperature anneals, the diffusion of Al into n-type Si caused the barrier height to rise substantially and produce rectifying behaviour [35]. A thorough treatment of aluminium-silicon contacts is given by Card in which he gives current J, as a function of oxide thickness d, temperature T, voltage V, barrier height  $\Phi_{_B}$ , and tunnelling probability  $\Psi^{1/2}$  [35]:

$$J = J_{sat} \left( \exp\left(\frac{qV}{k_B T}\right) - 1 \right)$$

(2.15)

Where:

$$J_{sat} = AT^2 \exp\left(-\Psi^{1/2}d + \frac{\Phi_B}{k_B T}\right)$$

(2.16)

A is the modified Richardson constant ( $\sim 115$  electrons).

There are two ways to create an Ohmic contact between a metal and silicon. Either  $\Phi_{B}$  is low (~0.3eV) causing the saturation current to rise, or silicon is heavily doped so that W < 10 nm and is easily tunnelled through [35]. Of course, a material with low resistivity, thermal stability, good adhesion, and a smooth morphology is preferred when making Ohmic contacts for electrical applications. In real-world applications of making contacts, it is difficult to apply theoretical treatments due to its sensitive nature. Typical materials used in industry to create Ohmic contacts with silicon are shown in Table 2.4.

| n-type Si | p-type Si |

|-----------|-----------|

| Ag        | Al*       |

| Ni        | Au        |

| $Pt^*$    | Pt        |

| Au-Sb     | Au-Ga     |

| Al        |           |

Table 2.4: Commonly used materials for Ohmic contacts in Si [31, 36-39].

\*under certain conditions such as high dopant density  $({>}10^{18} {\rm cm^{-3}})$  or high temperature anneal.

# 2.4. Characterization Techniques

#### 2.4.1. Four Point Probe (4PP)

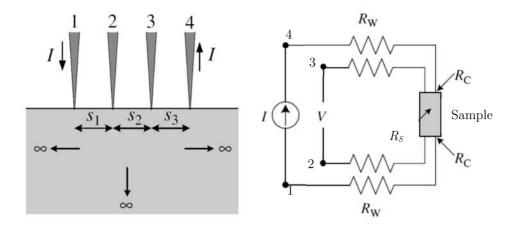

The four point probe (4PP) is a common method to measure electrical impedance in the semiconductor industry. Using a 4-terminal setup, the 4PP can directly measure sheet resistance by measuring a voltage drop across a terminal separation distance. In the 4-terminal mode, a voltage drop is measured by two current neutral terminals held within a collinear and equally spaced active terminals. The benefit of a 4-terminal setup is separation of the current and voltage means there is virtually zero current flowing through the inner sensing electrodes, which limits its contact resistance to virtually zero. A schematic of the 4PP setup is shown in Figure 2.23.

Figure 2.23: Left) Diagram of 4-terminal head on a semi-infinite sample illustrating head spacing. Right) Equivalent electrical circuitry of a 4PP setup. Rs represents measured resistance, while R<sub>c</sub> is the contact resistance on the active current heads [31].

Current, voltage drop, and resistivity are related by Ohm's Law. Given in vector form:

$$\mathbf{J} = \mathbf{\sigma} \mathbf{E} \tag{2.17}$$

Where J represents current density,  $\sigma$ , the conductivity, and E, the field strength.

#### 2.4.1.1. Semi-infinite Samples

Wafers and relatively large samples where the dimensions are large compared to probe spacing are considered semi-infinite samples. The relationship between voltage, current, and resistivity depends highly on the shape of the sample being measured. In the semiconductor industry, wafers and semi-infinite planar samples are popular and 4PP measurements are regularly used to characterize resistivity.

Assuming an isotropic system in (2.17), where  $S_1 = S_2 = S_3$ , and a semi-infinite sample one can derive that [31]:

$$\int_{0}^{V} dV = \int_{0}^{r} \left(\frac{I\rho}{2\pi r^{2}}\right) dr$$

$$\rho = 2\pi S \frac{V}{I}$$

(2.18)

Where I represents current, S the electrode spacing, V is the voltage drop, and  $\rho$  is the resistivity of the material. Eq. (2.18) assumes a semi-infinite sample size, however, when the sample thickness, t<S, or the electrode placement is an edge, a correction factor, F must be applied. Eq. (2.18) becomes [31]:

$$\rho = 2\pi S \frac{V}{I} \cdot F \tag{2.19}$$

F has been examined using Carbino sources, Poisson's Equation, Green's Functions and conformal mapping. A detailed derivation of correction factors is given by Weller [40]. F can be written as a product of independent factors.

$$\boldsymbol{F} = \boldsymbol{F}_1 \boldsymbol{F}_2 \boldsymbol{F}_3 \tag{2.20}$$

$F_1$  represents a contribution from sample thickness,  $F_2$  the contribution for lateral sample dimensions, and  $F_3$  the placement of probes relative to sample edges. Calculation of the correction cofactors is difficult and their equations usually simplify. This is the case with the sample thickness cofactor,  $F_1$ . If  $t / s \leq 0.5$ , and the sample is on an insulating substrate,  $F_1$  approximates to [31]:

$$F_1 = \frac{t/s}{2\ln(2)}$$

(2.21)

One can see that in general, this process quickly becomes complex as the sample size decreases, or for oddly shaped samples.

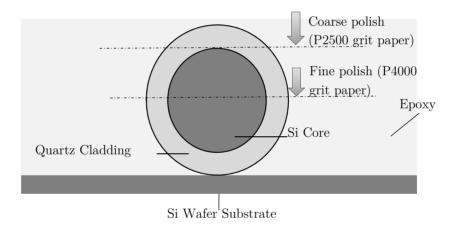

#### 2.4.1.2. Small Cylindrical Samples

For a small cylindrical shaped samples such as fibres, the electrical field can be assumed to be uniform along the longitudinal axis of the cylinder. This assumption leads to a simplified expression relating voltage, current, probe spacing and resistivity.

$$E = -\nabla \Phi(x)$$

$$= \frac{-\Delta \Phi(x)}{S}$$

(2.22)