# Exploring the Use of IP-XACT in a TLM Environment

Eirik Prestegårdshus

Master of Science in Electronics Submission date: June 2017 Supervisor: Kjetil Svarstad, IES

Norwegian University of Science and Technology Department of Electronic Systems

# **Problem Description**

Title: Exploring the Use of IP-XACT in a TLM Environment

Date: 18.06.2017

Student: Eirik Prestegårdshus

Academic Supervisor: Kjetil Svarstad

Corporate Supervisors: Conrad Foik, Junaid Elahi

The IP-XACT standard presents a methodology to store metadata of electronic components. There are increasing efforts to automate design flows, which leads to metadata methodologies becoming increasingly valuable to the industry. IP-XACT's analysis consist of both the methodologies and the format to store the metadata.

The goal of this thesis is to explore the viability of using IP-XACT in the design flow, and additionally its relevance to a transaction-level modelling (TLM) environment. Research includes study, experimentation and analysis of IP-XACT.

The problem is provided by Nordic Semiconductor ASA.

# Preface

This Master thesis is the final work of my Master's Degree in electronics at Norwegian University of Science and Technology (NTNU). The work is carried out at the Department of Electronic Systems. The project has great relevancy to the education, especially to the last few years sporting a more digital approach. The six months researching the thesis has been a very interesting journey, which has helped to grasp an understanding of one of the back-end systems in the industry. The project is proposed by Nordic Semiconductor ASA, which also provides all equipment and a workplace.

First and foremost, I would like to thank Conrad Foik for outstanding support and feedback to all aspects of the thesis. Without his advice, the study, discussions nor thesis would be nearly as interesting as it have become. Furthermore I would like to thank J. Elahi and L. H. Olsen for an insight to methodologies at Nordic, together with all other colleagues at Nordic that made the months of study and writing much easier to get through. I would also like to thank Vincent Thibaut for taking the time to answer many of my questions regarding the standard.

At last, I would like to express my true gratitude to my academic tutor Kjetil Svarstad who, albeit a very tight schedule, provided good feedback, rewarding meetings and generally kept me on track.

Sincerely,

Eirik Prestegårdshus, June 11th, 2017

# Abstract

As both semiconductor technology and industry evolves, the need for robust methodologies and efficient design flows becomes more and more important. This thesis investigates IP-XACT, which is a standard that describes metadata of electronic systems aimed at computer-aided designs. The thesis emphasises methodologies of IP-XACT, as well as the overall structure and execution of said methodologies.

The thesis carries out an experiment where IP-XACT is used with transactional-level modelling (TLM). The experiment emphasises methodologies, implementation and structure of the standard. IP-XACT fully accomplishes to describe a component's metadata, and additionally serve as very valuable to the entire design flow and as a back-end metadata organisation. Study and experimentation show the methodologies and core metadata description to be strong concepts, but criticise lacking vendor neutrality and an unintuitive mixed-model structure. To solve the discovered weaknesses, the thesis proposes an alternative model that restructure elements that describe information specific to models (like TLM).

IP-XACT is ready to be used in the design flow, but is still a subject of development, thus feedback can prove very valuable for future versions. IP-XACT seemingly has a positive future to come, especially with the industry being more reliant on computer-aided design flows to achieve higher levels of efficiency.

# Sammendrag

En voksende halvleder teknologi med tilhørende industri gjør at robuste metoder og effektive designsykler blir viktigere og viktigere. Denne avhandlingen undersøker IP-XACT, som er en standard som beskriver metadata for elektroniske systemer rettet mot datastyrte design. Avhandlingen vektlegger metodikken til IP-XACT, samt generell struktur og utførelse av nevnt metodikk.

Avhandlingen utfører et eksperiment hvor IP-XACT brukes sammen med en model på transaksjonsnivå (TLM). Forsøket vektlegger metodikk, implementering og struktur av standarden. Observasjoner viser at IP-XACT beskriver komponenters og systemers metadata på en bra måte, og fungerer bra som en singel kilde for metadata i designflyten. Studier og eksperimentet viser metodologien, ideene og kjernestrukturen som sterke konsepter, men kritiserer manglende leverandør-nøytralitiet og en lite intiutiv struktur for å beskrive forskjellige implementasjonsmodeller. For å løse de oppdagede svakhetene, foreslår avhandlingen en alternativ modell som omstrukturerer elementene som beskriver spesifikke implementasjonsmodeller (som TLM).

IP-XACT er klar til å brukes i designflyten, men blir fortsatt utviklet og forbedret, derfor kan tilbakemeldinger bringe store verdier for fremtidige versjoner. IP-XACT har tilsynelatende en positiv fremtid fremfor seg, særlig ettersom industrien blir mer avhengig av en datastyrt designflyt for å oppnå høyere effektivitet.

# **Table of Contents**

| PROBLEM DESCRIPTION                        | III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PREFACE                                    | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ABSTRACT                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ABBREVIATIONS                              | XIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| INTRODUCTION                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.1 SCOPE OF THE THESIS                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.2 REPORT ORGANISATION                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| THEORY                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1 EXTENSIBLE MARKUP LANGUAGE             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2 IP-XACT                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.3 TRANSACTION LEVEL MODELLING            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.4 LEON2                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| EXPERIMENT                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1 METHODOLOGY                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.2 Setup                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.2.1 RNG Module                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.3 TLM IMPLEMENTATION                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.4 TOOLS                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| EXPERIENCES                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.1 METHODOLOGY                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.2 STRUCTURE                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.3 THE EXPERIMENT                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.3.1 RNG Module                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.4 MODEL PROPOSAL                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DISCUSSION                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.1 SCOPE OF IP-XACT                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.2 METHODOLOGY                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.3 STRUCTURE                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.4 VENDOR NEUTRALITY                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.5 IP-XACT TLM SUPPORT                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.6 GAIN VERSUS COST, INDUSTRY PERSPECTIVE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.7 TOOL SUPPORT                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                            | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.8 MODEL PROPOSAL                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.8       MODEL PROPOSAL                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                            | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.9 FUTURE PREDICTIONS                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.9 FUTURE PREDICTIONS<br>CONCLUSION       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.9 FUTURE PREDICTIONS                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                            | PREFACE         ABSTRACT         SAMMENDRAG         ABBREVIATIONS         INTRODUCTION         1.1         SCOPE OF THE THESIS         1.2         REPORT ORGANISATION         THEORY         2.1         EXTENSIBLE MARKUP LANGUAGE         2.2         IP-XACT         2.3         TRANSACTION LEVEL MODELLING         2.4         LEON2         EXPERIMENT         3.1         METHODOLOGY         3.2         SETUP         3.2.1         RNG Module         3.3         TLM IMPLEMENTATION         3.4         TOOLS         EXPERIENCES         4.1         METHODOLOGY         4.2         STRUCTURE         4.3         THE EXPERIMENT         4.3.1         RNG Module         4.4         MODEL PROPOSAL         DISCUSSION         5.1       SCOPE OF IP-XACT         5.2       METHODOLOGY         5.3       STRUCTURE         5.4       VENDOR NEUTRAL |

# Abbreviations

- API Application Programming Interface

- CAD Computer-Aided Design

- EDA Electronic design automation

- GNU GNU's Not Unix

- GPL GNU Public License

- HW Hardware

- IP Intellectual Property

- LGPL Lesser GNU Public License

- OSCI Open SystemC Initiative

- OVM Open Verification Methodology

- RNG Random Number Generator

- RTL Register transfer level

- SAM System Architecture Model

- SOC System-On-a-Chip

- SW Software

- TLM Transaction Level Modelling

- UVM Universal Verification Methodology

- VHDL Very high speed Hardware Descriptive Language

- VLNV Vendor Library Name Version

- XML eXstensible Markup Language

# **1** Introduction

More than fifty years ago Moore's Law predicted that the number of transistors per area grows exponentially every two years. The law still holds true today, and according to the industry, it will continue to be valid for the next couple of decades [1]. From a digital perspective, this means that more complexity will be packed into each chip. There is fierce competition in the semiconductor market, which follow this exponential trend. As complexity rises, design methodologies and design flow become more and more important. Time-to-market is an important factor as the technology evolves, and staying behind in design methodologies may lead to a company's downfall [2]. To tackle the growing complexity while keeping a competitive edge requires an efficient design cycle is required to keep up with aggressive schedules. IP-XACT proposes a solution to the problem, which emphasizes reuse and design integration, as well as a unified design methodology. The high complexity also pushes the need for the designer to take correct design decisions early in the design cycle, which is where IP-XACT is the most prevalent.

This thesis investigates IP-XACT, and its impact on the design flow methodologies. IP-XACT is a standard that describes component metadata conveniently for a computeraided design (CAD) flow [3]. IP-XACT emphasizes reuse of existing components for a more unified and efficient design cycle. This thesis experiments with IP-XACT implemented with a Transaction-Level Modelling (TLM) design. TLM has the value of a higher abstraction that enables quicker and easier experimentation compared to RTL [4]. The experiment shows IP-XACT generally interpreted in a design flow and how it contributes to the TLM design flow specifically. TLM is likely to be less known for the front-end designer than RTL, but TLM's importance grows proportional to the complexity of designs and future predictions depict TLM to be a necessity for large-scale designs [5]. IP-XACT's level of abstraction is particularly interesting when applied to system-on-a-chip (SOC), aka large-scale designs, which makes the two a good match for research.

Important areas of research comprise of how IP-XACT can contribute to the design and increase design productivity. IP-Reuse and IP integration are two significant aspects of IP-XACT, it is important to emphasize how the standard implements those two. IP-XACT released in 2004, but is still a subject of further development [6], so there are multiple changes and additions coming in the future. The recent changes targets support for more complex system representation and conveniently adds more support for TLM. Chip complexity is only increasing in the future, thus the thesis also aim to lightly discuss future projections for IP-XACT. The contributions of this thesis are research and analysis of IP-XACT, an IP-XACT/TLM experiment, and discussion regarding IP-XACT in general, its application to the world and its internal structure.

## 1.1 Scope of the thesis

The scope of the thesis is IP-XACT within a TLM environment. Both IP-XACT and TLM are tightly coupled with RTL. However, this thesis will only discuss RTL lightly and experiment solely with IP-XACT and TLM. The reason behind that is that the representation of a component described by its metadata are almost the same whether the model is TLM or RTL. TLM provides the benefit of being faster to implement and simulate, also in a simpler and more accessible way than the RTL counterpart. The experiment does not aim to perform complex in-depth TLM experimentation, but discusses aspects where IP-XACT can provide benefit for a more in-depth TLM implementation along its use in the current setup.

The thesis emphasises the general design flow and methodology of IP-XACT. The design flow presented in this thesis is a simplified version of one in the industry, but still resembles many of the same cases and problems present to the industry. The thesis often discuss from a designer's point of view, meaning a designer that presumably works in a stage of the design cycle at a company. The thesis often use the wording *complexity* as a measure. In theory, complexity is the amount of functionality contained within a defined design space, but functionality can be interpreted both user-friendly and hard to understand; the impression of *complexity* changes accordingly.

IP-XACT is not coupled to any one language nor vendor, yet IP-XACT is only used in conjunction with a tool. The thesis aim to discuss the standard itself and not the tools that use it. The investigation of IP-XACT properties derive entirely from IEEE 1865-2009/2014 standards, and will to a lesser degree emphasise what may be added through *vendorExtension*. The core of the thesis' scope is to present IP-XACT's strengths and weaknesses, and more specifically in a TLM setting. To aid the discussion and demonstration of the standard; the thesis make use of an experiment.

# 1.2 Report Organisation

The report is divided into Theory, Experiment, Experiences, Discussion and Conclusion. The Theory provides relevant background information for XML, IP-XACT, TLM and the processor used in the experiment. The Experiment presents methodologies of design flow and setup of the experiment. Experiences describes observations from the structure and methodologies and observations of the experiment. Discussion is the main body of the thesis. The Discussion debates the methodologies and interpretation of IP-XACT both as ideas and execution, and from multiple angles. Lastly, Conclusion brings all of the results and discussions together to form a verdict to IP-XACT's current and future situation.

# 2 Theory

This chapter gives essential background information regarding the systems and methodologies used by the thesis. It introduces IP-Reuse, theory of the used programming languages, methodologies in TLM and the environment of the experiment.

IP-Reuse, as the name suggests, is to reuse a part of the design previously created by others. Others may refer to people within a design group, within a company or from an external provider. When talking about IP-Reuse there are two terms one should know, the types of Intellectual Property (IP) [7]. An IP can be delivered/described as either soft-IP or hard-IP. Soft-IP is synthesisable HDL [8], which means the internals can be viewed, debugged and potentially edited. According to the providers' licenses, one might not be allowed to edit the delivered code. The other deliverable is hard-IP, an IP described as technology specific layout that cannot be viewed nor altered. IP-Reuse most commonly refers to soft-IP, and this thesis further assumes IP-Reuse linked to soft-IPs. Furthermore, since the focus of the thesis is TLM, the soft-IP in the experiment describes in compileable SystemC [9], not synthesisable HDL.

### 2.1 Extensible Markup Language

Extensible Markup Language (XML) [10] defines a markup language that describes rules for encoding structured data. The specification of XML is governed by World Wide Web Consortium (W3C) [11], and serve as a worldwide standard. XML's goal is to be simple and to serve many purposes, as well as being easily readable by both humans and machines. XML has been widely adopted by the internet, and numerous XML schemas leverage data transfers across the web [12].

XML is like programming languages in the way that it has syntax that must be followed. However, XML and programming languages differ in the way they are used; XML is not executable. XML is merely a format to store information. The language is a textual language where the markups are tags. A tag can store information and have child tags, which frequently are structured hierarchically as trees. This thesis often use the wording element when describing a tag with its underlying tags. The format that defines allowed tags, and how they are structured are called a schema. IP-XACT is one of many standardised XML schemas.

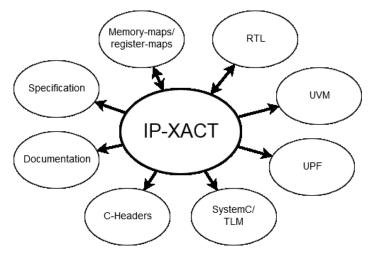

# 2.2 IP-XACT

IP-XACT is an XML Schema that describes the structure of metadata in and about electronic components. IP-XACT is an open industry standard that goes by the code *IEEE 1685, Standard for IP-XACT, Standard Structure for Packaging, Integrating and Re-Using IP Within Tool-Flows* [13]. SPIRIT Consortium initially created IP-XACT in 2003, and as of 2009 SPIRIT merged with Accellera [14]. In June 2010 IP-XACT became an IEEE [15] standard, IEEE-1685 [13]. IP-XACT is currently being worked on

by Accellera's working group, which has members across multiple big companies such as ARM [16], Magillem [17] and Xilinx [18]. The working group has lately developed a set of extensions for IP-XACT to describe analog/mixed-signal/digital designs, area estimates and support for power descriptions [6].

IP-XACT is able to describe the entire design, and splits design into eight different toplevel elements. The following list describes each of the elements, be aware that additional top-level descriptions might be added in the future. The list below describes all the elements with a short description.

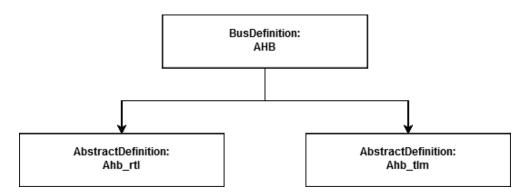

- A *bus definition* description defines the type attributes of a bus.

- An *abstraction definition* description defines the representation attributes of a bus.

- A *component* description defines an IP or interconnect structure.

- A *design* description defines the configuration of and interconnection between components.

- An *abstractor* description defines an adaptor between interfaces of two different abstractions.

- A generator chain description defines the grouping and ordering of generators.

- A *design configuration* description defines additional configuration information for a generator-chain or design description.

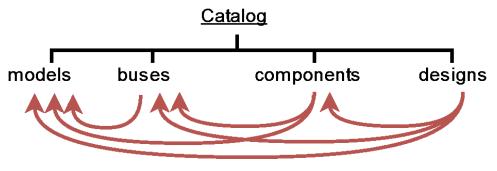

- A *catalog* description provides a mapping between IP-XACT VLNVs<sup>1</sup> (see 1.3.3) and the physical location of the IP-XACT file defining the IP-XACT object with the given VLNV.

#### IEEE Std 1685<sup>TM</sup>-2014 [13]

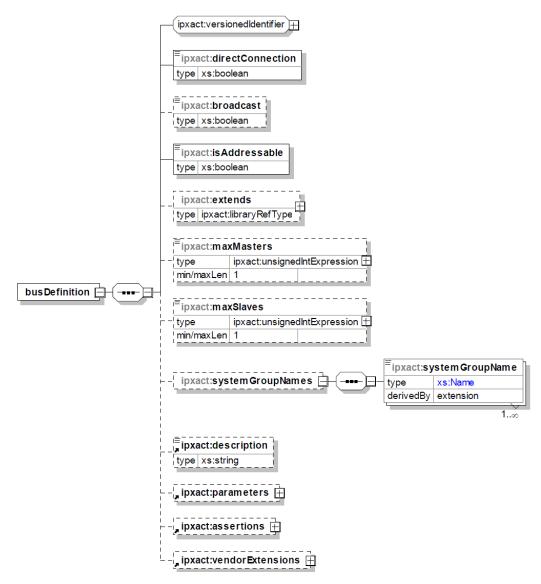

XML allow IP-XACT to store data in a tree like structure. Figure 2-a describes the *busDefinition* element with all the possible sub-elements; elements with dotted boxes are optional. A set of checkers can run through each element to validate correctness of the contained data.

<sup>&</sup>lt;sup>1</sup> Vendor Library Name Version (VLNV) is an identifier to uniquely reference an electronic component. They are often described as strings with colon as separators, an example of such VLNV may be *amba.com:AMBA3:AHBLite:r1p0\_6*.

Figure 2-a busDefinition xml-element [13]

#### 2.3 Transaction Level Modelling

Transaction Level Modelling (TLM) [19] is a way to describe an IP in abstraction levels above RTL. TLM uses function calls (transactions) to represent RTLs pins, signals and actions. Individual design teams might not see the benefit of TLM at first, but it is very beneficial as a top-down approach, especially from a system architecture point of view [4]. TLM enables architectural modelling, algorithmic modelling, virtual development platform and functional verification with much faster simulation speeds than RTL. These provide benefits as earlier software development, earlier hardware functional verification and a clear path from customer specifications to detailed software and hardware design.

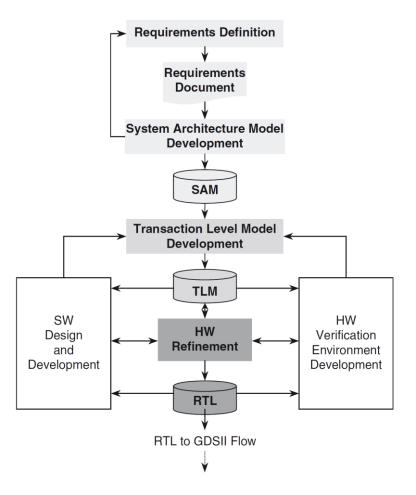

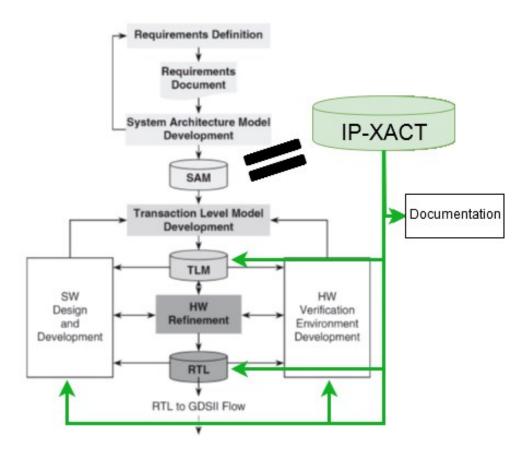

Figure 2-b Design flow with a TLM environment [4]

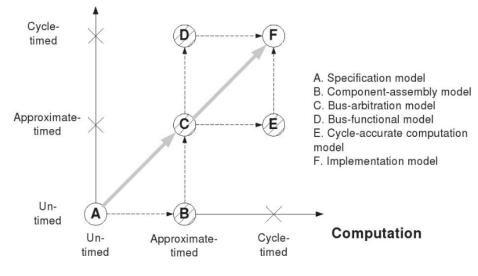

Figure 2-b above display a design flow with TLM interpreted. The TLM model work as a reference model between hardware and software teams. The lowest level of abstraction is the System Architecture Model (SAM), an untimed, point-to-point model to describe the system as high-level block diagrams. GDSII is a format for rendering the physical chip layout, so the arrow pointing downwards describes RTL to chip-layout/chip production. In Figure 2-c, the RTL model equals **F**. Implementation model, while SAM is **A**. Specification model. Everything in between is considered functional TLM.

#### Communication

Figure 2-c Transaction Level Modeling [20]

A TLM design flow usually moves through multiple models, where each model should functionally correspond to the predecessor. To run functional verification and performance modelling one must at least be using an approximate timed model, whilst SAM is sufficient for simple architectural modelling.

TLM is generally an idea of a system that uses transactions to pass messages around. To use TLM, a programming language that has such a transaction implementation must be used. Usually TLM is a library building upon the underlying programming language. Programming languages that has available libraries include SystemC [9], SystemVerilog [21] and Matlab [22]. Universal Verification Method (UVM) [23] and Open Verification Method (OVM) [24] are the common methods of using TLM in SystemVerilog, while Matlab has Simulink [22]. The SystemC TLM library is by far the most common and complete TLM implementation to date. Open SystemC Initiative (OSCI) TLM is the name of the initial library, which now lies under Accellera [25]. The electronics industry has embraced SystemC as standard for building transaction level models, where OSCI TLM is the TLM library. As mentioned earlier, OSCI TLM is not a programming language in itself, but builds directly on SystemC. SystemC is a superset of C++, with its available open-source simulators and compilers [26]. OSCI recently released TLM 2.0 with additional features to describe sockets, generic payload and timing annotation [9].

# 2.4 LEON2

LEON [27] is a 32-bit microprocessor, based on SPARC-V8 [28] instruction set. It was originally owned and created by European Space Agency (ESA), now it is owned and maintained by Gaisler Research [29]. The processor core is in VHDL, and is configurable through VHDL generics. LEON2 is published under two licenses: GNU Public License (GPL) [30] and Lesser GNU Public License (LGPL) [31]. The core is LGPL, while all support files belong under GPL. In short, that makes LEON practically open-source, making it very attractive for SOC designs. LEON is originally designed for space applications, but LEON fits in both commercial and research designs. Since its creation, LEON developed multiple models, where the newer models include additional infrastructure, like a SOC. LEON2, LEON3 and LEON4 are different versions, and they often refer to SOC designs. There are also Fault-Tolerant (FT) versions of the design, but FT versions are not relevant for this thesis.

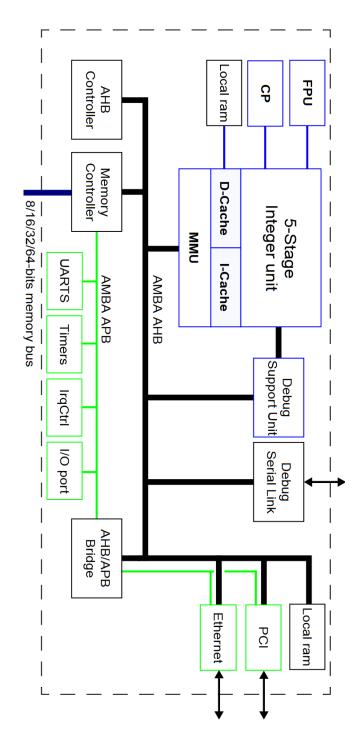

LEON2 is the second iteration of the LEON processor, and is commonly distributed as a SOC with the following Intellectual Properties (IP):

- AMBA AHB bus system

- Memory controller

- AHB/APB Bridge

- Debug support unit with trace buffer

- AMBA APB bus system

- UART

- Timers

- Interrupt controller

- I/O port

Figure 2-d visually displays the LEON2 SOC with connections between each module. The implementation used in this thesis does not include the PCI/Ethernet connections nor the Debug Serial Link in Figure 2-d. LEON2 often refer to the synthesizable VHDL implementation, but this thesis uses a SystemC implementation. Magillem provides the SystemC implementation, which is not publicly available. However, it is derived from and almost identical to the implementation provided by Accellera. The implementation provided by Accellera is a part of the public IP-XACT example for LEON2 from their website [32]. The HDL implementation of LEON2 is available as Open-Source through GitHub [33] provided by Jiri Gaisler. Wherever the report mentions LEON2, it is always a reference to the entire SOC, rather than only the processor.

Figure 2-d LEON2 model [27]

# **3 Experiment**

Proper investigation of IP-XACT's impact is clearer with the help of an experiment. The experiment uses a TLM implementation, but the discussion includes a very brief introduction to the RTL aspect of IP-XACT. The experiment revolves around LEON2 with its deliverables that together form a SOC. It is very convenient for the experiment that the SOC implementation is open-source and available both as TLM and RTL. Investigation consists of using IP-XACT in practice and applying changes and updates to the TLM implementation with the help of IP-XACT. The experiment will help to identify pros and cons directly related to the design flow utilizing IP-XACT.

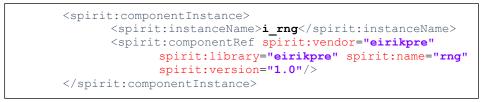

The experiment consists of taking an IP-XACT and TLM implementation, and add a module to them. Since it is hard to get a hold of a module described in IP-XACT and TLM, the module is built from the ground up. The module must be compatible with OSCI TLM design, and then integrated with IP-XACT. Take note that an external module must match both the IP-XACT version and TLM version. There are also restraints to the module in terms of ports and connectivity to the LEON2 SOC. Connections must be to either AHB or APB bus systems, and the processor does not have extra ad-hoc connections, so any ad-hoc signals of the module will be passed outwards to the eventual test bench.

Purpose is to investigate IP-XACT's properties, not the tools' properties. However, each tool will of course present IP-XACT slightly different, thus slightly influence IP-XACT's representation.

# 3.1 Methodology

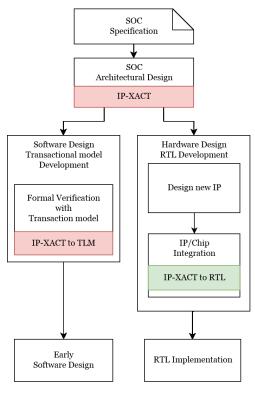

The entire design flow can in theory be fully described by IP-XACT in every stage. However, the experiment will only cover the beginnings of the design cycle, but further discussion will be regarding the entire design flow. In practice, a company choose how much they should embrace IP-XACT. Figure 3-a shows a simplified design flow, where IP-XACT is utilized in two places; mainly where there is need for connectivity and integration metadata.

Figure 3-a Uncomplicated design flow

IP integration and the integration of the architectural design are very similar. For a design environment that already uses IP-XACT, there most likely exists a big part of the design described in IP-XACT already and either TLM or RTL. IP-XACT contributes by binding all the predefined IPs together in implementation of choice. Of course, as there are new IPs added they could practically be added to the already existing system, which is what the experiment aim to trial.

Since IP-XACT carries a more computer-aided design flow it is reasonable that what does the integration, or rather create files for the integration in another programming language, are generators. The physical generators are not part of the standard itself, but the standard include support for choosing generators as well as description of the interface between the generator and design environment. The interface's name is Tight Generator Interface (TGI) and it is utilizing the SOAP standard [34] to pass messages. All of the tools researched in this thesis both have support for custom-made generators through TGI and various built-in generators. The experiment uses built-in generators, and does not cover creating custom ones.

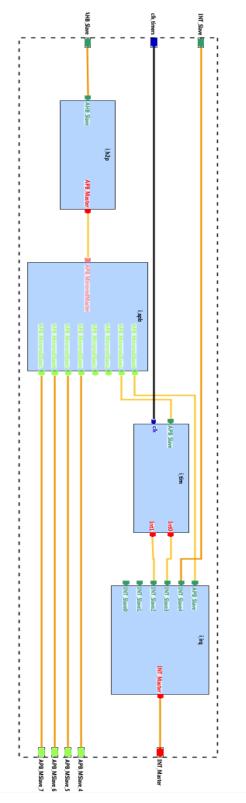

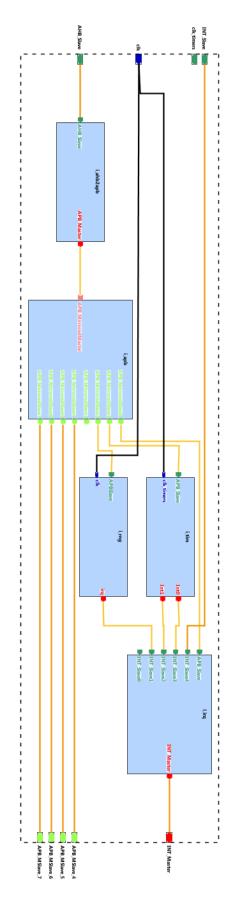

## 3.2 Setup

The setup consists of the LEON2 IP-XACT implementation alongside the TLM implementation. The most interesting areas of research here are how the design methodologies work, how IP-XACT contributes to a TLM environment, and to architectural exploration. The setup will also clarify the interactions the designer would have with IP-XACT and its impact on the entire design flow. Other areas of interest are how or even if IP-XACT stands on its own and what does the company need for IP-XACT to be effective. *Standard Structure for Packaging, Integrating, and Reusing IP within Tool Flows* is the slogan of IP-XACT, put simply that is what the experiment provides insight to.

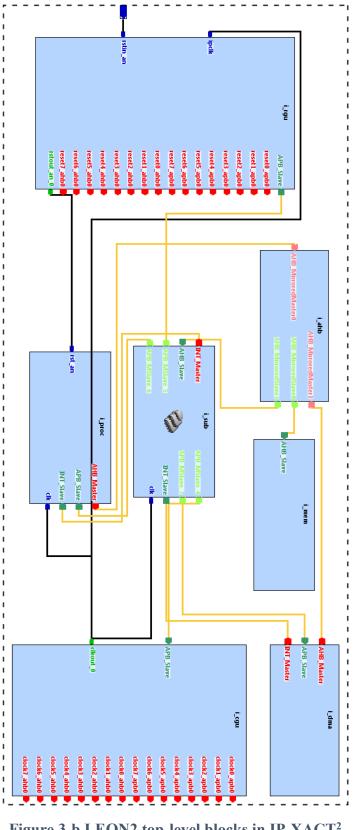

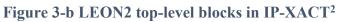

Figure 3-b shows a visual representation of the top-level IP-XACT implementation, versions with and without RNG module are figures added in appendix A. The component with a chip illustration indicates ApbSubSystem, which implements the APB bus and the IPs connected to it. A close look at the figure reveals that the AHB bus is being passed around, where each component has either a slave or master connection. The AHB bus distribution is also implemented with its own component, which is required in IP-XACT to distribute a bus. Figure 3-c displays the internal connections of ApbSubSystem. Similar to the LEON2 model from Theory the first block is the AHB/APB Bridge (i\_ahb2apb). In this figure, it is also clear how the bus distribution works in IP-XACT (see i\_apb).

<sup>&</sup>lt;sup>2</sup> Graphical illustrations from the tool *Magillem*

Figure 3-c Blocks within ApbSubSystem (i\_sub)<sup>2</sup>

IP-XACT resembles a black box design, a design where there is little to no information on internal behaviour. The module needed for the experiment is also a black box, except it has to interact with the TLM for testability. RNG module is made from scratch for the purpose of experiment, but a black box module from an external provider can be used as well. If an external IP is used, it only has the constraint that it has to be compatible to either AHB or APB for easy connection. If it were not compatible, one would have to change the internals of other black boxes to connect it to the design, which is not desired.

To put the experiment into context with an industrial design flow, the designer would most likely already have a partly assembled design. An industrial design is likely to be more complex, but the way IP-XACT work and the interaction between IP-XACT and TLM is almost identical. How the designer adds a component to the design is identical, as it is necessary to use the exactly same constructs of IP-XACT. ARM's AMBA AHB/APB [35] buses are also very common in the industry. IP-XACT describes views, which in short resembles point of view. The experiment uses a TLM point of view, with no point of view configured for RTL.

The addition of a module sheds light upon how to create, add and modify a component as well as how to integrate it into the already existing design. The act of removing/moving the component should be investigated, and if its interfaces change. The interface change consists of first adding the bus connections and later add an interrupt and a clock. The act of adding or altering the design is in theory a form of architectural exploration.

Adding connectivity through IP-XACT is one thing, if the new connections fair well with the TLM/RTL implementation is another. To be able to add on extra connections after creation, the design has to be parameterized completely, but the experiment implies that the design is. An interesting feature here is if IP-XACT has constructs that supports a parameterized design in the sense that it can hold and set those parameters.

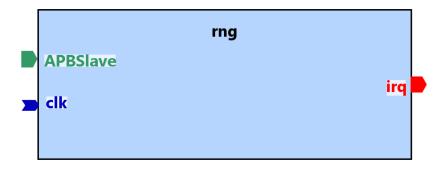

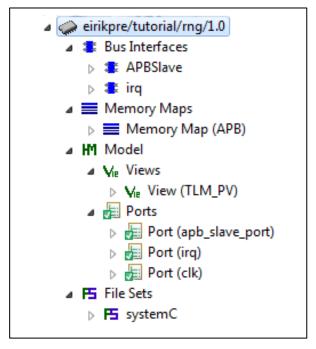

#### 3.2.1 RNG Module

Finding an IP-XACT open-source module that fits LEON2 is hard; hence, it is reasonable to create a new module for the system. As stated previously, behavioural functionality of the module is almost insignificant to IP-XACT, because mostly connectivity applies to IP-XACT. The module added to the design for this experiment is a Random Number Generator (RNG). From an IP-XACT point of view, the module can be entirely a black box design, but the TLM requires some simple functionality to ensure that the module has properly integrated with the design.

The thesis could include a complex behavioural TLM model of the module, but that is not necessary for this study nor will it have a huge impact on the IP-XACT implementation. The TLM implementation of the RNG module has functionality that allow for transactions, signalling and an interrupt. The interrupt is a *BusDefinition* description and the clock is described as a signal, which provides a bit of diversity

between the two. The module itself provides local addresses of its registers, and the toplevel design provides addresses for each underlying module.

Figure 3-d RNG module

Most tools support some form of automatic generation of TLM/RTL, and often provides IP code skeletons for further development. The experiment will not emphasize the generation of skeletons, since that is not directly bound to the standard.

### 3.3 TLM Implementation

In the industry, iterating on products and during creation of new systems it is very common to reuse a lot of the design. This experiment reuses an implementation similar to the IP-XACT example at Accellera's site [32]. The implementation is approximately timed TLM, and belong to *B. Component Assembly Model* from Figure 2-c in Theory. Using this TLM version saves a lot of time due to reuse and simplistic design, where it should be easy to add an IP without rewriting big parts of the code. The design ensures testability from the processors point of view, where the designer can specify write and read operations to specific addresses from the processor. The implementation is in SystemC, so there are available free tools and simulation is fast. IP-XACT as a data-book for metadata role in the design flow will always be as a support flow to either TLM or RTL. Realistically TLM carries more of a support role for RTL, but for this experiment, TLM is the main flow and purpose.

The experiment describes the interaction between IP-XACT and TLM, but in order to rationalize deductions from the interaction, the TLM implementation should have a purpose. Adding a purpose to the TLM implementation enables deeper analysis of the interactions between the two. It can also help uncover what could be done with IP-XACT in the future to support more complex/elaborate modelling. The purpose of the TLM implementation is to perform architectural exploration. The task to perform architectural exploration carry over to IP-XACT; an interesting question is how IP-XACT allow for architectural exploration through generators for TLM and more importantly on its own.

Architectural exploration is a broad term; it might describe very different levels of abstract modelling. The architectural exploration often depends on technology, which has different granularities and benefits. Therefore, architectural exploration for the

purpose of the experiment is narrowed down and concretized. This thesis limits architectural exploration adding, removing and editing blocks in the design and changing between two or more parallel designs. In the context of RTL design flow, all the points above are steps performed much earlier than RTL design in the design flow.

Although it excludes IP behavioural modelling, a discussion to how IP-XACT support more complex modelling through SystemC is further down in the thesis. Complex modelling is outside of the scope of this thesis, but how IP-XACT may support it is not. Complex modelling includes increasing the precision by moving further towards a cycle/pin-accurate TLM model, by adding on performance and energy modelling.

### 3.4 Tools

As IP-XACT is becoming a worldwide standard with notable supporters, more and more companies are adding support for IP-XACT to their tools. Many businesses claim to support IP-XACT, but the amount of commitment and actual support is varying. This chapter describes the selection of most of the available tools. It is important to remember that the research is on IP-XACT; not the tool using it or presenting it. That being said, IP-XACT provide structures and opportunities that might be or not be fully/practically compatible with a tool flow.

There exists many tools with IP-XACT support, and more are being created almost every year [36]. There are different levels of commitment among those; some provide full support to set up a connected design, while others simply include support to parse components, respectively categorized as full and partial. The following list categorizes most of the available tools with providers in parentheses:

- Full

- Magillem (Magillem) [17]

- o Kaktus2 (Tampere University of Technology) [37]

- DesignPlayer (EDAUtils) [38]

- Socrates (ARM) [16]

- GenSys (Synopsis) [39]

- STAR (deFacto) [40]

- Scineric Workspace (Scineric) [41]

- IDesignSpec (AgniSys) [42]

- Partial

- Vivado (Xilinx) [43]

There may, or probably, exist more tools than listed here, but this provide a good selection with some diversity. First that diversify them are cost, some are free; others are costly. Kaktus2 and EDAUtils are completely free; Scineric Workspace has half a year trial, whilst the rest are not free. Some of the rest are available under temporary academic/research licenses that require application. Since TLM is the narrated purpose of the thesis, it is convenient to sort out which tools only support RTL designs. STAR,

Vivado, Socrates, AgniSys, Kaktus2 and GenSys are all tools that per 2017 is geared mainly towards RTL. There is a reason to use a tool that uses IP-XACT back-end as well, elsewise the designer interfaces with blocks that are not directly described with IP-XACT's constructs.

Magillem is the best suited tool to implement and research the standard. The reasoning behind is that they are one of the main contributors to the IP-XACT standardization, and the software is built with IP-XACT as its main functionality. With Magillem being built around IP-XACT it is possible to easily get a good picture of IP-XACT's constructs. Magillem is one of the two tools that add TLM integration, the other being EDAUtils. Magillem is also the better, more stable and more user-friendly tool of the tested ones. Out of the tools listed; Magillem, Kaktus2, EDAUtils and Scineric Workspace were installed and tested.

# **4** Experiences

The experiment is very valuable for the general understanding of IP-XACT's methodology and usage. This chapter describes observations that provide value to the discussion to come. All the experiences derive from studying the IEEE standard itself and observations throughout experimentation.

# 4.1 Methodology

Initially IP-XACT only described components, but has expanded a lot since then. IP-XACT is now able to describe entire systems, and to be a part of the entire design flow. IP-XACT much resembles the system architecture model (SAM) with additional properties to help the rest of the design space.

Figure 4-a Design flow with IP-XACT

In practice, the arrows in Figure 4-a describe generators, but for the design flow they also stand for general knowledge. Knowledge about the entire design and its connectivity is very valuable to the designer throughout the flow. IP-XACT serve as an extended SAM applicable to all parts of the design, where every part uses the same exact reference model for further development. This is a valuable resource to the design teams early in the design cycle.

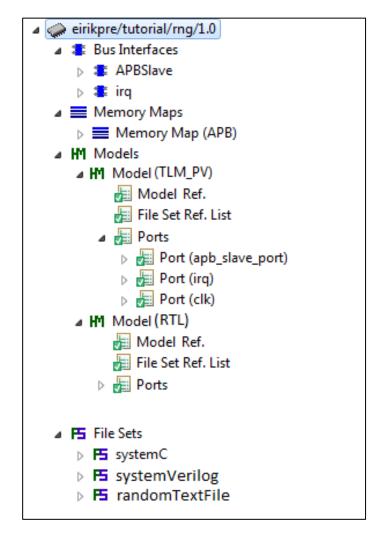

IP-XACT ties all the different environments together with the help of views and file-sets. Views are usually design views, simulation views or documentation views. In the experiment the common view describes the SystemC design, simulation view describes simulation directives and dependencies, and documentation view describes documentation. File-sets specifies which files, what kind of files and what view they belong to. Names of the views must be global, while they are used locally. With IP-XACT describing views and links to different environments, development teams can all work simultaneously with the same reference model. Each team would describe their view and file-sets. The experiment describes the TLM view as *TLM\_PV*, which is used for the RNG module too.

Views are one of the more important features of IP-XACT, but IP-XACT does not contain objects to globally define each view. The ability to describe each view and their properties would have been very useful to the general understanding of the system and very practical, especially in multi-team environments with different views. At the moment, views are simply strings that happen to match, and the way to find matches is to use the view specified in the top-level *design* schema and find that name in its underlying components.

Xml is human and machine readable, but IP-XACT's complexity definitely makes it less attractive to edit and more attractive for Computer-Aided Designs (CAD). For the most part, it is not practical to edit IP-XACT schemes by hand. To deal with this, IP-XACT includes Tight Generator Interface (TGI). TGI is a standardized Application Programming Interface (API) to connect generators that use or edit the IP-XACT schemas, generators allow for easy editing of the design automatically. Since IP-XACT is hard to handle directly, tools make it easier to edit using GUIs that describes the elements in XML.

#### 4.2 Structure

IP-XACT is a comprehensive standard that captures big parts the design with most of its data, and that is a characteristic that comes with both benefits and drawbacks.

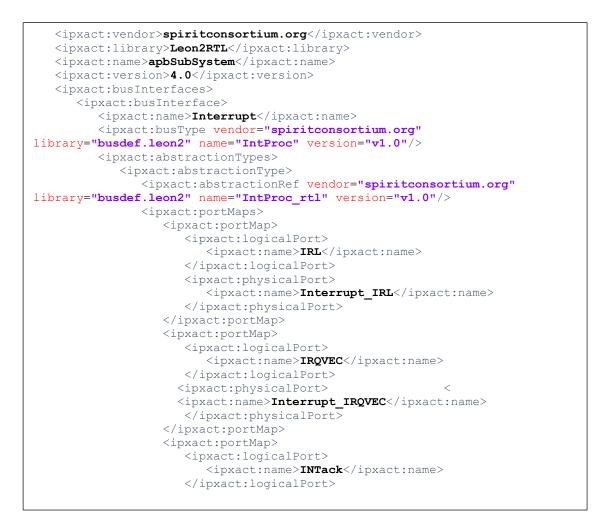

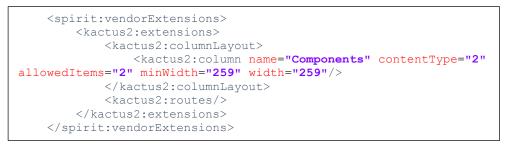

All designers start out as novices when initially starting out with IP-XACT. It is an immense standard, with a lot of different aspects and objects to understand. The XML-syntax makes it easy to understand the structure, but does not make it easy to read. Figure 4-b displays a small part of the XML behind the *ApbSubSystem component* previously marked in Figure 3-b. The entire description totals a little less than 1000 lines of code, and that is without the internal design hierarchy. This makes manually editing the files a hassle, and in reality, not practically viable. It does become easier with a tool, tools also include restrictions according to the standard's elements. That makes it a lot easier, but still there a lot of objects that may not come as easy to the designer.

Figure 4-b ApbSubSystem code snippet

XML structure all the objects in a hierarchy, with the eight top-level schemas as the roots. Hierarchically ordering makes a lot of sense, and makes understanding a lot easier, also most components are best described hierarchal anyway. *ApbSubSystem* also has a *design* description separate to the *component* description. The design specification only describes connectivity, so if the design requires any functionality one has to create that by adding a component within the design.

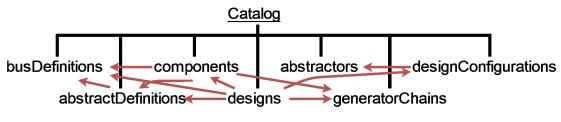

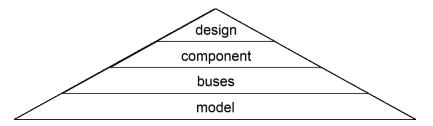

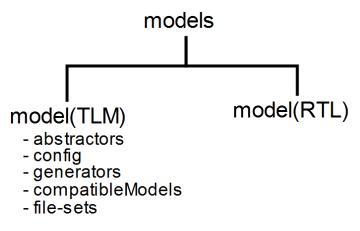

IP-XACT is no longer limited to describing individual components, but can now describe entire electronic systems. It does so with the following eight top-level schemas; *BusDefinition, abstractDefinition, component, design, abstractor, generatorChain, designConfiguration* and *catalog*. Out of the eight schemas it is only *component* that describes metadata of an electronic component as initially intended. The rest describe an interconnected system of said components, as well as the design flow. The designer does not need to use all of the eight level schemas to describe a component / system. *BusDefinition, abstractDefinition, design* and *catalog* are essential to a system, respectively describing buses, implementation of buses, connections and instantiations of a design and locations to definitions, designs and components. The top-level schemas

*component, design, busDefinition* and *abstractDefinition* are enough to entirely build the experiment.

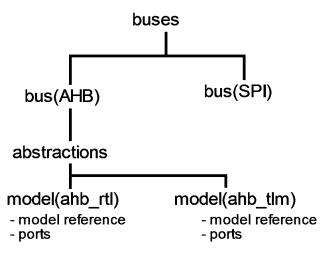

Figure 4-c BusDefinition and abstractDefinition