# Ultra-low power serial communication for Internet of Things

Martin Lesund

Master of Science in ElectronicsSubmission date:July 2017Supervisor:Snorre Aunet, IESCo-supervisor:Sigve Tjora, Disruptive Technologies

Norwegian University of Science and Technology Department of Electronic Systems

### **Master Assignment**

#### **Candidate Name:**

Martin Lesund

#### **Assignment Title:**

Ultra-low power serial communication for Internet of Things

### **Assignment Description:**

In ultra low power systems, the energy used for inter die communication is an important contributor to power dissipation. Many sensors communicate with the host system over low pin count serial buses like I2C, SPI or single wire buses. Careful analysis and optimized design of building blocks like I2C or SPI masters are needed to minimize the current consumption. The assignment will be:

- Study literature and identify solutions for low power serial communication

- Investigate tradeoffs and compare the identified solutions

- Select best approach and design key building blocks, e.g. for an ultra-low power I2C master

The assignment could be done as a purely digital assignment or as a small mixed signal assignment. The design should target implementation in an ASIC.

Assignment Proposer/Co-Supervisor: Sigve Tjora - Disruptive Technologies AS Supervisor: Snorre Aunet ii

### Abstract

This master thesis is about finding a suitable bus protocol to use on an ultra low power IoT device. The bus protocols I<sup>2</sup>C, 1-Wire, SPI, and MBus is compared by different parameters and previous power measurement experiments. Both Mbus and SPI uses substantially less power compared to the other interfaces. The SPI protocol is suggested as a good communication solution, and for this reason an SPI master design is made from scratch. The RTL code is written in VHDL and different energy techniques is used to make it more suitable for ultra low power devices. The SPI master design is implemented on an FPGA on the "Zedboard development kit" which is connected to an external temperature sensor called "LM74". Then a custom test application runs on the "Zedboard" to evaluate the functionality of the SPI master. The data read from the sensor is outputted on a serial terminal to the computer. The SPI master design functioned as expected and got the correct data from the temperature sensor.

This thesis contains material that sometimes can be overlooked in the design process, namely how the communication is done between integrated circuits. There are several solutions that can do this, and some communication solutions is better suited than others. A good communication solution can increase the battery life of an IoT device. This is because the energy used for inter die communication is an important contributor to power dissipation, which is important to keep as low as possible when it comes to ultra low power systems.

This thesis is a collection of some of the most common bus protocols in serial communication, and makes arguments why the SPI interface can be the most suitable for your design. To further prove this argument an SPI master design is made and tested on an FPGA with a temperature sensor to verify the functionality of the design. iv

### Sammendrag

#### (Abstract in Norwegian)

Denne masteroppgaven handler om å finne en egnet bus protokoll til bruk for en ultra lav effekt IoT enhet. Bus protokollene I<sup>2</sup>C, 1-Wire, SPI og Mbus blir sammenlignet med hverandre fra forskjellige parametre og tidligere effektmålings eksperiment. SPI protokollen blir foreslått som en god kommunikasjons metode, og av den grunn blir det designet en egen SPI master. RTL koden er skrevet i VHDL og forskjellige energisparende teknikker er brukt for å gjøre modulen tilpasset for en ultra lav effekt enhet. SPI masteren blir implementert på en FPGA på "Zedboard development kit", som er koblet til en ekstern temperatur sensor navngitt "LM74". Deretter testes funksjonaliteten av designet for SPI masteren med et eget test program, og temperaturen leses fra sensoren og blir sendt til en seriell terminal på datamaskinen. Designet av SPI masteren fungerte som forventet og ga ut riktig temperatur fra sensoren.

Denne masteroppgaven omhandler et tema som noen ganger kan bli oversett i design prosessen, nemlig hvordan kommunikasjonen burde gjøres mellom enhetene i et system. Det er mange forskjellige måter å gjøre dette på, og noen løsninger er bedre egnet enn andre. Forbedret kommunikasjon mellom enhetene kan for eksempel føre til en lengre batterilevetid for en IoT enhet. Dette er fordi energien som er brukt i kommunikasjonen mellom enheter er en viktig bidragsyter til energitap. Det er viktig å holde energitapet så lavt som mulig når det kommer til ultra lave effekt systemer.

Denne masterenoppgaven er en samling av noen av de mest brukte bus protokollene for seriell kommunikasjon, og gjør argumenter for at SPI grensesnittet kan være den beste løsningen for ditt design. For å ytterlige prøve å bevise dette, blir en SPI master laget og testet på en FPGA med en temperatur sensor. vi

### Preface

This is a master thesis in "Design of Digital Systems" with the course code TFE4915, carried out at the Norwegian University of Science and Technology in Trondheim. This is the last project for the masters program in Electronics (program code MIEL). The master thesis was carried out during the spring semester of 2017, and is a continuation of a specialization project under the same name (course code TFE4520). This master was done in cooperation with the company "Disruptive Technologies AS". It was supervised by professor Snorre Aunet at NTNU and Sigve Tjora at Disruptive Technologies. This master is executed and documented by the student Martin Lesund.

Trondheim, 2017-07-13

artin esund

Martin Lesund

viii

### Acknowledgment

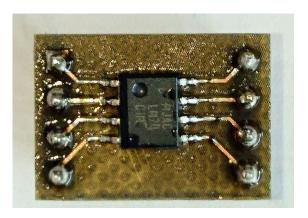

I would like to thank the following persons for their great help during this master thesis. I would like to thank my supervisor Snorre Aunet for giving me guidance and support throughout this master. I would also like to thank Sigve Tjora from Disruptive Technologies for helping me when I had questions, and giving me tips during this period. I would also like to thank senior engineer at NTNU Terje Mathiesen, who made a breakout board for the LM74 sensor, which made it usable for testing my design.

M.L.

х

### Abbreviations

- **IoT** Internet of Things

- IC Integrated Circuit

- FPGA Field-programmable gate array

- SoC System on Chip

- LSB Least Significant Bit

- MSB Most Significant Bit

- **SDK** Software Development Kit

- $\mu C$  Microcontroller

- **GPIO** General Purpose Input/Output

- I/F Interface

- DAC Digital to Analog Converter

- ADC Analog to Digital Converter

- LUT Look Up Table

- ASIC Application-Specific Integrated Circuit

- **RTL** Register Transfer Level

- FSM Finite-State Machine

xii

## Contents

|   | Mas  | eter Assignment                      | i    |

|---|------|--------------------------------------|------|

|   | Abs  | tract                                | iii  |

|   | Sam  | nmendrag                             | v    |

|   | Pref | ace                                  | vii  |

|   | Ack  | nowledgment                          | ix   |

|   | Abb  | reviations                           | xi   |

|   | List | of Figures                           | xvii |

|   | List | of Tables                            | xxi  |

|   |      |                                      |      |

| 1 | Intr | oduction                             | 1    |

|   | 1.1  | Торіс                                | 1    |

|   | 1.2  | Problem Description                  | 2    |

|   | 1.3  | Objectives                           | 2    |

|   | 1.4  | Motivation                           | 3    |

|   | 1.5  | Thesis Outline                       | 4    |

|   |      |                                      |      |

| 2 | Bac  | kground Theory                       | 5    |

|   | 2.1  | Communication                        | 5    |

|   | 2.2  | Bus Communication                    | 7    |

|   | 2.3  | Interconnects                        | 9    |

|   |      | 2.3.1 Power Savings in Interconnects | 12   |

### CONTENTS

|   | 2.4  | Coding Techniques                                                | 13 |

|---|------|------------------------------------------------------------------|----|

|   | 2.5  | Serial communication protocols                                   | 13 |

|   |      | 2.5.1 $I^2C$                                                     | 14 |

|   |      | 2.5.2 1-Wire                                                     | 15 |

|   |      | 2.5.3 SPI                                                        | 16 |

|   |      | 2.5.4 MBus                                                       | 19 |

| 3 | Con  | nparing the Bus Protocols I <sup>2</sup> C, 1-Wire, SPI and MBus | 21 |

|   | 3.1  | Comparison of bus protocols                                      | 21 |

|   | 3.2  | Previous Power Measurement Experiments                           | 23 |

|   | 3.3  | Suggestion for solution                                          | 24 |

| 4 | Des  | ign Process of an SPI Master                                     | 29 |

|   | 4.1  | SPI Specification                                                | 30 |

|   |      | 4.1.1 Port List                                                  | 30 |

|   |      | 4.1.2 SPI Architecture                                           | 31 |

|   |      | 4.1.3 SPI FSM                                                    | 33 |

|   |      | 4.1.4 SPI Addressing                                             | 35 |

|   | 4.2  | SPI Simulation                                                   | 35 |

|   | 4.3  | SPI Registers                                                    | 39 |

|   |      | 4.3.1 Implementing the Registers                                 | 40 |

|   |      | 4.3.2 AXI lite Connection                                        | 42 |

| 5 | Res  | ults for the SPI Experiment                                      | 45 |

|   | 5.1  | SPI with LM74                                                    | 45 |

|   | 5.2  | Power Saving Techniques                                          | 48 |

| 6 | Dise | cussion                                                          | 49 |

|   | 6.1  | Power Consumption                                                | 49 |

xiv

|        | 6.2                                             | SPI with LM74                                                                                                                            | 49                                                     |

|--------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

|        | 6.3                                             | Power Saving Techniques                                                                                                                  | 50                                                     |

|        |                                                 | Limitations of the Findings                                                                                                              | 51                                                     |

| 7      | Con                                             | clusion                                                                                                                                  | 53                                                     |

|        | 7.1                                             | Recommendations for Further Work                                                                                                         | 54                                                     |

| Re     | fere                                            | nces                                                                                                                                     | 55                                                     |

| A      | LM7                                             | 74 Temperature Sensor                                                                                                                    | 61                                                     |

|        | A.1                                             | LM74                                                                                                                                     | 61                                                     |

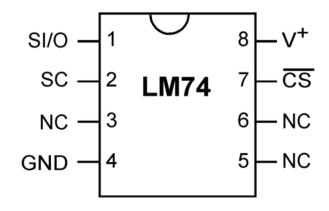

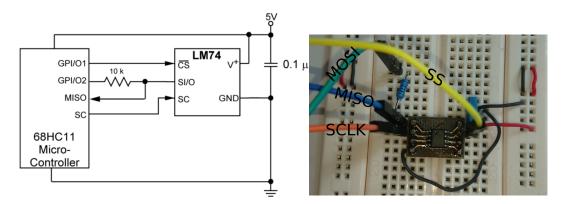

|        | A.2                                             | Serial Bus Interface                                                                                                                     | 62                                                     |

|        | A.3                                             | Interfacing with 3-wire SPI                                                                                                              | 63                                                     |

|        |                                                 |                                                                                                                                          |                                                        |

| B      | Con                                             | nnecting to the Zedboard                                                                                                                 | 65                                                     |

|        |                                                 | nnecting to the Zedboard<br>Lite core                                                                                                    | 65<br>69                                               |

|        | Axi                                             |                                                                                                                                          |                                                        |

| С      | <b>Axi</b><br>C.1                               | Lite core                                                                                                                                | 69                                                     |

| С      | <b>Axi</b><br>C.1<br><b>SPI</b>                 | Lite core Creating a new IP                                                                                                              | <b>69</b><br>76                                        |

| С      | <b>Axi</b><br>C.1<br><b>SPI</b><br>D.1          | Lite core Creating a new IP                                                                                                              | <b>69</b><br>76<br><b>89</b>                           |

| C<br>D | <b>Axi</b><br>C.1<br><b>SPI</b><br>D.1<br>D.2   | Lite core         Creating a new IP         Master code         SPI Master         Test bench                                            | <b>69</b><br>76<br><b>89</b><br>89                     |

| C<br>D | Axi 2<br>C.1<br>SPI<br>D.1<br>D.2<br>AXI        | Lite core   Creating a new IP   Master code   SPI Master   Test bench   Vhdl files                                                       | <b>69</b><br>76<br><b>89</b><br>89<br>96               |

| C<br>D | Axi 2<br>C.1<br>SPI<br>D.1<br>D.2<br>AXI<br>E.1 | Lite core         Creating a new IP         Master code         SPI Master         Test bench         vhdl files         my_spi_v1_0.vhd | <b>69</b><br>76<br><b>89</b><br>89<br>96<br><b>103</b> |

### CONTENTS

xvi

# **List of Figures**

| 1.1  | Growth of IoT in the 2000s. Source: [11]                                                  | 3  |

|------|-------------------------------------------------------------------------------------------|----|

| 2.1  | Example of Parallel interface                                                             | 6  |

| 2.2  | Example of Serial interface                                                               | 6  |

| 2.3  | Example of bus-based communication architecture. Adapted from source                      | :  |

|      | [27]                                                                                      | 8  |

| 2.4  | An example of bidirectional bus lines. Adapted from Source: [27] $$                       | 8  |

| 2.5  | Single and multiple microstrip wire. Source: [29]                                         | 10 |

| 2.6  | Using coding on a bus. Adapted from source: [29]                                          | 12 |

| 2.7  | A simple I <sup>2</sup> C example. Adapted from source:[38] $\ldots \ldots \ldots \ldots$ | 14 |

| 2.8  | A microcontroller with multiple 1-Wire temperature sensors. Adapted                       |    |

|      | from source:[28]                                                                          | 15 |

| 2.9  | A simple SPI example. Adapted from source:[20]                                            | 17 |

| 2.10 | Timing diagram of SPI modes 0 and 1                                                       | 18 |

| 2.11 | Timing diagram of SPI modes 2 and 3                                                       | 18 |

| 2.12 | MBus physical topology for stepped 3D stacking with wirebonding. Source                   | :  |

|      | [26]                                                                                      | 20 |

| 3.1  | Bus overhead. Adapted from source: [26]                                                   | 25 |

| 3.2  | Total Power Draw. Adapted from source: [26]                                               | 26 |

| 4.1 | Flowchart of the design process                                      | 29 |

|-----|----------------------------------------------------------------------|----|

| 4.2 | This is the architecture of the design                               | 32 |

| 4.3 | This is the FSM of the SPI Master                                    | 33 |

| 4.4 | FSM VHDL code                                                        | 34 |

| 4.5 | Simulation of the SPI Master (Mode 2)                                | 38 |

| 4.6 | Simulation of the SPI Master (Mode3)                                 | 38 |

| 4.7 | VHDL code of the registers                                           | 41 |

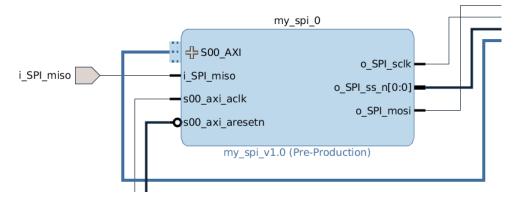

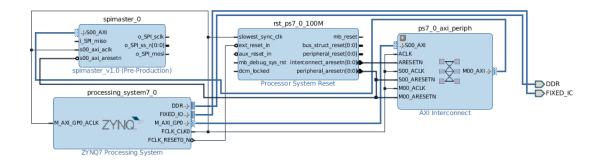

| 4.8 | Block diagram of the AXI interconnects with the SPI Master and PS $$ | 43 |

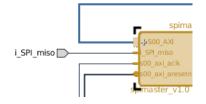

| 4.9 | Block diagram of the SPI master                                      | 44 |

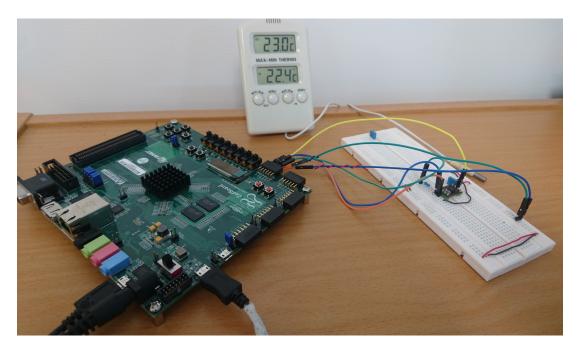

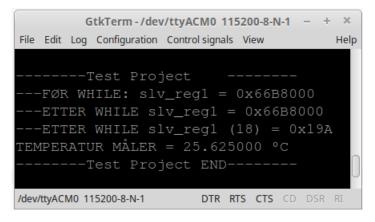

| 5.1 | Testing environment                                                  | 46 |

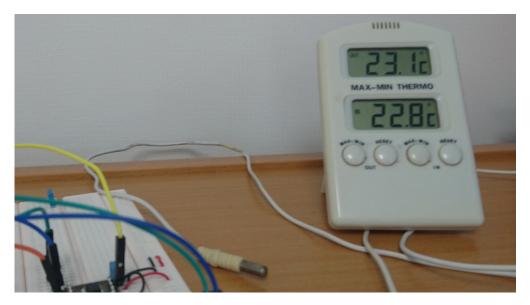

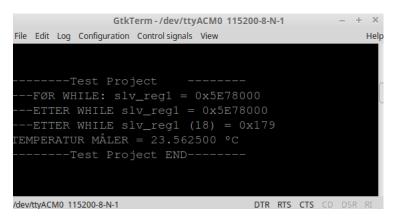

| 5.2 | Read from terminal                                                   | 46 |

| 5.3 | Validating temperature                                               | 47 |

| 5.4 | Temperature increasing                                               | 47 |

| 5.5 | Utilization Report of Binary Encoding                                | 48 |

| 5.6 | Utilization Report of Gray Encoding                                  | 48 |

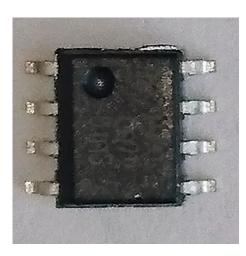

| A.1 | The LM74 chip                                                        | 62 |

| A.2 | The LM74 on a breakout board                                         | 62 |

| A.3 | SOIC - Top View. Source [35]                                         | 62 |

| A.4 | LM74 digital input control using $\mu$ C's GPIO. Source [35]         | 63 |

| A.5 | The LM74 on a breakout board                                         | 63 |

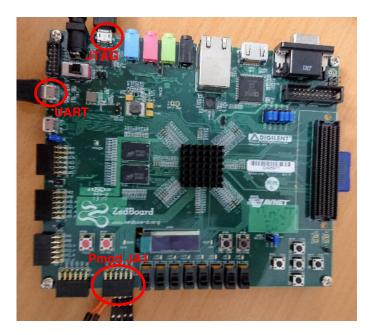

| B.1 | The Zedboard Connections                                             | 65 |

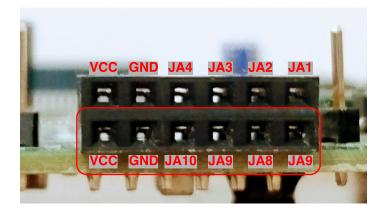

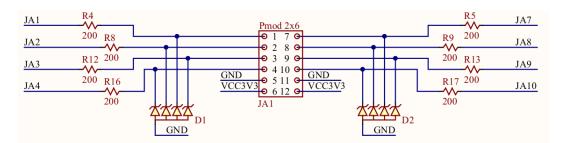

| B.2 | The Zedboard Connections                                             | 66 |

| B.3 | Pmod schematic. Source [8]                                           | 67 |

| C.1 | Create a new project                                                 | 70 |

| C.2 | Pick a suitable project name                                         | 70 |

| C.3 Choose RTL Project                                | . 71 |

|-------------------------------------------------------|------|

| C.4 Select what platform you are using                | . 71 |

| C.5 GUI of Vivado                                     | . 72 |

| C.6 Creating a block design                           | . 72 |

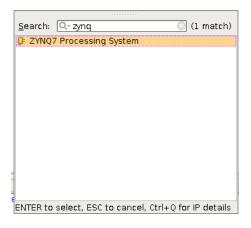

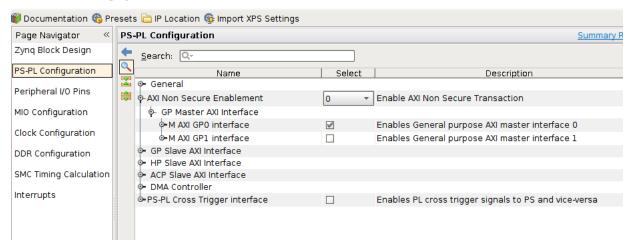

| C.7 Add a new IP                                      | . 73 |

| C.8 Find the Zynq IP                                  | . 73 |

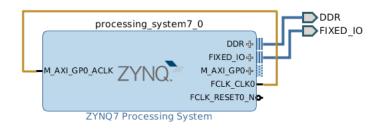

| C.9 Zynq added to design                              | . 73 |

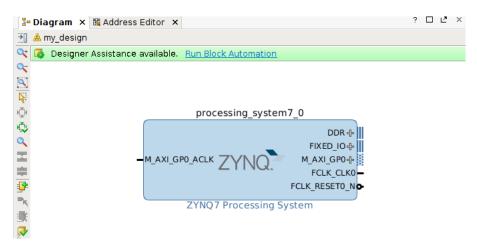

| C.10 Re-Customize IP                                  | . 74 |

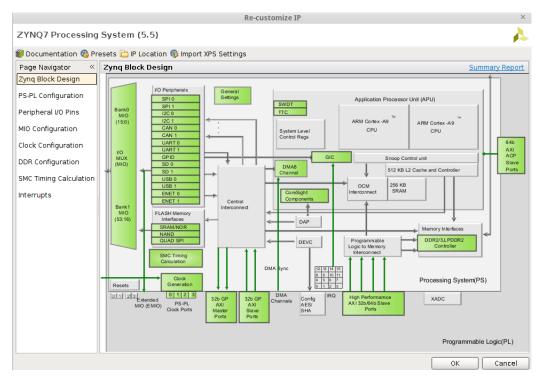

| C.11 PS-PL Configuration panel                        | . 75 |

| C.12 Connect the wire highlighted in the block design | . 75 |

| C.13 Choose AXI4 peripheral                           | . 76 |

| C.14 Default settings for AXI Lite                    | . 77 |

| C.15 Choosing the SPImaster.vhd                       | . 78 |

| C.16 Package IP panel                                 | . 79 |

| C.17 Add your custom IP                               | . 79 |

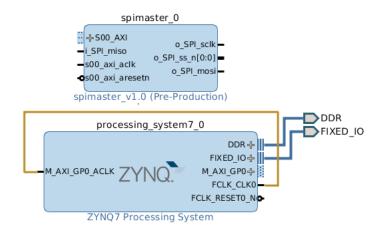

| C.18 Updated block diagram                            | . 80 |

| C.19 Block diagram after connection automation        | . 80 |

| C.20 Make inputs/outputs external                     | . 81 |

| C.21 Generate output products                         | . 81 |

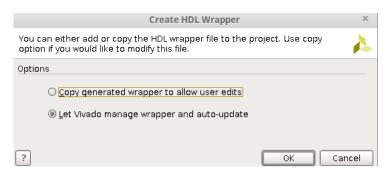

| C.22 Creating HDL Wrapper                             | . 82 |

| C.23 Bitstream finished                               | . 82 |

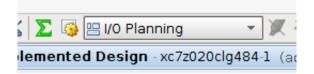

| C.24 I/O planning section                             | . 83 |

| C.25 I/O addressing                                   | . 83 |

| C.26 Export Hardware                                  | . 84 |

| C.27 Make a New Project                               | . 84 |

| C.28 Src folder for the project                       | . 85 |

| C.29 Copy "ps7_init.h" into your src folder           | . 85 |

| C.30 Program FPGA                 | 85 |

|-----------------------------------|----|

| C.31 Select test file             | 86 |

| C.32 Serial terminal port options | 86 |

| C.33 Read data from UART          | 87 |

# List of Tables

| 2.1 | The different SPI modes                                                 | 17 |

|-----|-------------------------------------------------------------------------|----|

| 3.1 | Comparison of the serial interfaces. Adapted from source: [26] and [21] | 22 |

| 3.2 | Energy consumption for evaluated serial interfaces [21]                 | 24 |

| 4.1 | SPI signals in the design                                               | 31 |

|     | Binary vs. Gray Encoding                                                |    |

| 4.3 | SPI Master addressing                                                   | 35 |

| 4.4 | slv_reg0, D31 to D16                                                    | 39 |

| 4.5 | slv_reg0, D15 to D0                                                     | 39 |

| 4.6 | spi_to_ps, D31 to D16                                                   | 40 |

| 4.7 | spi_to_ps, D15 to D0                                                    | 40 |

| B.1 | Pmod Connection. Adapted from source [3]                                | 66 |

### LIST OF TABLES

xxii

### Chapter 1

### Introduction

This chapter contains information about why bus communication is important for ultra low power devices. It also contains the problem description and the objectives of this master thesis as well the motivation for this research. At the end of the chapter a thesis outline is listed.

### 1.1 Topic

The energy used for inter die communication is an important contributor to power dissipation. This is important to keep as low as possible for ultra low power systems to increase battery life if it's used as a power supply. These systems could include sensors which usually communicate with the host system over serial buses like 1-Wire, I<sup>2</sup>C or SPI buses. Which bus you chose can have an impact on the overall power dissipation. The interconnects between devices are generally responsible for a substantial fraction of the total power consumption [16]. The trend is that systems are getting more complex with additional features, size requirements and power requirements. Therefore, the method of communication can have a great impact for power savings and prolonged battery life. In the past, the serial bus you chose usually wasn't

as much thought through, because of lower requirements for the system. They prioritized the parts that where the most power hungry, not the parts where power dissipation was relatively lower. Today, for ultra low power systems we have to optimize everything to save as much power as possible, and serial buses has an impact in the overall power dissipation.

### **1.2 Problem Description**

The difference between the serial buses can have a respective impact on the power dissipation for a system. We must identify what can be done to minimize the current consumption for a bus master. Then we have to compare the most common serial busses for several parameters e.g. difference between complexity, pins used and robustness. After that we use the most suited interface for an ultra low power system, and design the master module for this interface. The serial communication design solution is directed towards a System on Chip (SoC).

### 1.3 Objectives

The objectives for this master thesis is as follows:

- · Identify solutions for low power serial communication

- Investigate tradeoffs and compare the identified solutions

- Select the best approach and design key building blocks for an ultra low bus master

### 1.4 Motivation

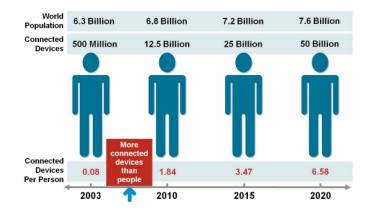

In the last few years the interest for devices connected to the Internet has rapidly increased, under the term most known as the "Internet of Things" (IoT). We are surrounded by small electronic devices everywhere which usually runs on battery as their power supply. This trend of increasing numbers of IoT devices doesn't seem to stagnate. "Cisco Internet Business Solutions Group" predicted in 2010, that there will be over 50 billion<sup>1</sup> connected devices to the Internet in 2020 [11]. The Figure 1.1 shows the estimated growth of connected IoT devices. This relatively high estimate can also be interpreted to create market efficiency by guiding companies to make choices to for example invest and enter this new era of IoT.

Figure 1.1: Growth of IoT in the 2000s. Source: [11]

The energy required for operations from machines build around embedded systems are increasing [14]. Systems are getting more complex and the energy requirements increases. Reduction of energy consumption in core processors or controllers, peripherals and communication interfaces can increase the lifetime of a battery substantially [39]. This is why choosing the right bus protocol for your system is important and has the potential of reducing the energy consumption considerably.

<sup>&</sup>lt;sup>1</sup>This number has been reduced to around 20-30 billion by new estimates from Gartner, Ericsson and others [24]

### 1.5 Thesis Outline

The structure of this thesis is as follows:

**Chapter 2 - Background Theory:** This chapter presents relevant information behind basic communication styles, bus communication and interconnects between devices in a system. This chapter also include power saving techniques such as coding techniques, and ends with information about the I<sup>2</sup>C, 1-Wire, SPI and MBus protocols.

**Chapter 3 - Comparing the Bus Protocols I<sup>2</sup>C, 1-Wire, SPI and MBus:** This chapter compares the different bus protocols, investigate tradeoffs and look at advantages and disadvantages. This chapter also includes previous power measurement experiments with a couple of the bus protocols. The chapter ends with a suggestion for a suited bus interface for an ultra low power system.

**Chapter 4 - Design Process of an SPI Master:** This chapter will describe the design process of an SPI bus master. The specifications, including port list, architecture, Finite-State Machine (FSM), Addressing and simulation of the design are described. The end of the chapter describes how the SPI master is implemented on a FPGA with the AXI Lite interface and how the registers are set up.

**Chapter 5 - Results for the SPI Experiment:** This chapter contains the results of testing the design with an LM74 sensor and power saving techniques results.

**Chapter 6 - Discussion:** This chapter contains the discussions of the results for the experiment. It also includes what frequencies worked on the design and why. As well as how the power saving techniques affected the design. The chapter ends with the limitations of the findings.

**Chapter 7 - Conclusion:** This chapter is the conclusion of the whole thesis. It summarizes why the SPI is a suitable protocol for an ultra low power device, as well as the design process and testing. This chapter also includes some recommendations for further work/investigation.

### **Chapter 2**

### **Background Theory**

This chapter will give a summary on how communication can be done in Integrated Circuits, how this is done with buses, theory behind interconnects, some power saving techniques and information about the different bus protocols I<sup>2</sup>C, 1-Wire, SPI and MBus.

### 2.1 Communication

Communication in Integrated Circuits (IC) are typically designed in serial or parallel, and it can either be done with synchronous or asynchronous transfer.

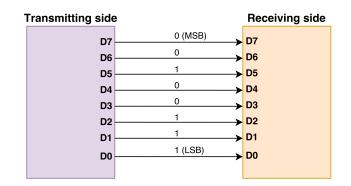

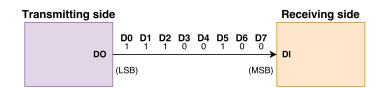

Parallel communication are used in for example modern computers, and can have eight data wires (+ ground wires/control wires) in parallel between two components. Parallel communication is a method of transferring blocks e.g. one byte of data at the same time. The Figure 2.1 shows an example on how the interface can look like. These connections have a high throughput and are fast. However, they require more lines which can lead to a high energy consumption and increased overall area cost. They are impractical for longer distances and have a higher probability for "*crosstalk*" between the lines. Crosstalk describes the circumstance when a transmitted signal creates an undesired effect in another circuit or wire. This can corrupt the transmission and the data has to be sent again.

Serial communication can have a single data (+ ground and/or control) wire, where the bits are sent sequentially (one bit at a time). An example of how the interface can look like is seen in Figure 2.2, where 1 byte (= 8 bits) of data is sent from one device to another. This way of communication is more area cost effective and can therefore be a more favourable choice of communication when it comes to IoT devices, because these devices often need to be small-scaled and have few pins between the ICs.

Figure 2.1: Example of Parallel interface

Figure 2.2: Example of Serial interface

Synchronous communication uses a separate clock signal to synchronize transfers between components. The clock is an oscillating signal that tells the receiver exactly when to sample the bits on the data line. Asynchronous communication do not have a separate clock signal line, instead it can use a handshake protocol to synchronize transfer. This often leads to a larger overhead because many of the transmitted bits are used only for control purposes.

### 2.2 Bus Communication

Buses consist of one or several wires where signals are transmitted through for communicating between one or more ICs. The terminology for a bus is defined by [27]:

- Master Initiate and controls data transfer

- Slave Respond to data transfer requests from master

- Arbiter Decides which master grants access to the bus

- Interface Connection between component and bus<sup>1</sup>

- Bridge Connection between buses

- Decoder Decodes the address and selects the correct slave to receive data

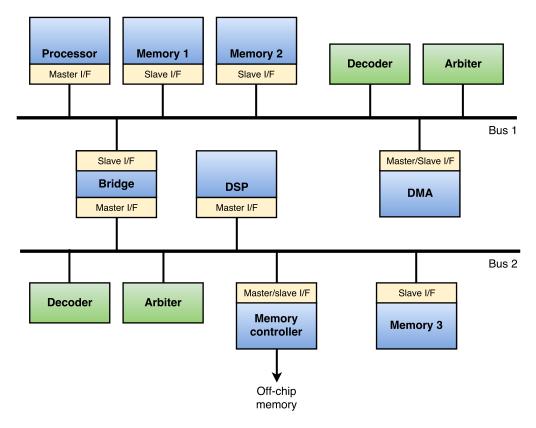

The Figure 2.3 shows an example of a bus-based communication architecture with two buses connected via a bridge. For **Bus 1** the Processor is the master of the slave devices Memory 1 and 2. It also contains a Direct Memory Access (DMA) which is often used in systems to relieve the use of the CPU (master) to access the memory. This gives the CPU opportunity to do other tasks or sleep. **Bus 2** has a Digital Signal Processing (DSP) unit which works as the master. **Bus 2** also contains the slave device Memory 3. The components DMA and Memory controller have both master and slave Interface (I/F), which mean they can act as both master and slave. There is also logic components such as decoders, arbiters and bridges in this architecture example. The decoder decodes the destination address of a data transfer initiated by the master. The arbiter determines which master is granted access to the bus. The bridge connects the two buses.

<sup>&</sup>lt;sup>1</sup>buffers, wires, frequency converter etc.

Figure 2.3: Example of bus-based communication architecture. Adapted from source: [27]

Figure 2.4: An example of bidirectional bus lines. Adapted from Source: [27]

The Figure 2.4 shows the three common signal lines for a bidirectional bus. The lines are:

- Address bus Destination address for the transmitted data

- Data bus Information to be transferred

- Control bus Information about the data transfer (e.g. req/ack signals)

The address signals transmits the address for the destination of the data transfer. The data signals transmits the data values to their destination address. The control signals are used to transmit information about the data transfer. This is usually specified by the bus protocol and can be "request", "acknowledge", "data size indicator" and/or "error" signals.

### 2.3 Interconnects

The trend seems to be that the physical dimensions of interconnects are frequently getting reduced and the operating speed increased. The performance of interconnects is progressively affected by their electrical parasitics, i.e. capacitance, inductance and resistance. These parasitics may increase propagation delays for signals traveling in interconnects or in signals distorted by noise. To transmit a signal in an interconnect, the wire capacitances are charged and discharged, which consumes energy. The energy dissipated in the interconnects can grow greatly due to higher frequencies and the increased number of metal layers which seems to be a trend in today's technology. This increased aspect ratio of the wires and metal layers leads to increased wire-to-wire capacitance, compared to wire-to-ground capacitance, which increases the power consumption [29].

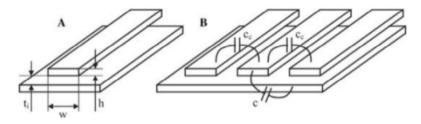

In the paper [17] over 50% of the overall dynamic power consumption of a microprocessor was determined to be consumed by interconnect switching. This means that there is a huge potential for reducing power dissipation in interconnects. To reduce the total wire load, buses can be implemented using techniques such as bus splitting [12]. The simplest model of a wire is typically a microstrip. A microstrip can be described simply as a metal strip on top of a ground plane. In Figure 2.5**A** we see a metal strip on top of a ground plane.

These wires can be modelled through:

- c Capacitance to ground per unit length

- r Resistance per unit length

- 1 Inductance per unit length

We can simplify the parasitics for very short interconnect lengths, so that the capacitance is sufficient enough as a model. As the length increases the resistance and inductance becomes more important.

Figure 2.5: Single and multiple microstrip wire. Source: [29]

When wires are surrounded by several other wires, as shown in Figure 2.5**B**, we have to consider capacitances to neighboring wires as well to the ground plane. They also have a potential problem with crosstalk which can affect power consumption.

However, the power consumption occurs as in logic. The capacitance is charged by the supply voltage and then discharged. Power consumption related to interconnects is given by the Equation 2.1.

$$P_w = {}^1/_2 \,\alpha \, f_c \, C_w \,\Delta V^2 \tag{2.1}$$

#### 2.3. INTERCONNECTS

The symbol  $\alpha$  is the signal activity which is the probability that the signal will switch per clock cycle. The  $f_c$  symbol represents the clock frequency,  $C_w$  is the total capacitance and  $\Delta V$  is the signal voltage swing. The signal activity ( $\alpha$ ) in Equation 2.1 makes power predictions difficult when it comes to power optimization, because it depends on data statistics, architectures and what applications run on the system.

Power consumption for a digital Complementary Metal–Oxide–Semiconductor (CMOS) circuit is mainly contributed from three parts:

- Power consumed by leakage current (Leaking diodes and transistors)

- · Short circuit current between supply rails during switching

- Charging-discharging capacitors (Dynamic power consumption)

$$P_{avg} = P_{switching} + P_{short-circuit} + P_{leakage}$$

$$= \alpha_{0\to 1} C_L \cdot V_{dd}^2 \cdot f_{clk} + I_{sc} \cdot V_{dd} + I_{leakage} \cdot V_{dd}$$

(2.2)

This is represented in Equation 2.2. The first term represent the switching component of power, where  $C_L$  is the load capacitance,  $V_d d$  is the supply voltage,  $f_{clk}$  is the clock frequency and  $\alpha_{0\rightarrow 1}$  is the node transition activity factor (average number of times the node makes a power consuming transition) [7]. The second and third term is not that interesting for the topic in this paper. The second term however is due to the direct-path short circuit current (happens when both NMOS and PMOS transistors are active simultaneously) and last term is leakage current that can arise from substrate injection and subthreshold effects. The power consumption relevant to the charging-discharging current is the dominant part in the total power consumption.

### 2.3.1 Power Savings in Interconnects

There are several methods for reducing the power consumption in interconnects [29]. The most obvious one is to shorten the wire length to reduce the capacitance, resistance and inductance. Another method is to reduce the signal voltage swing  $\Delta V$  via a technique called "*reduced voltage swing*". However, this can lead to "delay penalty". Unless you are making a high performance system this can be accepted. There is also a method to reduce the product of data activity and capacitance by considering the data activity during floorplanning and routing, which optimizes the power consumption based on wire activity/length product.

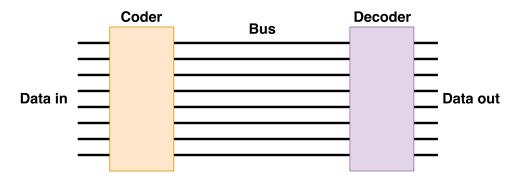

Another way to reduce the power consumption is to reduce the data activity on buses, which can be done through coding. These methods can be utilized for on-chip and off-chip wires. The Figure 2.6 shows the idea behind the bus coding technique, which is to generate an encoder and a decoder. This can be done by encoding the data signals sent by reducing the switching activity on the bus line, and the decoder will interpret the signals decode it back to the original message.

Figure 2.6: Using coding on a bus. Adapted from source: [29]

# 2.4 Coding Techniques

The main reason for coding techniques are:

- · Minimizing the power consumption on the bus

- Minimizing the crosstalk delay

Reducing power on bus transaction by lowering transition-switching activity on the bit lines of a bus, will lead to significant reduction in the (dynamic) bus power consumption. There are several coding schemes developed over the years to reduce the logical activity in interconnects. It is also a promising method to avoid problematic switching patterns for long buses. However, this is achieved with additional logic circuitry, which can be problematic for small size systems. One of the most popular techniques to reduce the number of transitions on a bus is the "Bus Invert Coding scheme" [33]. This is a suitable technique for a data bus with uncorrelated data patterns. It is also a good method when you lack prior knowledge of the data statics. For instruction address buses, "inc-xor code" [30], "Gray code" [34], "T0 code" [6] and the "Beach code" [5] have been proposed. In the paper [32] more of these techniques are listed and explored in depth.

### 2.5 Serial communication protocols

Buses have different properties, and one bus interface can be preferred over the other, depending on what environment or requirements you may have. In this section the serial communication protocols  $I^2C$ , 1-Wire, SPI and MBus are listed.

#### **2.5.1** $I^2C$

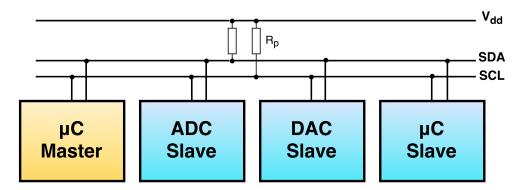

Inter-Integrated Circuit (I<sup>2</sup>C) bus requires only two bidirectional open-drain bus lines, a Serial Data Line (SDA) and a Serial Clock Line (SCL) [25]. This protocol is widely used and popular because of its simplicity. It was developed in the early 1980's by Phillips Semiconductors (now NXP Semiconductors) for easy communication between Integrated Circuits (IC) on the same circuit board. The bus is 8-bit oriented, and has bidirectional data transfers up to 100 kbit/s in Standard-mode, up to 400 kbit/s in Fast-mode, up to 1 Mbit in Fast-mode plus or up to 3.4 Mbit/s in High-speed *mode*. The unidirectional data transfers can come up to 5 Mbit/s in *Ultra-Fast mode*. The protocol is a "multi-master", "multi-slave", "single-ended", serial computer bus which includes collision detection and arbitration to prevent data corruption if two or more masters tries to initiate data transfer simultaneously. The interface I<sup>2</sup>C has a 7-bit or a 10-bit address space depending on the devices used. The devices connected to the bus is software addressable with an unique address. The master can operate as master-transmitter or as master-receiver. The Figure 2.7 shows an example of the interface with a microcontroller as master and a Digital to Analog Converter (DAC), Analog to Digital Converter (ADC) and another microcontroller as slaves.

Figure 2.7: A simple I<sup>2</sup>C example. Adapted from source:[38]

#### 2.5.2 1-Wire

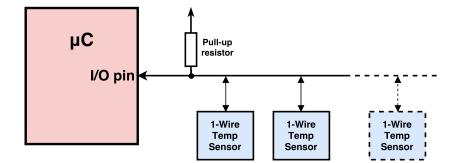

The 1-Wire bus uses only a single data line and a ground reference for communication [36]. This is accomplished by the bus system using a capacitor to store charge, and power the devices when the data line is active. A network made of 1-Wire devices are called "Microlans" and can be used in different sensor applications. This bus has a rather low-speed data signaling, but then again benefits from the low pin count and longer range than for example  $I^2C$ .

The 1-Wire master can initiate and control the communication with one or more slave devices on the bus. Each slave has a unique 64-bit Identification Number (ID), which is factory programmed. This ID serves as the device address on the bus. A subset of the 64-bit ID, (the 8-bit family code) identifies the device type and functionality. The slave devices usually operates between the voltage range 2.8V(min) to 5.25V(max). The grand part of 1-Wire devices take their energy from the bus (parasitic supply), which means they do not need an extra pin for power supply. In Figure 2.8 we can see an example of a microcontroller as master with multiple temperature sensor as slaves.

Figure 2.8: A microcontroller with multiple 1-Wire temperature sensors. Adapted from source:[28]

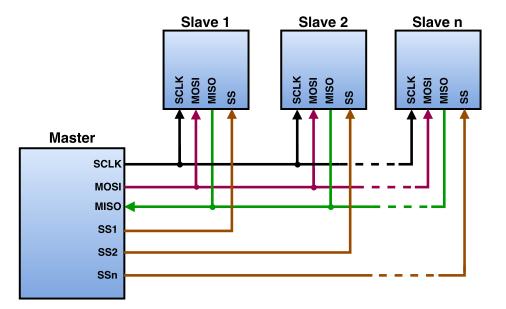

#### 2.5.3 SPI

Serial to Peripheral interface (SPI) have a 4-wire synchronous serial interface developed by Motorola in the late 1980s [18]. The bus lines are namely:

• SCLK - Serial Data Clock:

Outputs the clock from the SPI master to the selected slave on this line to synchronize transfer

- **MOSI** *Master Output, Slave Input* : Transmits data out from the SPI master to the selected slave on this line

- MISO Master Input, Slave Output:

SPI master receives data from the selected slave on this line.

• **CS/SS** - Chip Select/Slave Select:

Outputs the slave select signal from the SPI master to a specific slave. The transmission of the data starts with a falling edge of the  $\overline{SS}$  and ends with the rising edge. (The  $\overline{SS}$  line is an input for the slave).

The SPI protocol is not a well defined protocol, and has numerous of versions on the market today. This can be seen as an upside when it comes to the numerous options and adaptation it can have, depending to the users needs. Unlike the protocol  $I^2C$ , SPI does not define which clock frequency to be used.

The pin count increases with the number of slaves because of the "slave select" lines, this can be unfavorable to the area cost if the number of slaves are high. The SPI protocol is primarily used for short distance communication (like  $I^2C$ ) and it can communicate in full duplex mode, which means it can send and receive data at the same time. The master selects which slave to transfer to or receive from, by the individual "slave select" lines ( $\overline{SS}$ ). A simple SPI example with one master and several slaves is shown in Figure 2.9.

Figure 2.9: A simple SPI example. Adapted from source:[20]

When the SPI master wants to initiate communication, it configures the clock with the frequency supported by the slave device. Then the master selects the slave it wants to write/read from, by switching the  $\overline{SS}$  from logic "1" to "0" for that specific slave line. For example if the master from Figure 2.9 wants to communicate with slave 2, it will switch the "SS2" from logic "1" to "0". The slave for that line will then be listening to the bus and the master is free to transmit data. For each clock cycle a full duplex transmission occurs. This means that data is transmitted and received simultaneously. Slaves devices that are not selected (have  $\overline{SS}$  line high) do not interfere with the SPI bus activities.

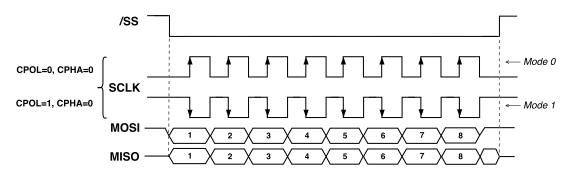

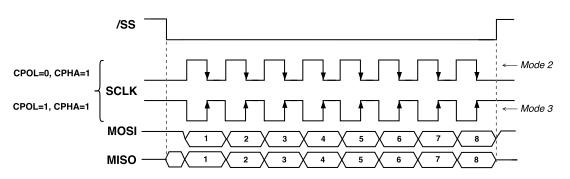

Table 2.1: The different SPI modes

| Mode | CPOL | CPHA |

|------|------|------|

| 0    | 0    | 0    |

| 1    | 1    | 0    |

| 2    | 0    | 1    |

| 3    | 1    | 1    |

There are 4 different SPI bus standards modes with regards to the **SCLK** signal. The modes are selected by one of four combinations of serial Clock Phase (**CPHA**) and Clock Polarity (**CPOL**) signals. The different modes and combinations are listed in Table 2.1 and represented in the timing diagram in Figure 2.10 and Figure 2.11. The **CPOL** designates the default value (high or low) of the **SCLK** signal when the bus is in the state "idle". If **CPOL** = 0, the **SCLK** starts out at logic "0" and raises to a "1". If **CPOL** = 1, the default value of **SCLK** is a logic "1" (high) and falls to "0" when it starts transmitting. When **CPHA** = 0, the data on the **MISO** and **MOSI** line is sampled on the first **SCLK** transition (falling or rising edge) seen in Figure 2.10. This means that **CPHA** determines which edge of the **SCLK** the data is sampled. When **CPHA** = 0, the data is interpreted on the first change of the clock seen in Figure 2.10. When **CHPA** = 1, the data is interpreted on the second change of the clock seen in Figure 2.11.

Figure 2.10: Timing diagram of SPI modes 0 and 1

Figure 2.11: Timing diagram of SPI modes 2 and 3

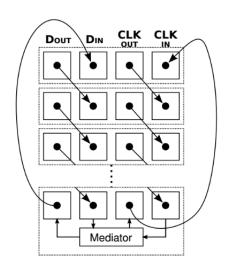

#### 2.5.4 MBus

The MBus<sup>2</sup> is described as an ultra-low power interconnect bus which is targeted for microscale systems [26]. It is most known for being a key element for the Michigan Micro Mote platform [37]. Other than that it is not broadly used like the other bus interfaces. MBus is a 4 pin, 22.6pJ/bit/chip (on average) chip-to-chip interconnect.

The MBus system consist of a mediator node and one or more member nodes connected in two "shoot-through" rings, *CLK* and *DATA* which is represented in Figure 2.12. The mediator node generates the MBus clock and resolves arbitration. It can be a stand-alone component or attached to a core device like a microcontroller. MBus delivers a superset of the features from SPI and I<sup>2</sup>C, but with fixed area, fixed pin count and lower power. It also uses a fully synthesizable logic and minimal protocol overhead. The big drawback from this protocol is that it is not commonly used, and there are few products that have this protocol implemented. This causes problems when you for example want a sensor for a project, since it is not yet in commercial "off-the-shelf" products.

<sup>&</sup>lt;sup>2</sup>They have released the MBus specification and a reference Verilog implementation for free at http://mbus.io/.

Figure 2.12: MBus physical topology for stepped 3D stacking with wirebonding. Source: [26]

# **Chapter 3**

# Comparing the Bus Protocols I<sup>2</sup>C, 1-Wire, SPI and MBus

In this chapter we look closer at the protocols I<sup>2</sup>C, 1-Wire, SPI and MBus. We will examine the advantages and disadvantages, and determine which protocol is the most suited for an ultra low power interface.

# **3.1** Comparison of bus protocols

We are going to look at the difference between the bus protocols listed in Section 2.5 based on different parameters. In Table 3.1 we can see that SPI can potentially have the highest data rate (70Mbit/s), and the 1-Wire the lowest (16Kbit/s). 1-Wire however has the least number of wires, and SPI can have the most depending on how many slaves are in the system. The SPI bus is the only protocol that can transfer data in full duplex, which means it can send and receive data at the same time. The other bus protocols can only communicate one way at the time. They all share the master-to-slave communication model, and that they can have multiple slaves, but only MBus and  $I^2C$  can have multiple masters. A typical disadvantage for "mas-

ter/slave" architectures is that the communications between slave devices must go through the master. This again doubles the communication costs because the messages is sent twice and there is an extra energy cost of running the central controller. The SPI uses the  $\overline{SS}$  lines to communicate with slaves, while the rest uses an addressing method. Out of all the parameters in Table 3.1 the MBus and SPI are arguably the most favourable for an ultra low power interface.

| Parameters                       | SPI               | I <sup>2</sup> C      | 1-Wire          | MBus            |

|----------------------------------|-------------------|-----------------------|-----------------|-----------------|

| Number of lines:                 | 3 + 1 per slave   | 2 with pull-ups       | 1 with pull-ups | 4               |

| Data transfer:                   | full duplex       | half duplex           | half duplex     | half duplex     |

| Communication model:             | master-to-slave   | master-to-slave       | master-to-slave | master-to-slave |

| Number of master devices:        | single            | multiple              | single          | multiple        |

| Number of slave devices:         | multiple          | multiple <sup>a</sup> | multiple        | multiple        |

| Maximum data rate, Mbit/s:       | $70^{\mathrm{b}}$ | 3.4 <sup>c</sup>      | 16 <b>Kb/s</b>  | 10 <sup>d</sup> |

| Interface features:              |                   |                       |                 |                 |

| Device identification mechanism: | slave select      | address               | address         | address         |

| Critical                         |                   |                       |                 |                 |

| I/O pads (n nodes)               | 3 + n             | 2/4 <sup>e</sup>      | -               | 4               |

| Standby power:                   | Low               | Low                   | Low             | Low             |

| Active power:                    | Low               | High                  | Low             | Low             |

| Synthesizable:                   | Yes               | Yes                   | Yes             | Yes             |

| Globally unique addresses:       | -                 | 128                   | $2^{48}$        | 224             |

| Multi-master (interrupt):        | No                | Yes                   | -               | Yes             |

| Desirable                        |                   |                       |                 |                 |

| Broadcast messages:              | Option            | No                    | Yes             | Yes             |

| Data independent:                | Yes               | Yes                   | -               | Yes             |

| Bits overhead(n byte message):   | 2                 | 10 + n                | -               | 19 or 43        |

| Hardware acknowledgement:        | No                | Yes                   | -               | Yes             |

| Power aware:                     | No                | No                    | No              | Yes             |

Table 3.1: Comparison of the serial interfaces. Adapted from source: [26] and [21]

The SPI bus do not suffer the same power challenges faced by "open-collectors" such as  $I^2C$  and 1-Wire. "Open-collectors" usually suffer from high power dissipation. The SPI interface also has the advantage with little to no "protocol overhead". A potentially disadvantage is that the SPI requires a "slave-select" ( $\overline{SS}$ ) line for every slave

caccording to [25]

<sup>d</sup>According to [31]

<sup>&</sup>lt;sup>a</sup>119 when using 7-bit addresses or 1024 when using 10-bit addresses

<sup>&</sup>lt;sup>b</sup>According to [13]

<sup>&</sup>lt;sup>e</sup>When wirebonding, a shared bus requires two pads/chip

device, which means it can be challenging when we think of small and more I/O constrained devices. For modular systems with a variable and unknown number of components until design time, it can be difficult to choose the right amount of "slave select" lines. This can lead to choosing too many lines which can violate the area constrains, or insufficient lines which will disrupt the modularity.

### **3.2 Previous Power Measurement Experiments**

There has been done experiments comparing different bus protocols by power consumption. First of is the article [21]. It involves investigating and comparing three digital serial interfaces (UART,  $I^2C$  and SPI) by their energy efficiency under a given "test bed" build around PICKit 3 development boards [19]. The experiments was executed using one hardware platform PIC18F45K20 microcontroller. The Table 3.2 shows the results of the experiment. It is not representative for energy consumption on a bus for SoC, but it shows the difference which can be propagated for a SoC. The Table 3.2 show the power consumption for data transmissions over the interface implemented in software vs. the same interface implementation using the inbuilt microcontroller hardware module. According to the Table 3.2 the SPI interface is seen to be the lowest of the three interfaces, from the point of power consumption. The conclusion for this paper was that the SPI has the lowest power consumption both with inactive interface and during data exchange when all the interfaces were using the same data rate. This applied for both implementation in hardware and in software.

The second research paper done on the same topic is [23]. They compared the two digital serial interfaces SPI and  $I^2C$  on a PIC16F877 microcontroller. They constructed the serial communication between two microcontrollers where one was master and

|                                               | U                         | ART     |          | SF      | Ы       |               |        | $I^2$   | С      |         |

|-----------------------------------------------|---------------------------|---------|----------|---------|---------|---------------|--------|---------|--------|---------|

| Parameters                                    | RX selected RX unselected |         | selected | RX se   | elected | RX unselected |        |         |        |         |

|                                               | 1 byte                    | 9 bytes | 1 byte   | 9 bytes | 1 byte  | 9 bytes       | 1 byte | 9 bytes | 1 byte | 9 bytes |

| Interface implementation in hardware          |                           |         |          |         |         |               |        |         |        |         |

| Power consumption with inactive interface, mW | 6.06                      | 6.06    | 4.66     | 4.66    | 4.66    | 4.66          | 6.13   | 6.13    | 6.13   | 6.13    |

| Communication:                                |                           |         |          |         |         |               |        |         |        |         |

| Required time, ms                             | 0.68                      | 5.78    | 0.52     | 4.6     | 0.52    | 4.6           | 1.26   | 5.91    | 1.26   | 5.91    |

| Required energy, $\mu$ J                      | 7.31                      | 53.31   | 2.5      | 23.53   | 2.42    | 22.52         | 8.11   | 31.71   | 8.01   | 30.23   |

| Interface implementation in software          |                           |         |          |         |         |               |        |         |        |         |

| Power consumption with inactive interface, mW | 11.04                     | 11.04   | 11.17    | 11.17   | 11.17   | 11.17         | 11.23  | 11.23   | 11.23  | 11.23   |

| Communication:                                |                           |         |          |         |         |               |        |         |        |         |

| Required time, ms                             | 0.64                      | 5.72    | 0.51     | 4.62    | 0.51    | 4.61          | 1.23   | 5.85    | 1.23   | 5.86    |

| Required energy, $\mu$ J                      | 9.00                      | 80.06   | 7.26     | 65.25   | 7.26    | 65.25         | 17.45  | 82.84   | 17.44  | 83.6    |

Table 3.2: Energy consumption for evaluated serial interfaces [21]

the other one was a slave. They then transmitted one-byte data from master to slave and displayed it in two 7-segment LEDs and observed. From their experiment with transmitting one byte of data (0x30 in Hex) from master to slave with 5V supplied, the energy consumed was:

- SPI 9.325nJ

- **I**<sup>2</sup>**C** 126.68mJ

The results from their experiment shows that the SPI interface consumes considerably less energy than the I<sup>2</sup>C interface for sending one byte of data. The SPI interface consumes approximately  $1.36 \cdot 10^7$  less energy than I<sup>2</sup>C according to these results. This is mainly due to the extra pull-up resistors the I<sup>2</sup>C interface needs, which are power hungry. By looking at these two articles the SPI shows best promise out of the known interfaces, regarding power/energy consumption.

# 3.3 Suggestion for solution

The I<sup>2</sup>C bus is a widely used communication protocol mainly because it only requires two wires, independent of the number of connected devices. The big drawback from both I<sup>2</sup>C and 1-Wire bus is that each wire requires an open-collector circuit which needs pull-up resistors and they are not considered energy efficient. The SPI bus do not suffer the same power challenges faced by open-collectors (like  $I^2C$  and 1-Wire) and have little to no protocol overhead. The articles mentioned in the previous Section 3.2 comes to the conclusion that SPI uses the least amount of energy (compared to  $I^2C$ ). However as mentioned, the SPI requires a "slave-select" ( $\overline{SS}$ ) line for every slave device (represented in Figure 2.9), so this can be challenging when we think of small and more I/O constrained devices.

In the paper [26] they "taped out" a chip that implemented the MBus into a temperature sensor system where the power traces required 22.6pJ/bit/chip, which where two orders of magnitude better than the standard  $I^2C$ . The limitations with MBus is that it does not guarantee fairness (nor does  $I^2C$ ). The intention behind the development of MBus was to be used for ultra low power devices and micro scale systems. As mentioned, it is not widely used like the other protocols, which causes problems to get modules with MBus interface.

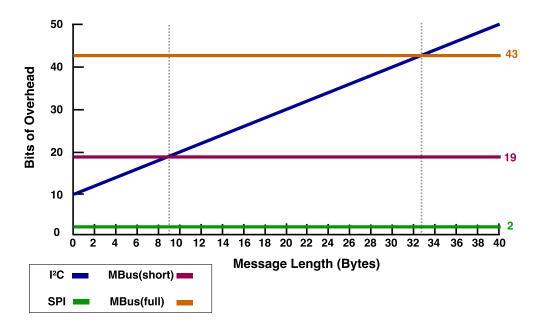

Figure 3.1: Bus overhead. Adapted from source: [26]

In Figure 3.1 we can see the comparison of bits of overhead and message length in bytes as they increase. We see that message overhead is independent for SPI and MBus. For short addressed MBus messages it is 19 bits of overhead and for full addressed messages it is constant 43 bits of overhead. SPI holds the lowest constant of overhead at 2 bits. This makes these buses scale efficiently to messages, while I<sup>2</sup>C steadily increases the bits of overhead when the message length increases. For short-addressed MBus messages we see that they become more efficient than I<sup>2</sup>C after 9 bytes.

Figure 3.2: Total Power Draw. Adapted from source: [26]

In Figure 3.2 we can see the different power draws when clock frequency and node population increases for the  $I^2C$  and MBus configurations [26]. We can see that for both simulated and measured nodes, MBus outperforms the  $I^2C$ .

The best approach for a communication solution for an ultra low power device would either be the SPI or MBus protocol. They both consumes considerably less power than the I<sup>2</sup>C based on the results seen in Section 3.2 and from the paper [26]. The SPI is a widely used interface compared to MBus. There are many modules such as sensors with implemented SPI interfaces, but minimal amount of modules with the MBus interface. This means it would be much cheaper and easier to built a system with the SPI interface. Therefore it will be more beneficial for someone to design an ultra low power system with the SPI interface. This is why I choose to design the SPI master in the next chapter.

28 CHAPTER 3. COMPARING THE BUS PROTOCOLS I<sup>2</sup>C, 1-WIRE, SPI AND MBUS

# **Chapter 4**

# **Design Process of an SPI Master**

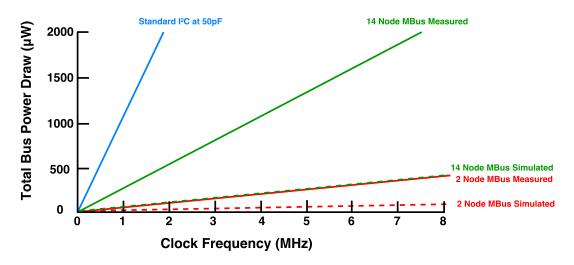

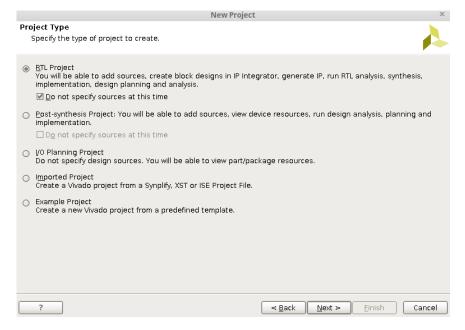

This chapter contains the design process of an SPI master. The design process I am following for my design is seen in Figure 4.1. The first section is to provide the specification for the design, then write the Register Transfer Level (RTL) code for the master design, parallel with the "test bench" in "Xilinx Vivado Design Suite"<sup>a</sup>. We will further run a simulation based on the design file and the "test bench". After that we do the synthesis for the design and then the implementation. When this is done, we program and debug the code and export it to "Xilinx Software Development Kit" (SDK) to write an application software

Figure 4.1: Flowchart of the design process

<sup>&</sup>lt;sup>a</sup>https://www.xilinx.com/products/design-tools/vivado.html

program in "C". This is going to run on the design which will be implemented on the FPGA on the "Zedboard development kit"<sup>b</sup>. The Zedboard uses the "Xilinx Zynq®-7000 All Programmable System on Chip (SoC)". The last step is to test the design with an external temperature sensor. The Appendix B shows how to connect the sensor "LM74" (Appendix A) to the Zedboard.

### 4.1 SPI Specification

For any design it is important to have a detailed and complete specification, so that it works as a foundation for the whole design.

#### 4.1.1 Port List

The port list made for this SPI master design can be seen in the Table 4.1. This port list is custom made by me for this design, but sections of the port list is typical for every SPI master design [22]. This includes the external signals **o\_SPI\_sclk**, **o\_SPI\_ss\_n**, **o\_SPI\_mosi** and **i\_SPI\_miso** which is necessary for an SPI master to be valid [22]. The rest of the signals are for the "user logic" and can be different from one SPI master to another.

The signal **g\_divide\_value** is based on the Equation 4.1, and determines the frequency of the SCLK signal sent to the slave, seen in the Figure 4.2. In Equation 4.1 the  $f_{sclk}$  represents the **o\_SPI\_sclk** signal and the  $f_{clock}$  represents the **i\_clock** signal. An example on how to use the Equation 4.1 could be to set the **g\_divide\_value** = 1, and the clock frequency (i\_clock) to 50MHz. This would equal the SCLK frequency to 25MHz.

$$f_{sclk} = \frac{f_{clock}}{2 \times g_{divider_value}}$$

(4.1)

<sup>&</sup>lt;sup>b</sup>http://zedboard.org/product/zedboard

| Term used        | Definition                 | InputOutput |

|------------------|----------------------------|-------------|

| g_data_bus_width | Data bus Width             | Generic     |

| g_num_of_slaves  | Number of slaves           | Generic     |

| g_divide_value   | Divider value for sclk     | Generic     |

| g_CPOL           | Clock Polarity             | Generic     |

| g_CHPA           | Clock Phase                | Generic     |

| i_clock          | System Clock               | Input       |

| i_reset_n        | Reset (Active Low)         | Input       |

| i_enable         | Initiates transfer         | Input       |

| i_write_data     | Data to Transmit           | Input       |

| o_done           | Signal the end of transfer | Output      |

| o_read_data      | Received data from Slave   | Output      |

| i_addr           | Address for the Slave      | Input       |

| o_SPI_sclk       | Serial Clock Line          | Output      |

| o_SPI_ss_n       | Slave select (Active Low)  | Output      |

| o_SPI_mosi       | Master out Slave In        | Output      |

| i_SPI_miso       | Master In Slave Out        | Input       |

Table 4.1: SPI signals in the design

The SPI master can have several slaves for this design. This would also imply that the number of wires would increase with the increased number of slaves. This can be negative for a small scaled system.

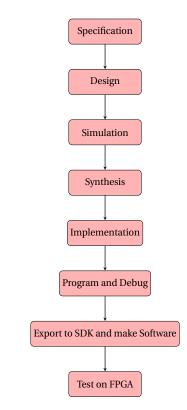

#### 4.1.2 SPI Architecture

The proposed architecture based on this SPI master module can be seen in the Figure 4.2. The inputs on the left side of the block is signals from the user logic and the signals on the right side is for communication with the slave devices. In our example we use only one slave, a Temperature sensor (Appendix A). This architecture is for my SPI master design and is not a standard for other SPI master designs. Another SPI Master design can be seen in [1] and has other signals and architecture than my design.

Figure 4.2: This is the architecture of the design

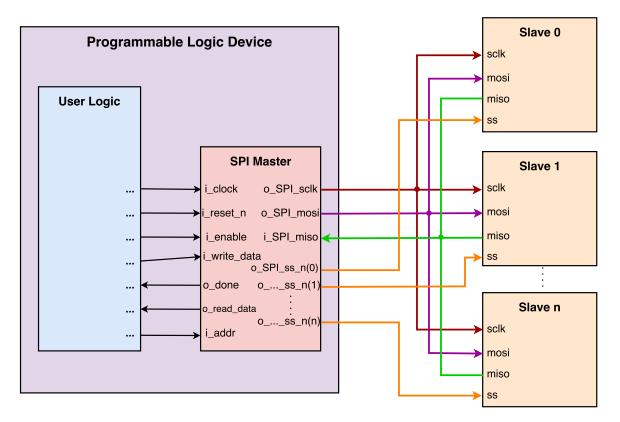

#### 4.1.3 **SPI FSM**

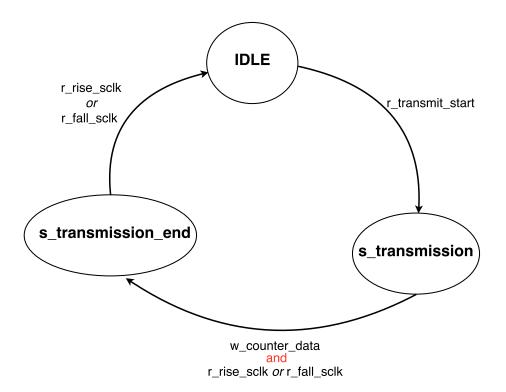

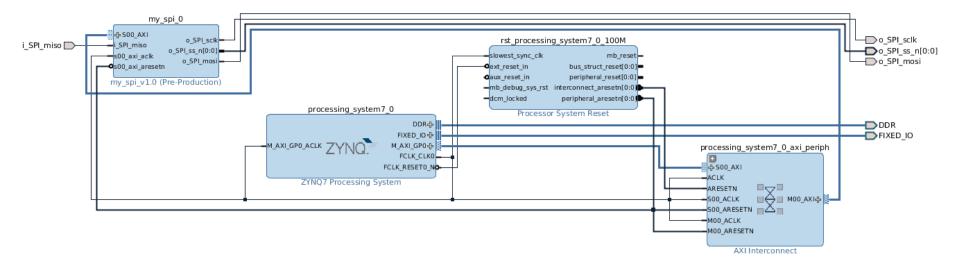

The Figure 4.3 shows how the Finite State Machine (FSM) of the design is constructed. It starts of in the state **IDLE** and jumps to the next state when **r\_transmit\_start** signal goes high. In this state (**s\_transmission**) the transmission happen (sending and receiving data). When the signal **w\_counter\_data** goes high and either **r\_rise\_sclk** or **r\_fall\_sclk** signal goes high (depending which mode you use) it jumps to the next state. The next state is **s\_transmission\_end** and in this state the transmission stops and goes to the next state when **r\_rise\_sclk** or **r\_fall\_sclk** signal goes high (depending which mode you use) is jumps to the next state.

Figure 4.3: This is the FSM of the SPI Master

In the SPI Master design we have three states for executing the transfer of data, seen in Figure 4.3. The standard state machine encoding in Vivado is binary encoding. For this design we use Gray encoding which is known for using lesser power. We should also note that State machine encoding in Gray eliminates any glitches/hazards on combinational equations that depend on the state [2].

| Binar    | ry code     | Gray     | v code      |

|----------|-------------|----------|-------------|

| Sequence | No. toggles | Sequence | No. toggles |

| 00       | 1           | 00       | 2           |

| 01       | 1           | 01       | 1           |

| 10       | 2           | 11       | 1           |

Table 4.2: Binary vs. Gray Encoding

The Table 4.2 represents Binary and Gray encoding for three states. We can see the number of toggles per transition between the states in combination with the sequences of the bits.

```

type state is (s_idle, s_transmission, s_transmission_end);

signal present_state, next_state : state;

attribute enum_encoding: string;

-- Optional attribute IMPORTANT FOR OPTIMAL USAGE

attribute enum_encoding of state: type is "00 01 11";

-- Describes which encoding style used

```

#### Figure 4.4: FSM VHDL code

In Figure 4.4 we see how this is implemented in VHDL. We can see the three states **s\_idle**, **s\_transmission** and **s\_transmission\_end** is declared in the first line. The last line determines the encoding style, which in our case is Gray. This is retrieved from Appendix D.1.

#### 4.1.4 SPI Addressing

The Table 4.3 show how the addressing works with **4** slaves for this design. If you choose to address slave 3 you send 0x3 to the **i\_addr** signal and the MSB of **o\_SPI\_ss\_n** goes low for slave 3. You can see this simulated in the Figure 4.5. If you want to communicate with slave 1 you can send 0x1 to **i\_addr** and the **o\_SPI\_ss\_n** goes low for the LSB seen in Table 4.3. This can be seen simulated in the Figure 4.6.

|         | i_addı      |        | o_SPI_ss_n  |

|---------|-------------|--------|-------------|

| Name    | Hexadecimal | Binary | 0_311_85_11 |

| slave 0 | 0           | 0000   | 1110        |

| slave 1 | 1           | 0001   | 1101        |

| slave 2 | 2           | 0010   | 1011        |

| slave 3 | 3           | 0011   | 0111        |

Table 4.3: SPI Master addressing

# 4.2 SPI Simulation

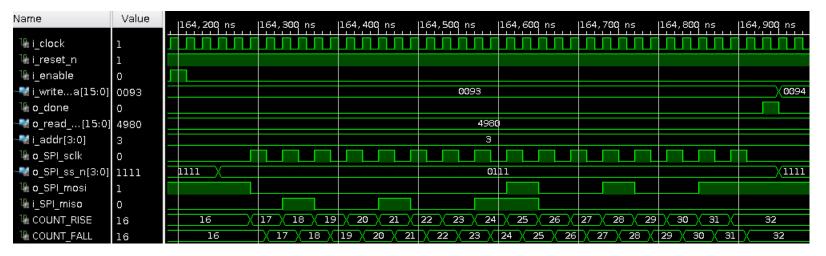

The RTL code for the SPI master logic can be found in Appendix D.1 and the code for the "test bench" can be found in Appendix D.2. The behaviour simulation for this design can be seen in Figure 4.5 and Figure 4.6. The Figure 4.5 represents the simulation for the SPI in mode 2 (CPOL = 0 and CPHA =1) and Figure 4.6 represents the simulation of the SPI in mode 3 (CPOL = 1 and CPHA = 1). The modes are explained in Section 2.5.3, and the timing diagram for these modes are defined in Figure 2.11. The purpose for the "test bench" is to test the behavior of the SPI master, and verify that it functions correctly. We use the "test bench" to evaluate all the "user logic" signals and the standard SPI signals.

Note that the "test bench" code in Appendix D.2 have some parameters that may vary from the simulations. The **i\_clock** signal for these simulations runs at 50MHz which

means the **c\_CLOCK\_PERIOD** from the "test bench" is set to 20ns. This will assign the **o\_SPI\_sclk** signal to run at a frequency of 25MHz. The **g\_num\_of\_slaves** are set to "4" for these simulations. Also the line that addresses the slaves in Appendix D.2 (page 99) is set to slave 3 (0x03) in Figure 4.5 and to slave 1 (0x01) in Figure 4.6.

The difference between these two simulations are the SPI modes and the slave addressing. We can see the difference in the **o\_SPI\_sclk** signal behaving as low (logic "0") when not used (IDLE state) in mode 2 (Figure 4.5), and high (logic "1") when not used (IDLE state) for mode 3 (Figure 4.6). From Figure 4.5 the SPI master addresses "slave 3" and in the Figure 4.6 the SPI master addresses "slave 1". This can be distinguished by the signal **i\_addr** = 3 and the **o\_SPI\_ss\_n** signal set to logic "0" for slave 3 (0111) seen in Figure 4.5.

From the Figure 4.5 we see the **i\_clock** signal running at 50MHz and the **i\_reset\_n** signal high (not enabled). The **i\_enable** signal asserts at 164,2ns, which assert the **r\_transmit\_start** register signal in the SPI master design. From Figure 4.3 we can see that this register is responsible for the state jumping from "IDLE" to "s\_transmission". Now the transition can begin. From Figure 4.5 we see the **o\_SPI\_ss\_n** signal go low for the slave addressed as "3" seen by the **i\_addr** signal being set to "3". This initiates the communication between the master and the selected slave. The data sent from the slave to master can be seen by that the **i\_SPI\_miso** signal is "0xC9" in Hex ("11001001" in binary). The first bit in **i\_SPI\_miso** is sampled on the second falling edge of the **o\_SPI\_sclk** signal (because CPOL=1). The data from **i\_SPI\_miso** is sent to the "user logic" signal **o\_read\_date** seen by value "4980" in Hex, (0100 1001 1000 000 in binary). This is "4980" in Hex because it reads **i\_SPI\_miso** from all the sixteen cycles.

After eight clock cycles of the **o\_SPI\_sclk** signal, the first bit of the data in **o\_SPI\_mosi** is sampled. The data that is sent from the master to the slave is seen by the "user logic" signal **i\_write\_data** equal to "0x93" in Hex ("10010011" in binary). After the full sixteen clock cycles the signal **o\_done** is asserted, and the **o\_SPI\_ss\_n** goes high for the selected slave. This also includes the **w\_counter\_data** counter signal in the SPI master seen in Figure 4.3, which means we jump to state "s\_transmission\_end". This concludes that the transmission is finished and we end up in state "IDLE". The signals that are not mentioned from the figures are for debug purposes and can be overlooked.

Figure 4.5: Simulation of the SPI Master (Mode 2)

Figure 4.6: Simulation of the SPI Master (Mode3)

38

### 4.3 SPI Registers

There are two registers used for this design. Both have a width of 32 bits and one is primarily for writing (input for the SPI master) and one is for reading (output from the SPI master). In Figure 4.7 we can see how this is implemented in VHDL. The two registers are named **slv\_reg0** and **spi\_to\_ps**.

Table 4.4: slv\_reg0, D31 to D16

| D31       | D30      | D29 | D28 | D27 | D26 | D25 | D24 | D23     | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

|-----------|----------|-----|-----|-----|-----|-----|-----|---------|--------|-----|-----|-----|-----|-----|-----|

| i_reset_n | i_enable |     |     |     |     |     |     | i_write | e_data |     |     |     |     |     |     |

Table 4.5: slv\_reg0, D15 to D0

| D15    | D14    | D13 | D12    | D11 | D10 | D9 | <b>D8</b> | D7 | D6 | D5 | D4 | D3 | D2 | D1 | <b>D0</b> |

|--------|--------|-----|--------|-----|-----|----|-----------|----|----|----|----|----|----|----|-----------|

| i_writ | e_data | Х   | i_addr | Х   | Х   | Х  | Х         | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х         |

The Table 4.4 shows what data is stored in the range bit 31 to bit 16 in the **slv\_reg0**. The Table 4.5 shows the data stored in register **slv\_reg0** from bit 15 to bit 0. The first bit is **i\_reset\_n** which can be set to "0" to reset the SPI master. The second bit place (D30) is reserved for the **i\_enable** signal which is set to high to enable the transmission. The next places are for the **i\_write\_data**, which is the size of 16, which means that it takes up 16 bits. This is customized and can also be selected to be the size of 8, by changing the **g\_data\_bus\_width** value to 8 instead of 16. This will affect the register size automatically to only contain 8 bits of **i\_write\_data**. The **i\_addr** in Table 4.5 only takes up 1 bit because in our design we use one slave. If we want to use more than one slave, we can increase the **g\_num\_of\_slaves** value, and this will in turn increase the **space** taken in the register **slv reg0**.

Table 4.6: spi\_to\_ps, D31 to D16

| D31    | D30   | D29    | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

|--------|-------|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| o_done | o_rea | d_data |     |     |     |     |     |     |     |     |     |     |     |     |     |

Table 4.7: spi\_to\_ps, D15 to D0

| D15         | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | <b>D6</b> | D5 | D4 | D3 | D2 | D1 | <b>D0</b> |

|-------------|-----|-----|-----|-----|-----|----|----|----|-----------|----|----|----|----|----|-----------|

| o_read_data | Х   | Х   | Х   | Х   | Х   | Х  | Х  | Х  | Х         | Х  | Х  | Х  | Х  | Х  | Х         |

The Table 4.6 and Table 4.7 shows where the output signals takes place in the **spi\_to\_ps** register. Table 4.6 shows what data is stored in the range bit 31 to bit 16, and Table 4.7 shows what data is stored in the range bit 15 to bit 0. In Table 4.6 we see that first place is reserved to the **o\_done** signal, which goes high when the transmission in the SPI master design is finished. The next places are for **o\_read\_data**, which takes up 16 bits because of the **g\_data\_bus\_width** = 16 in our design. If we change this down to 8 this will also automatically affect the **spi\_to\_ps** register so **o\_read\_data** only takes up 8 bits.

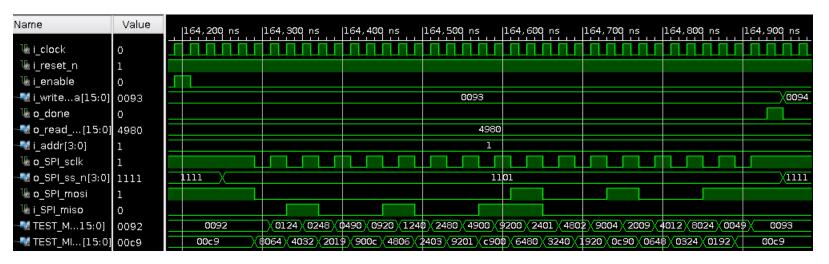

#### 4.3.1 Implementing the Registers

To communicate with the design through the AXI interface we need to read and write from registers. This is made custom for this design in the "port map" section in the "my\_spi\_v1\_0\_S00\_AXI.vhd" file. The whole code is listed in Appendix E.

```

port map(

-- USER LOGIC ------

i_clock => S_AXI_ACLK,

i_reset_n => slv_reg0(31),

i_enable => slv_reg0(30),

i_write_data => slv_reg0(29 downto (30 - g_data_bus_width)),

o_done => spi_to_ps(31),

o_read_data => spi_to_ps(30 downto (31 - g_data_bus_width)),

i_addr => slv_reg0(12 downto (13 - g_num_of_slaves)),

-- SPI MASTER INTERFACE -----

o_SPI_sclk => o_SPI_sclk,

o_SPI_ss_n => o_SPI_ss_n,

o_SPI_mosi => o_SPI_mosi,

i_SPI_miso => i_SPI_miso

);

```

Figure 4.7: VHDL code of the registers