# Modeling, simulation and control of the alternate arm converter

### **Donatas Dembinskas**

Wind Energy

Submission date: August 2017

Supervisor: Elisabetta Tedeschi, IEL

Co-supervisor: Pavol Bauer, TU DELFT Electrical Sustainable Energy

Abel Taffese, IEL Gilbert Bergna, IEL

Norwegian University of Science and Technology Department of Electric Power Engineering

# Modeling, simulation and control of the alternate arm converter

in partial fulfillment of the requirements for the degrees of

MSc in Electrical Engineering at Delft University of Technology & MSc-Technology in Wind Energy at Norwegian University of Science and Technology,

> under the European Wind Energy Masters programme. To be publicly defended on

> > Monday 21st August 2017 at NTNU

| Cupanzican .      | Prof. Elisabetta Tedeschi   | NTNU     |

|-------------------|-----------------------------|----------|

| Supervisor :      | Prof. Pavol Bauer           | TU Delft |

| Co-Supervisor :   | PhD s. Abel Assegid Taffese | SINTEF   |

|                   | Prof. Elisabetta Tedeschi   | NTNU     |

| Thesis Committee: | Prof. Pavol Bauer           | TU Delft |

|                   | Assistant Prof. Zian Qin    | TU Delft |

| <br> | <br> |  |

|------|------|--|

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

### **Preface**

Master Thesis was carried out at the Norwegian University of Science and Technology, Department of Electric Power Engineering and Delft University of Technology, Department of Electrical Sustainable Energy during the spring semester of 2017.

This Master Thesis is for the joint education programme European Wind Energy Master (EWEM) with a focus of Electrical Power Systems (EPS) track. It was wrote for two universities Norwegian University of Science and Technology and Delft University of Technology.

I hereby declare that this thesis titled "Modeling, simulation and control of the alternate arm converter" and the work presented in it is my own.

Trondheim,  $04^{th}$  August 2017

Donatas Dembinskas

## Acknowledgment

I would like to put my words of gratitude to my two supervisors Professor Elisabetta Tedeschi, Norwegian University of Science and Technology (NTNU) and Professor Pavol Bauer, Delft University of Technology (TUDelft), for their experienced guidance and generous support, despite their busy schedules. Furthermore I would like to thank my cosupervisor PhD candidate Abel Assegid Taffese, (NTNU), for his support and and guidance. Whenever I had doubts of some theories aspects or I lacked of self confidence, his words motivated and helped me to keep my focus on this thesis. His help was priceless for guidance and moral support.

I also wish to thank Postdoctoral fellow Gilbert Bergna-Diaz for his advice and guidance.

I have to remember my friends and colleagues from EWEM study program, electrical power system track, for reminding me that I am not alone in this though ride and encouraging me to keep going.

Finally, I want to thank my Family back home in Lithuania, for being supportive and understanding of my desires to learn more for being on this long journey. Special thank goes to my Father Jonas, which guided and believed in me through this long journey.

Donatas Dembinskas

$04^{th}$  August 2017

### **Abstract**

The fast evolving technologies have resulted in an extensive use of the power electronics. More intelligent grids can be made by implementing the power electronic devices. In response to global increasing energy demand and significance of the clean and sustainable future the renewable energy sources, like sun, wind and water are exploited. Power electronic devices together with the renewable energy resources create a new type of grids. The new type of grids create a new challenges. Nowadays more often the new energy production resources are moved outside the land in the seas or the oceans, while the land is used for the accommodation of people. The energy resources moved outside the land require the transmission of the energy, where it is used. Connecting all those three dots: power electronic devices, sustainable and clean future and the new location of the renewable energy sources results in the question how to create the grid for energy transmission and transit the energy in the cheapest and the most sustainable way.

The offshore energy mostly are delivered to the land by the cables. With increasing length of the cable losses increases, in order to avoid losses the AC voltage are transformed to the DC voltage. The transformation of the voltage from AC/DC requires somewhere in the sea or ocean a substation. A substation contains a converter where the all nearby distributed energy resources are connected. The voltage is transformed to DC in these substations. The voltage are transformed again from DC/AC in the next substation usually located onshore. The costs and the reduction of the substation size requires to look for a new and better voltage transformation topology.

In this study a new hybrid voltage source converter based topology is modeled, simulated and controlled. This new topology is usually known as alternate arm converter. For the simulation developing MATLAB/Simulink software is used. With the MATLAB/Simulink software the model of alternate arm converter is developed from the scratch. Firstly the simple one-phase average mathematical model is developed and implemented in the simulation. Then the balancing control between the arms voltages is implemented in the onephase model. The simple one-phase with a simplified control model is evaluated. Then the three-phase model is created in the same MATLAB/Simulink software. Firstly the threephase model is evaluated as working in the island mode, which means that it is working alone, not connected to the grid. The improved control is implemented in this 3-phase model in order to increase the performance of the converter. The 3-phase model with improved control model is connected to the grid by using MATLAB/Simulink software. The grid connection is simulated with the voltage sources and phase locked loop control. The phase locked loop constantly adjust the voltage in order to lock onto the phase and frequency. Furthermore it is extract a voltage angle for the used dq0 transformation, which simplifies control. The grid connected model is simulated and evaluated. After this evaluation the MATLAB/Simulink simulation model of the alternate arm converter, together with control is connected in the point to point scheme. The point to point scheme repre-

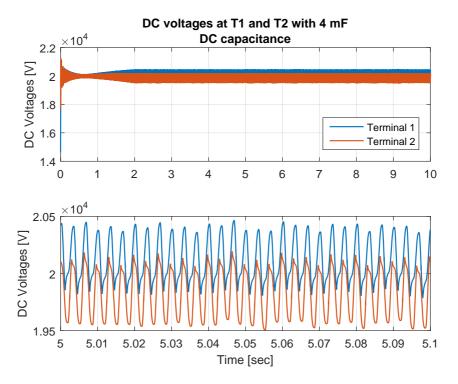

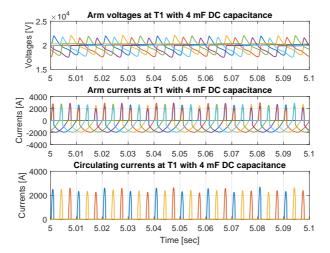

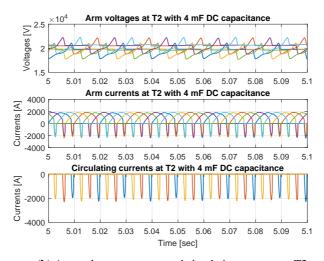

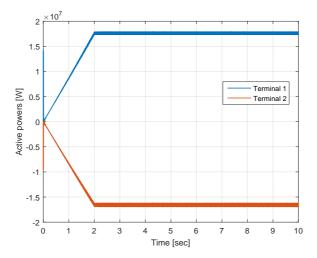

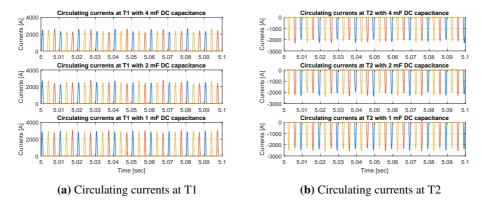

sents the energy transmission from the one point to another or in the different case it can also transmit the energy in the other side. The point to point system is represented in the MATLAB/Simulink model, together with additional droop control, which controls the DC voltage accordingly to the active power. If the active power reaches the maximum value the DC voltage decreases accordingly to the drop value and the way around. The six study cases are simulated in the MATLAB/Simulink software, with the point to point connection. In the first case the operation points are evaluated of the system and the behaviour of the AC voltages, AC currents, DC voltage, arm voltages, arm currents and circulating currents are observed in the terminal 1 and terminal 2, which is AC/DC and DC/AC converters, respectively. The second study case is aimed to inspect the DC side capacitance effect to the DC voltage. In this study case is evaluated that by increasing the DC side capacitance the DC voltage ripple reduces, therefore the AC currents with less harmonic distortions are presented. The third case shows the droop control behaviour for the different drop values. When the drop value is increasing the gain value of the droop control decreases and the smaller deviation of the active power is presented. The forth, fifth and sixth cases arise, because of the problem confronted during the operating point case simulations. The voltages between the upper and lower arms in some of the operating points are not balanced. This issue creates an arm voltage balancing problem, which in the forth study case is solving by increasing overlap time. The observation is made, that by increasing overlap time the balance between the arm voltages becomes better, but the alternate arm converter are forced to approach and change the topology to modular multilevel converter, when the 10 ms is reached in this case. The fifth study case investigates the cell capacitance effect for the arm voltage balance. In this case was found that increasing or decreasing the cell capacitance in the submodules, do not fix the arm voltage balancing problem. This approach makes voltage balance between the arms even worse. The last study case introduces the case of the arm voltage balance technique by using third harmonic current flow together with 1 ms overlap time. This study case requires a minor changes in the point to point system. The results of this technique are evaluated and it shows that this type of the balancing technique is the best technique of the voltage balancing between the arms in this system of the point to point connection.

# **Table of Contents**

| Pr | eface   |                                                        | i    |

|----|---------|--------------------------------------------------------|------|

| A  | cknov   | vledgment                                              | iii  |

| A۱ | bstrac  | et e                                                   | v    |

| Ta | ble of  | f Contents                                             | viii |

| Li | st of ' | Tables                                                 | ix   |

| Li | st of l | Figures                                                | XV   |

| Αl | brev    | iations                                                | xvi  |

| 1  | INT     | RODUCTION                                              | 1    |

|    | 1.1     | Background                                             | 1    |

|    | 1.2     | Objective of the work and motivation                   | 2    |

|    | 1.3     | Outline of the thesis                                  | 3    |

| 2  | HIG     | CH VOLTAGE TRANSMISSION TECHNOLOGIES                   | 5    |

|    | 2.1     | High voltage alternating current technology            | 5    |

|    | 2.2     | High voltage direct current technology                 | 7    |

|    | 2.3     | Comparison of the HVAC and HVDC in transmission system | 11   |

| 3  | TOI     | POLOGY OF THE CONVERTERS                               | 14   |

|    | 3.1     | Line current commutated converters                     | 14   |

|    | 3.2     | Voltage source converters                              | 18   |

|    |         | 3.2.1 2 level voltage source converters                | 19   |

|    |         | 3.2.2 Modular multilevel converters                    | 19   |

| 4  | MO         | DELING AN ALTERNATE ARM CONVERTER                                        | 21         |

|----|------------|--------------------------------------------------------------------------|------------|

|    | 4.1        | Topology of the alternate arm converter and operation principle          | 21         |

|    | 4.2        | Types of VSC HVDC models                                                 | 22         |

|    | 4.3        | Mathematical representation of the alternate arm converter average model | 23         |

|    | 4.4        | 1-phase alternate arm converter average model Simulation in Simulink     | 29         |

|    | 4.5        | Sweet spot derivation and implementation in the average model            | 34         |

|    | 4.6        | Implementation of the overlap in the average model                       | 39         |

| 5  | COI        | NTROL STRATEGY OF AN ALTERNATE ARM CONVERTER                             | 43         |

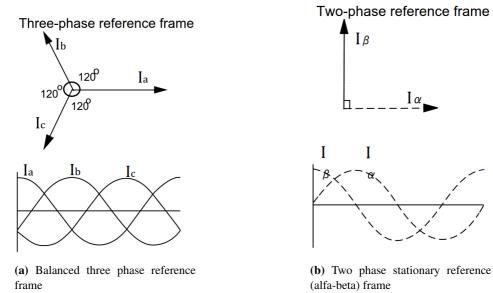

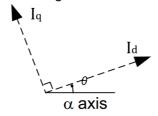

|    | 5.1        | Park-Clarke transformation                                               | 43         |

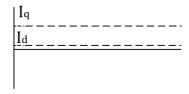

|    | 5.2        | Implementation of the control strategy                                   | 45         |

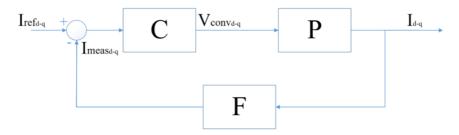

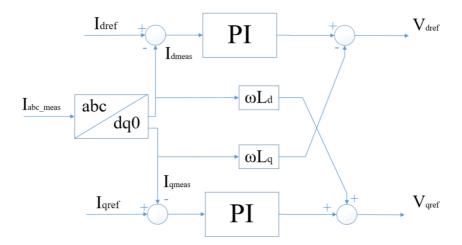

|    |            | 5.2.1 Inner current control                                              | 46         |

|    |            | 5.2.2 PI regulator                                                       | 46         |

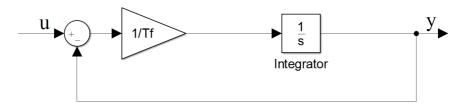

|    |            | 5.2.3 Filter                                                             | 47         |

|    |            | 5.2.4 System                                                             | 47         |

|    |            | 5.2.5 Tuning of the regulator                                            | 48         |

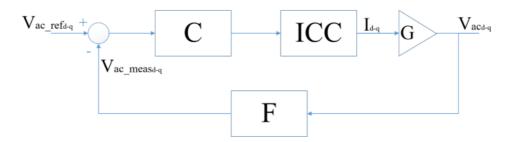

|    | 5.3        | Voltage control                                                          | 52         |

| 6  | ALT        | ERNATE ARM CONVERTER IN THE POINT TO POINT CONNEC-                       |            |

|    | TIO        | N                                                                        | 57         |

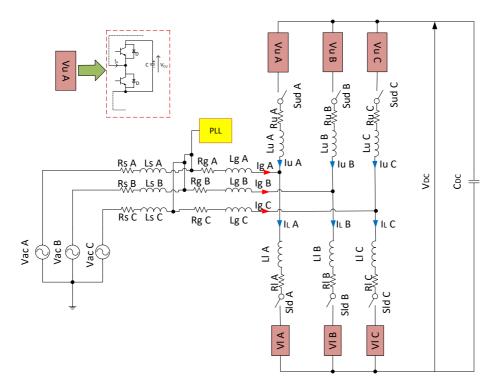

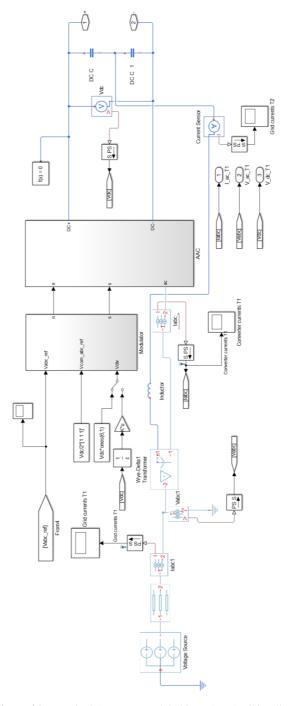

|    | 6.1        | System components                                                        | 58         |

|    |            | 6.1.1 Converter                                                          | 58         |

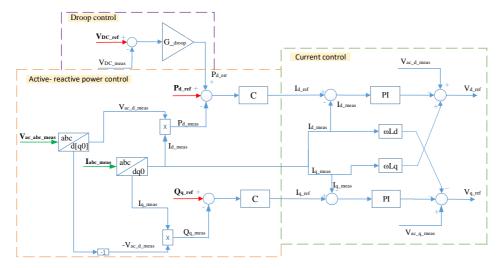

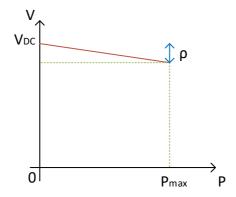

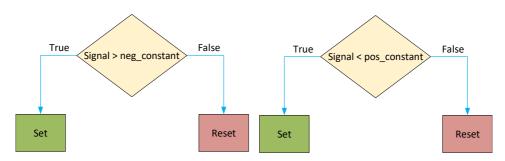

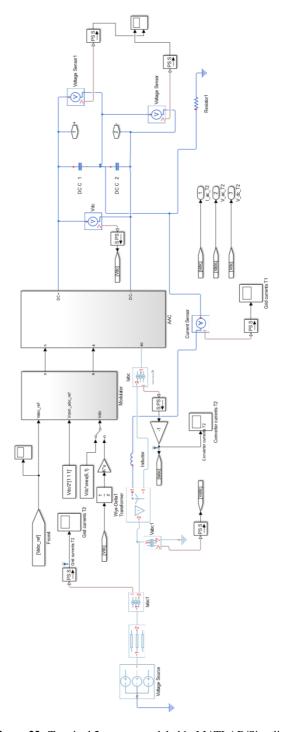

|    |            | 6.1.2 Point to point connected converters control                        | 59         |

|    |            | 6.1.3 Cable                                                              | 64         |

|    | 6.2        | Study cases                                                              | 65         |

|    |            | 6.2.1 Operation points of the system and behaviour                       | 66         |

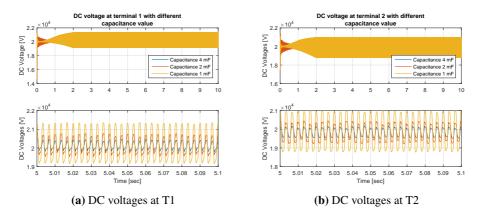

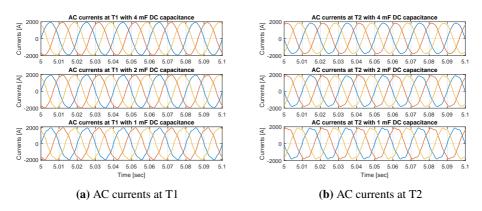

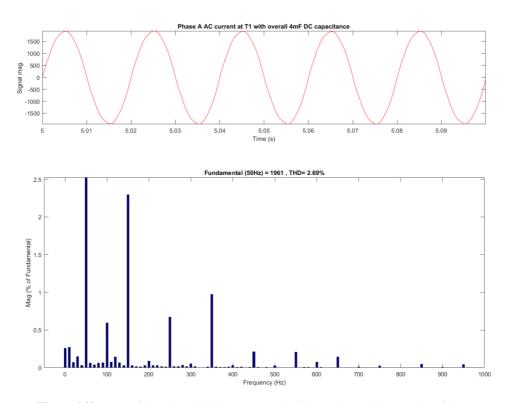

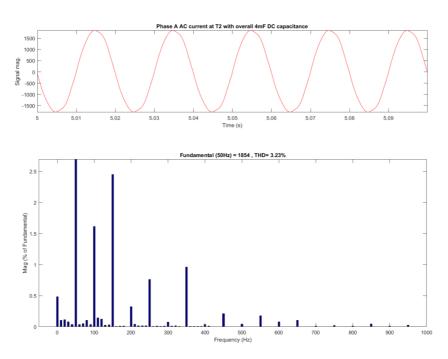

|    |            | 6.2.2 Effect of the DC side capacitance                                  | 84         |

|    |            | 6.2.3 Effect of the different droop control drop values                  | 98         |

|    |            | 6.2.4 Different overlap times                                            | 101        |

|    |            | 6.2.5 Different values of the capacitance in the cell                    | 110        |

|    |            | 6.2.6 Balancing technique with the third harmonic current                | 114        |

| 7  | COI        | NCLUSION                                                                 | 123        |

| 8  | FUT        | TURE WORK                                                                | 125        |

| Bi | hliogi     | raphy                                                                    | 126        |

|    | Ü          |                                                                          |            |

| Αŗ | pend<br>.1 |                                                                          | 132<br>132 |

|    |            | •                                                                        |            |

| Aŗ | pend       |                                                                          | 151        |

|    | .2         | MATLAB codes                                                             | 151        |

| Aŗ | pend       |                                                                          | 159        |

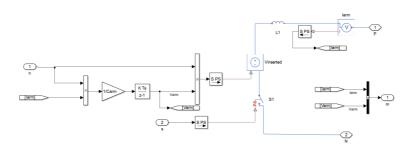

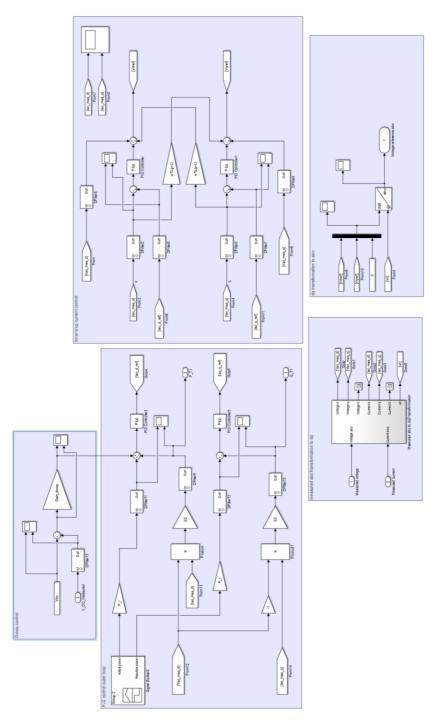

|    | .3         | Simulink models of the point to point connection                         | 160        |

## List of Tables

| 4.1 | Data of the 1-phase average model alternate arm converter |    |  |  |

|-----|-----------------------------------------------------------|----|--|--|

| 6.1 | System and converters parameters                          | 58 |  |  |

| 6.2 | Cable parameters                                          | 65 |  |  |

# List of Figures

| 1.1  | Example of the possible realization of the AAC                          | 3  |

|------|-------------------------------------------------------------------------|----|

| 2.1  | AC transmission diagram [1]                                             | 6  |

| 2.2  | Future aspect of the possible HVDC network connection [2]               | 8  |

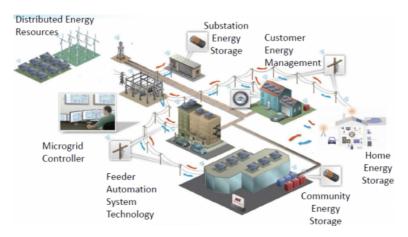

| 2.3  | Network example of the distributed energy resources connection [3]      | 8  |

| 2.4  | Monopolar configurations [4]                                            | 9  |

| 2.5  | Bipolar configurations [4]                                              | 10 |

| 2.6  | Back to back configuration [4]                                          | 10 |

| 2.7  | Multiterminal configuration [4]                                         | 11 |

| 2.8  | Break-even distance of the costs for the HVAC and HVDC systems [5]      | 13 |

| 3.1  | Thyristor symbol [6]                                                    | 15 |

| 3.2  | 3-phase 6-pulse converter                                               | 15 |

| 3.3  | Commutation of the rectifier operation [7]                              | 16 |

| 3.4  | Commutation of the inverter operation [7]                               | 17 |

| 3.5  | IGBT representations                                                    | 18 |

| 3.6  | Two level 3-phase voltage source converter topology                     | 19 |

| 3.7  | Modular multilevel converter topology                                   | 20 |

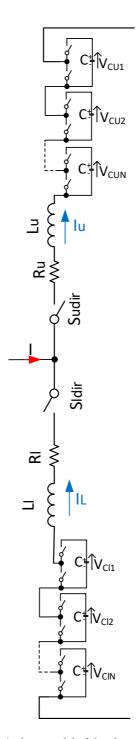

| 4.1  | Alternate arm topology                                                  | 22 |

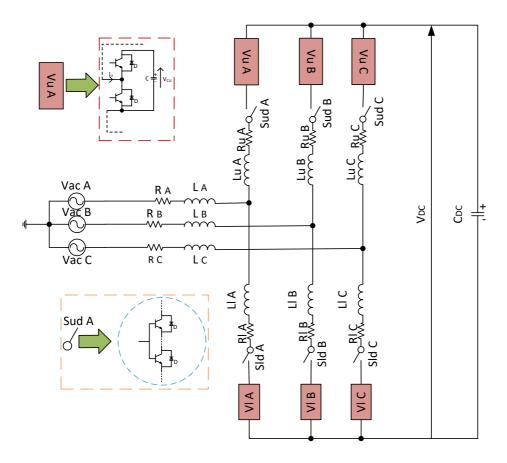

| 4.2  | Submodule connection types                                              | 24 |

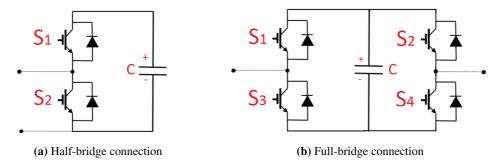

| 4.3  | Ideal half-bridge submodule                                             | 25 |

| 4.4  | Ideal A phase model of the alternate arm converter                      | 26 |

| 4.5  | Kirchhoff's voltage law for the alternate arm converter                 | 28 |

| 4.6  | Average model of the alternate arm converter A phase in Simulink        | 31 |

| 4.7  | Average model of the upper arm stack voltage in Simulink                | 32 |

| 4.8  | Average model of the lower arm stack voltage in Simulink                | 32 |

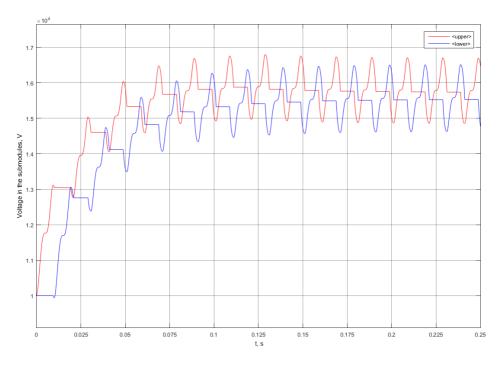

| 4.9  | Voltage in the sub-modules for upper and lower arm without balancing    | _  |

|      | techniques                                                              | 33 |

| 4.10 | Voltage in the sub-modules for upper and lower arm with double AC volt- | _  |

|      | age input                                                               | 34 |

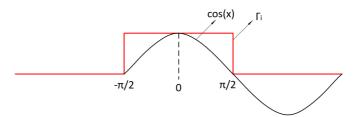

| 4.11 | Cosine wave form and Gamma window representation                          | 35 |

|------|---------------------------------------------------------------------------|----|

|      | Voltage in the sub-modules for upper and lower arm with sweet spot volt-  |    |

|      | age input                                                                 | 37 |

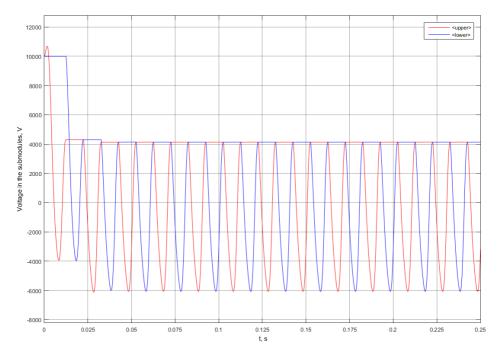

| 4.13 | Arm voltages for upper and lower arms with a "sweet spot" voltage applied | 38 |

|      | Arm currents for upper and lower arm with "sweet spot" voltage input      | 38 |

|      | Overlap implementation in phase A for the upper and lower arms            | 40 |

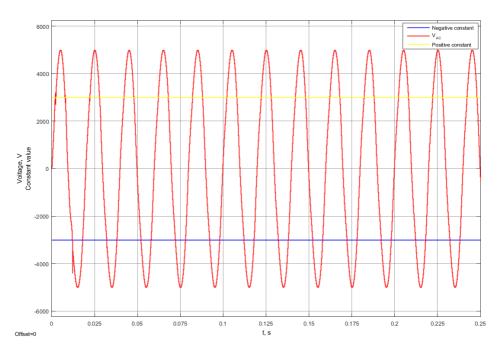

|      | Signals provided to gain overlap                                          | 40 |

| 4.17 | Arm voltages with 1 ms overlap implementation                             | 41 |

|      | Arm currents with 1 ms overlap implementation                             | 42 |

| 0    | Time entremes with Time overlap imprementation                            |    |

| 5.1  | Park-Clarke transformation [8]                                            | 44 |

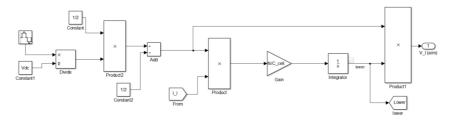

| 5.2  | General block diagram of the current controller                           | 46 |

| 5.3  | Filer representation in the Simulink                                      | 47 |

| 5.4  | Decoupling terms representation in ICC                                    | 48 |

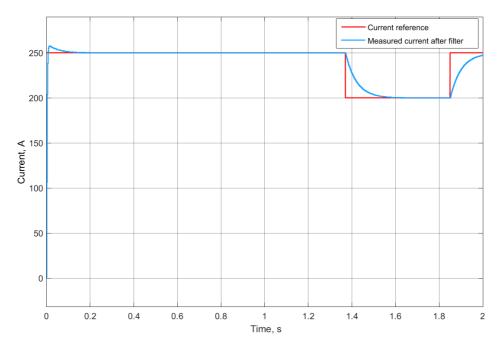

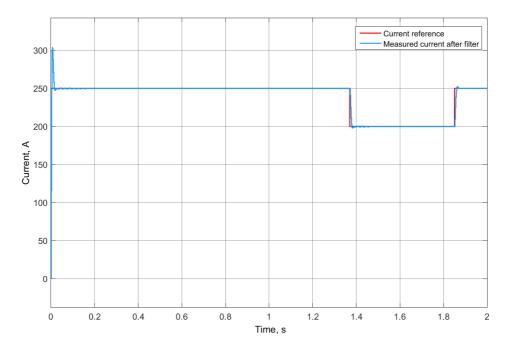

| 5.5  | Response of the ICC for the first order system                            | 50 |

| 5.6  | Response of the ICC for the second order system                           | 52 |

| 5.7  | General block diagram of the voltage control                              | 53 |

| 5.8  | Reference signal and measured signal of the OVC                           | 55 |

| 5.9  | Reference signal and measured signal of the secondary controller with im- | 55 |

| 5.7  | plemented primary control                                                 | 56 |

|      | promoticed primary control                                                | 50 |

| 6.1  | Block diagram of the point to point connection                            | 57 |

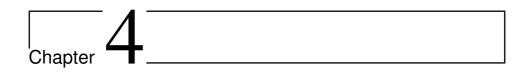

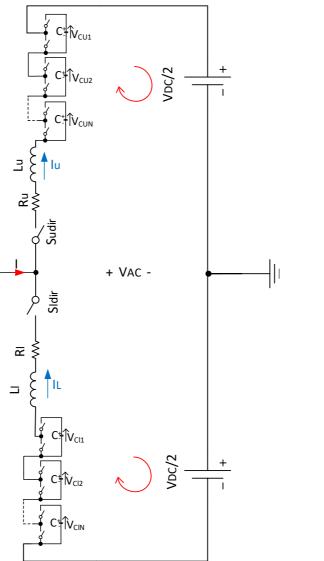

| 6.2  | AAC 3-phase model                                                         | 59 |

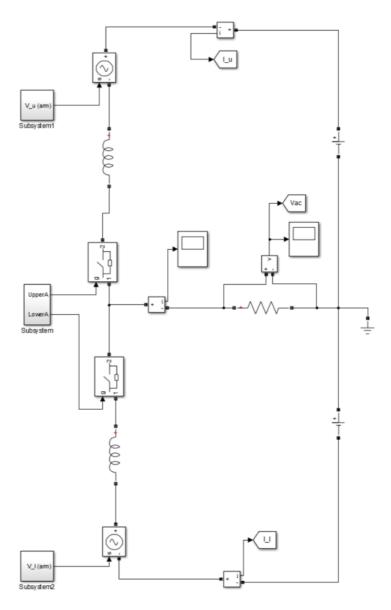

| 6.3  | Droop, outer and inner controllers                                        | 60 |

| 6.4  | Droop control characteristic                                              | 62 |

| 6.5  | The flow chats of the overlap                                             | 63 |

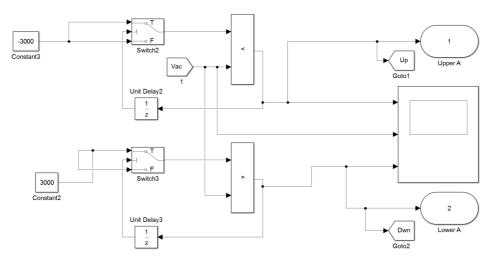

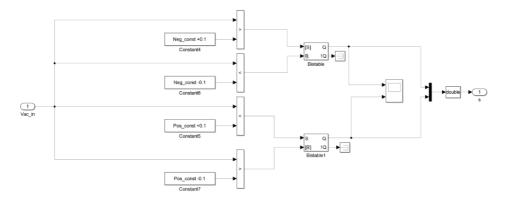

| 6.6  | Overlap control implementation in MATLAB/Simulink                         | 64 |

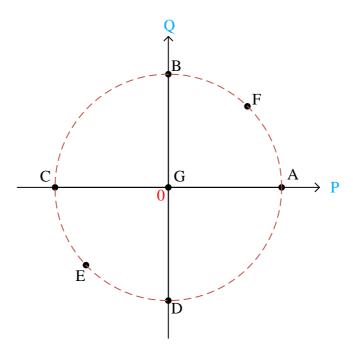

| 6.7  | Simulated operation points                                                | 67 |

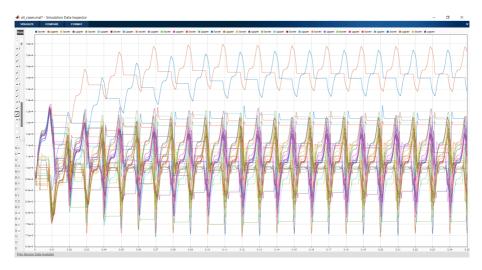

| 6.8  | Operation points during 10 s simulation                                   | 68 |

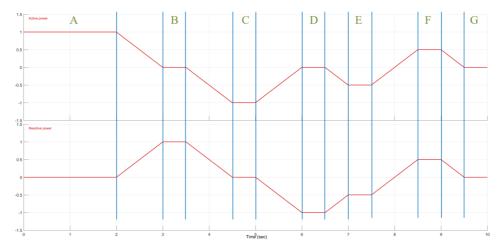

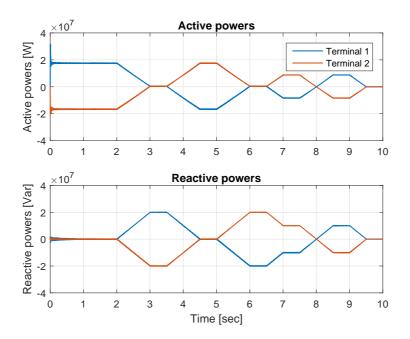

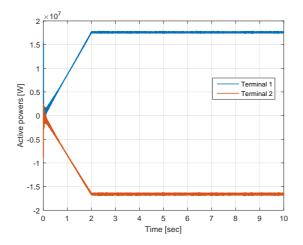

| 6.9  | Active and reactive power injection during simulation                     | 69 |

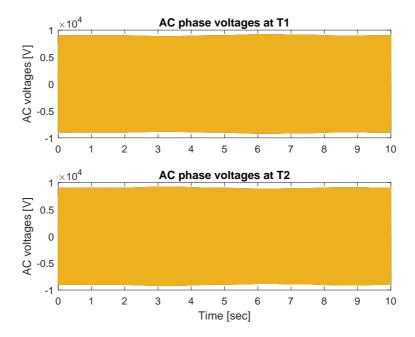

|      | AC voltages during full simulation of 10 s in T1 and T2                   | 69 |

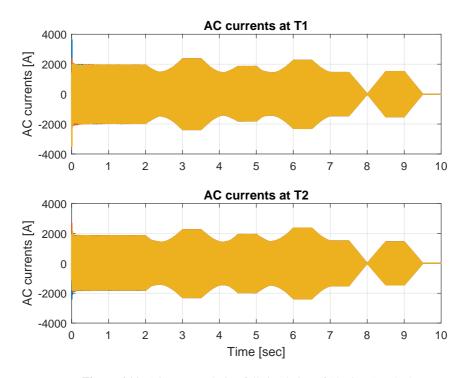

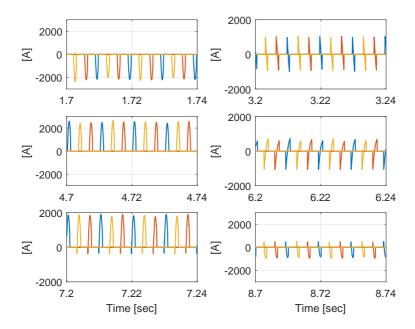

|      | AC currents during full simulation of 10 s in T1 and T2                   | 70 |

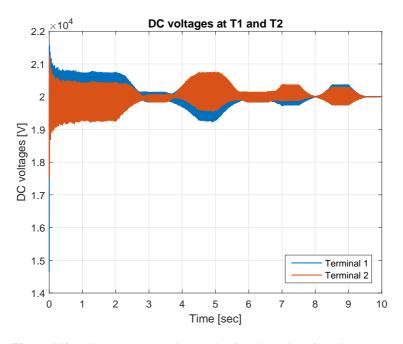

|      | DC voltages comparison during full simulation of 10 s in T1 and T2        | 71 |

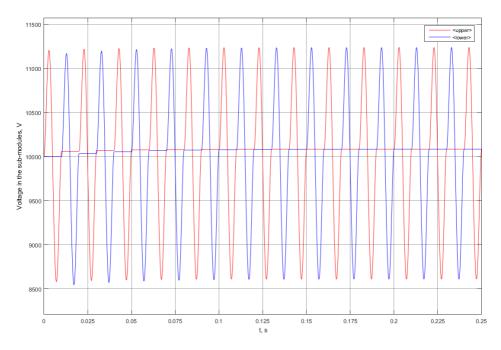

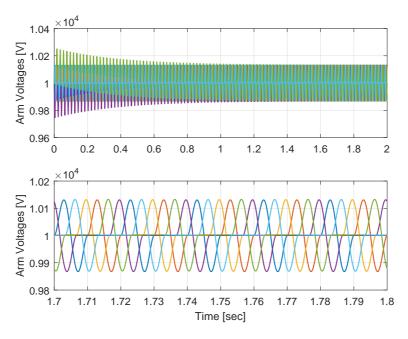

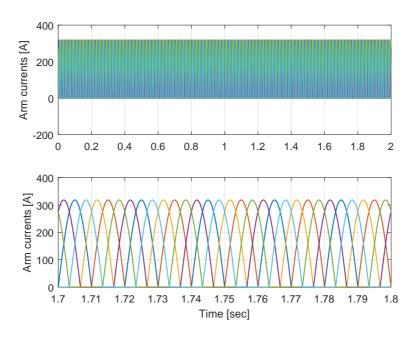

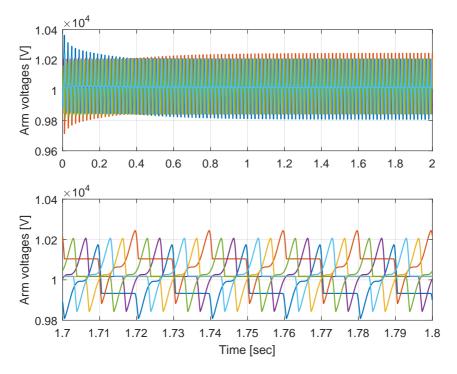

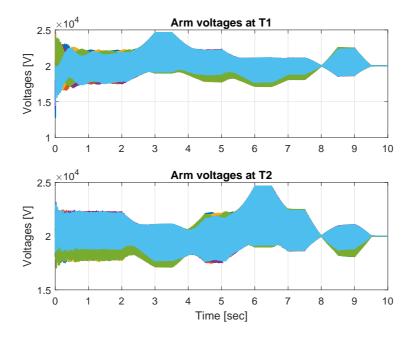

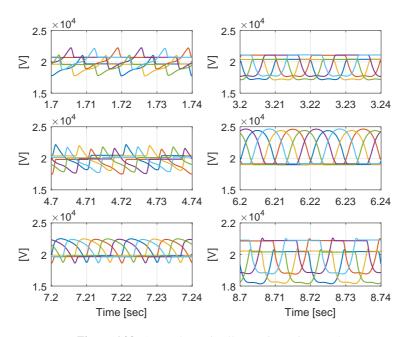

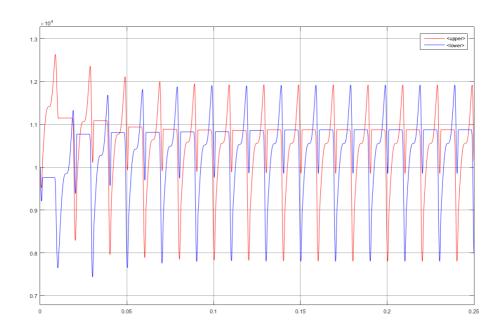

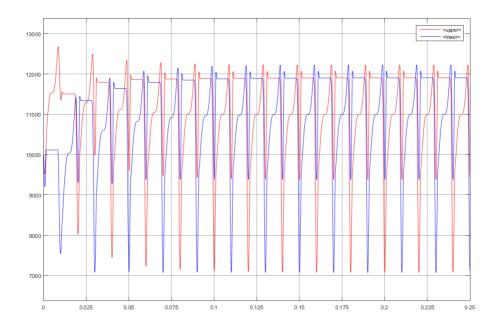

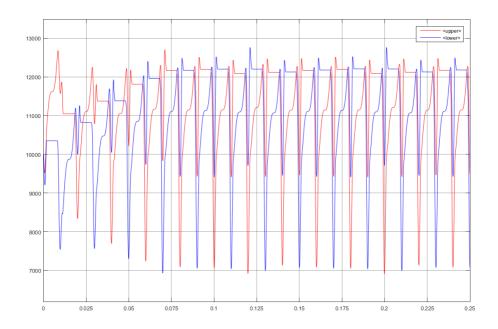

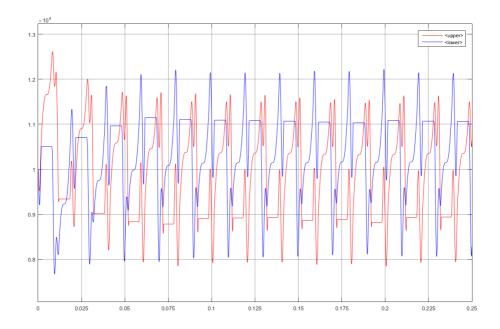

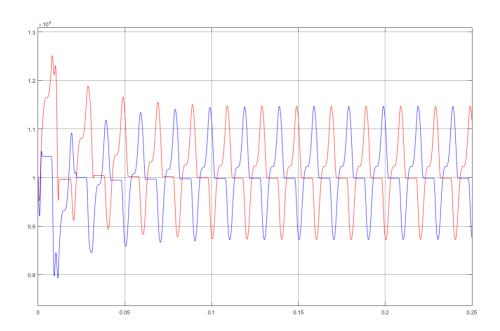

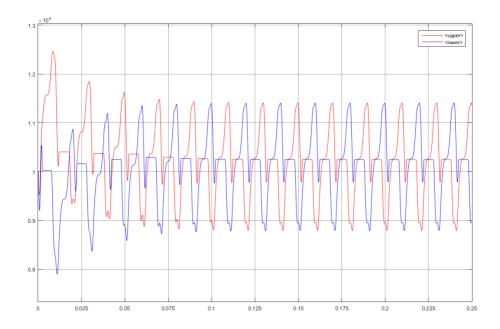

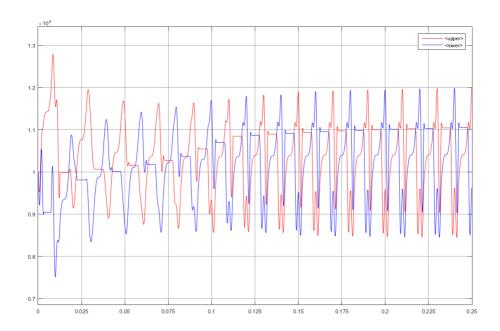

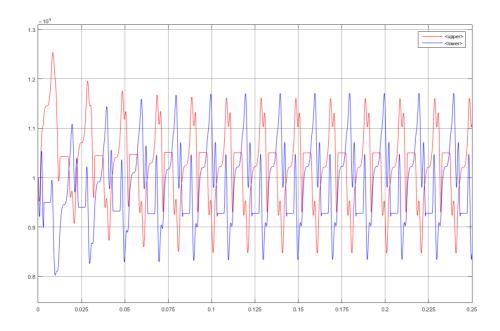

|      | Arm voltages in T1 and T2                                                 | 72 |

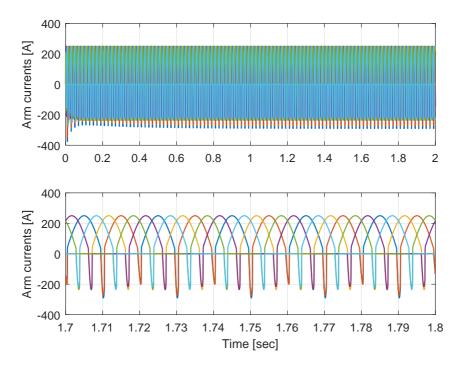

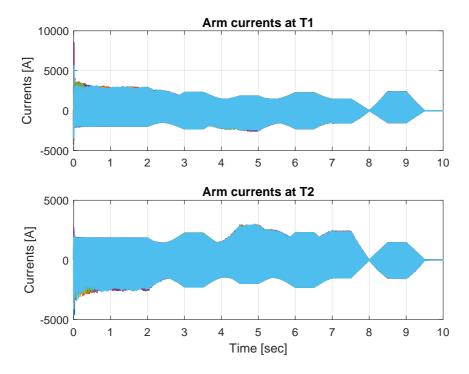

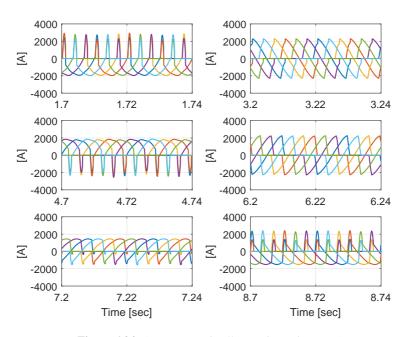

|      | Arm currents in T1 and T2                                                 | 73 |

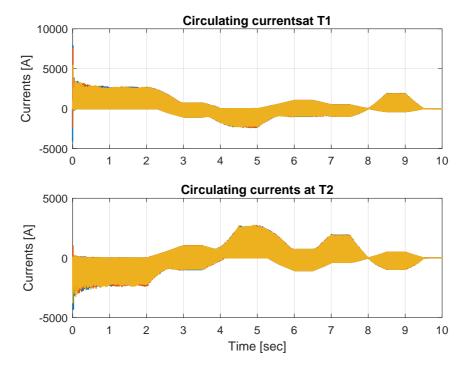

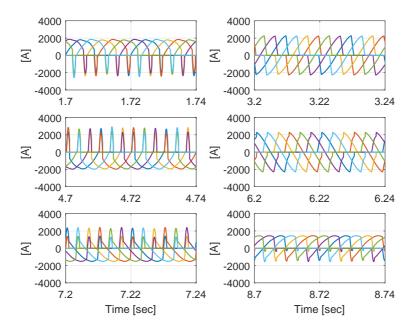

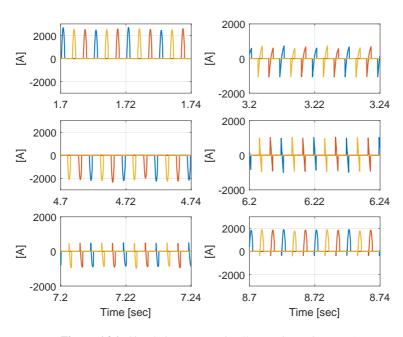

|      | Circulating currents in T1 and T2                                         | 74 |

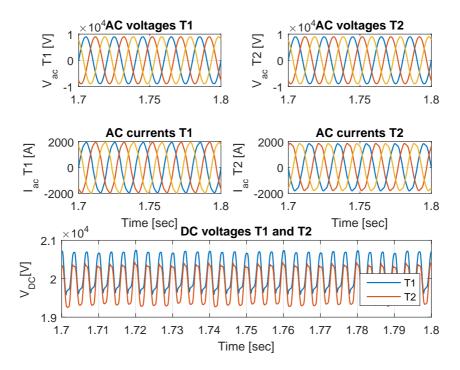

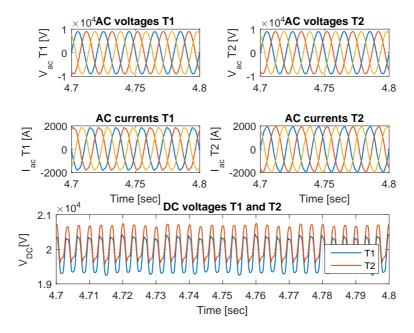

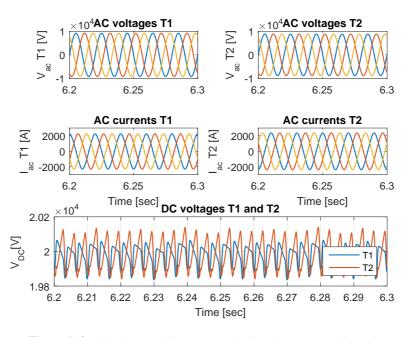

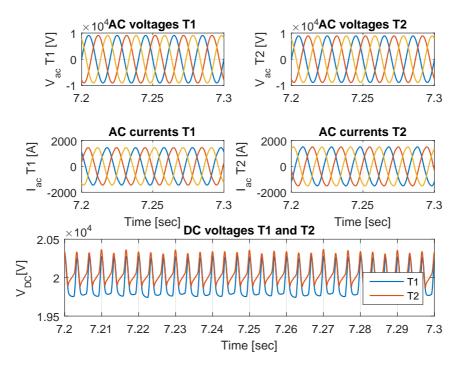

|      | AC voltages, AC currents and DC voltages at operating point A             | 75 |

|      |                                                                           |    |

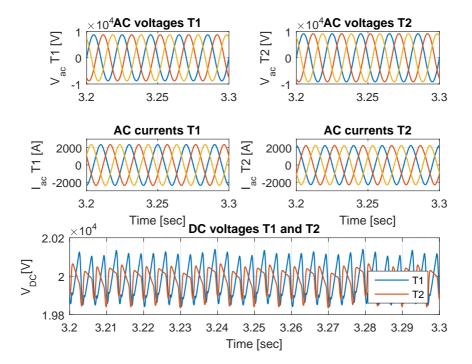

|      | AC voltages, AC currents and DC voltages at operating point B             | 76 |

|      | AC voltages, AC currents and DC voltages at operating point C             | 77 |

|      | AC voltages, AC currents and DC voltages at operating point D             | 77 |

|      | AC voltages, AC currents and DC voltages at operating point E             | 78 |

|      | AC voltages, AC currents and DC voltages at operating point F             | 79 |

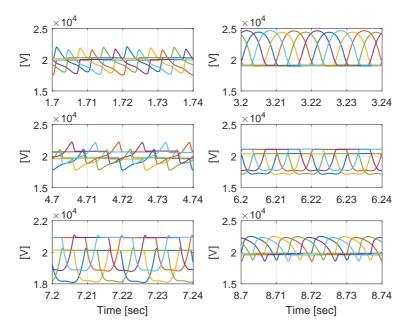

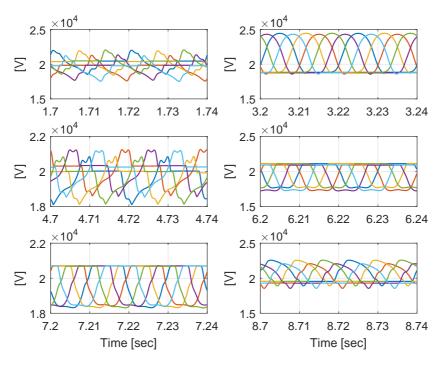

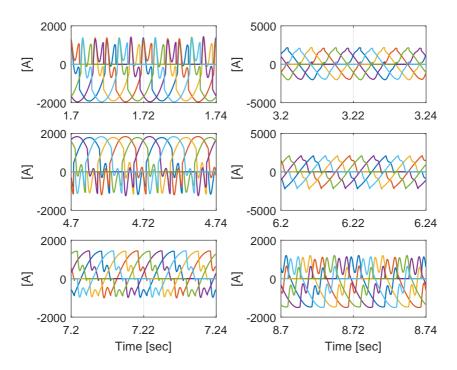

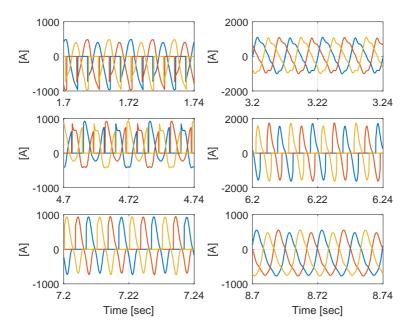

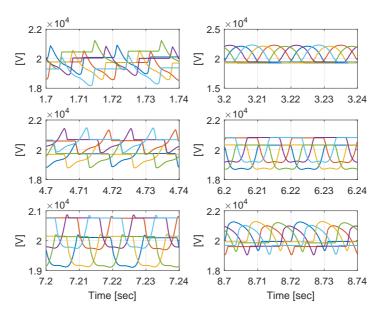

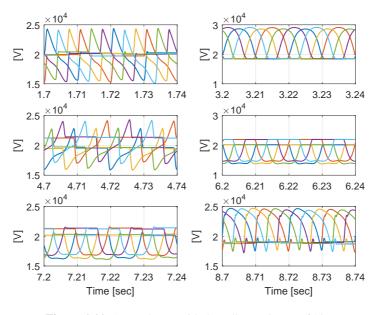

|      | Arm voltages in all operation points at T1                                | 80 |

|      | Arm voltages in all operation points at T2                                | 80 |

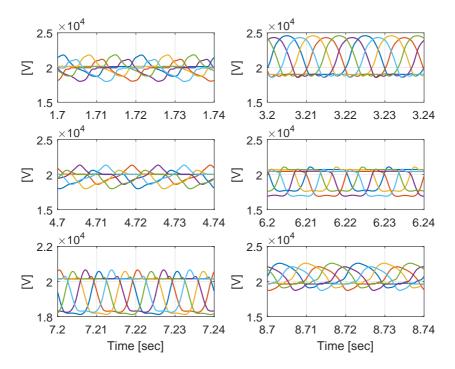

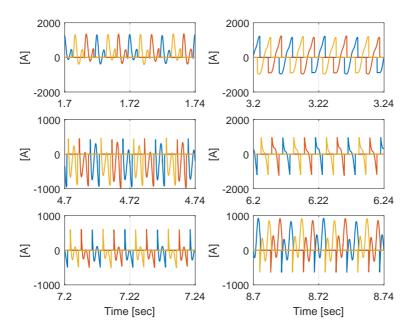

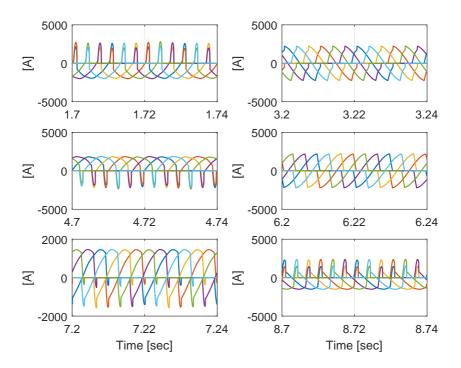

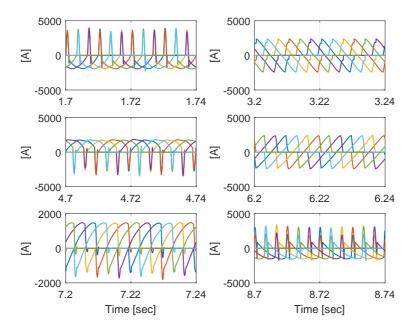

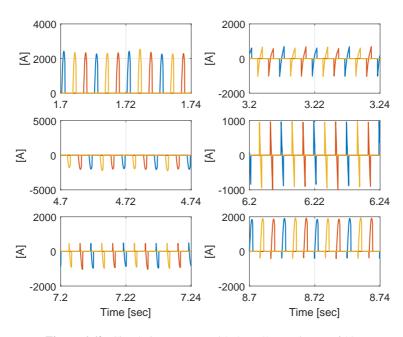

|      | Arm currents in all operation points at T1                                | 82 |

| 6.25 | Arm currents in all operation points at T2                                | 83 |

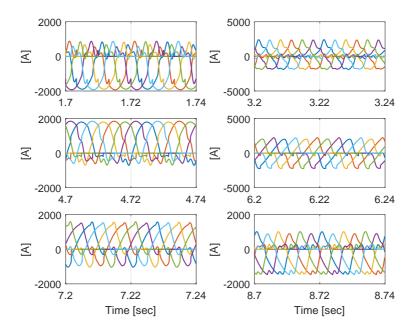

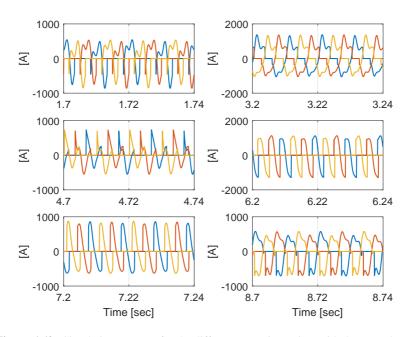

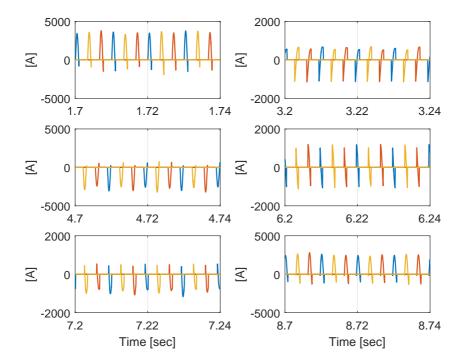

| 6.26 | Circulating currents in all operation points at T1                                                 |

|------|----------------------------------------------------------------------------------------------------|

| 6.27 | Circulating currents in all operation points at T2                                                 |

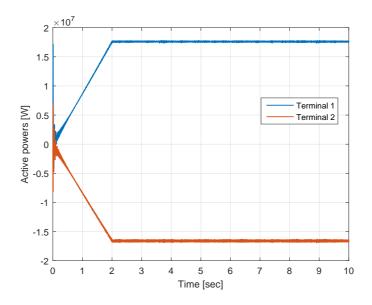

| 6.28 | T1 and T2 active powers                                                                            |

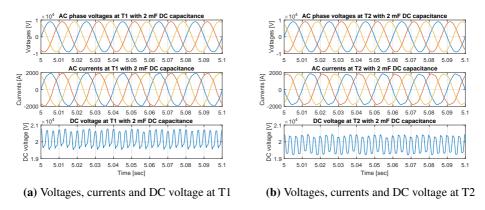

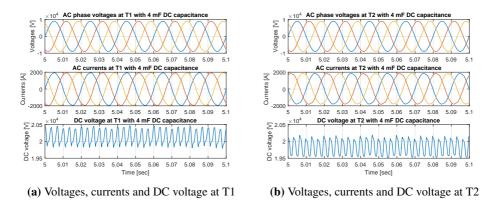

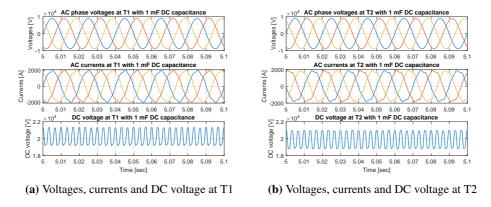

| 6.29 | AC phase voltages, ac currents and DC voltage at T1 and T2 85                                      |

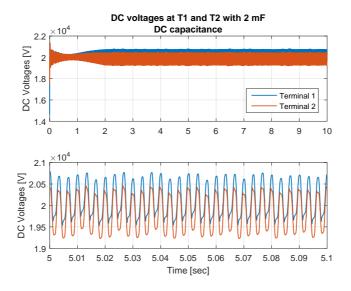

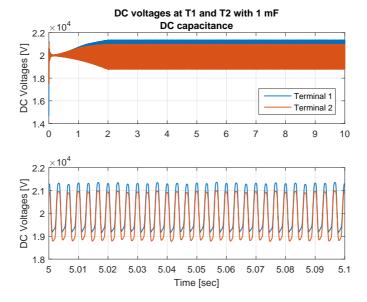

| 6.30 | DC voltages at T1 and T2 with $2mF$ capacitance value 86                                           |

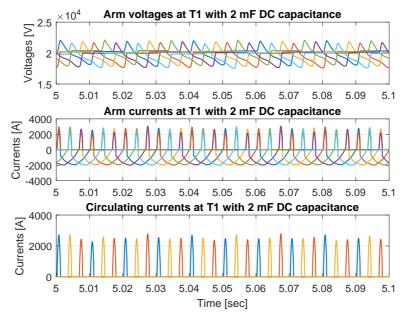

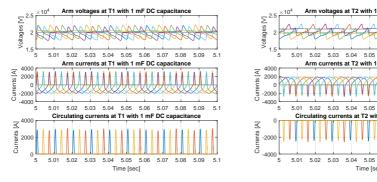

| 6.31 | Arm voltages, currents and circulating currents at T1 and T2 87                                    |

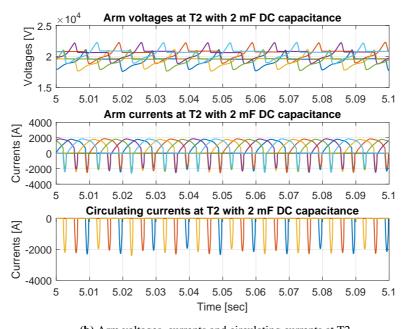

| 6.32 | T1 and T2 active powers                                                                            |

| 6.33 | AC phase voltages, ac currents and DC voltage at T1 and T2 88                                      |

| 6.34 | DC voltages at T1 and T2 with $4mF$ capacitance value 89                                           |

|      | Arm voltages, currents and circulating currents at T1 and T2 90                                    |

|      | T1 and T2 active powers                                                                            |

|      | AC phase voltages, ac currents and DC voltage at T1 and T2 91                                      |

|      | DC voltages at T1 and T2 with $1mF$ capacitance value 92                                           |

|      | Arm voltages, currents and circulating currents at T1 and T2 92                                    |

| 6.40 | Circulating currents at T1 and T2 with different DC side capacitance values 93                     |

| 6.41 | DC voltages at T1 and T2 with different DC side capacitance values 94                              |

| 6.42 | AC currents at T1 and T2 with different DC side capacitance values 94                              |

|      | THD of the phase A AC current at T1 with overall capacitance value of 4 ms 95                      |

|      | THD of the phase A AC current at T2 with overall capacitance value of 4 ms 96                      |

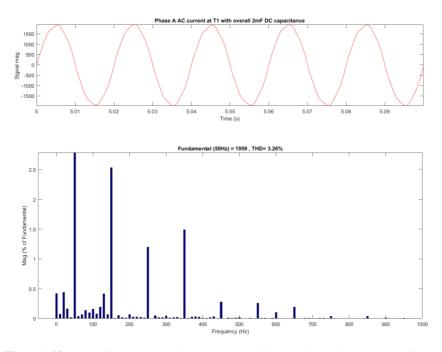

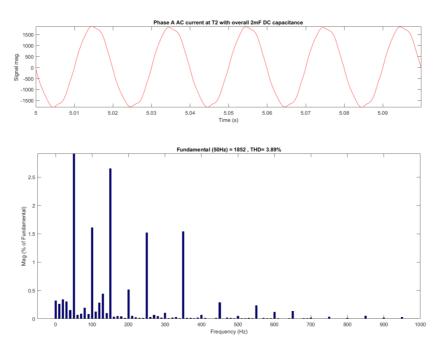

|      | THD of the phase A AC current at T1 with overall capacitance value of 2 ms 96                      |

|      | THD of the phase A AC current at T2 with overall capacitance value of 2 ms 97                      |

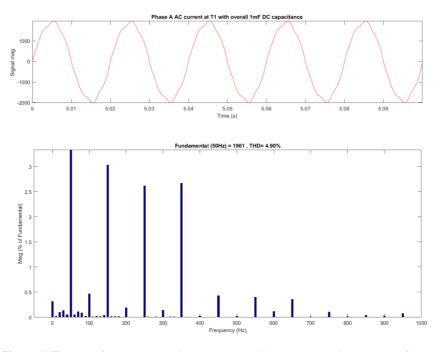

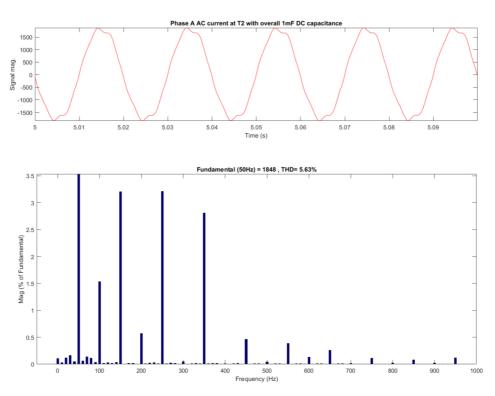

|      | THD of the phase A AC current at T1 with overall capacitance value of 1 ms 97                      |

|      | THD of the phase A AC current at T2 with overall capacitance value of 1 ms 98                      |

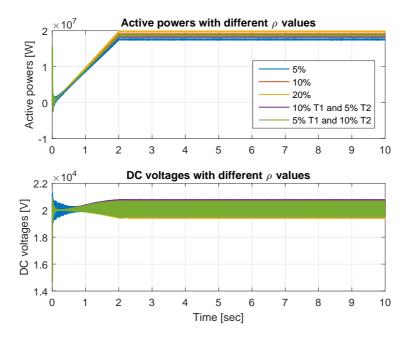

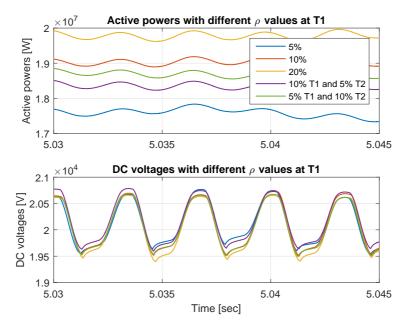

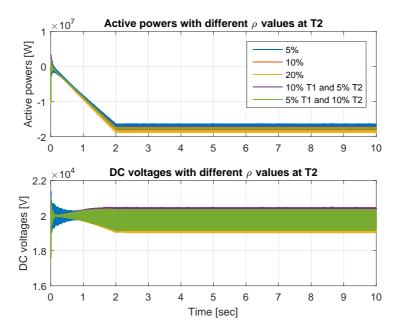

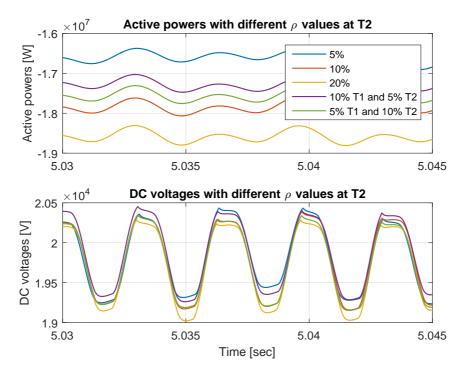

|      | Active powers and DC voltages with different $\rho$ values measured at T1 99                       |

| 6.50 | Closer look of the active powers and DC voltages with different $\rho$ values                      |

|      | measured in T1                                                                                     |

|      | Active powers and DC voltages with different $\rho$ values measured at T2 100                      |

| 6.52 | Closer look of the active powers and DC voltages with different $\rho$ values                      |

|      | measured in T2                                                                                     |

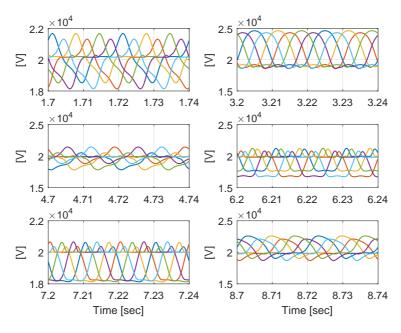

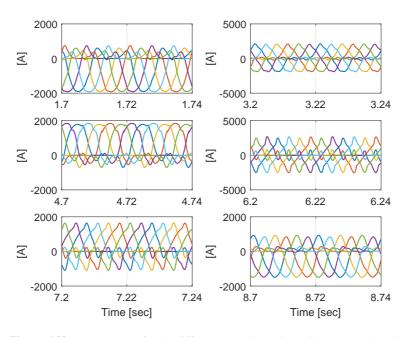

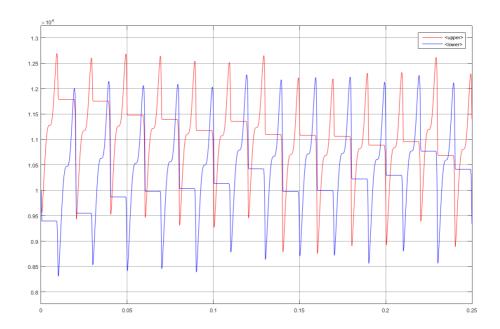

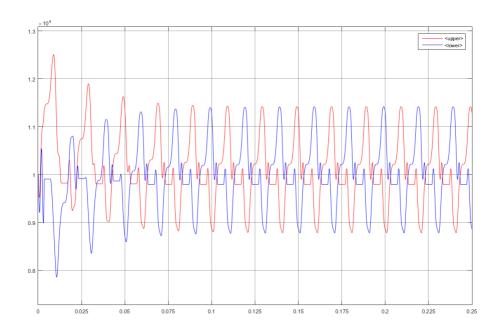

|      | Arm voltages for the different operation points with 3 ms overlap time 102                         |

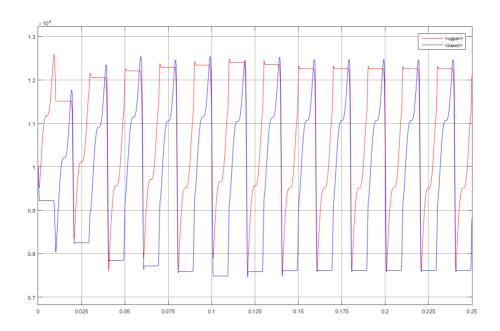

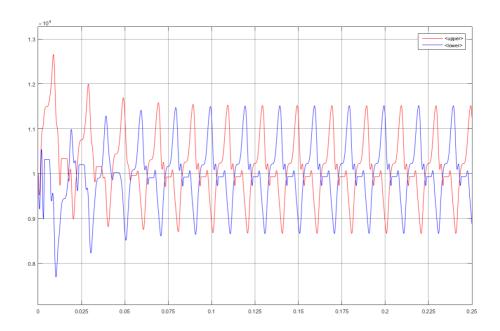

|      | Arm voltages for the different operation points with 5 ms overlap time 103                         |

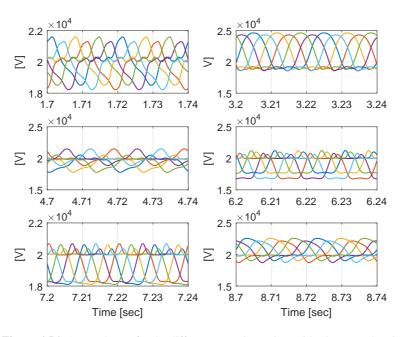

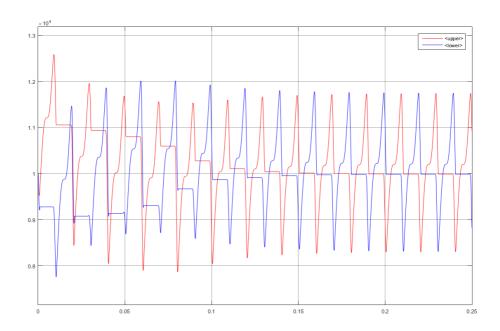

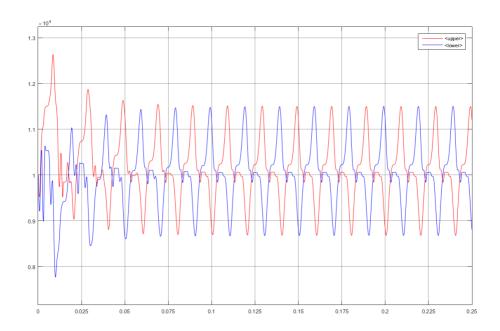

|      | Arm voltages for the different operation points with 7 ms overlap time 104                         |

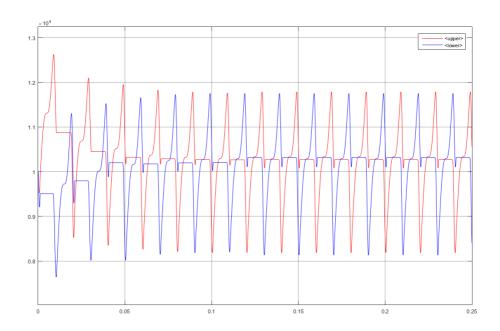

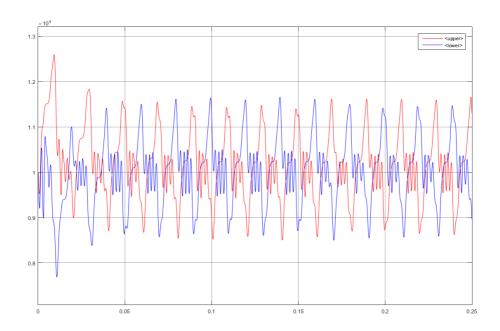

|      | Arm voltages for the different operation points with $10 \text{ ms}$ overlap time $104 \text{ ms}$ |

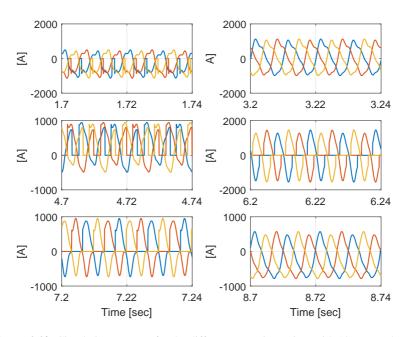

|      | Arm currents for the different operation points with 3 ms overlap time 105                         |

|      | Arm currents for the different operation points with 5 ms overlap time 106                         |

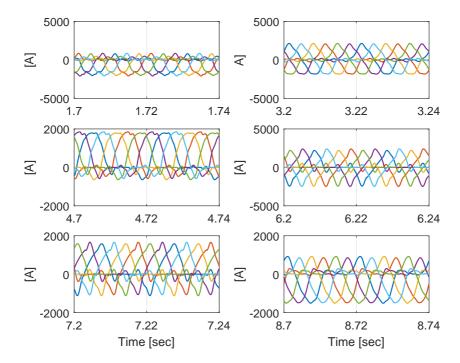

|      | Arm currents for the different operation points with 7 ms overlap time 106                         |

|      | Arm currents for the different operation points with 10 ms overlap time . 107                      |

|      | Circulating currents for the different operation points with 3 ms overlap time 108                 |

|      | Circulating currents for the different operation points with 5 ms overlap time 108                 |

|      | Circulating currents for the different operation points with 7 ms overlap time 109                 |

| 6.64 | Circulating currents for the different operation points with 10 ms overlap                         |

|      | time                                                                                               |

|      | Arm voltages with the cell capacitance of 80 ms                                                    |

|      | Arm voltages with the cell capacitance of 20 ms                                                    |

| 6.67 | Arm currents with the cell capacitance of 80 ms                                                    |

| 6.68 | Arm currents with the cell capacitance of 20 ms                                    | 113 |  |  |  |

|------|------------------------------------------------------------------------------------|-----|--|--|--|

| 6.69 | Circulating currents with the cell capacitance of 80 ms                            |     |  |  |  |

| 6.70 | Circulating currents with the cell capacitance of 20 ms                            | 114 |  |  |  |

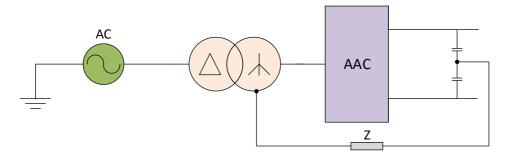

| 6.71 | Path created by the third harmonic                                                 |     |  |  |  |

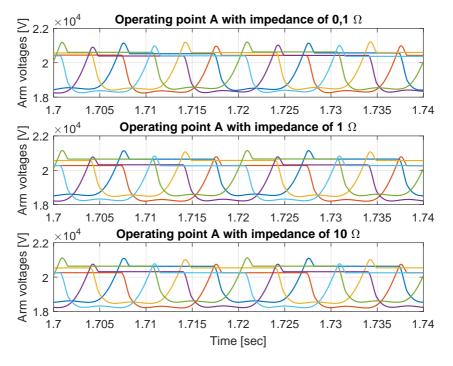

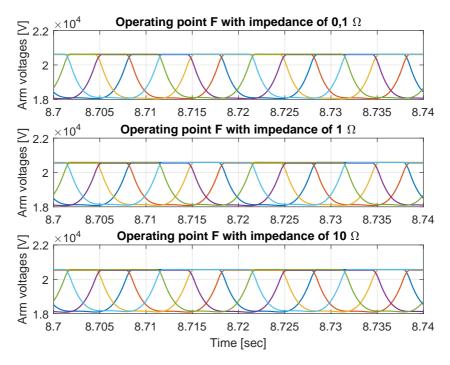

| 6.72 | Arm voltages with varied value of the impedance for 3rd harmonic of                |     |  |  |  |

|      | $0.1\Omega$ , $1\Omega$ and $10\Omega$ during operating point A                    |     |  |  |  |

| 6.73 | Arm voltages with varied value of the impedance for 3rd harmonic of                |     |  |  |  |

|      | $0.1\Omega$ , $1\Omega$ and $10\Omega$ during operating point F                    |     |  |  |  |

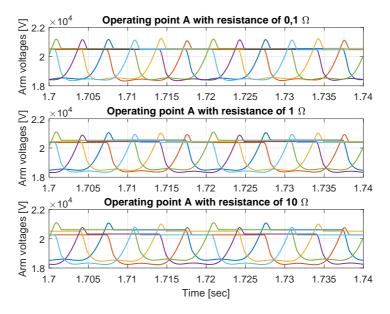

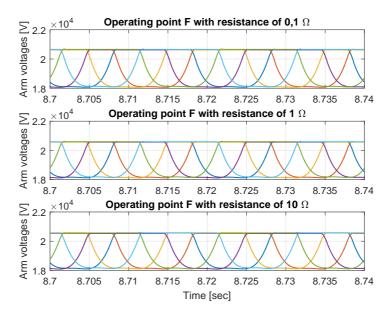

| 6.74 | Arm voltages with varied value of the resistance for 3rd harmonic of $0.1\Omega$ , |     |  |  |  |

|      | $1\Omega$ and $10\Omega$ during operating point A                                  | 118 |  |  |  |

| 6.75 | Arm voltages with varied value of the resistance for 3rd harmonic of $0.1\Omega$ , |     |  |  |  |

|      | $1\Omega$ and $10\Omega$ during operating point F                                  | 118 |  |  |  |

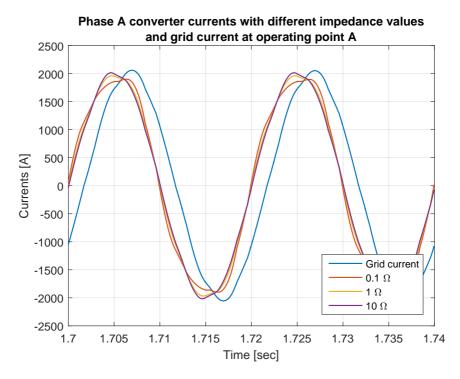

| 6.76 | Comparison of the grid current and 3 different converter currents due to           |     |  |  |  |

|      | the different impedance values in the path created for the third harmonic .        | 119 |  |  |  |

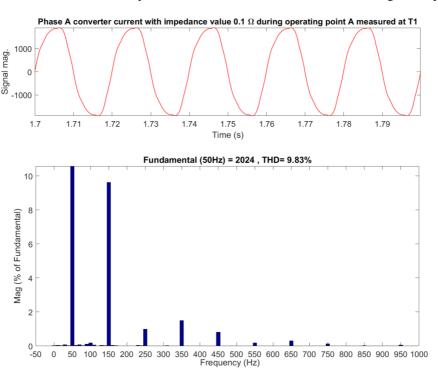

| 6.77 | Phase A converter current with impedance value $0.1\Omega$ during operating        |     |  |  |  |

|      | point A measured at T1 and it THD analysis with frequency magnitude in             |     |  |  |  |

|      | percentage of the fundamental                                                      | 120 |  |  |  |

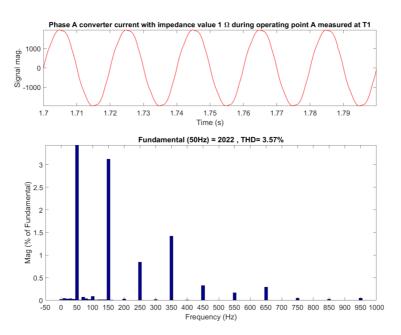

| 6.78 | Phase A converter current with impedance value $1\Omega$ during operating point    |     |  |  |  |

|      | A measured at T1 and it THD analysis with frequency magnitude in per-              |     |  |  |  |

|      | centage of the fundamental                                                         | 121 |  |  |  |

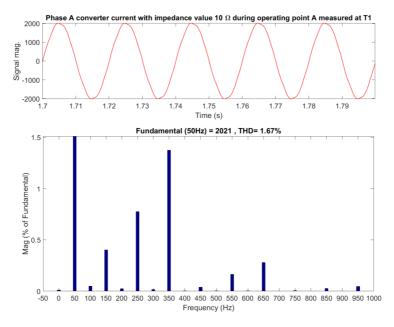

| 6.79 | Phase A converter current with impedance value $10\Omega$ during operating         |     |  |  |  |

|      | point A measured at T1 and it THD analysis with frequency magnitude in             |     |  |  |  |

|      | percentage of the fundamental                                                      | 121 |  |  |  |

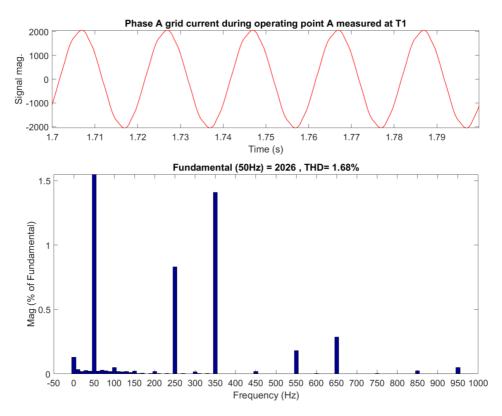

| 6.80 | Phase A grid current during operating point A measured at T1 and it THD            |     |  |  |  |

|      | analysis with frequency magnitude in percentage of the fundamental $\ . \ .$       | 122 |  |  |  |

| 1    |                                                                                    | 122 |  |  |  |

| 1    | Voltage dynamics in the arm stacks case1                                           | 132 |  |  |  |

| 2    | Voltage dynamics in the arm stacks case2                                           | 133 |  |  |  |

| 3    | Voltage dynamics in the arm stacks case3                                           | 134 |  |  |  |

| 4    | Voltage dynamics in the arm stacks case4                                           | 135 |  |  |  |

| 5    | Voltage dynamics in the arm stacks case5                                           | 136 |  |  |  |

| 6    | Voltage dynamics in the arm stacks case6                                           | 137 |  |  |  |

| 7    | Voltage dynamics in the arm stacks case?                                           | 138 |  |  |  |

| 8    | Voltage dynamics in the arm stacks case8                                           | 139 |  |  |  |

| 9    | Voltage dynamics in the arm stacks case9                                           | 140 |  |  |  |

| 10   | Voltage dynamics in the arm stacks case 10                                         | 141 |  |  |  |

| 11   | Voltage dynamics in the arm stacks case11                                          | 142 |  |  |  |

| 12   | Voltage dynamics in the arm stacks case 12                                         | 143 |  |  |  |

| 13   | Voltage dynamics in the arm stacks case 13                                         | 144 |  |  |  |

| 14   | Voltage dynamics in the arm stacks case 14                                         | 145 |  |  |  |

| 15   | Voltage dynamics in the arm stacks case 15                                         | 146 |  |  |  |

| 16   | Voltage dynamics in the arm stacks case16                                          | 147 |  |  |  |

| 17   | Voltage dynamics in the arm stacks case 17                                         | 148 |  |  |  |

| 18   | Voltage dynamics in the arm stacks case 18                                         | 149 |  |  |  |

| 19   | All data                                                                           | 149 |  |  |  |

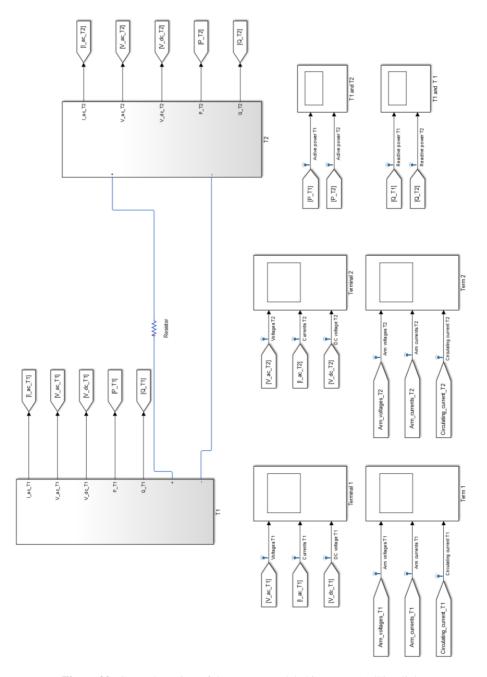

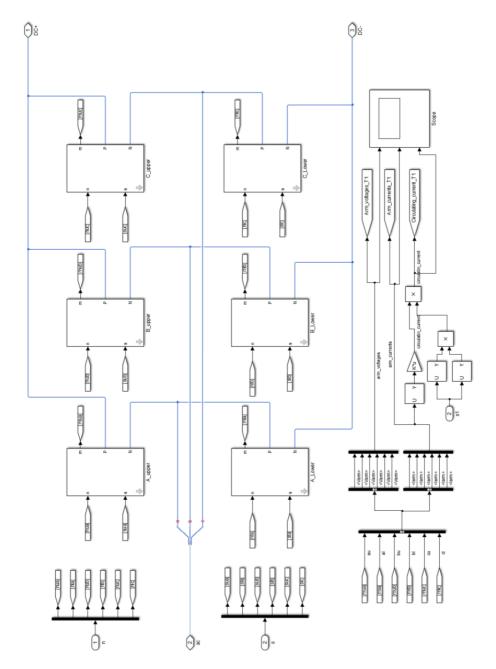

| 20   | General preview of the system modeled in MATLAB/Simulink                           | 160 |  |  |  |

| 21 | Terminal 1 system modeled in MATLAB/Simulink                            | 161 |

|----|-------------------------------------------------------------------------|-----|

| 22 | Terminal 2 system modeled in MATLAB/Simulink                            | 162 |

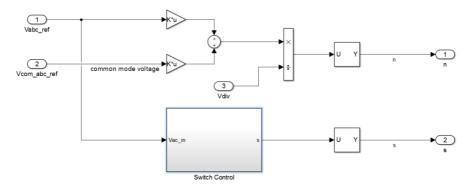

| 23 | Modulator modeled in MATLAB/Simulink                                    | 163 |

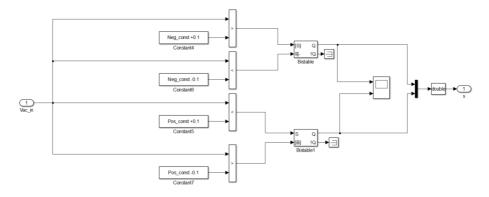

| 24 | Overlap control for the switches modeled in MATLAB/Simulink             | 163 |

| 25 | Alternate arm converter representation modeled in MATLAB/Simulink       | 164 |

| 26 | Upper arm of the AAC modeled in MATLAB/Simulink                         | 165 |

| 27 | Lower arm of the AAC modeled in MATLAB/Simulink                         | 165 |

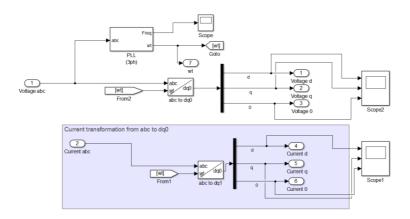

| 28 | Transformation from abc reference frame to the dq0 reference frame mod- |     |

|    | eled in MATLAB/Simulink                                                 | 165 |

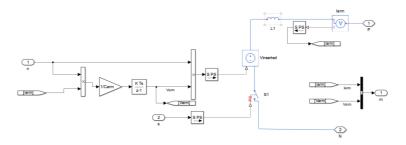

| 29 | Control in T1 of the point to point connected system modeled in MAT-    |     |

|    | LAB/Simulink                                                            | 166 |

xv

### **Abbreviations**

COP Conference of the Parties, RES Renewable energy source, HVDC high voltage direct current, DER distributed energy resources, **HVAC** high voltage alternating current, LCC line commutated converter, **VSC** voltage source converter, MMC modular multilevel converter, AAC alternate arm converter.

DC = direct current, AC = alternating current,

FACTS = flexible alternating current transmission system,

GTO = gate turn off,

IGCT = integrated gate commutated thyristors,IGBT = insulated gate bipolar transistor,

SVC = static var compensation,

STATCOM = static synchronous compensator, TCSC = thyristor controlled series capacitor,

PAR = phase angle regulators, AVM = average value model, ICC = inner current controller, OVC = outer voltage controller, PLL = phase locked loop,

TSO = transmission system operator,

|         | <u> </u> |  |  |

|---------|----------|--|--|

|         | 1        |  |  |

|         |          |  |  |

|         |          |  |  |

| 1       |          |  |  |

| Chapter |          |  |  |

| Chapton |          |  |  |

### INTRODUCTION

#### 1.1 Background

Nowadays the rapidly changing world and the booming population will require more and more energy generation. Old thermal and nuclear plants are not capable to provide that huge amount of energy, furthermore the carbon footprint left by generating energy from these power plants will increase with the increasing number of the new power plants. The nuclear plants are debatable to be safe anymore after couple of the incidents and the nuclear waste storage are unsolved issue [9][10]. The non-renewable energy sources are limited and increasing population will increase usage of them, therefore the new solutions should be planed, otherwise in the nearly future it will be a lack of the fossil fuel [11].

Another huge risk is a global warming. The situation is getting worse and worse each year, that is why a such events as United Nations climate change conferences are organized. Conference COP 21 was held in 2015. In this conference 195 countries were participating and by now 154 [20-05-2017] countries signed an agreement to reduce green house gasses and keep the global warming temperature well bellow than 2°C [12]. This conference directed a new point of view in the energy production, transformation, transmission and even usage. The production will be achieved by using renewable energy sources ( RES) as wind parks, solar systems, hydro plants, biomass, geothermal energy and so on. Transformation efficiency and the reliability will be increased. The bulky power transmission systems to become more efficient are requiring less energy losses, therefore the high voltage direct current ( HVDC) transmission systems are taking over. Nowadays smarter ways how to save energy get more trend. The word "smart" gets a new meaning, where saving of the energy are highlighted in the every step and people are encourage to save energy even in the smallest amounts. People are taught how to use the produced energy widely. A simple example even of the smallest thing like "turnoff" of the TV standby mode, can make huge impact, when it will be used widely. Increasing energy production can not stand alone, it should be supported by the usage of it in the most efficient way. The production of the energy should be harmless to the environment, therefore the world driven of the green energy getting more fashion than before.

The situation requires to coupe people from the different places. Most of them to produce energy are implementing solar systems, which are the best solution for the households. The energy production for the communities, villages or even towns are wind energy, biomass or hydro plants. These different access points are called distributed energy resources (DER), where the access are distributed to the energy in the area and are not centralized to one energy production resource. Distributed energy resources at some point have to be coupled with the grid access point. The connection should satisfy certain limits as voltage, current or frequency levels and during the connection should not disturb the grid. Today most of the DER are connected with a grid using an alternating current (AC), but it is not a solution in the future, due to the difficulties of synchronization, satisfaction of the grid constraints and increasing requirement of the efficiency in the transmission systems. While the relatively small DER can still be coupled easier with the strong grid by using AC. The high voltage direct current transmissions or links are better solution to couple large DER to the grid. Huge converter stations are used to collect and covert from AC to DC all the DER. The offshore wind energy parks are the good example of the converter station terminals in the sea, since most of the time they are connected through the cables, which generates more reactive power, than the lines.

#### 1.2 Objective of the work and motivation

The substation converter can connect and convert high voltage alternating current (HVAC) and HVDC links and vise versa. Two types of the converter topology are used nowadays. Line commutated converters (LCC) and voltage source converters (VSC) [4]. Nowadays VSC can be divided into proven two types of the converters: two level converters and modular multilevel converters (MMC).

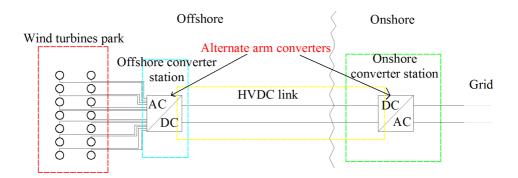

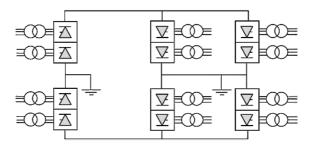

The new topology of VSC arises, which is a hybrid of merged two of mentioned VSC types. It is known as alternate arm converter (AAC) and was firstly introduced in [13]. The converter type is under investigation nowadays and not yet proven technology to be used commercially. The study aims to create a MATLAB/Simulink model to test the behaviour of the converter. First the model of AAC will be created in Simulink, together with a simple control schemes. Then it will be tested in the island mode, by observing its operation and understanding its working principle. After that the connection to the grid and implementation of the improved control will be observed. Finally the simulation of the converter will be used in the point to point connection. The connection scheme are illustrated in Figure 1.1. As it can be seen in this case the wind turbine park is considered operating in offshore. The wind turbines are connected to the substation, which is placed in offshore. The connections of the wind turbines to the substation are through AC submarine cables. The distance between the wind park and the offshore substation is feasible to still use AC voltage. Offshore and onshore converter stations converts AC to DC and DC to AC, respectively. LCC and VSC topology can be used in these converter stations. The converters are connected through the HVDC link. The HVDC link consist of the HVDC submarine cables and transfers power to the onshore substation.

Figure 1.1: Example of the possible realization of the AAC.

Considering all of the above mentioned steps and remarks Master thesis project motivates to inspect the new topology of the converter - AAC and its behaviour in the point to point connection, which can be usefull in the future renewable energy sources, especially wind energy.

#### 1.3 Outline of the thesis

#### **Chapter 1 [Introduction]**

This chapter firstly represents briefly the movement towards and need of renewable energy sources. The rise of the distributed energy resources and couple of them in the network. The next subsection represents objective of the work and motivation.

#### Chapter 2 [High voltage transmission technologies]

This chapter introduces two types of the high voltage transmission technologies and comparison between them. The introductory part of the high voltage alternating current technology is presented in the first section. The second section presents high voltage direct current technology and future aspects of the network connection. The connection types of high voltage direct current are also explained in this section. The third section is comparison between high voltage alternating current and high voltage direct current. The comparison of the power amount transferred in both of the transmission systems are presented. The amount of the losses occurring during power transfer and the costs of the each transmission system, break-even distance.

#### Chapter 3 [Topology of the converters]

The topology of two commonly used converters are introduced in this section. Line current commutated converters are briefly represented in the first section and voltage source converters are represented in the second section, with 2 subsections of the already used in the commercial projects voltage source converters. The one is called 2-level converter and other modular multilevel converter. The brief topology is explained of these two voltage source converter types.

#### Chapter 4 [Modeling an alternate arm converter]

The new hybrid topology of the voltage source converter is introduced in the first section of this chapter. The type of the voltage source converter high voltage direct current

is introduced in the second section. Chosen average value model type is discussed. The third sections talks about the mathematical representation of the alternate arm converter. The simple mathematical model is derived. The forth section shows one-phase simple average model simulated in the Simulink by using mathematical model representation of the previous section. The simple controls of the arm voltage balancing are implemented in the following sections. The fifth sections shows the derivation of the "sweet spot" voltage and its implementation in the one phase simulation model. The sixth section provides information about overlap balancing technique and implementation in the one-phase Simulink model. The different constant values of the overlap control are investigated and represented in the Appendix A.

#### Chapter 5 [Control strategy of the alternate arm converter]

In this chapter controls are adapted for the 3-phase island mode simulation model. In the first section the Park-Clarke transformations are represented in order to simplify further control schemes. The second section shows steps of the control strategy used in the 3-phase island mode simulation model and the current control as inner loop. The third section represents outer loop control, which for this simulation model is voltage control.

#### Chapter 6 [Alternate arm converter in the point to point connection]

This chapter represents the alternate arm converters connected in the point to point connection, its behaviour, simulation results and problems arise during the connection. The first sections introduces system components and evaluation and why they are needed. The control required for the converters in this type of the connection is briefly introduced. The second section introduces six study cases in the point to point connection. The study cases are splat up in the six subsections. The first subsection introduces the study case for the different operating points of the point to point connected alternate arm converters. The second subsections shows the DC side capacitance effect for the DC voltage. The third subsection introduces effect of the different droop control drop values for the active power and DC voltage. The forth subsection shows arm voltage balance problem and its solution by varying overlap time, which is confronted in some operating points during the first subsection. The fifth subsection continues solve the arm voltage balance problem with the different approach, by changing cell capacitance value. The results and observations are represented in this subsection. The sixth subsection introduces a new arm voltage balancing technique with circulating third harmonic current. This technique is used together with overlap control. This merged technique solves the issue confronted in the forth subsection, when the AAC typology is forced to change a topology to the MMC, in order for the better balance between the arm voltages. This balancing way required a small system changes in order to implement it.

#### **Chapter 7 [Conclusion]**

The final conclusion and discussion will be represented in this chapter.

#### Chapter 8 [Future work]

The possible future work will be stated in this chapter.

# HIGH VOLTAGE TRANSMISSION TECHNOLOGIES

The first thing about high voltage comes in mind that it is harmful for the livings. The definition of the high voltage exists, due to the classification of the voltage levels. The classification can be made differently in each country, but mainly the high voltage term is considered to be when the voltage level can cause the spark in the air. Therefore the term high voltage means that the level is above the threshold limits. The high voltage can be used everywhere starting from the power transmission, medical equipment like X-RAY, laboratory equipment like arcing demonstration or at home like TV. In this chapter HVAC, HVDC and comparison between them will be discussed.

### 2.1 High voltage alternating current technology

At the very beginning electric power transmission system was created to be direct current. By operating direct current (DC) transmission system increase or decrease voltage level at that moment was not that easy, because the different type of loads required the different levels of the voltage and these issues required different generators and circuits. The certain events like evolution of the induction motors and the development of the transformers, allowed easily to transmit power and distribute it in the required voltage levels. Therefore the alternating current transmission system spread all over the world.

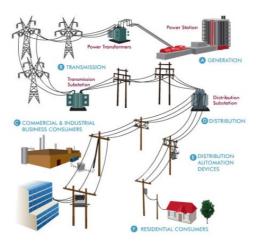

The first high voltage (at that time) commercial alternating current (AC) transmission system was build in 1891. The transmission line was 15kV and 175km long, it connected Lauffen and the Frankfurt [14]. The electrical power system consist of the generation, transmission and distribution parts. The vertical power transmission system is represented in Figure 2.1. Mainly the power of the electrical power system are produced by the AC generators, after that the AC voltage level is increased by transformers in order to reduce

conduction losses, due to the fact that voltage have opposite proportionality of current. Mostly long and bulky transmission systems are operating in high voltage level by transmitting power along overhead lines or cables to the following substation. At the receiving substation the transformer lowers the voltage level to the feasible for the distribution. The distribution system depends on the type of the customers, they require different voltage levels, therefore the distribution substations can contain several transformers.

**Figure 2.1:** AC transmission diagram [1]

The transmitted power is defined by the equation 2.1, where P is an active power flow,  $V_s$  is sending end voltage,  $V_r$  is receiving end voltage,  $X_s$  is line impedance and  $\delta_{sr}$  is voltage-phase angle at the sending end with respect to the receiving end. As it can be seen from the equation 2.1 the limiting factor of the power transmission is line impedance  $X_s$ . Therefore the lower is line impedance the higher active power flow can be achieved. The power consumption grows and forces to search for a new ways of the power transmission. One of the ways is to create a parallel line for the power flow in the vertical power transmission. The issue comes when the power flow is shared and one of the line caries higher amount of power than other, therefore the control should be obtained for the equal power flow. In the meshed systems this issue creates even more complications, since reliability should be maintained. The solutions can be high voltage direct current usage, which is represented in section 2.2, or flexible alternating current transmission systems (FACTS).

$$P = \frac{V_s V_r}{X_S} \sin \delta_{sr} \tag{2.1}$$

In order to reduce the line impedance or have a ability to control line impedance FACTS are used in the HVAC transmission systems. It was developed in 1980s at EPRI in USA [15]. The power flow is regulated and control with the power electronic devices in the high voltage alternating current transmission systems. Implementation of the FACTS allow to reduce investment costs of operation and transmission, increase reliability and security of the system, transfer higher power through the system and control dynamic re-

active power with fast acting power electronic devices. Power flow capability can be only limited by the thermal limits.

Depending on the power electronic devices, which are used for the FACTS, they can be divided. Thyristor based: gate turn off (GTO) and integrated gate commutated thyristors (IGCT), which are switched at the low frequency. Insulated gate bipolar transistor (IGBT) based, which are switched at the high frequency. FACTS not only allows to control line impedance, but also voltage and delta angle between buses. The voltage can be controlled by the shunt compensation FACTS like static var compensation (SVC), STATCOM. Line impedance control can be achieved by using series compensation schemes as thyristor controlled series capacitor (TCSC). For the controlling angle delta, the phase angle regulators (PAR) are used [15].

### 2.2 High voltage direct current technology

The first commercial high voltage direct current (HVDC) transmission link was between the Gotland island and the Swedish mainland. The link was launched in 1954 with the rated voltage value of 100 kV. Since then the HVDC evolved and populated dramatically over the world [16].

High voltage direct current has very attractive characteristics for the certain applications. Mostly HVDC are used for the high power transmissions over the long distance. In addition the advantage is asynchronous connections between the networks, where the two power systems are not synchronized with each other. Mostly HVDC technology are used, when the two networks should be connected through the submarine cables. The technology is advantageous, because of the no reactive power are transmitted in the HVDC. With the increasing amount of the renewable energy resources in the power system like offshore wind energy farms more often direct current technology is used for the bulky power transmission. Research and usage of the power electronics increase HVDC technology spread worldwide even more. With the newest power electronics converters come better reliability, voltage stabilization and the lower price, which still are the huge drawback for the HVDC network for the short time period, because the initial investments into the power electronics converter stations are higher than for the HVAC. During the long term period the costs become smaller comparing with the HVAC.

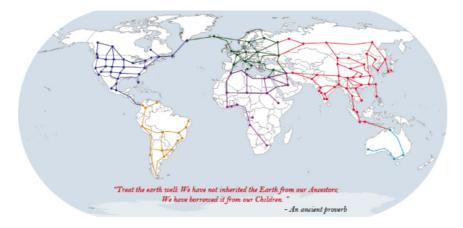

The projects and the capacity of the HVDC networks are increasing worldwide. Figure 2.2 illustrates one of the possibilities to connect whole world in HVDC transmission system. Every year capacity of the HVDC transmission systems are expanding. This phenomena allows to escalate another, but not new concept presented in 1889 by Thomas Alva Edison. At that time due to complexity and absence of the power electronics the distributed energy resources (DER) concept was hard to maintain and the distribution of the generation required huge investments. Therefore the concept of the DER at that time was faded away. Nowadays, where the power electronics are ruling every our step, the concept of DER is likely possible, so the concept gain new breath. Figure 2.3 provides an example of DER. As it can be seen the power flow is no more unidirectional by implementing DC in the grid the bidirectional power flow is easy to achieve. Bidirectional power flow allows higher usage and flexibility of the renewable energy resources. For example the solar systems on the house rooftops are capable to generate electricity and accumulate in the

energy storage places during the day, while in the evening the energy can be consumed by same household. Similar situation can be implemented for the wind turbine parks, when the wind is blowing generated energy can be stored at the storage units, when the wind stops the energy are consumed from storage places. Since more and more equipment in our houses are using power electronics, it will be easier if the grid will be DC. The initiative concept of the DC grid are also represented among researchers [17], but long distance bulky power transmission are more important case.

Figure 2.2: Future aspect of the possible HVDC network connection [2]

**Figure 2.3:** Network example of the distributed energy resources connection [3]

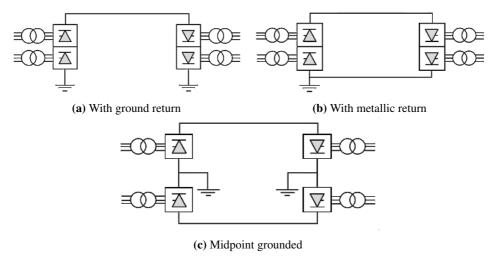

Long distance HVDC transmission has variety of configurations. The configuration depends on the systems design. Factors such as power transfer capability, voltage level or cable technology are taken into account, when the configuration is determined. The main configurations are monopolar, bipolar, back to back and multiterminal.

Three types of the monopolar configurations are illustrated in Figures 2.4a 2.4b and

2.4c. The figure 2.4a represents the cheapest and the most used type of the HVDC configuration for the offshore transmission. The idea behind this is to use the ground as the return conductor. It can be achieved since the sea or ocean water is salted. This solution is the cheapest, because it is not required the return conductor, it uses only ground electrodes. The main drawbacks are limited power transfer and the cause of the metallic objects corrosion. The monopolar configuration with ground return can not work if the return ground path is very resistive. The monopolar configuration with the metallic ground return is illustrated in the Figure 2.4b to overcome these issues. The issue of the corrosion is solved, by implementing metallic neutral or low voltage cable as the return conductor. The return conductor can be grounded, which results in the asymmetrical monopole with metallic return configuration. The advantage of this configuration, DC conductor does not require full insulation, whereas the symmetrical monopole configuration with not grounded return conductor requires full DC conductor insulation [18]. In order to implement the redundancy in the monopolar configuration the midpoint of the ground connection are used. The Figure 2.4c represents the solution, if one of the transmission line fails, other still remains operational.

**Figure 2.4:** Monopolar configurations [4]

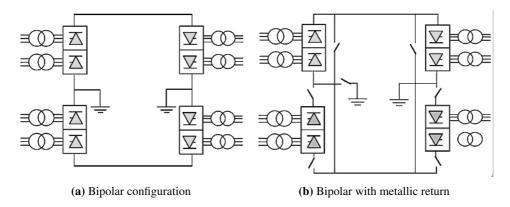

Bipolar configurations are represented in Figures 2.5a and 2.5b. This configuration consist of the two poles, where one is positive and other one is negative. Each pole has their grounded neutral points. For the normal operation the current flows in the loop, therefore there is no current flowing in the ground. This type allows to prevent the corrosion. Furthermore if the fault occurs at one of the poles, the configuration still can operate as the monopolar with the ground return. The Figure 2.5b illustrates the solution in the bipolar configuration during the fault in one of the poles with metallic return. The metallic return used for the ground connection prevents corrosion, when the configuration operates as monopolar [18]. The power transmitted through the bipolar configuration is double, than one transmitted in the monopolar configuration, because the bipolar configuration has 2 poles. The power flow reversal can be controlled by changing polarities of two poles in

the case of line commutated converter. The main drawback is the higher costs, than the monopolar solution.

Figure 2.5: Bipolar configurations [4]

Back to back configuration is illustrated in Figure 2.6. Mainly back to back configuration are used as an interconnection of the asynchronous AC networks and when the system has two different frequencies, like in Japan. The two converters are placed close to each other, most of the time in the same station due to additional substation costs. The power transfer capability are limited by the connected AC system.

Figure 2.6: Back to back configuration [4]

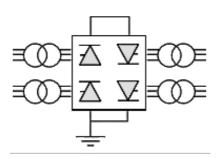

Multiterminal configuration is shown in Figure 2.7. The configuration has three or more converter stations. The idea behind this is to connect multiple generation resources to one terminal. This allows to save cots of the terminals and reduces the conversion loses. The multiterminal configuration is useful for distributed energy resources and for the offshore industry, like wind farms, oil and gas rigs.

Figure 2.7: Multiterminal configuration [4]

# 2.3 Comparison of the HVAC and HVDC in transmission system

Comparison between HVAC and HVDC will be discussed in this section. Two calculations will be held in order to justify advantages of HVDC system in the bulky power transmission.

First of all the active power transfer capability is compared. Assuming AC and DC systems with the same properties and length. Two systems in AC have 6 conductors in total, because each system is three phase so three conductors per system. DC results in 3 systems, due the same amount of the 6 conductors, where direct current needs only 2 conductors per system. The first observation is that the DC capable to transfer higher amount of power, due to higher number of the systems. The comparison per phase voltage between AC and DC can be calculated by the equation 2.2, where  $V_{DC}$  is voltage of the one conductor in DC,  $V_{AC}$  is voltage of the one phase in AC. Then the active power for AC systems assuming current I can be written by equation 2.3. Active power for DC systems with the same current value I and substituted  $V_{DC}$  value from 2.2 equation results in equation 2.4. By equating  $P_{DC}$ , which is active power in DC and  $P_{AC}$ , which is active power in AC results in equation 2.5.

$$V_{DC} = \frac{\sqrt{2}}{\sqrt{3}} V_{AC} \tag{2.2}$$

$$P_{AC} = 2\sqrt{3}U_{AC}I\tag{2.3}$$

$$P_{DC} = 3(2\frac{\sqrt{2}}{\sqrt{3}}U_{AC}I) \tag{2.4}$$

$$P_{DC} = \sqrt{2}P_{AC} \tag{2.5}$$

As it can be seen from equation 2.5 the DC active power is higher than AC active power by  $\sqrt{2}$ . Furthermore DC transmission does not transfer reactive power, there is no dielectric losses, no skin effect losses and no proximity effect, so the active power transmitted in DC is even higher than  $\sqrt{2}$ . The greater power can be transmitted in DC

transmission system per conductor, because the active power in AC transmission has more losses, so that becomes lower.

The second case is comparison of the transmission conduction losses in the conductor. Assuming same properties and the length, same insulation level, same transferred power and same resistance for AC and DC. The relation of the current flowing in DC conductor and AC can be calculated by the equation 2.6, where  $I_{DC}$  is current in DC conductor and  $I_{AC}$  is current in AC conductor. The active power losses in DC can be calculated by the equation 2.7, where  $P_{L-DC}$  is active power losses in DC and  $P_{L-AC}$  is active power losses in AC. This gives that the active power losses in DC system is only half of the one in the AC system.

$$I_{DC} = \frac{I_{AC}}{\sqrt{2}} \tag{2.6}$$

$$P_{L-DC} = (\frac{1}{\sqrt{2}})^2 P_{L-AC} \tag{2.7}$$

HVDC transmission systems comparing with HVAC has simpler line construction, which has lower environmental effect. The conductors can be set closer to each other, because HVDC has no proximity effect. Less conductors are needed for the higher active power transmission capability. This results in smaller and less number of towers for HVDC in order to transfer same amount of the power.

The cable transmission system has a different behaviour than the overhead lines. The main issue in the long distance HVAC are current limit in the cables. The limitation arises, because the AC cable current consist of two components - active current and mainly capacitive current. Long HVAC cables has very high capacitive component in it, therefore the capacitive current becomes high, which causes higher reactive power transmission through long HVAC cables. The long HVAC cables have a limitation of distance. In order to reduce the capacitive current FACTS can be used in the system, which compensates capacitive current with the inductive current. Another solution to avoid this issue will be HVDC cables. The HVDC does not transfer the reactive power. The situation of the long HVAC transmission systems are severe in the overhead lines also. The distance are longer in the overhead lines than for the cable, but the problems arise when the overhead lines reaches 500 – 800 km [19]. In the system with fully maintained heavy loads collapse of the system can be observed even in the half of the desired distance. No loading or very small loading has a so called Ferranti effect. The effect is, that the voltage at the receiving end will rise and can exceed the required voltage limits, therefore damaging some equipment [20].

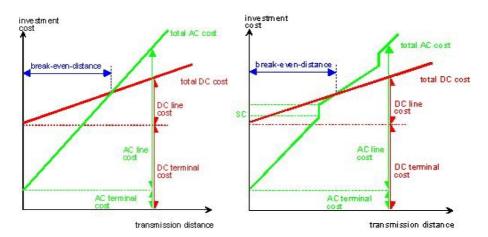

The greatest disadvantage of the HVDC transmission systems are costs of the converter station. The Figure 2.8 illustrates the break-even distance for the costs of HVAC and HVDC systems. As it can be seen in the left side Figure the costs of the DC terminal itself covers together AC terminal costs and half of the AC line costs. DC line costs are smaller than AC line. Initial investments for the DC system is way higher than AC, but the total investments, taking into account losses are higher for the AC system. Therefore the break-even distance of the costs can be observed. Break-even distance for the overhead lines is typically  $700-800~\mathrm{km}$  [19] and for submarine cables  $40-70~\mathrm{km}$  [21]. The break-even distance can vary depending on the properties of the project, transmitted power or voltage

levels. The right side Figure shows break-even distance for HVAC and HVDC taking into account the additional cost of the shunt compensation in the HVAC systems, therefore the break-even distance costs between HVAC and HVDC becomes even smaller.

Figure 2.8: Break-even distance of the costs for the HVAC and HVDC systems [5]

Another disadvantage of the HVDC system is limited overload capability of the converter. The overload capability in the converters are getting higher each year, due to semiconductor devices and increasing researches. Line commutated converters are called traditional HVDC converters. These converter stations require reactive power, has harmonic pollution, due to thyristors switching, which require filtering. The filtering in the HVDC traditional converter stations occupies huge amount of space. In the section 3.1 the traditional line commutated converters are described. The following section 3.2 points out the relatively new voltage source converter technology.

|         | 7 |  |  |  |

|---------|---|--|--|--|

| Chapter | J |  |  |  |

# TOPOLOGY OF THE CONVERTERS

#### 3.1 Line current commutated converters

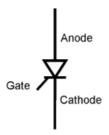

Line current commutated converters are based on the thyristor switches. When the first commercial HVDC lines were used, they were based on thyristor valves, due to the high reliability [7]. Thyristors have wide voltage blocking capability and large current conduction. The thyristor symbol is represented in 3.1. Thyristors have three terminals, where anode is positive, cathode-negative and gate represents triggering pulse of the thyristor. Anode has a higher potential than the cathode, therefore current are flowing from anode to cathode, only then when a small pulse are applied to the gate terminal, otherwise the conduction is not happening. After triggering, the pulse can be removed from the gate terminal and conduction process running till the flowing current drops to zero. After that a new pulse should be triggered again. The gate allows to turn-on thyristor at a desired time. Assuming frequency/time domain ( $\omega t$ ), the time when the pulse is triggered is called firing angle,  $\alpha$ . Phase voltage zero crossover defines the firing angle. Zero is the earliest point when the thyristor can be gated on [22]. Commonly thyristors are used with the snubbers connected to the device in parallel. Snubbers protect semiconductor from voltage transients, reduce the response of dv/dt and can be used for the soft switching and reduces losses [7].

**Figure 3.1:** Thyristor symbol [6]

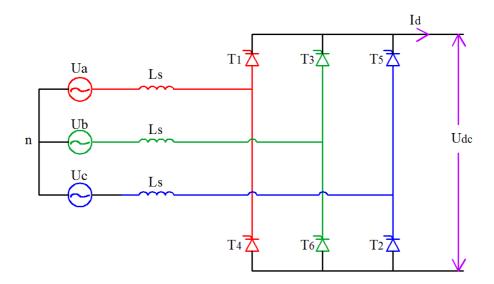

Classical line current commutated converters require the thyristor devices. The devices for operation require synchronized voltage source. Graetz bridge is the basic building block for the three phase conversion of the 6-pulse configuration converter. Definition of the 6-pulse means, that the converter has a six switching operations per period, causing the dc output voltage to be a harmonic ripple of six times the harmonic frequency [4]. The converter is illustrated in Figure 3.2. During the conduction period the current  $I_d$  flows through one of the upper thyristor  $(T_1,T_3)$  and  $T_5$  and one of the bottom thyristors  $(T_2,T_4)$  and  $T_6$ . The commutation between thyristors occurs naturally since they are displaced  $120^\circ$  [7]. The average DC voltage can be controlled by the firing angle  $\alpha$  or by applied voltage magnitude. The relationship are represented in equation 3.1, where  $V_D$  is an average DC side voltage,  $V_{LL}$  is rms value of line-line voltage,  $\alpha$  is a firing angle,  $L_8$  is AC-side inductance (stray inductance),  $\omega$  is angular frequency and  $I_d$  is converter DC current.

Figure 3.2: 3-phase 6-pulse converter

As it can be seen from the equation 3.1 the average DC voltage can be increased by increasing the  $V_{LL}$ . Furthermore the increased alpha reduces the  $V_D$ . Assuming the ideal situation, when the stray inductance  $L_s=0$  and keeping  $V_{LL}$  constant, the relevant cases can be observed. When  $\alpha=0^\circ$  the operation is similar to the diode operation. When  $\alpha=90^\circ$  the average voltage of the DC goes to zero. If the  $\alpha$  is increased further, the converter starts behave as the inverter. Since the thyristor only operates in two quadrants and the current flows in one way, during the inverter operation voltage polarity changes, therefore the power flow starts to flow from DC side [22].

$$V_D = \frac{3\sqrt{2}}{\pi} V_{LL} \cos \alpha - \frac{3\omega L_s}{\pi} I_d \tag{3.1}$$

Before the assumption of the ideal situation when  $L_s=0$  leads to simultaneous change from one thyristor to another. In reality there is always leakage inductance, which slows down that transition. The transition time is defined by the current changing steepness di/dt. This results in releasing and receiving phase voltages and transferring current at the same time. This process is called overlap and it is defined by the overlap angle,  $\mu$ . The Figure 3.3 represents overlap,  $\mu$ , in the rectifier operation, during the commutation, the line to line voltage is shorted and released energy are absorbed by  $L_s$ , till the transfer of the current is finished [7]. In order to extend overlap time the value of the inductor can be increased, but from the equation 3.1 can be seen that larger inductor will reduce the overall average DC voltage output.

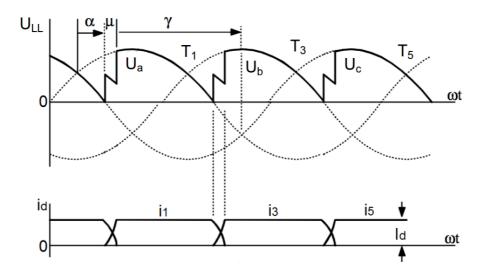

Figure 3.3: Commutation of the rectifier operation [7]

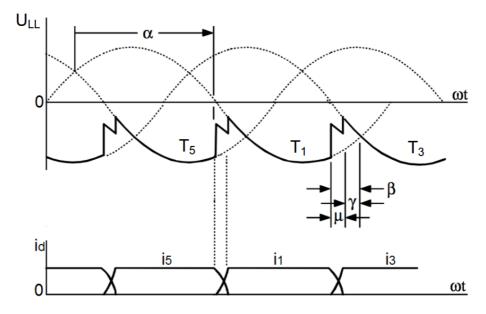

The commutation of the inverter operation is represented in Figure 3.4, as it can be seen the commutation process should be done before the voltage intersection, because the thyristor should recover its blocking capability. The minimum advance limit angle for safe commutation is called  $\beta$ . It is related to the  $\mu$  and  $\gamma$ . Where  $\gamma$  is the angle for the thyristor

to regain its capability to withstand positive voltage after current conduction (extinction angle) [7]. Relation between  $\mu$  and  $\gamma$  is showed in formula 3.2, where the link between  $\alpha$  and  $\beta$  is presented by equation 3.3.

$$\beta = \mu + \gamma \tag{3.2}$$

$$\alpha = 180^{\circ} - \beta \tag{3.3}$$

**Figure 3.4:** Commutation of the inverter operation [7]

Commonly the ideal thyristors should stop conducting when the current reaches zero crossing, however the real thyristors conduct further even the current reaches zero crossing, due to the reverse recovery charge. Commutation failure arises, when the flow of the current from one thyristor to another is not completed, before voltage commutation reverses across following thyristor. In order to avoid commutation failure the minimum turn-off time should be ensured. This allows thyristor to go to the reverse recovery state, where it can regain full forward voltage blocking capability. The turn-off time is associated with the extinction angle  $\gamma$  [22]. The failure causes high short circuit currents, therefore converter components are damaged. The minimum extinction angle should be ensured for the thyristors, otherwise during the system disturbances commutation failure is inevitable. During disturbances on the AC side are important to have safe margin for the extinction angle, however the large margin will require higher reactive power consumption. A trade of the extinction angle and reactive power, which depends on how strong is the AC grid, should be considered when designing LCC.

### 3.2 Voltage source converters

The first voltage source converters were introduced in the late 1990s. Since then the evolution in design, rapid grow of the power ratings and higher voltage levels are achieved [23]. Mainly the voltage source converters use power electronic valves, which can be turned-on and turned-off at desire. Usually valves are established with the insulated-gate bipolar transistors (IGBT). The IGBT circuit diagram is represented in the Figure 3.5a. The controllable signal is provided in the gate (G) port, which is the signal with two degrees of freedom turns on and turns off. When the signal has a turn-on command the IGBT starts to conduct current from the collector (C) to emitter (E). The current flow from the collector to emitter is called unidirectional, since it flows only in one way. However, in order to create the bidirectional current flow the anti parallel diode is introduced in the IGBT circuit diagram shown in the Figure 3.5b. Furthermore the IGBT has an excellent and simple switching characteristics, but the switching loses in it are higher than in thyristor based converters [24].

Figure 3.5: IGBT representations

With increasing power the voltage and current grow up. IGBTs are connected in series to withstand the higher voltage levels. Series connection provides higher voltage blocking capability. To withstand higher current ratings, the current is shared by connecting IGBTs in parallel. The anti parallel diode has to be design to prevent the stress created by the faults in the system. Usually the implementation of these features are done in the production and the IGBTs are provided in modules for the higher power applications.

In comparison voltage source converters with line commutated converters, the advantages and disadvantages depends on the project requirements. The VSC has a "black start capability", insignificant level of harmonic generation (valid not for 2-level converter, but for MMC type), hence no filters required, smoother reactive power control, easier power flow reversal, since it can be done by reversing current flow, compact site area. While the line commutated converter technology is more mature, therefore more reliable, the higher power transmission capability, good overload capability, lower station losses, lower cost [16].

### 3.2.1 2 level voltage source converters

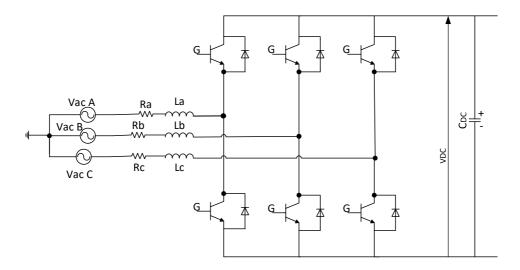

Two-level converters were the first generation of the voltage source converters, introduced in the beginning of this chapter 3.2. The 2-level VSC converters are using self commutated IGBT switches, which are able to turn on and turn off at will. The IGBT switches, which are doing this procedure are represented in section 3.2. The topology of the 2-level VSC converter is represented in the Figure 3.6.

Figure 3.6: Two level 3-phase voltage source converter topology

The 2-level 3 phase converter consist of the 6 arms or 3 legs. The IGBTs are representing switches in each arm, where the terminal G of the IGBTs is the gate, where the switching signal is provided. The operation principle is very straight forward. The switches in each leg are complementary, which means while upper is on the lower is turned-off. Therefore the each leg can produce half of the DC voltage, when the upper switch is turned-on the AC terminal voltage is connected to the positive DC terminal voltage, resulting in  $+0.5V_{DC}$  and when the lower switch is turned-on the AC terminal is connected to the negative DC terminal voltage, resulting in  $-0.5V_{DC}$  [25]. Therefore the resulting output voltage signal is a square wave with positive half value of DC and negative half value of DC.

#### 3.2.2 Modular multilevel converters

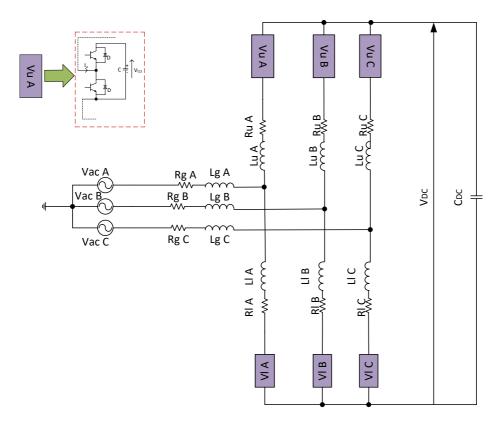

The modular multilevel converter (MMC) commercially was firstly used in the Trans bay project in San Francisco [26]. The topology of the MMC is illustrated in the Figure 3.7. The 3 phase MMC consist of 6 arms or 3 legs as the 2-level converter 3.2.1. Different from a 2-level converter the MMC consists of the number independent submodules in the each arm and the submodules contain its own capacitor. Each arm contains an inductor with the small resistance [27].

Figure 3.7: Modular multilevel converter topology

The operation principle of the MMC is a bit different than other converters, because the MMC has no turn-on or tun-off state for the flowing current. Therefore the current in the MMC flows continuously. The DC current divides equally into 3-phases and a 3-phases AC current splits equally in the upper and lower arms of the each phase [26]. The submodules existing in the arms are controlled in a way that the capacitor is inserted in the circuit or bypassed. This results for submodules act as the independent converters, where inserted voltage can be 0 or  $V_{stcell}$ . Depending on the current direction the capacitor in the submodule can be charged or discharged. When the sufficient amount of submodules are connected in series the stepped voltage wave form close to the sinusoidal can be generated. The generated sine wave contains low level harmonics distortion [27].

# MODELING AN ALTERNATE ARM CONVERTER

Alternate arm converter topology and operating principle will be discussed in the beginning of this chapter. The average dynamics model is developed in 4.3 section. This model will be used for the system studies. In this model the computation time will be significantly reduced, because the full model with all the dynamics increase simulation time, and results in slowing down system simulation studies. The average model will be constructed i the MATLAB/Simulink software and mathematically modeled in the following sub-sections.

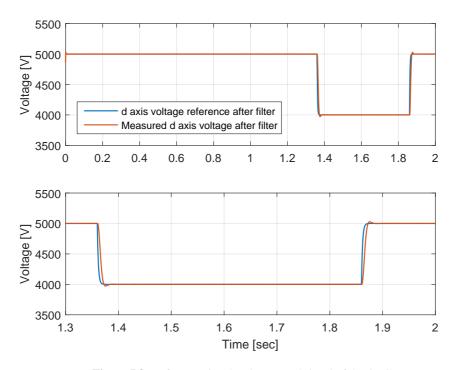

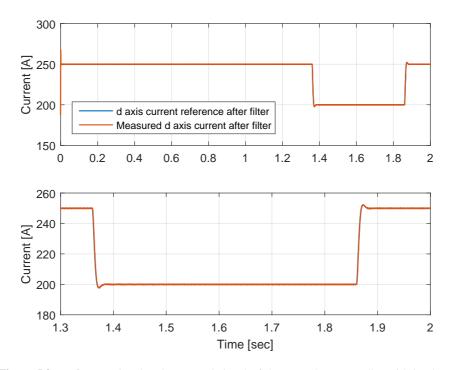

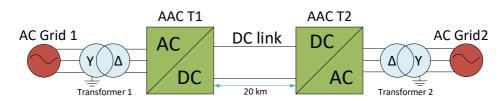

# 4.1 Topology of the alternate arm converter and operation principle