# Clock Tree Power Analysis

Knut Austbø

Master of Science in Electronics Submission date: June 2016 Supervisor: Per Gunnar Kjeldsberg, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## **Project Assignment**

Candidate name: Knut Austbø

Assignment title: Clock Tree Power Analysis

### Assignment text:

In some chips and power modes as much as half of the chip's power consumption can be associated with the clock trees, i.e. the circuit structures used to distribute the clock signal. A standard practice to optimize for power is to gate clocks, that is, to turn off clocks when they are not needed. There are challenging trade-offs between how and where to do the clock gating and what power performance that gives for the different power modes. This Master's project builds on using a power-benchmarking framework, and enhance it with dedicated clock power classification. A number of different clock gating strategies should be benchmarked on a representative test case, and a detailed assessment of the results is expected. The student needs to know basic digital design and power analysis in digital logic. Initial understanding of clock tree structures is preferable.

Responsible professor: Per Gunnar Kjeldsberg, IET, NTNU.

Supervisors: Johnny Pihl, Nordic Semiconductor ASA.

Co-supervisors: Jan Egil Øye and Are Aarseth, Nordic Semiconductor ASA.

## Abstract

The buffered clock tree structure is commonly used to distribute the clock signal to the memory elements in digital circuits. Since the clock signal is used as a temporal reference, it has to be distributed to the registers with decent timing characteristics and low skew. In order to achieve this, buffers and inverters are inserted in the clock tree, typically by a synthesis tool.

The clock tree is a major contributor to the power consumption. This is a result of a combination of high switching activity, due to the high frequency of the clock signal, and high total load in the buffers, registers and other cells. In order to reduce the power, clock gates are inserted in the clock tree, disabling the clock signal for unused logic. In this project, clock skew, buffer area and power consumption are considered the most important clock tree parameters.

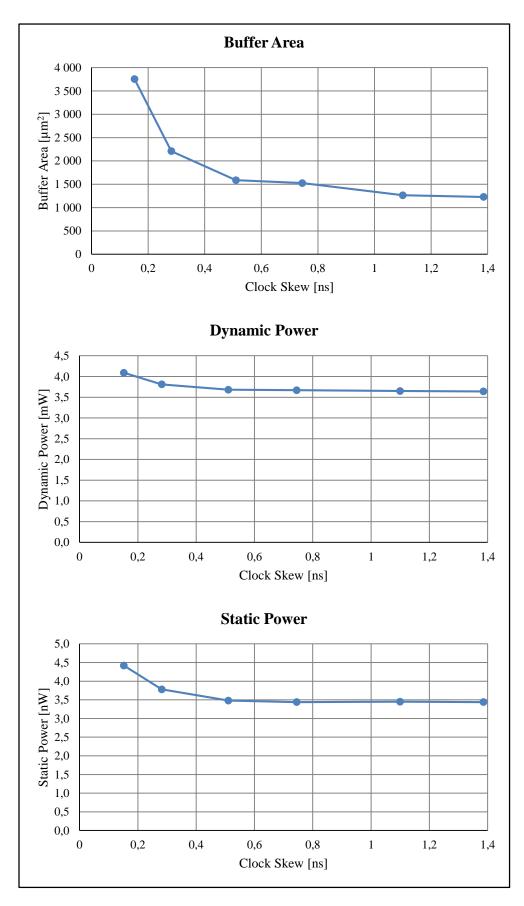

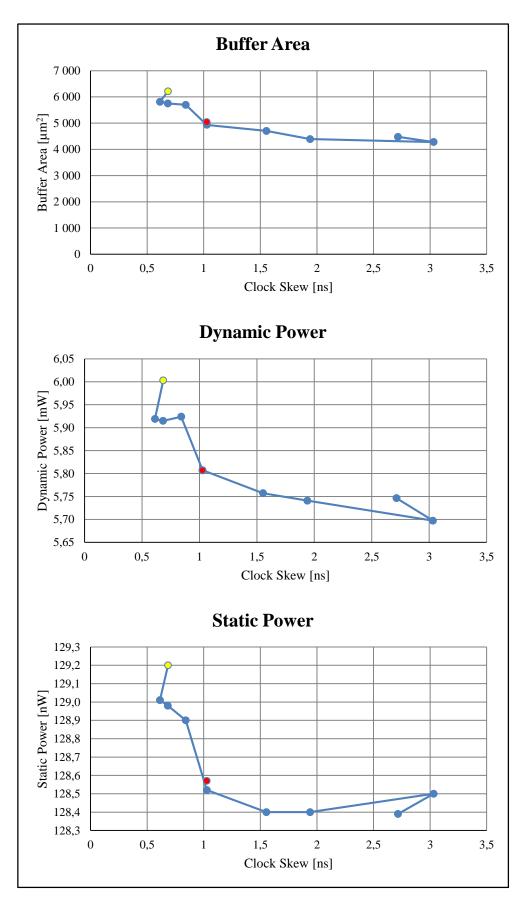

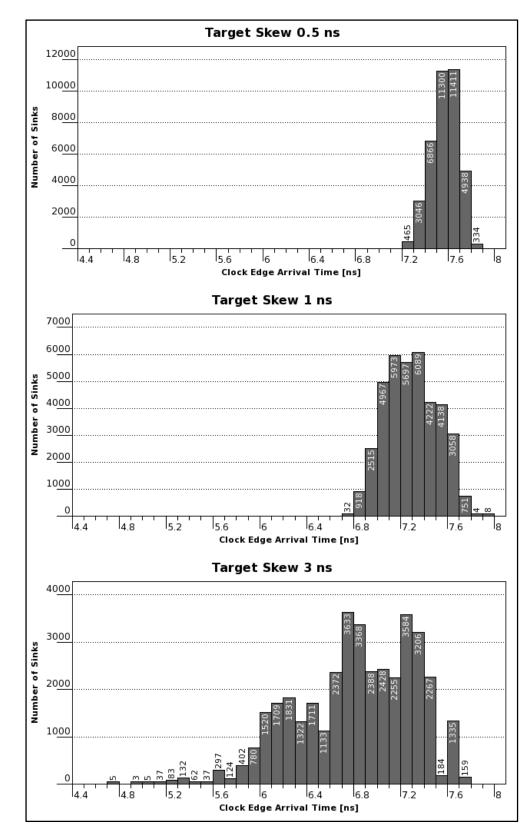

The clock-tree synthesis functionality of the Synopsys® IC Compiler<sup>TM</sup> tool has been explored. The goal of this exploration is to illustrate trade-offs and examine how the different options affect the synthesis results. Synthesis results on a generated test design and a real Bluetooth Smart design show cost reduction when the skew target is increased from the default zero skew target. By increasing the skew target to 0.5 ns for the generated design, the buffer area is reduced by 2 168  $\mu$ m<sup>2</sup> (58%), while the dynamic and static power are reduced by 0.41 mW (10%) and 0.94 nW (21%), respectively. The reductions are less significant in the Bluetooth Smart design, however, comparable in absolute values. By increasing the skew target to 1.0 ns, the buffer area is reduced by 1 284  $\mu$ m<sup>2</sup> (21%), while the dynamic and static power consumption are reduced by 0.19 mW (3.3%) and 0.7 nW (0.5%), respectively. The increased clock skew of the Bluetooth Smart design does not show any significant increase in hold time violations cost.

A multi-level module-level clock gating strategy has been implemented in the Bluetooth Smart design. In this strategy, an additional layer of clock gates has been inserted between the existing module-level and the clock source. Results indicate a dynamic power reduction of about 0.04 mW (18%) in a selected low-power scenario, without any significant cost increase, compared to the unmodified structure. However, the control circuit for the new level has not been implemented. Further work is therefore needed to determine if the tested strategy is beneficial.

## Sammendrag

Bufrede klokketrær er en mye brukt strategi for å distribuere klokkesignalet til minneelemntene i en digital krets. Ettersom klokkesignalet blir brukt som en tidsreferanse, er det viktig at signalet blir distribuert med god karakteristikk og liten tidsforskyvning. For å oppnå dette settes bufre og invertere inn i trestrukturen. Dette er vanligvis gjort av et synteseverktøy.

Klokketreet står for en stor andel av det total effektforbruket i et digital system. Årsaken til dette er en kombinasjon av høy vekselrate, på grunn av høy klokkefrekvens, og stor totallast i klokketreets bufre, registre og andre byggeblokker. Typisk blir klokkeporter satt inn i klokketreet for å redusere effektforbruket, ved å slå av klokkesignalet til ubrukt logikk. I dette prosjektet er klokkeforskyvningen, bufferarealet og effektforbruket ansett som de viktigste parameterne.

Klokkesyntesen i verktøyet Synopsys® IC Compiler<sup>TM</sup> har blitt undersøkt. Målet med denne undesøkelsen er å observere vekselvirkninger, samt å utforske hvordan innstillingene påvirker synteseresultatet. Synteseresultater fra et kunstig design og et reelt «Bluetooth Smart»-design viser at man kan oppnå reduserte kostnader ved å tillate høyere klokkeforskyving enn verktøyets standardmål (ingen forskyvning). Ved å øke forskyvningen til 0.5 ns oppnås en reduksjon i buffer areal på 168  $\mu$ m<sup>2</sup> (58%), samt en reduksjon i dynamisk- og statisk effektforbruk på henholdsvis 0,41 mW (10%) og 0,94 nW (21%), i det kunstige designet. For det reelle designet er reduksjonene mindre betydningsfulle, men fortsatt sammenlignbare i absoluttverdi. Ved å tillate 1.0 ns forskyvning reduseres bufferarealet med 1 284  $\mu$ m<sup>2</sup> (21%), mens det dynamiske- og statiske effektforbruket reduseres med henholdsvis 0,19 mW (3,3%) og 0,7 nW (0,5%). Undersøkelser viser at den økte forskyvningen ikke gir i høyere holdetidskostnad for det reelle designet.

En flernivå klokkeportstrategi på modulnivå har blitt implementert i det reelle «Bluetooth Smart»-designet. I denne strategien er et nytt nivå med klokkeporter innført mellom de eksisterende klokkeportene og klokkekilden. Resultater viser en effektreduksjon på omtrent 0,04 mW (18%) i en utvalgt strømsparingstilstand, dette uten noen betydningsfulle kostnadsøkninger. Styringskretsen for det nye nivået er imidlertid ikke implementert. Videre arbeid er derfor nødvendig for å avgjøre om denne strategien er lønnsom.

## Preface

This Master's Thesis has been written as a part of my 5-year M.Sc. degree in Electronics, with specialization in design of digital systems, at the Norwegian University of Science and Technology (NTNU). This thesis is a continuation of a previous semester project, where a clock-tree analysis tool was created to aid the designer in the clock-tree synthesis process [1]. The goal of this thesis has been to use features of the analysis tool to examine the clock tree synthesis in Synopsys® IC Compiler<sup>™</sup>, as well as evaluate a clock gating strategy with multiple levels of module-level clock gates.

Nordic Semiconductor ASA has contributed to this Thesis with a workplace and a computer. In addition, I have been given access to a local server with licenses for the required Synopsys® tools. On this server, I have been able to work without any major interruptions and without interfering with design work by Nordic Semiconductor employees. The only issue during this project was a failure of a hard disk controller. This failure lead to about one week of downtime, before the component was replaced. However, this issue was not critical for the progress of the Thesis. I would like to thank Nordic Semiconductor and my supervisors at Nordic Semiconductor, Jan Egil Øye, Are Aarseth and Johnny Pihl, for the help and feedback during this project.

During the semester, I have also been doing some part time work for Nordic Semiconductor. Among the different tasks, I have finalized the analysis tool from the previous project and created a user guide. The tool is now usable by Nordic Semiconductor employees.

I would like to thank Professor Per Gunnar Kjeldsberg for good academic supervision throughout the semester. In addition, I would like to thank my fellow students at NTNU for a good working environment. Lastly, I would like to thank my family, friends and girlfriend for the support during the project. A special thanks to my brother Bjørn, for helping me proofreading this Thesis.

Knut Austbø Trondheim, 17 June 2016

# **Table of Contents**

| ABSTRACT                                                                                                                                                                                                                                                                                               | P |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| PREFACE       VI         TABLE OF CONTENTS       IX         LIST OF FIGURES       XIII         LIST OF TABLES       XV         ABBREVIATIONS       XVI         1       INTRODUCTION       I         1.1       PROJECT DELINEATION AND CONTRIBUTIONS       I         1.2       REPORT STRUCTURE       2 | A |

| TABLE OF CONTENTS       IX         LIST OF FIGURES       XIII         LIST OF TABLES       XV         ABBREVIATIONS       XVII         1       INTRODUCTION       1         1.1       PROJECT DELINEATION AND CONTRIBUTIONS       1         1.2       REPORT STRUCTURE       2                         | S |

| LIST OF FIGURESXIII<br>LIST OF TABLESXV<br>ABBREVIATIONSXVII<br>1 INTRODUCTION                                                                                                                                                                                                                         | Р |

| LIST OF TABLESXV<br>ABBREVIATIONSXVI<br>1 INTRODUCTION                                                                                                                                                                                                                                                 | Т |

| LIST OF TABLESXV<br>ABBREVIATIONSXVI<br>1 INTRODUCTION                                                                                                                                                                                                                                                 | L |

| ABBREVIATIONS                                                                                                                                                                                                                                                                                          |   |

| 1       INTRODUCTION       1         1.1       PROJECT DELINEATION AND CONTRIBUTIONS       1         1.2       REPORT STRUCTURE       2                                                                                                                                                                |   |

| 1.1       PROJECT DELINEATION AND CONTRIBUTIONS       1         1.2       REPORT STRUCTURE       2                                                                                                                                                                                                     |   |

| 1.2 Report Structure                                                                                                                                                                                                                                                                                   | 1 |

|                                                                                                                                                                                                                                                                                                        |   |

|                                                                                                                                                                                                                                                                                                        |   |

|                                                                                                                                                                                                                                                                                                        | 2 |

| 2.1 TERMINOLOGY                                                                                                                                                                                                                                                                                        |   |

| 2.2 BLUETOOTH SMART                                                                                                                                                                                                                                                                                    |   |

| 2.3 POWER CONSUMPTION                                                                                                                                                                                                                                                                                  |   |

| 2.3.1 Dynamic Power                                                                                                                                                                                                                                                                                    |   |

| 2.3.2 Static Power                                                                                                                                                                                                                                                                                     |   |

| 2.4 CLOCK TREES                                                                                                                                                                                                                                                                                        |   |

| 2.4.1 Characterization                                                                                                                                                                                                                                                                                 |   |

| 2.4.2 Clock Buffers and Inverters                                                                                                                                                                                                                                                                      |   |

| 2.4.3 Clock Gating Cells                                                                                                                                                                                                                                                                               |   |

| 2.4.4 Registers                                                                                                                                                                                                                                                                                        |   |

| 2.5 CLOCK GATING STRATEGIES                                                                                                                                                                                                                                                                            |   |

| 2.5.1 Leaf-Level Clock Gating                                                                                                                                                                                                                                                                          |   |

| 2.5.2 XOR Self-Gating                                                                                                                                                                                                                                                                                  |   |

| 2.5.3 Module-Level Clock Gating                                                                                                                                                                                                                                                                        |   |

| 3 PREVIOUS WORK AND DESIGN TOOLS                                                                                                                                                                                                                                                                       | 3 |

| 3.1 CLOCK TREE SYNTHESIS                                                                                                                                                                                                                                                                               |   |

| 3.2 CLOCK GATING STRATEGIES                                                                                                                                                                                                                                                                            |   |

| 3.3 CLOCK TREE IMPLEMENTATION IN SYNOPSYS® IC COMPILER <sup>TM</sup>                                                                                                                                                                                                                                   |   |

| 3.3.1 Clock Tree Options                                                                                                                                                                                                                                                                               |   |

| 3.3.2 Clock Tree Synthesis                                                                                                                                                                                                                                                                             |   |

| 3.3.3 Clock Tree Optimization                                                                                                                                                                                                                                                                          |   |

| 3.3.4 Logic Level Balancing                                                                                                                                                                                                                                                                            |   |

| 3.3.5 Guidelines                                                                                                                                                                                                                                                                                       |   |

| 3.4 POWER ESTIMATION IN SYNOPSYS® IC COMPILER <sup>TM</sup>                                                                                                                                                                                                                                            |   |

|   | 3.5 Clo  | CK TREE ANALYSIS TOOL            | 26 |

|---|----------|----------------------------------|----|

|   | 3.5.1    | Activity-Based Power Estimation  | 27 |

| 4 | METH     | ODOLOGY                          | 29 |

|   | 4.1 TEST | Г Designs                        |    |

|   | 4.1.1    | Generated Test Design            |    |

|   | 4.1.2    | Bluetooth Smart Design           |    |

|   | 4.2 Pow  | PER ESTIMATION                   |    |

|   | 4.2.1    | ICG Enable Pin Toggle Rate       |    |

|   | 4.3 ICG  | STRUCTURE ANALYSIS               |    |

| 5 | CLOC     | K TREE SYNTHESIS EXPLORATION     |    |

|   | 5.1 Clo  | CK SIZE AND COMPLEXITY           |    |

|   | 5.1.1    | Effects of the Clock Size        | 40 |

|   | 5.1.2    | Clock Tree Complexity Effects    |    |

|   | 5.2 TAR  | GET SKEW                         | 43 |

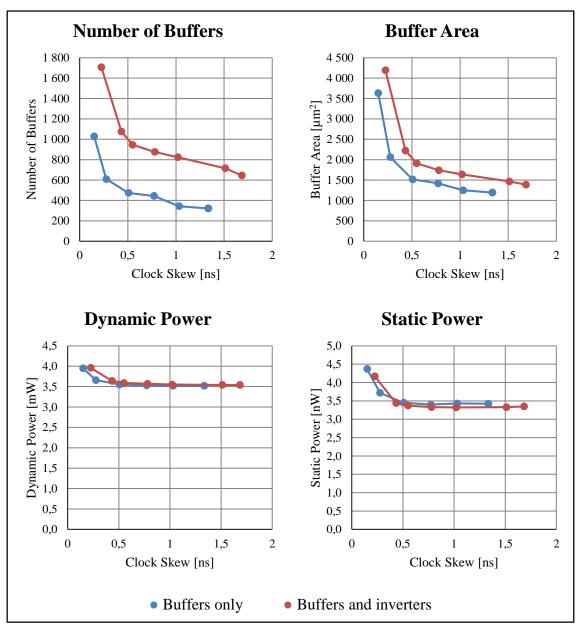

|   | 5.2.1    | Generated Test Design Results    | 44 |

|   | 5.2.2    | Bluetooth Smart Design Results   |    |

|   | 5.3 May  | KIMUM TRANSITION TIME CONSTRAINT | 51 |

|   | 5.3.1    | Generated Test Design Results    |    |

|   | 5.3.2    | Bluetooth Smart Design Results   | 53 |

|   | 5.4 BUE  | FER SELECTION                    | 54 |

|   | 5.4.1    | Generated Test Design Results    | 54 |

|   | 5.5 Log  | IC LEVEL BALANCING               | 56 |

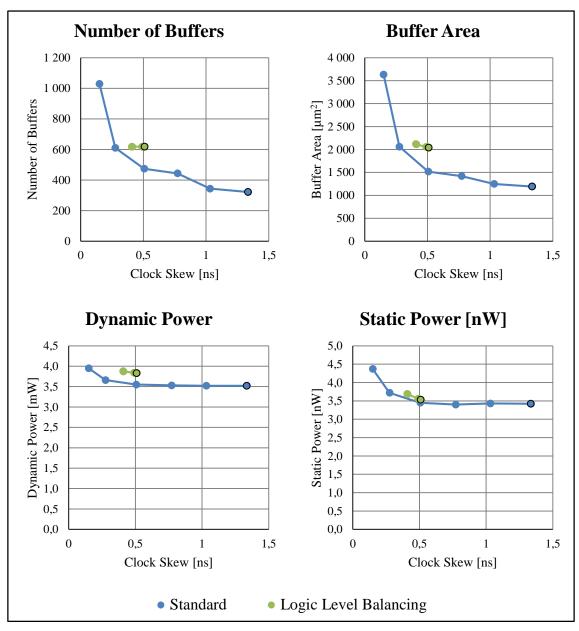

|   | 5.5.1    | Generated Test Design Results    |    |

|   | 5.6 Syn  | THESIS INCONSISTENCY             |    |

|   | 5.7 Sum  | IMARY                            | 59 |

| 6 | CLOC     | K GATING EXPERIMENT              | 61 |

|   | 6.1 Low  | Power Scenario                   | 61 |

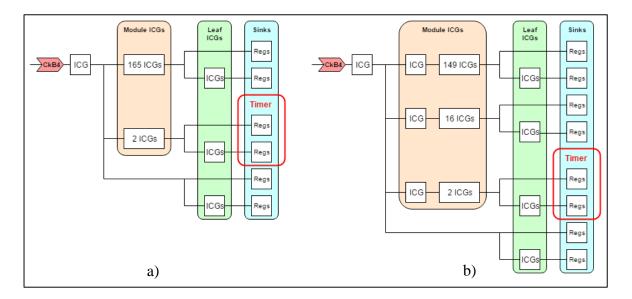

|   | 6.2 Імрі | LEMENTATION                      |    |

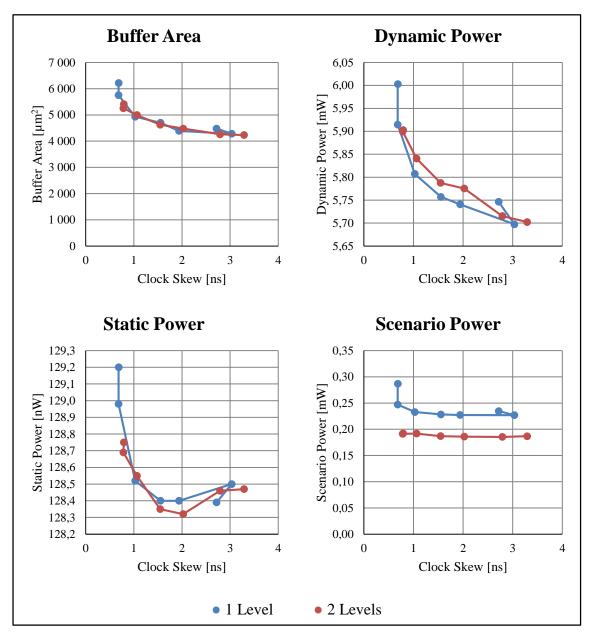

|   | 6.3 Resu | ULTS AND DISCUSSION              | 63 |

| 7 | CLOC     | K TREE SYNTHESIS RECOMMENDATIONS | 67 |

|   | 7.1 Prei | REQUISITES                       | 67 |

|   | 7.2 REC  | OMMENDED SETTINGS                | 67 |

|   | 7.2.1    | Constraints and Targets          | 67 |

|   | 7.2.2    | Buffer Selection                 |    |

|   | 7.2.3    | Logic Level Balancing            |    |

|   | 7.2.4    | XOR Self-Gating                  |    |

|   | 7.3 CTS  | PROCEDURE                        | 68 |

| 8 | CONC     | LUSIONS                          |    |

| - |          | THER WORK                        |    |

|   |          |                                  |    |

| 9 BIBLIOG  | RAPHY                        |

|------------|------------------------------|

| APPENDIX A | EXAMPLE ICG STRUCTURE REPORT |

| APPENDIX B | GENERATED DESIGN RESULTS     |

| APPENDIX C | BLUETOOTH SMART RESULTS      |

| APPENDIX D | REGISTER DELAY CALCULATION   |

# List of Figures

| Figure 2.1: Common clock distribution structures.                     |   |

|-----------------------------------------------------------------------|---|

| Figure 2.2: Buffered clock tree with ICGs.                            | 9 |

| Figure 2.3: ICG schematic                                             |   |

| Figure 2.4: Hold and setup timing                                     |   |

| Figure 2.5: Scan register schematic                                   |   |

| Figure 2.6: Scan chain connection                                     |   |

| Figure 2.7: Clock gating at leaf level                                |   |

| Figure 2.8: XOR self-gating                                           |   |

| Figure 2.9: Module-level clock gating in a) one and b) two levels     |   |

| Figure 3.1: Logic Level Balancing                                     |   |

| Figure 4.1: SoC design flow                                           |   |

| Figure 4.2: Test design data path                                     |   |

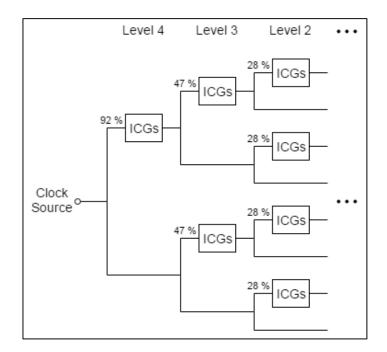

| Figure 4.3: Test design clock tree structure                          |   |

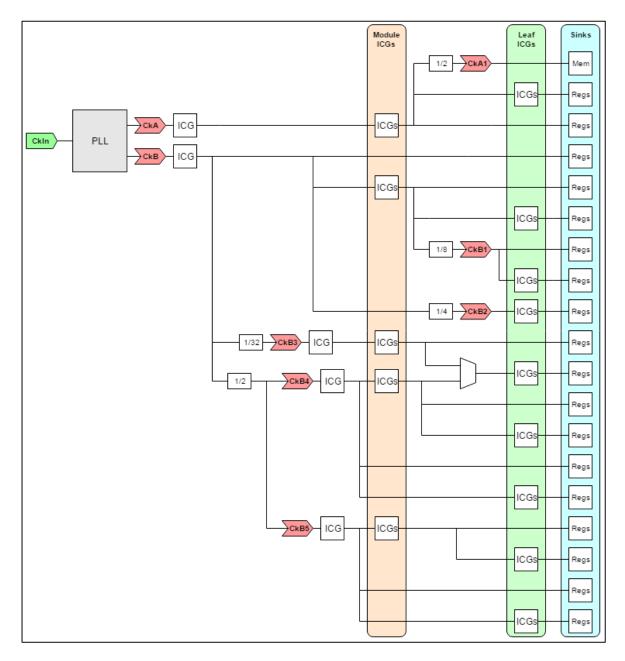

| Figure 4.4: CkIn tree structure                                       |   |

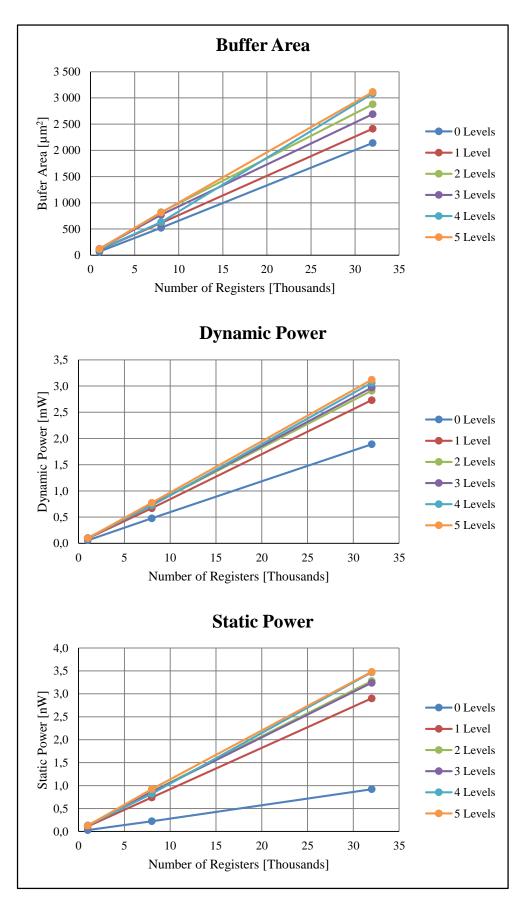

| Figure 5.1: Design size and clock complexity results.                 |   |

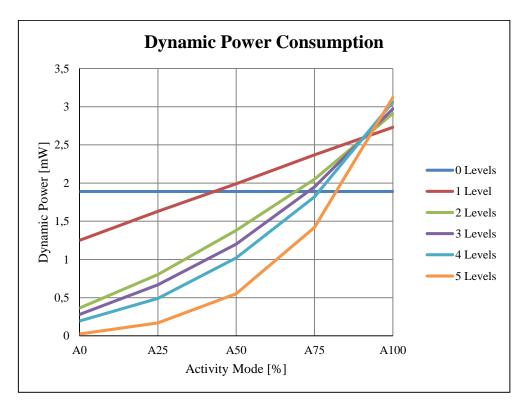

| Figure 5.2: Dynamic power consumption for activity 0-100%             |   |

| Figure 5.3: Costs vs. achieved skew                                   |   |

| Figure 5.4: Target skew costs vs. achieved skew                       |   |

| Figure 5.5: Clock edge arrival histogram.                             |   |

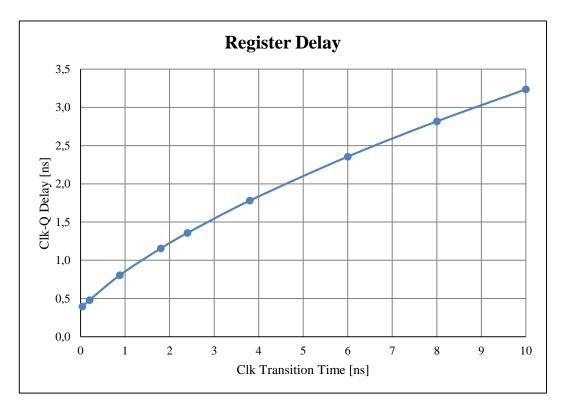

| Figure 5.6: $Clk$ to $Q$ propagation delay                            |   |

| Figure 5.7: Buffer selection costs vs. achieved skew                  |   |

| Figure 5.8: Logic level balancing cost vs. achieved skew.             |   |

| Figure 6.1: Subtree clock structure with a) one and b) two ICG levels |   |

| Figure 6.2: Multi level module ICG results                            |   |

# List of Tables

| Table 2.1: Internal node ENint state table.                                    | 12 |

|--------------------------------------------------------------------------------|----|

| Table 3.1: Clock tree synthesis options.                                       | 21 |

| Table 4.1: Clock inputs per level                                              | 32 |

| Table 4.2: Clock gating statistics                                             | 33 |

| Table 4.3: Enable pin toggle rate results.                                     | 36 |

| Table 5.1: Design size synthesis results.                                      | 40 |

| Table 5.2: ICG levels synthesis results                                        | 42 |

| Table 5.3: Test design target skew parameter results                           | 44 |

| Table 5.4: Bluetooth Smart design target skew parameter results.               | 46 |

| Table 5.5: Bluetooth Smart target skew hold time cost                          | 50 |

| Table 5.6: Max transition parameter results for the generated design.          | 52 |

| Table 5.7: Leaf max transition parameter results on the generated design       | 52 |

| Table 5.8: Max transition parameter results on the Bluetooth Smart design      | 53 |

| Table 5.9: Leaf max transition parameter results on the Bluetooth Smart design | 53 |

| Table 5.10: Buffer selection results.                                          | 55 |

| Table 5.11: Logic level balancing results.                                     | 57 |

| Table 5.12: Clock Tree Synthesis Exploration Summary                           | 60 |

| Table 6.1: Additional ICG level results                                        | 63 |

# Abbreviations

| auons                                            |

|--------------------------------------------------|

| Analogue-to-digital converter                    |

| Complementary metal-oxide-semiconductor          |

| Central processing unit                          |

| Clock tree synthesis                             |

| Digital-to-analogue converter                    |

| Design for test                                  |

| Design rule constraints                          |

| Engineering change orders                        |

| Electrostatic discharge                          |

| Floating point unit                              |

| Hardware descriptive language                    |

| Input/output                                     |

| Integrated clock gate                            |

| Department of Electronics and Telecommunications |

| Internet of Things                               |

| Industrial, scientific and medical               |

| Mega bit per second                              |

| Metal-oxide-semiconductor field-effect           |

| Multiplexer                                      |

| Not and (logical function)                       |

| N-channel MOSFET                                 |

| Norwegian University of Science and Technology   |

| Phase locked loop                                |

| P-channel MOSFET                                 |

| Quality of results                               |

| Register transfer level                          |

| System on chip                                   |

|                                                  |

|                                                  |

## **1** Introduction

One of the leading trends in today's electronics is the Internet of Things (IoT), a trend where all kinds of devices are connected in networks. This is a rapidly growing trend with estimates of about 40 billion IoT devices by 2020 [2, 3]. The Internet of Things has emerged as a result of progress in chip technology. Devices are becoming increasingly smarter and power efficient. In addition, new System on Chip (SoC) solutions with integrated radio enable wireless communication with smart devices.

The power consumption is one of the most important parameters of IoT devices. Low power consumption has several benefits, e.g. increased the time between each battery recharging or battery replacement. Therefore, modern devices have several features to reduce the power consumption. Dependent on the application, the device operates in different activity modes. Typically, the device spends most of its time in an idle or low power mode, from which it wakes up to perform a task in a high activity mode. In order to do make the device as efficient as possible, it is therefore important to consider the power consumption in several different modes.

One of the major contributors to the power consumption is the clock tree. The task of the clock tree is to synchronize the digital circuit, as the clock signal is used as a temporal reference in the circuit. In other words, the clock edge has to arrive simultaneously at every memory element in the design. In order to distribute the clock signal across the chip with decent timing characteristics, a synthesis tool is used to implement a balanced clock tree. This tool inserts buffers in the clock tree in order to improve timing performance. However, these buffers increase the total load in the clock tree. In addition, due to its high frequency, the clock signal is typically the fastest toggling signal in the circuit. The combination of high toggle rate and high load is resulting in very high power consumption.

Clock gates are inserted in the clock tree to reduce the power consumption. These gates are used to stop propagation of the clock signal to unused circuitry, thus reducing power consumption. However, inserting clock gates increases the complexity of the clock tree and makes it more difficult for the synthesis tool to achieve good timing performance.

### **1.1 Project Delineation and Contributions**

In a previous project, it was observed inexplicably large variations in the results after clock tree synthesis in Synopsys® IC Compiler<sup>™</sup> [1]. This observation indicates the need of a

thorough exploration of the synthesis tool. The target of this exploration is to obtain a better understanding of the tool functionality. It is considered important to find out how the synthesis settings influence the synthesis results and potential performance trade-offs. In addition, the effects of the design size and complexity should be examined. The insertion of clock gates in the clock tree lead to increased clock complexity, and can cause imbalance in the clock tree. An assessment of the cost of inserting clock gates is therefore required.

Based on the results of the synthesis exploration, a set of synthesis recommendations has been developed. These recommendations cover the synthesis process and its settings from preparing the design for synthesis to post synthesis debugging. The purpose of this guide is to aid the designer in the synthesis process and enable him to achieve good synthesis results.

In order to minimize the power consumption in the clock tree, a multi-level module-level clock gating strategy has been examined for a real Bluetooth Smart design. The idea behind this strategy is to extend the current single-level module clock gating with an additional level closer to the clock root. However, due to the limited time of this project, the work has been limited to the synthesis stage only. This means that the control circuitry for the new level has not been implemented, as this is done in RTL.

The main contributions in this project can be summed up in the following three parts:

- Exploration of the clock tree synthesis and optimization functionality in Synopsys<sup>®</sup> IC Compiler<sup>TM</sup>.

- Creation of a set of recommendations for the synthesis process in Synopsys<sup>®</sup> IC Compiler<sup>™</sup>.

- 3. Examination and evaluation of a purposed multi-level module-level clock gating strategy for a real Bluetooth Smart design.

### **1.2 Report Structure**

This report has been divided into the following chapters:

**Chapter 2: Theory** presenting the useful background theory for this project. Clock trees and CMOS power consumption are examples of presented topics.

**Chapter 3: Previous Work and Design Tools** presenting relevant research and literature. In addition, the tools used in this project are described.

**Chapter 4: Methodology** describing the basic methodology in this project. The two test designs used in this project are presented.

**Chapter 5: Clock Tree Synthesis Exploration** presenting the methodology and results of exploring the functionality of the clock tree synthesis in Synopsys<sup>®</sup> IC Compiler<sup>TM</sup>. A detailed assessment of the results is also provided.

**Chapter 6: Clock Gating Experiment** examining the benefits and drawbacks of implementing an additional level of module-level clock gating.

**Chapter 7: Clock Tree Synthesis Recommendations** presenting a set of useful recommendations for clock tree synthesis in Synopsys® IC Compiler<sup>TM</sup>.

**Chapter 8: Conclusion** summarizing the results of this project, in addition to suggesting topics for further work.

Chapter 9: Bibliography listing references used in this report.

Additional information, e.g. raw data from synthesis results, are attached to this report in the Appendices A to D.

## 2 Theory

This chapter presents the background theory in this project. First, common terminology, used throughout this report is presented in Section 2.1. Then, a short introduction to the Bluetooth Smart technology is given in Section 2.2. CMOS power consumption is described in Section 2.3. Section 2.4 presents the buffered clock-tree structure, while clock gating strategies, used to reduce the power consumption of this structure, are presented in Section 2.5.

## 2.1 Terminology

Expressions commonly used throughout this report are presented below:

**Cell:** Cells are the building blocks of the circuit design. A cell can consist of multiple gates and sub-cells.

**Net:** The nets are the interconnections between the cells. A net is driven by one cell output only, but can be connected to several cell inputs.

**Fan-out:** The fan-out of an output pin is the collection of cell inputs connected to the output net.

## 2.2 Bluetooth Smart

Bluetooth Smart, or Low Energy (LE), is a wireless technology located in the 2.4 GHz ISM band [4, 5]. The technology has 40 channels with 2 MHz bandwidth and uses adaptive channel hopping to avoid interference from other 2.4 GHz technologies such as Wi-Fi, ZigBee and regular Bluetooth. Bluetooth Smart is especially designed for low power applications and offers a bit rate of 1 Mbps with a low latency of 3 ms. The output power is limited to 10 mW (10 dBm) which gives an open field range up to 100-150 meters [5].

Bluetooth Smart has a low data throughput [5]. Therefore, it is not suited for transferring large quantities of data, e.g. video or audio. Instead, it is used to transmit states, e.g. small quantities of data such from sensors, such as temperature and heart rate. Due to its low power functionality, Bluetooth Smart is well suited for many IoT applications. In these applications, the device spends most of the time asleep, only waking up to transmit its state. Typically, the device operates on battery, and low power consumption is very important.

### **2.3 Power Consumption**

The power consumption in digital CMOS can be divided into the dynamic power consumption related to switching activity, and the static consumption that is activity independent [6].

#### 2.3.1 Dynamic Power

The dynamic power consumption is divided into two groups: switching power and internal power [6]. The switching power is the average power dissipated by the nets and is the main contribution to the total dynamic power consumption. Equation (1) shows a formula of the switching power for a single net, where  $V_{DD}$  is the supply voltage and  $C_L$  is the net load capacitance. The switching activity is given by the clock frequency  $f_{CLK}$  and the switching factor  $\alpha$ . This factor is the average number of "0-to-1" and "1-to-0"-transitions by the net in one clock cycle.

$$P_{SW} = \frac{\alpha}{2} C_L V_{DD}^2 f_{CLK} \tag{1}$$

The secondary source to dynamic power consumption is the internal power,  $P_{IN}$ . This is the average dynamic power dissipated internally in a cell. Activity on the inputs of the cell causes switching in the internal nodes, and creates short circuit currents through the cell. For a short period when a net is transitioning, both the PMOS and the NMOS transistors are conducting, resulting in a short circuit current from  $V_{DD}$  to ground. The power dissipated by this effect,  $P_{SC}$ , is given in Equation (2), where  $t_{TR}$  is the transition time and  $\overline{I_{SC}}$  is the average short circuit current.

$$P_{SC} = \alpha t_{TR} \overline{I_{SC}} V_{DD} f_{CLK}$$

(2)

The impact of the internal power is dependent on the complexity of the cell. Simple cells, like an inverter or a two-input NAND gate, have few transistors and internal nets. In these cells, the internal power is typically less than 10 % of the switching power of the output [6]. However, for complex cells with several levels, such as multistage clock buffers, the internal power may exceed the output net power.

In order to calculate the total dynamic power consumption, the switching power is summed over all nets and added to the sum of the internal power of all cells, as shown in Equation (3).

$$P_{DYN} = \sum_{n}^{Nets} P_{SW,n} + \sum_{c}^{Cells} P_{IN,c}$$

(3)

#### 2.3.2 Static Power

Similar to the internal power consumption, the static power consumption is also calculated per cell in the design, as shown in Equation (4). The cause of the static consumption is leakage currents  $I_{LK}$  in the cells, as the transistors do not work as perfect switches [6]. Although this consumption is switching independent, it may be dependent on the state of its input, output and internal nodes.

$$P_{ST} = V_{DD} \sum_{c}^{Cells} I_{LK,c}$$

(4)

The main sources of leakage currents in CMOS transistors are [6]:

- Sub-threshold leakage: The current flowing from drain to source when operating in the sub-threshold region.

- Gate leakage: Oxide tunnelling and hot carrier injection is causing current flow from the gate to the substrate.

- Gate induced drain leakage: Current from the drain to the substrate due to high  $V_{DG}$  voltage.

- Reverse bias junction leakage: Leakage caused by carrier drift in the depletion region.

Due to technology scaling, the static power is becoming increasingly important. There are many strategies for reducing static power, e.g. power gating, Multi- $V_T$  designs and transistor stacking. However, as the dynamic power consumption is the dominant in the clock tree, this project does not implement any strategies for reducing static power consumption.

## 2.4 Clock Trees

The task of the clock distribution network is to control the data flow in synchronous digital systems [7]. The clock is used as a temporal reference for movement of data. Therefore, it is very important that the clock is distributed, sharp and clean, to every part of its domain, without any major timing differences. This is a complex task as the clocks are the signals with the highest frequencies within the design, and both the fan-out and physical distance can be large. A single clock source might drive several thousand registers all across the chip. In addition, technology scaling is making this task even more difficult as the lines become more resistive as the dimensions are reduced.

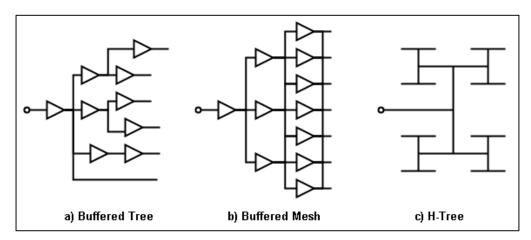

There are several different ways to organize the clock network [7]. Some common structures are illustrated in Figure 2.1. This project focuses on buffered clock trees. In these trees, buffers are inserted at the clock source and along the clock paths, organized in a tree structure. The clock source is referred to as the root of the tree, while the registers (or sinks) are the leaf nodes. Clock buffers are inserted to improve reliability and timing characteristics, as described in Section 2.4.2. The most important characteristics of the clock trees are described in the following section.

Figure 2.1: Common clock distribution structures.

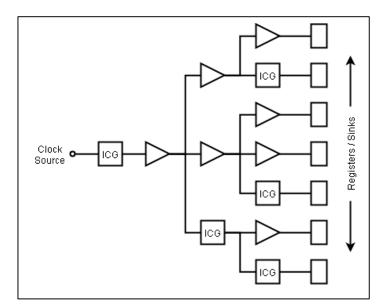

The nodes in the tree are switching state twice every clock cycle, resulting in very high switching activity. However, the clock is not always needed on the entire chip at all time, as some logic might be unused and not all registers changes value. In order to reduce the power consumption, the clock can be turned off where it is not needed [6]. This can be done with Internal Clock Gating Cells (ICGs), described in Section 2.4.3. As presented in

Section 2.5, there are several strategies in placing the ICGs. Figure 2.2 shows an example of a clock tree with ICGs.

Figure 2.2: Buffered clock tree with ICGs.

An ICG has the ability to stop the clock signal from propagating and thereby cancel all switching activity and dynamic power consumption in its subtree. ICGs are commonly used to reduce the dynamic power consumption of the clock tree, but does not have any major effect on the static power consumption.

Power gating is a common method to reduce the static power consumption. In order to stop leakage currents, the power rail is switched off for unused logic. A side effect of this is that all register states are lost. To be able to keep the register contents, their state has to be saved in retention registers before the power is gated. The states can be reloaded once the power is restored. Power gating is not the focus of this project, and is therefore not further examined.

In some cases, the clock signal may be derived from other clocks domains. A slower clock can be created by using clock dividers, and a faster clock can be generated with phase-locked loops (PLLs). In both cases, the derived clock tree becomes a subtree of the original tree. A clock tree can also have several clock sources. However, only one source is active at a time, selected by a clock multiplexer (MUX). A typical example is the selection of an internal RC-oscillator versus a high precision external crystal oscillator as the clock source.

#### 2.4.1 Characterization

In order to be able to characterize the performance of a clock tree, the following parameters are defined [1]:

**Longest path (latency):** This is a measure of the longest time delay from the clock source to any leaf node in the tree. A high latency is not desired, as it makes the clock unreliable and prone to timing mismatch. High latency is also an indication of high power consumption, as the clock tree is deep and has several stages of buffering.

**Clock skew:** The skew is a measure of the difference in timing between two leaf nodes. The clock skew is often denoted as the maximum global skew, the difference between the shortest and longest path. In an ideal case, the clock edge arrives simultaneously at all registers, i.e. zero skew. However, it is difficult and expensive to achieve zero clock skew. The clock skew affects the data path, and can cause race effects and limit the performance.

**Transition time:** The transition time is the time it takes for the clock signal to switch state. For reliability, sharp and clean edges, i.e. short transition times, are desired. The transition time should also be equal for the rising and falling edge. A short transition time also reduces the short circuit current, as described in Section 2.3.1. The drawback of low transition times is higher current peaks and noise.

**Number of sinks:** This parameter is equal to the total number of registers using the clock signal. It is used as a measure of the size and complexity of the clock domain.

**Number of buffers:** The number of buffers is the total number of buffers and inverters in the clock domain.

**Number of ICGs:** This parameter is the total number of clock gating cells in the clock domain.

**Number of cells:** The total number of cells includes all buffers, inverters, ICGs, multiplexers, and any other cells in the clock tree.

**Sinks per buffer (SpB):** This ratio provides an indication of both the efficiency of the buffering and the fan-out in the clock tree. The parameter can be used to compare clock trees of different size/number of sinks.

**Buffer area** (**BA**): The total buffer area is a measurement of the total area cost of the buffers inserted in the tree. Buffer area is also related to power consumption, as the buffers are a major source to power consumption in the clock tree.

**Sinks per buffer area (SpBA):** Similar to sinks per buffer, this parameter can be used to compare different clock trees. However, this parameter takes the buffer area into account.

**Power consumption:** The power consumption in the clock tree is a very important parameter. However, it can be very different in different modes. It is therefore important to consider different scenarios, and evaluate both the dynamic and static power consumption.

#### 2.4.2 Clock Buffers and Inverters

Clock buffers are inserted into the tree structure to amplify the clock signal, reduce the propagation delay and sharpen the clock edges. Nets with high load react very slowly, which gives slow transitions. There are two primary sources to the load in the clock tree nets; the input capacitances of the gates connected to the net and the line load itself. The input capacitances become a problem when the fan-out is large. The total fan-out capacitance is equal to the sum of all the input capacitances, as shown in Equation (5) and can be of significant size when the fan-out is large. A single buffer can be inserted to drive the net, but this might require a very large buffer. Alternatively, the fan-out can be divided into several branches driven by multiple buffers. The optimal solution is dependent on the fan-out and the range of buffers available in the cell library.

$$C_{Fan-out} = \sum_{i}^{Fan-out} C_{IN,i}$$

(5)

The line load becomes a problem as the clock signal has to be transported a long distance. Long wires have high capacitive and resistive load. This effect is an increasing problem due to technology scaling. The dimensions and cross section of the lines are shrinking, but the line lengths are not decreasing accordingly. In order to get acceptable timing characteristics, several buffers might be required along long lines.

Inverters and buffers are also inserted to increase delay in a clock branch, exploiting the propagation delay of the buffer. This technique is used to lengthen short clock paths in order to balance the clock tree and reduce the clock skew.

Typically, a clock buffer consists of an even number of inverters. Hence, standalone inverters can be used in the clock tree similar to the buffers. The drawback of using inverters is, however, that the clock phase is inverted. The inverters must therefore consider edge dependent cells in the clock tree, e.g. registers, clock dividers and ICGs.

The selection of buffers and inverters is dependent on the technology's cell library. Typically, a range of sizes is available, from small and weak buffers to large buffers with high drive strength. In order to get good signal characteristics, the output resistance of the selected buffer should be much larger than the resistance of the driven net [7].

### 2.4.3 Clock Gating Cells

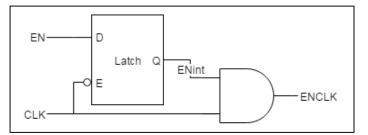

As previously mentioned, the switching activity in a clock tree is high as the clock signal toggles twice every cycle ( $\alpha = 2$ ). However, depending on the application, parts of the chip may not need the clock at a given point in time. In these inactive parts, it is desired to reduce the activity to  $\alpha = 0$ , and thereby eliminate the dynamic consumption. This is done with ICGs similar to the one shown in Figure 2.3. In this schematic, *CLK* and *ENCLK* are the input and gated output clock signals, respectively. The enable signal, *EN*, is set to logic 1 in order to enable propagation of the clock signal through the ICG. The internal signal *ENint* controls the output clock, and is latched while *CLK* is low, as shown in Table 2.1. This is done to avoid propagation of glitches from *EN* to *ENCLK*.

CLK

EN

ENint

0

0

0

0

1

1

1

ENint,prev

Table 2.1: Internal node *ENint* state table.

Figure 2.3: ICG schematic.

There are several different strategies of inserting the ICGs in the clock tree. This is presented in Section 2.5.

#### 2.4.4 Registers

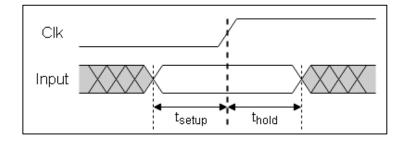

The registers are the sinks of the clock tree. These are sequential cells used to remember states of the system [8]. A commonly used register is the rising edge triggered D flip-flop. The input value of this flip-flop is sampled, stored and propagated to its output on the rising edge of the clock signal. For the sample to be correct, the input has to be stable for a setup time,  $t_{setup}$ , before the clock edge. In addition, the input has to remain stable for at least a hold time,  $t_{hold}$  after the clock edge. These timing requirements are illustrated in Figure 2.4. Violating the timing requirements can cause erroneous behaviour.

Figure 2.4: Hold and setup timing.

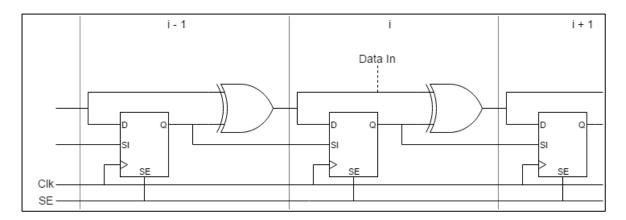

The registers come with various features. One of these is the scan feature, commonly used in design for test (DFT) [9]. With this feature, the registers can be organized in one or more scan chains. The chain is an alternative data path where the registers are connected as a long shift register with one input and output. The scan feature enables reading and writing to any register. This is a desirable feature in complex designs with several thousand registers.

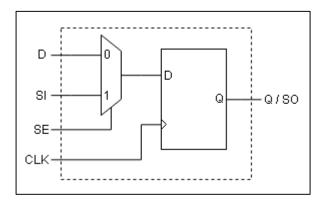

As Figure 2.5 shows, a single multiplexer is used to implement the scan functionality [9]. The scan-mode enable signal, SE, selects the register input source. When SE is logic 1, the scan input, SI, is selected. Otherwise, the data input, D, is selected and the register is behaving as regular. However, regular output, Q, is also used as the scan output, SO. In the scan chain, the scan output is connected directly to the scan input of the next register in the chain, as illustrated in Figure 2.6.

Figure 2.5: Scan register schematic.

The registers use the same clock signal for both regular and scan mode. However, an external source is typically used for the scan clock. The scan chains can contain registers from several clock domains, which gives a different clock structure than regular mode. Due to the short path in the scan chain, low skew is required in the scan clock to avoid hold time violations. Therefore, the clock system has to be optimized for both regular and scan mode.

Figure 2.6: Scan chain connection.

## 2.5 Clock Gating Strategies

There are several strategies when it comes to inserting the ICGs in the clock tree. Design tools are able reduce the dynamic power consumption by inserting clock gates in the leaf levels as explained in Section 2.5.1 and 2.5.2. However, as the clock tree itself consumes a lot of power, ICGs can also be placed closer to the root. These clock gates are used to disable entire modules as described in Section 2.5.3.

#### 2.5.1 Leaf-Level Clock Gating

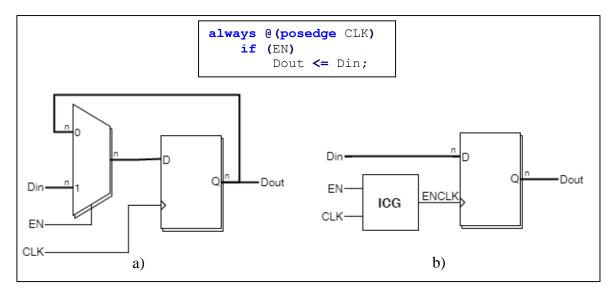

Many registers are implemented with code similar to the Verilog HDL code in Figure 2.7, and already have an enable signal. This is often implemented with multiplexers as illustrated in Figure 2.7a. With this solution, the n registers are updated every cycle, but only given the new input value when the enable signal is logic 1. However, updating the register consumes power independent of the value being new or old. Unnecessary updates should therefore be avoided.

Figure 2.7: Clock gating at leaf level.

This is done with the schematic presented in Figure 2.7b. The ICG cell disables the clock signal when the enable signal is logic 0. Therefore, the register is only updated when the enable signal is logic 1, thus reducing the power consumption. Depending on the bit width, n, this clock gating strategy may enable area reductions, as n multiplexers can be replaced by a single ICG cell. The savings, of both power and area, are also dependant on the register activity and technology. Testing done in a 180 µm technology by Pokhrel, shows that gating is neither beneficial with respect to power nor area, for n less than three [6] [10].

Clock gating at the leaf level can be done by design tools and does not change the logic functionality of the circuit. A drawback of this method is that it increases the length of the clock path.

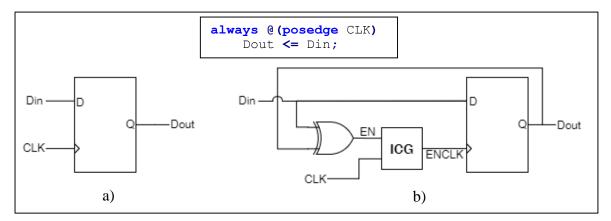

### 2.5.2 XOR Self-Gating

Many registers are implemented without the enable signal, as illustrated in Figure 2.8a. For these registers, the XOR self-gating technique can be used to gate the clock signal and reduce the dynamic power consumption [11]. This method is similar to the leaf-level strategy presented in the Section 2.5.1. However, as shown in Figure 2.8b, an enable signal is created by an XOR-gate. With this implementation, the clock signal is disabled while the data input remains unchanged, thus reducing the dynamic power consumption. The bit width for this technique is naturally limited to one register.

Figure 2.8: XOR self-gating.

In order to reduce the dynamic power consumption in a single register, an XOR-gate and an ICG cell has been added. This increases both the static power consumption and the area. For XOR self-gating to be beneficial, the reduction in dynamic power consumption has to be larger than the increased static consumption. It can therefore be suited for registers with high clock frequency, but low switching activity on the data input.

### 2.5.3 Module-Level Clock Gating

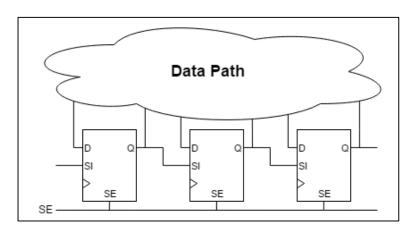

As mentioned, ICGs can be placed closer to the clock root in order to reduce the power consumption in the clock tree structure in addition to the registers. This is called module-level clock gating, as these clock gates can be used to disable the activity in large unused modules. A typical SoC for Bluetooth Smart consist of several different modules (CPU, Timers/Counters, DACs/ADCs, etc.), of which only a few are used at a given point in time. Disabling the clock signal to an unused module cancels the dynamic power consumption in the module's clock tree, registers and data path. Module-level clock gating has great power saving potential since up to 50 %, or even more, of the total dynamic power is consumed in the clock buffers [6].

The module-level clock gate can either be manually controlled by the program, or automatically controlled by the hardware. In a manual system, the clock gates are controlled by program code. Program lines are added to enable and disable the module's clock. Alternatively, an automated system can ensure that the clock is only enabled when the module is used and immediately turned off after its task is completed. This system requires some additional control logic, but simplifies the clock control for the programmer.

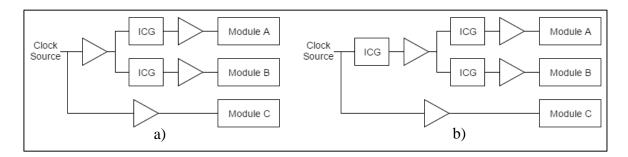

Figure 2.9: Module-level clock gating in a) one and b) two levels.

Figure 2.9 illustrates how module-level clock gating can be done. In Figure 2.9a, ICGs are inserted for modules A and B, while module C is not gated. In order to further reduce the power consumption, an additional level of clock gates has been added in Figure 2.9b. Depending on the scenario, larger parts of the clock tree to be disabled with multiple levels of clock gates. As shown in Figure 2.9b, the buffer driving the ICGs for Module A and B can be clock gated is both modules are inactive. However, adding additional levels of clock gates requires additional logic. In addition, the ICGs can cause imbalance in the clock tree.

# **3** Previous Work and Design Tools

This chapter presents relevant research in the topic of clock tree synthesis and clock gating. In addition, the tools used in this project are described.

## 3.1 Clock Tree Synthesis

Clock tree synthesis is a well-researched topic in continuous progress. The most common strategy is to minimize the clock skew. In this strategy, the clock tree is formed so that the clock edge arrives simultaneously for all sequential cells, i.e. zero skew. In order to do this, the sinks of the clock tree have to be clustered so that the load of the clock tree becomes balanced. Algorithms for clustering is addressed by [12, 13, 14, 15]. Most recent of these is the work by Shelar [15]. Shelar presents a power-aware clustering algorithm that uses a minimum-spanning tree metric to achieve low power consumption. Results on a 65 nm technology shows consistent reduction of the total clock tree capacitance by up to 21% compared to competitive approaches.

After the sinks have been clustered, the next step is to route the clock tree. Routing strategies for achieving low skew are addressed in [16, 17, 18].

As the clock complexity increases, minimizing the skew becomes difficult and expensive with respect to buffer area and power consumption. Therefore, an alternative strategy is to implement useful skew, a method of using the clock skew actively to meet timing requirements. Useful skew can be implemented to improve the performance, e.g. operating frequency [19, 20, 21]. By allowing some skew, timing violations in the critical data paths can be avoided at higher clock frequencies.

Alternatively, useful skew can be used to reduce the cost of the clock tree. Xi et al. [22] presents an algorithm that allows some negative skew (delayed clock edge arrival at the destination register), which gives a larger timing budget. Due to the large number of configurations, the algorithm uses the stochastic search method of simulated annealing to avoid being trapped in local minima. Experimental results show a power reduction of 12% to 20%, compared to previous methods, without any reduction in clock frequency.

Another approach based on useful skew is purposed by Ramachandran [23]. Instead of using a zero or bounded skew target, the arrival time requirements are derived from the sinks' timing constraints. The goal of this approach is to create a minimalistic clock tree and reduce the buffer count, thus reducing the power consumption.

## 3.2 Clock Gating Strategies

A recent survey by Pouiklis et al. [24] presents a spectrum of clock gating approaches. This survey presents both theoretical and practical considerations throughout the design process. Requirements, limitations and tool support have been examined for each step in the design process. In addition, an assessment of testing compatibility, such as scan clock functionality, is examined. Finally, clock gating results from other literature are presented and evaluated. The survey by Pouiklis et al. considers leaf-level clock gating only.

The literature and research on the topic of module-level clock gating is sparser than leaflevel clock gating. This lack of research can be explained by the fact that module-level clock gating is application specific. However, Bu et al. [25] present a novel module-level clock gating implementation of a CPU. First, an adaptive module-level clock-gating cell with the ability to automatically sense module activity is being created. This cell is then applied to reduce the power consumed during pipeline stalls and when modules such as FPUs and co-processors are idle. Simulations on a 65 nm technology show an average power reduction of 18% to 28%, with no impact on CPU performance and negligible area overhead [25].

In experiments by Suito et al. [26], low power techniques have been implemented on a multithreaded processor, where one technique is fine-grained module-level clock gating. In this experiment, the power consumption, chip temperature and timing overhead were examined. The total power consumption and temperature reduction of the implemented low power techniques, is 88% and 23%, respectively, while the timing overhead is up to 75  $\mu$ s. However, the timing overhead caused by the module-level clock gates is only 4  $\mu$ s.

## 3.3 Clock Tree Implementation in Synopsys® IC Compiler<sup>TM</sup>

The clock tree implementation can be done in Synopsys<sup>®</sup> IC Compiler<sup>TM</sup> with the *clock\_opt* command [11]. This command consists of the 12 steps listed below, where some are optional. All steps can also be done individually through separate commands.

- Clock tree synthesis: Building a violation free clock tree, as described in Section 3.3.1.

- 2. Clock tree optimization: Improving the clock skew, as described in Section 3.3.3.

- 3. Interclock delay balancing (Optional): Balancing the skew between a group of clocks.

- 4. Routing: Detailed routing of the clock nets.

- 5. Arrival time computation: Extracting values for resistance and capacitance in order to compute accurate arrival times.

- 6. Adjustment of I/O timing (Optional): Adjusting the input and output delays in order to match clock arrival times.

- 7. Power optimization (Optional): Performing a physical optimization of the ICGs, power-aware placement and leakage optimization.

- 8. Congestion reduction (Optional): Reducing congestions in order to improve the routability of scan nets.

- 9. Scan chain optimization (Optional): Reordering of the scan chain to reduce the number of buffer crossings in the chain.

- 10. Placement fixing: Fixing buffer and inverter placements.

- 11. Placement and timing optimization: Optimizing placement of registers and combinatorial logic, yet keeping the clock tree fixed.

- 12. Hold time violation fixing (Optional): Fixing register hold-time violations by manipulating the data paths, inserting buffers, etc.

This project focuses on the clock tree synthesis and optimization (steps 1 and 2), described in Sections 3.3.2 and 3.3.3, respectively. In order to perform these two steps exclusively, the *clock\_opt* command is given the *-only\_cts* and *-no\_clock\_route* arguments. The most important options for the clock tree synthesis and optimization are specified in Section 3.3.1.

## 3.3.1 Clock Tree Options

In addition to selecting the optional steps in the clock tree synthesis, constraints and optimization targets are set prior to synthesis. These options and their default values are listed by descending priority in Table 3.1. The options can be given values both globally and per clock.

| Priority  | Variable Name           | Default value |  |  |

|-----------|-------------------------|---------------|--|--|

| Design R  | Design Rule Constraints |               |  |  |

| 1         | max_capacitance         | 0.6 pF        |  |  |

| 2a        | max_transition          | 0.5 ns        |  |  |

| 2b        | leaf_max_transition     | "Unspecified" |  |  |

| 3         | max_fanout              | 2000          |  |  |

| Clock Tre | ee Timing Goals         |               |  |  |

| 4         | target_skew             | 0 ns          |  |  |

| 5         | target_early_delay      | 0 ns          |  |  |

Table 3.1: Clock tree synthesis options.

The design rule constraints set the maximum allowed values for the net capacitance, clock transition time and fan-out. For the transition time, the designer has the opportunity to set a separate constraint for the leaf-level nets (connected to the clock pin of the registers). If the maximum leaf transition time is not specified, the maximum transition time is used also for the leaf levels. This is the default behaviour. The skew target is used in the optimization process. When this target is met, the optimization ends. The target early delay specifies a minimum goal for the shortest clock path. This option can be used to match the delay in different clock trees.

In addition to the design rule constraints set by the user, the tool also considers constraints from the cell library and the design specification. The smallest value is chosen for max\_capacitance and max\_transition, while for max\_fanout, the user specified value is chosen.

It is also possible to select which cells to use in the clock tree synthesis and options. Three different selections needs to be specified. The first selection is the buffers and inverters available for insertion in the synthesis stage. The second selection is the delay buffers/inverters used to balance the delay of the branches. The third selection is the resizing list used for all cells in the clock tree (buffers, inverters, ICGs, multiplexers, etc.) resizing list. With these selections, it is possible to exclude cells with adverse effects, such as high current peaks and low drive strength.

### 3.3.2 Clock Tree Synthesis

The first step of the clock tree synthesis is an analysis of the available buffers and inverters. In this analysis, the positive and negative edge delays of the buffers are calculated. If the delay difference is too large, the buffer is excluded for use in the synthesis and optimization [27].

If the XOR self-gating methodology is enabled, clock gates are inserted in the leaf level. When these are inserted, the tool takes timing, power and clock-tree QoR into account. In order to determine whether the inserted ICG actually saves power, accurate switching activity annotations are required. XOR self-gating is only done for registers where the reduced dynamic power is greater than the increase in static power.

The next step is to prepare the clock tree for the synthesis. The existing clock cells are upsized to cells with higher drive strength. This is done to solve constraint violations

without inserting buffers, resulting in reduced tree depth and latency. In addition, the clock cells, including ICGs, are relocated if this can increase the QoR [11]. However, cells is not moved so that the functionality of the clock tree changes.

Finally, the clock tree is built to meet the constraints, while keeping the tree balanced and the clock skew minimized. As presented in Section 3.3.1, there are three clock tree constraints; maximum capacitance, maximum transition time and maximum fan-out. These constraints can be related, as a high fan-out net often has a high capacitance, and thereby reacts slowly. Therefore, the procedures to solve the violations are similar. Maximum capacitance violations and maximum fan-out violations are fixed by dividing the fan-out /load into smaller groups and drive these with individual buffers. When the fan-out is being dividing, it is important to maintain balance in the tree in order to minimize the clock skew.

There are two ways to fix transition time violations. Similar to the case of fan-out and capacitance violations, the fan-out driven net can be divided into smaller groups driven by individual buffers. This reduces the individual net loads, which gives faster reaction time and improved transition time. Alternatively, a larger buffer with higher drive strength can be used to reduce the transition time.

## 3.3.3 Clock Tree Optimization

The goal of the clock tree optimization is to minimize the clock skew to meet the target skew [11]. In order to do this, the tool can do the following, where all action are optional:

- Resize buffers/inverters

- Move buffers/inverters

- Resize clock tree cells (ICGs, multiplexers, etc.)

- Move clock tree cells

- Insert delay buffers

The optimization process stops when the skew target is reached. However, if the skew target is set very tight, the optimization might be stopped before the target is reached due to high buffer costs. This is controlled by the tool's internal cost function.

When the skew optimization process is completed, additional delay is inserted at the clock root to meet the target early delay. After this step, the shortest clock path should be greater than the specified target early delay. Since the default of this target is 0 ns, no root delay is inserted unless the target is increased by the user.

## 3.3.4 Logic Level Balancing

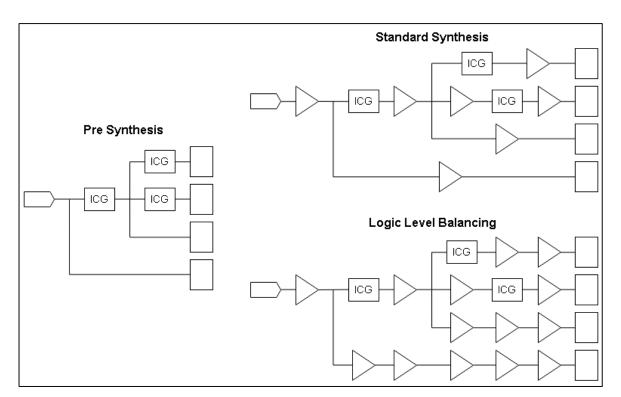

The logic level balancing feature builds the clock tree structure so that all sinks are placed at the same level of the clock tree [11]. This is illustrated in Figure 3.1. The clock tree structure prior to the synthesis is simple, with 0 to 2 cells between the clock source and registers. In a typical synthesis, buffers are inserted, increasing the amount of cells between the clock source and the registers to 2 to 6 cells. However, with logic level balancing, additional cells are inserted in the shorter branches so that there is an equal amount of cells between the clock source and every register.

Figure 3.1: Logic Level Balancing.

The logic level balancing feature provide a balanced clock tree with low path variation and is said to give the best clock skew [28]. The structure is also robust against process variations as the depth is identical for all sinks. However, as additional buffers are inserted, logic level balancing is typically more expensive with respect to buffer area and power consumption.

### 3.3.5 Guidelines

Synopsys® provides several application notes with guidelines and recommendations for the clock tree synthesis in Synopsys® IC Compiler<sup>™</sup> [27, 28, 29]. Some of the most important recommendations are listed below:

- Remove any existing buffers or inverters from the clock tree prior to the synthesis. These will be treated as balancing points and can affect the clock tree QoR [28].

- Prior to the synthesis, run the *check\_clock\_tree* command and solve any reported issues [29].

- Use buffers/inverters with minimal difference in their rising and falling edge delays [27, 29]. Unbalanced buffers might cause bad skew.

- Use default synthesis constraints as tightening the constraints will degrade the synthesis results considerably [27, 29]. Tight constraints can cause an excessive use of buffers and increase the clock tree power consumption.

- Use a naming convention for buffers/inverters inserted during the different steps of the synthesis [27]. This makes it easier to debug any synthesis issue.

## 3.4 Power Estimation in Synopsys® IC Compiler<sup>TM</sup>

In this project, power estimation is done in Synopsys® IC Compiler<sup>TM</sup>. This tool is calculating dynamic and static power consumption based on the static (i.e. time independent and averaged) switching activity parameters. These consist of the static probability and the toggle rate, and are denoted for each net in the design. The static probability is a floating point number between 0 and 1, and represents the percentage of the time the net is at logic 1. The toggle rate describes the number of "0-to-1" and "1-to-0" transitions the net is doing per nanosecond. E.g. a 1 MHz clock signal will have a static probability of 0.5 and toggle rate of  $0.002 \text{ ns}^{-1}$ .

With the denoted activity parameters, power is calculated using data from the cell library. The internal cell power and static power are calculated using the switching activity of the input nets and power data for the specific cell, obtained from the library. The switching power for a net,  $P_{SW,net}$ , is derived from Equation (1) in Section 2.3.1. The activity factor,  $\alpha f_{CLK}$ , is equal to the net's toggle rate,  $TR_{net}$ , and  $C_{net}$  is the total net capacitance. This gives the resulting formulas presented in Equation (6).

$$\alpha f_{CLK} = TR_{net} [ns^{-1}]$$

$$P_{SW,net} = \frac{TR_{net}}{2} C_{net} V_{DD}^2$$

(6)

The switching activity of a net can be denoted in three different ways. Primarily, the activity can be set to a specified value, by using tool commands or loading activity results from RTL-simulations, or similar. If the activity of a net is not set, the tool will try to calculate the activity using the functional description from the driving cells. If the net does not have any drivers, i.e. an input net, the net will be given a default activity specified by the variables *power\_default\_toggle\_rate* and *power\_default\_static\_probability*.

In order to analyse the design in a specific power mode, activity data for this mode is typically loaded from simulation results. Alternatively, the designer sets the switching activity of the clock sources and input pins. Activity can also be set to selected nets in order to put the design in a specified mode, before the tool propagates the activity to the rest of the design.

### 3.5 Clock Tree Analysis Tool

In order to evaluate the clock tree performance, an analysis tool created in a previous project has been used. The development of the tool is presented in detail in the project report [1]. The tool extracts data from a set of synthesis and power reports, and stores the data in a .csv file. The .csv data file is dynamically linked to a Microsoft Excel sheet, which presents the data in an informative manner. New synthesis data can easily be added to the tool by appending new lines to the .csv file. To display the new data, the sheet has to be refreshed.

The data presented by the tool are separated into the following categories:

- Dashboard: Links to every parameter for easy navigation.

- Summary: Table of the most important clock tree parameters. Similar to the Synopsys® IC Compiler<sup>™</sup> clock tree summary, but extended with efficiency ratios and power figures.

- Additional filters: Filters the results by data set, clock name, design name, scenario and clock tree settings.

- Design rule check: The number of synthesis constraint violations.

- Clock tree cells: The number of cells of the different of clock tree cell types and the efficiency ratio "sinks per buffer".

- Level information: The post synthesis level information of the clock tree, including how sinks, buffers and ICGs are distributed in the clock tree levels.

- Buffer area: Clock tree buffer area statistics and the ratio of "sinks per buffer area".

- Timing: Maximum global clock skew and longest clock path.

- Power activity 0-100%: Clock tree power figures from 0% to 100% activity as presented in Section 3.5.1.

- Power Scenario 1 and 2: Clock tree power figures for two optional power scenarios. In this project, one scenario has been used.

In this project, the most important feature of the tool is the ability to extract data from reports and make them available in Excel Pivot Tables. This simplifies the creation of data tables and plots. This also makes it easier to handle the large data collection.

## 3.5.1 Activity-Based Power Estimation

The activity-based power estimation scheme was created to analyse the power consumption in clock-gated trees without using results from simulations. Instead of analysing specific scenarios, in this scheme, the clock tree power consumption is estimated based on five steps of activity; 0%, 25%, 50%, 75% and 100% activity. These activity parameters determine the static probability of the clock gates' enable signal. In other words, 0 % activity means that all ICGs are disabled, and that the clock tree operates in its lowest power mode. However, at 100 % activity, all ICGs are enabled and the worst-case power consumption is estimated.

The activity parameter is set directly on the enable pin of all ICGs in the design. The idea behind this method is that the functional description of the ICG will lead to correct propagation of switching activity during the power analysis. Alternatively, the activity can be set directly on the output of the ICGs. This method can give better accuracy, but can also become very complicated for designs with multiple layers of ICGs and clock dividers. Hence, setting the enable pin is preferred.

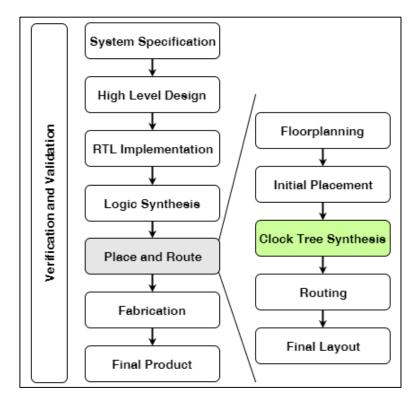

# 4 Methodology

In this project, only the clock-tree synthesis stage of the design process, highlighted in Figure 4.1, is considered. This means that no high level or RTL work have been done in this project. Instead, the two test design, presented in Section 4.1, have been provided in a post initial-placement state. From this state, the clock trees have been synthesized using Synopsys® IC Compiler<sup>TM</sup> tool, as presented in Section 3.3. The scan functionality has not been considered in this project. Therefore, the designs have not been synthesized in the scan mode.

Figure 4.1: SoC design flow.

In this project, the clock skew, buffer area and power consumption have been considered the most important parameters of the clock tree. The skew and the buffer area are obtained from tool generated synthesis reports, while the power consumption is estimated according to the description in Section 4.2.

The test and experiments in this project is divided into an exploration of the clock tree synthesis functionality of Synopsys® IC Compiler<sup>™</sup>, presented in Chapter 5, and a multi-level module-level clock gating experiment, presented in Chapter 6. In both chapters, the most important results are presented and discussed.

## 4.1 Test Designs

In this project, two designs in the same sub-100 nm technology have been examined. In order to test how the design size and complexity affect the clock tree synthesis, a simple artificial test design has been generated as presented in Section 4.1.1. A benefit of the artificial design is reduced synthesis time. Therefore, the artificial design has been used to test the functionality of the synthesis tool. Experiences on the artificial design has then been applied on a real Bluetooth Smart design, presented in Section 4.1.2. In addition, multilevel module-level clock gating has been tested on the real design.

### 4.1.1 Generated Test Design