# Design and Testing of a Race Car Inverter

Anders Holter Bjørkto Simen August Tinderholt

Master of Science in Cybernetics and Robotics

Submission date: July 2016

Supervisor: Bjørn B. Larsen, IET Co-supervisor: Amund Skavhaug, ITK

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## Problem description

In 2016, Revolve NTNU's fifth car will represent the team in Formula Student. Formula Student is a competition for engineering students, where teams design and build racing cars. The cars are evaluated in a series of tests evaluating performance and engineering design decisions.

For this season, Revolve wants to develop a self-made inverter, with the goal of increasing the performance of the four-wheel driven car. The power systems and motor control shall be implemented and integrated with the other electronic and tractive systems of the car.

During the fall of 2015, the candidates compiled a prestudy on the design of such a system. This work shall be continued by:

- 1. Revising solutions from the prestudy

- 2. Develop further requirements for the system

- 3. Design and manufacture hardware design prototypes of the system modules

- 4. Develop the necessary software of basic system functionality

- 5. If time permits, extend the performance of the system

- 6. Perform testing of the implemented system

- 7. Evaluate the final system with regards to suitability, quality and performance

#### Abstract

Electric drivetrains have become more prevalent in high performance motorsport communities. With high power to weight ratios and the ability to recover energy when braking, they are able to increase performance for racing cars. Such a machine needs to be powered and controlled. An inverter is the connecting interface between the power source and the motor performing this task. With the amount of energy and power needed to drive a racing car, safety and reliable operation is paramount.

This Master's Thesis will present the design, implementation and testing of a two-level voltage source inverter and motor control system. The target vehicle is driven on all four wheels, so a four channel inverter system is needed. The target motor of the car is a three-phase permanent magnet synchronous motor. The VSI presented is based on Silicon-Carbide Metal Oxide Semiconductor Field Effect Transistors (SiC MOSFETs).

The motor control system will be targeted at Atmel microcontrollers, for physical implementation in the car. Furthermore, base development for a System-on-Chip(SoC) will be done, for further development at later stages. Switching the motor control system onto a more powerful SoC will enable more precise control of the motor.

#### Sammendrag

Elektriske drivsystemer har gjennom de siste årene blitt vanlige i racing-miljøet. Høye kraft til vekt-rater samt muligheten for regenerering av energi ved bremsing, gjør at elektriske motorer kan brukes til å øke ytelsen til racerbiler. En slik maskin trenger energi og må kontrolleres, omformeren er koblingsleddet mellom energikilden og motoren som utfører dette. Med nok energi og effekt til å drive en racerbil, er sikkerhet og pålitelighet viktig.

Denne Masteroppgaven vil presentere designarbeid, implementasjon, og testing av et to-nivås spenningskildeomformer- og motorkontrollsystem. Systemet er tiltenkt brukt på en bil med firehjulstrekk via fire uavhengige motorer, så en fire-kanals omformer er ønsket. Motorene som skal drives er tre-fase permanentmagnet synkronmotorer, og inverteren vil være basert på Silisiumkarbid MOSFET-transistorer.

Motorkontrollsystemet vil i hovedsak bli utviklet for en Atmel mikrokontroller, for den praktiske implementasjonen i bilen. Grunnleggende arbeid vil også bli gjennomført på et enbrkkesystem (SoC) for videre arbeid i senere steg av utviklingen av systemet. Bruk av et enbrikkesystem vil tillate bruk av mer avanserte kontrollalgoritmer for mer korrekt styring av motoren.

# Acknowledgements

We want to thank Revolve NTNU for trusting us with this project. Without financial support and know-how, this project would not have been possible, we therefore want to thank Revolve's sponsors for supplying us with components, PCB production and experience. For helping structuring our report, and keeping us focused, we want to thank our supervisors, Bjørn B. Larsen and Amund Skavhaug.

# Contents

| 1 | Inti           | roduction                       | 8          |

|---|----------------|---------------------------------|------------|

|   | 1.1            | Formula Student                 | 8          |

|   | 1.2            | Revolve NTNU                    | 9          |

|   | 1.3            | Motivation                      | 10         |

|   | 1.4            | The electrical drivetrain       | 11         |

|   |                | 1.4.1 Battery accumulator       | 12         |

|   |                | 1.4.2 Voltage source inverter   | 12         |

|   |                | 1.4.3 Permanent-magnet motor    | 14         |

| 2 | Mo             | tor control theory              | <b>1</b> 5 |

|   | 2.1            | Basic equations                 | 15         |

|   | 2.2            | Field-Oriented Control          | 18         |

|   | 2.3            | Advanced Control Methods        | 19         |

|   |                | 2.3.1 Maximum Torque Per Ampere | 20         |

|   |                | 2.3.2 Field Weakening Control   | 20         |

|   | 2.4            | System modelling                | 24         |

|   |                | 2.4.1 Motor Model               | 25         |

|   |                | 2.4.2 Controller                | 26         |

|   |                | 2.4.3 Field Weakening           | 26         |

| 3 | $\mathbf{Sys}$ | tem Requirements 2              | 28         |

|   | 3.1            | Power system                    | 28         |

|   | 3.2            | Digital Interface               | 29         |

|   | 3.3            | Physical Interface              | 29         |

|   | 3.4            | Control system                  | 30         |

|   | 3.5            | Safety features                 | 30         |

|   | 3.6            | System Architecture             | 31         |

| 4 | Har            | rdware design 3                 | 33         |

|   | 4.1            | Current sensors                 | 33         |

|   | 4 2            | Encoder                         | 35         |

|      | 4.2.1   | Endat                             | 35 |

|------|---------|-----------------------------------|----|

|      | 4.2.2   | Altera MAX10                      | 38 |

| 4.3  | Contr   | ol Card and Insert                | 40 |

|      | 4.3.1   | Specifications                    | 40 |

|      | 4.3.2   | Design                            | 41 |

|      | 4.3.3   | Insert                            | 45 |

|      | 4.3.4   | Issues and experiences            | 45 |

| 4.4  | Power   | card                              | 46 |

|      | 4.4.1   | Requirements                      | 47 |

|      | 4.4.2   | Simulation                        | 47 |

|      | 4.4.3   | Experiences and issues            | 49 |

|      | 4.4.4   | Future work                       | 50 |

| 4.5  | Gate    | driver card                       | 53 |

|      | 4.5.1   | Specifications                    | 53 |

|      | 4.5.2   | Design                            | 56 |

|      | 4.5.3   | Issues and Experiences            | 57 |

|      | 4.5.4   | Future work                       | 58 |

|      | 4.5.5   | Casing design                     | 59 |

| 4.6  | System  | m on Chip                         | 60 |

|      | 4.6.1   | System on Modules                 | 60 |

|      | 4.6.2   | Using a SoC in the control system | 61 |

|      | 4.6.3   | Manufacturer choice               | 61 |

|      | 4.6.4   | A comparison of tools             | 62 |

| Soft | tware I | Design                            | 65 |

| 5.1  |         | 1 code                            | 65 |

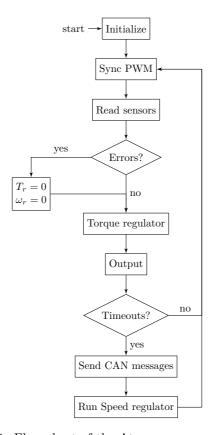

|      | 5.1.1   | Flow Control and OS               | 67 |

|      | 5.1.2   | Drivers and modules               | 70 |

|      | 5.1.3   | Future Work                       | 76 |

| 5.2  | Atme    | ga SW                             | 77 |

|      | 5.2.1   | Safety checks                     | 77 |

|      | 5.2.2   | Program                           | 77 |

| 5.3  | Zynq    | software                          | 81 |

|      | 5.3.1   | Hardware platform                 | 81 |

|      | 5.3.2   | Development hardware platform     | 84 |

|      | 5.3.3   | Future work                       | 87 |

| 6                         | Uni         | t Tests                | 88  |

|---------------------------|-------------|------------------------|-----|

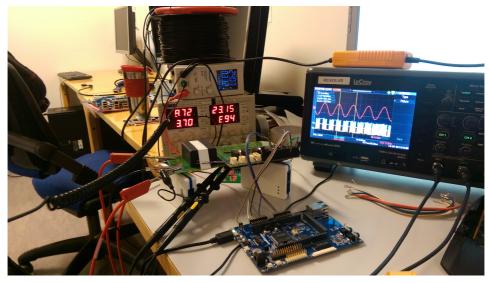

|                           | 6.1         | Gate Drivers           | 88  |

|                           | 6.2         | Power Stage            | 90  |

|                           | 6.3         | DC Voltage Measurement | 92  |

|                           | 6.4         | Current measurement    | 94  |

|                           | 6.5         | Motor Drive tests      | 94  |

|                           | 6.6         | Testing Accident       | 96  |

| 7                         | Fut         | ure Work               | 98  |

| 8                         | Con         | nclusion               | 100 |

| $\mathbf{A}_{\mathbf{J}}$ | ppen        | dices                  |     |

| A                         | Sou         | rce Code               | i   |

|                           | <b>A.</b> 1 | MAX10 encoder project  | i   |

|                           | A.2         | Atsam code             | i   |

|                           | A.3         | Atmega code            | i   |

|                           | A.4         | Zynq project           | i   |

| В                         | Boa         | ard Design             | iii |

# List of Figures

| 1.1  | Contestants at the 2015 FS Austria competition                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Revolve 2016 team after the reveal of Gnist $\dots \dots \dots$ |

| 1.3  | The electrical drivetrain [15] $\dots \dots \dots$              |

| 1.4  | Three-phase alternating current waveforms [15] $\dots \dots 15$                                                                                                 |

| 1.5  | Two-level VSI structure[15]                                                                                                                                     |

| 2.1  | ABC model of a Permanent Magnet Synchronous Motor 17                                                                                                            |

| 2.2  | DQ model of a Permanent Magnet Synchronous Motor                                                                                                                |

| 2.3  | Flow diagram of a simple FOC inverter                                                                                                                           |

| 2.4  | FOC parameter curves                                                                                                                                            |

| 2.5  | The torque vs speed plot of an AMK DD5 motor [1] $\dots \dots 22$                                                                                               |

| 2.6  | State diagram of the proposed voltage-follower FW algorithm $23$                                                                                                |

| 2.7  | D and Q axis models, from page 328 of [13] $\dots \dots 25$                                                                                                     |

| 2.8  | Motor model                                                                                                                                                     |

| 2.9  | Simulink controller model overview                                                                                                                              |

| 2.10 | Field weakening approximation                                                                                                                                   |

| 4.1  | Motor's internal wye connection                                                                                                                                 |

| 4.2  | A closed loop hall effect sensor $\dots \dots \dots$            |

| 4.3  | The EnDat serial protocol format. From page 6 in [7] $\dots 36$                                                                                                 |

| 4.4  | The SSC emulating a bidirectional serial protocol. From page 1065                                                                                               |

|      | of the Atsam E70N21 data<br>sheet [2] $\dots \dots \dots \dots 36$                                                                                              |

| 4.5  | The final block diagram of the encoder communication system $$ $$ 39                                                                                            |

| 4.6  | Inverter control card with Atsam insert                                                                                                                         |

| 4.7  | Inverter control card overview                                                                                                                                  |

| 4.9  | ECU and shutdown header                                                                                                                                         |

| 4.8  | 3.3V regulator                                                                                                                                                  |

| 4.10 | Voltage divider                                                                                                                                                 |

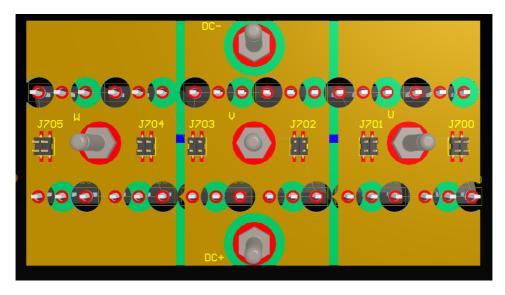

| 4.11 | The final Power PCB design                                                                                                                                      |

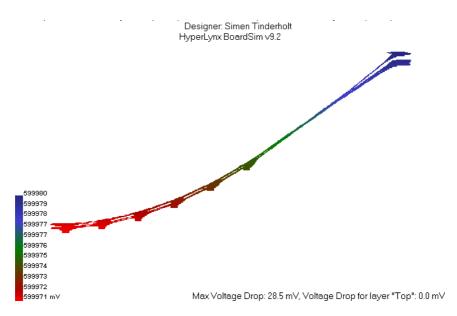

| 4.12 | Voltage drop in DC+ bus with six layers of 2Oz copper weight $$ 48                                                                                              |

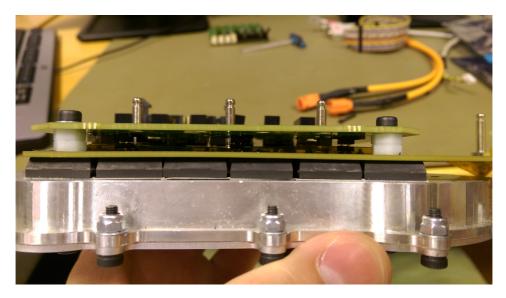

| 4.13 | Power Board mounted on the heat sink, transistors in between 50                                                                                                 |

| 4.14 | 3D image of revised Power PCB showing three phase conductors on   |     |

|------|-------------------------------------------------------------------|-----|

|      | top, and lower layers with DC conductors beneath                  | 51  |

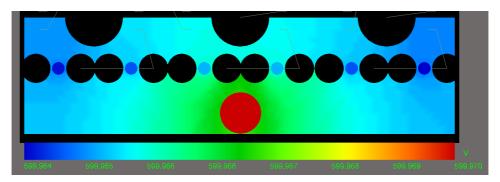

| 4.15 | Simulation results from Altium PDN analysis tool                  | 52  |

| 4.16 | Gate driver and Power PCB assembly in Solidworks                  | 53  |

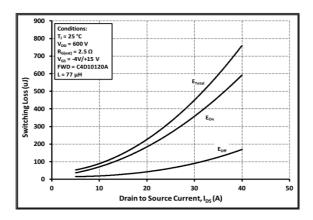

| 4.17 | Clamped Inductive Switching Energy vs. Drain Current ( $V_{DD}$ = |     |

|      | 600V) from [22]                                                   | 54  |

| 4.18 | Gate driver 4mm isolation zones marked in silk                    | 55  |

| 4.19 | Gate driver output filter                                         | 55  |

| 4.20 | Gate driver card, first (right) and last (left) revision          | 55  |

| 4.21 | Optocoupler schematic drawing                                     | 58  |

| 4.22 | The VSIs mounted inside the casing                                | 59  |

| 4.23 | Block diagram style in Vivado (a) and Quartus (b)                 | 63  |

| 5.1  | Flow chart of the Atsam processor program                         | 66  |

| 5.2  | DMA datastructure                                                 | 73  |

| 5.3  | Proposed hardware threshold guard using ADC comparators and       |     |

|      | timer counters                                                    | 76  |

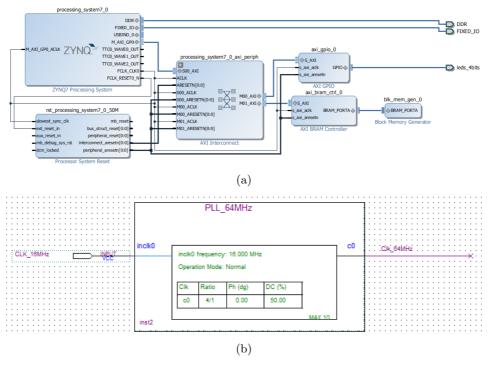

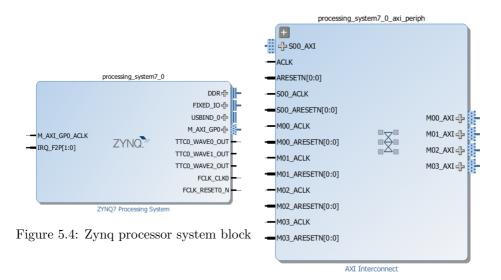

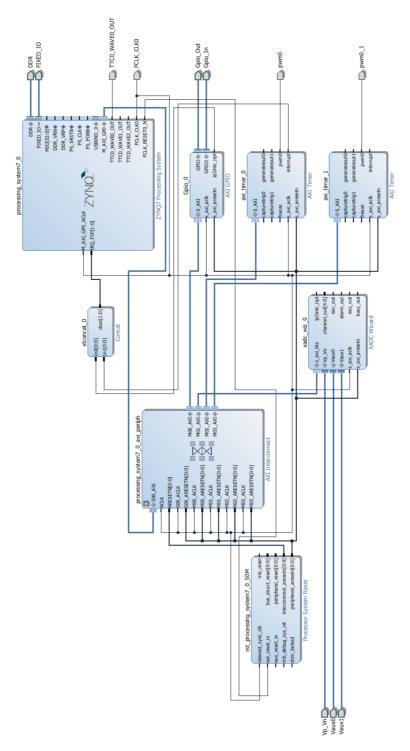

| 5.4  | Zynq processor system block                                       | 82  |

| 5.5  | AXI interconnect block                                            | 82  |

| 5.6  | AXI GPIO block                                                    | 82  |

| 5.7  | The package view in Vivado                                        | 83  |

| 5.8  | Test hardware platform                                            | 85  |

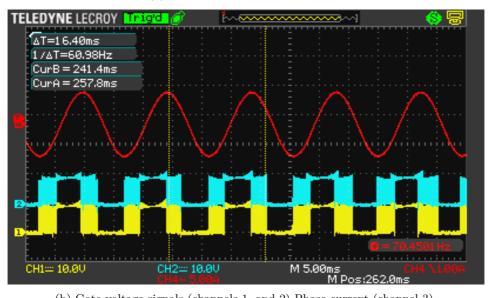

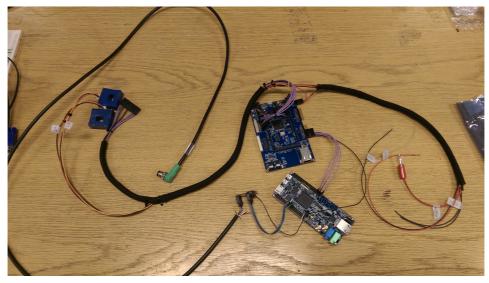

| 6.1  | Gate driver test setup                                            | 89  |

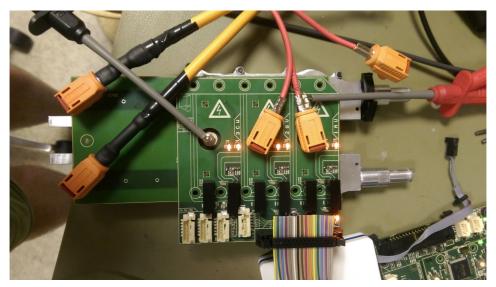

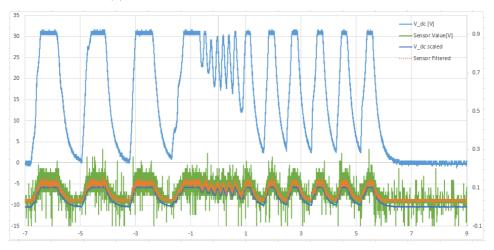

| 6.2  | Power stage test setup                                            | 91  |

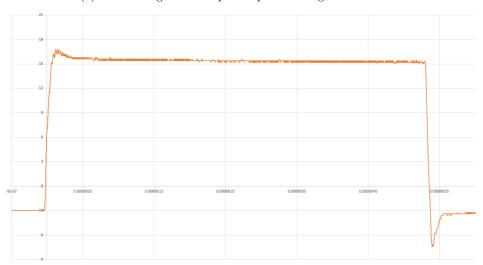

| 6.3  | DC voltage measurement tests                                      | 93  |

| 6.4  | Motor drive test setup $\dots$                                    | 95  |

| 6.5  | Damages after overcurrent incident. Scorching can be seen near    |     |

|      | J702, above phase V                                               | 97  |

| 8 1  | The finished inverter system during testing                       | 100 |

# List of Tables

| 1.1 | Formula Student competition evaluation                          | 9   |

|-----|-----------------------------------------------------------------|-----|

| 1.2 | AMK motor characteristics[1]                                    | 14  |

| 2.1 | Choice matrix for field weakening calculation algorithms        | 23  |

| 4.1 | Current sensor requirements                                     | 34  |

| 4.2 | Current sensor core data, LA 150-Pweight with adaptor PCB $\ .$ | 34  |

| 4.3 | Compilation restults of the MAX10                               | 38  |

| 4.4 | Voltage drop and power loss in DC+ rail at 20A                  | 47  |

| 4.5 | DC/DC Converter data                                            | 56  |

| 5.1 | Inverter Control Tasks, sorted by decreasing priority           | 67  |

| 5.2 | Error lines from Atmega to each Atsam                           | 77  |

| 5.3 | ADC and sensor mapping                                          | 79  |

| 8.1 | Comparative specifications of the AMK and R16 inverters         | 100 |

# Abbreviations

4WD : Four-wheel drive AC : Alternating current

ADC : Analog-to-digital converter AIR : ccumulator isolation relay

ASIC : Application specific integrated circuit

BMS : Battery managament system CAN : Controller area network

DC : Direct current

ECU : Engine control unit EV : Electric vehicle

FPGA : Field-programmable gate array

FS : Formula Student FSAE : Formula SAE

GLV : Grounded low voltage

HW : Hardware

IC : Internal combustion

IGBT : Isolated gate bipolar transistor

MOSFET : Metal oxide semiconductor field effect transistor

NTC : Negative temperature coefficient

PCB : Printed circuit board

PL : Programmable logic

PM : Permanent magnet

PWM : Pulse-width modulation

SAE : Society of Automotive Engineers

SiC : Silicon-carbide

SoC : System-on-chip

SoM : System-on-module

SPI : Serial peripheral interface

SW : Software

TV : Torque vectoring

VSI : Voltage source inverter

# 1. Introduction

### 1.1 Formula Student

Formula Student is a series of annual competitions where engineering students from all over the world compete with one-seat racing cars. The competitions started as SAE (Society of Automotive Engineers) Mini Indy at the University of Houston in 1979, but today they include a number of spin-off events all over the world. Fully electric vehicles (EVs) were introduced for the first time in Formula Student in 2010, and competes in a class separate from the internal combustion (IC) vehicles. However, in Formula Student UK, both EVs and IC vehicles compete in the same class, resulting in EV teams winning the event the last years.

Figure 1.1: Contestants at the 2015 FS Austria competition

The events are divided into eight different challenges, where a total of 1000 points can be obtained by each team. The team with the highest overall score wins the event. The total score is distributed, as shown in Table 1.1, between dynamic and static events. The static events are presentation, engineering design and cost analysis, and the goal of these events is to differentiate teams on the basis of planning, conceptual work, design, cost and general engineering practice.

| Static events  | Business presentation   | 75   |

|----------------|-------------------------|------|

|                | Cost and sustainability | 100  |

|                | Engineering Design      | 150  |

| Dynamic events | Skid-pad                | 50   |

|                | Acceleration            | 75   |

|                | Fuel Economy            | 100  |

|                | Autocross               | 150  |

|                | Endurance               | 300  |

| Total score    |                         | 1000 |

Table 1.1: Formula Student competition evaluation

The dynamic events are acceleration, skid-pad, autocross, fuel economy and endurance. The goal of the acceleration event is to drive 75 meters as fast as possible, from a standing start. The skid-pad event is a four-lap figure-of-eight course, testing the car's cornering abilities. In autocross, the vehicle's maneuverability and handling are tested at a tight track with sharp turns, to be completed as fast as possible. The endurance event evaluates the overall performance, and tests durability and reliability of the vehicle. It is a single 22km race, with driver change half way. This is one of the most important events both because it gives the most points, but also because it is the hardest test for both the car and the drivers. Fuel efficiency score is given in the same event, based on readings from an energy meter mounted in the car.

#### 1.2 Revolve NTNU

Revolve NTNU is a racing team representing the Norwegian University of Science and Technology in the Formula Student competition. The team is an independent student organization, who works on the project of building a new racing car from scratch every year.

Revolve was founded in 2010, and the team's first entry to the Formula Student competition was in 2012 with the internal combustion car KA Borealis R. The team was awarded the "Best newcomer award" and finished at 17<sup>th</sup> place overall in the UK. KA Aquilo R, the following year's car, made it to 16<sup>th</sup> place in the same

competition. Revolve's first fully electric vehicle was designed for the 2014 season, KOG Arctos R. With this car, the team finished at  $8^{\rm th}$  place in the UK. Revolve's 2015 electric car, Vilje, achieved a  $3^{\rm rd}$  place in engineering design in the UK and a  $4^{\rm th}$  overall in Formula Student Austria.

The 2016 car is called Gnist, and will participate in the Formula Student events at Silverstone in the UK, the Red Bull Ring in Austria and at Hockenheim in Germany. Gnist is the teams first four-wheel driven car, and with this new powerhouse and great results from last year, the goals are driven high, aiming for the top.

Figure 1.2: Revolve 2016 team after the reveal of Gnist

### 1.3 Motivation

A fully electric drivetrain has a distinct advantage to IC engines in the Formula Student competitions. The high torque and fast response of an EV fits well with the short tracks with tight and fast turns of the competition. The advantages does come at some cost, however. The battery accumulator of the electrical drivetrain is heavy, and there is added weight and complexity in the motor control system.

Revolve NTNU has been steadily improving their result every year since the first entry in 2012. This is a trend we want to continue, and the 2016 car therefore sports four-wheel drive (4WD). Each wheel is attached to a motor, each requiring a voltage source inverter to operate. In such a system, the control systems are more complex, and require more from the engine control unit (ECU). A 4WD solution adds considerable weight to the vehicle, due to multiple motors, power electronics and cooling circuitry. However, a 4WD system maximizes the total traction of the vehicle, and better utilizes regenerative braking. Individual control of four motors also allow for the implementation of torque vectoring (TV). A good TV algorithm distributes the torque between the four wheels, to give optimal traction and regenerative braking abilities. It also eliminates the need for a mechanical differential, reducing weight and increasing the level of control the driver has over the vehicle.

AMK has an inverter system that is widely used in the Formula Student competition. This system has also been considered by Revolve for the 2016 car, and it has been found that it is one of the best off the shelf solutions available. However, this inverter solution is large and heavy. In an acceleration and turning-focused competition like FSAE, weight is an important success parameter for any vehicle. Early estimates show that the inverter from AMK will weigh more than 7kg. In addition, the large form factor of the AMK inverter is difficult to position in the monocoque, and will be difficult to access when mounted in the car, should it be needed. The goal is to design an inverter that is an improvement over AMK's off the shelf solution. The main parameters that will be sought to be improved are weight, power efficiency and response time.

#### 1.4 The electrical drivetrain

The teams competing in Formula Student are allowed to choose between internal combustion vehicles and fully electrical vehicles, as long as the vehicle complies with the corresponding rule set in the FSAE rules[16]. Both combustion and electric cars are power limited to ensure a safe competition. For electric vehicles, the limitation is set to a maximum voltage of 600V and a maximum power draw of 80kW from the battery accumulator.

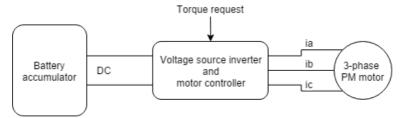

The electrical drivetrain is the core of any electric vehicle, and consists of three main parts: The battery accumulator, the voltage source inverter and the motor.

In Revolve's 2016 car, a three-phase permanent magnet (PM) motor is mounted on the hub of each wheel, for a four-wheel drive.

Figure 1.3: The electrical drivetrain[15]

#### 1.4.1 Battery accumulator

The battery accumulator stores the energy for driving the vehicle. It consists of 288 battery cells , in 2 cells in parallel, and 144 144 in series, giving a nominal accumulator voltage of  $550~\rm V$  and a capacity of about  $7.45~\rm kWh$ . While each single cell is lightweight, the battery accumulator is the single heaviest part of the vehicle, weighing more than  $45~\rm kg$ .

The battery cells needs to be monitored to make sure the individual cell voltages and temperatures are within safe operating ranges. The battery management system (BMS) is responsible for this. If the BMS detects a cell voltage outside the safe range, it shuts down the tractive system through the accumulator isolation relays (AIRs), two DC relays, one connected in series with each battery pole. These open on command from the BMS, or if the shutdown circuit is opened. The shutdown circuit traverses most of the car, and is activated if any of the safety systems detect an error or a fault.

## 1.4.2 Voltage source inverter

The voltage source inverter (VSI, or simply inverter) connects the battery accumulator to the three-phase PM motor. The VSI modulates the three-phase current driving the PM motors. The amplitude and frequency of the currents are determined by the motor controller, based on a torque request from the ECU.

The electromagnetic torque of a permanent magnet motor is determined from the permanent-magnet flux, the number of pole pairs and the stator current, as in

#### Equation 1.2.

$$\begin{bmatrix} i_a(t) \\ i_b(t) \\ i_c(t) \end{bmatrix} = I_s \cdot \begin{bmatrix} \sin(\omega \cdot t) \\ \sin(\omega \cdot t - \frac{2\pi}{3}) \\ \sin(\omega \cdot t - \frac{4\pi}{3}) \end{bmatrix}$$

(1.1)

$$T_e = \frac{3}{2}P \cdot \varphi_m \cdot I_s \tag{1.2}$$

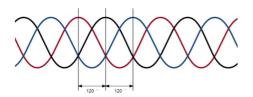

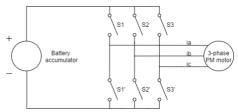

We can see From Equation 1.1 that a three-phase PM motor produces torque from three phases of sinusoidal current waveforms such as in Figure 1.4. The torque provided by the PM motor is controlled by changing the amplitude and frequency of the stator current waveforms. This is done by high frequency switching of the transistors in each phase leg in Figure 1.5. The amplitude determines the motor power, while the frequency is proportional to the speed of the motor. The task of the motor controller is to control the switches of the VSI in such a way that the amplitude and frequency corresponds to the driver's requested torque.

A two-level VSI such as the one in Figure 1.5 is the most widely used structure for smaller scale systems. It is compact, lightweight and have relatively good performance. Higher performance can be achieved with multilevel VSIs, where the DC voltage is divided into multiple levels. This will reduce losses in the motor, but the drawback is the rapidly increasing size: a three-level VSI requires 12 transistors, instead of only 6 for a two-level variant. Thus, it was early decided on a two-level system, due to easier implementation of the control system, and low weight being one of the main focuses for this car.

Figure 1.4: Three-phase alternating current waveforms[15]

Figure 1.5: Two-level VSI structure [15]

#### 1.4.3 Permanent-magnet motor

The permanent magnet (PM) synchronous motor is the electric machine with the highest torque-to-weight ratio, and therefore the most suitable for a low weight, high power race car. While expensive, the additional cost compared to simpler, weaker motor solutions can easily be justified by the higher performance of the PM motor.

This season, AMK's DD5-14-10-POW is the chosen motor. Its most important characteristics are listed in Table 1.2. The high power and low weight makes it ideal for a FS four-wheel drive car.

| P <sub>n</sub>        | 12.3 kW                                                                                    |

|-----------------------|--------------------------------------------------------------------------------------------|

| $M_{max}$             | 21 Nm                                                                                      |

| $I_{max}$             | $100 A_{RMS}$                                                                              |

| N <sub>n</sub>        | 12000 rpm                                                                                  |

| $N_0$                 | 18617 rpm                                                                                  |

| $N_{max}$             | 20000 rpm                                                                                  |

| P                     | 10                                                                                         |

| $L_{\rm d}/L_{\rm q}$ | $0.44~{ m mH} \ / \ 0.54~{ m mH}$                                                          |

| m                     | 3.55 kg                                                                                    |

|                       | $\begin{array}{c} M_{max} \\ I_{max} \\ N_n \\ N_0 \\ N_{max} \\ P \\ L_d/L_q \end{array}$ |

Table 1.2: AMK motor characteristics[1]

# 2. Motor control theory

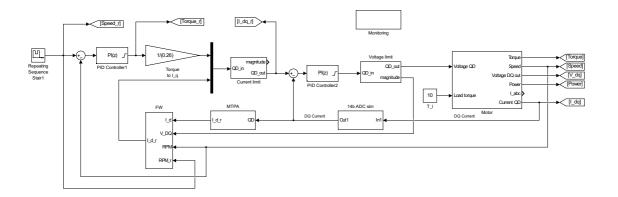

In this chapter, the mathematical basis for the implemented control system will be presented. Field Oriented Control theory and the relevant expansions will be explored, and a simple simulink model designed for testing the effect of different systems will be presented.

## 2.1 Basic equations

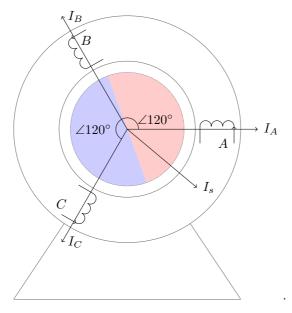

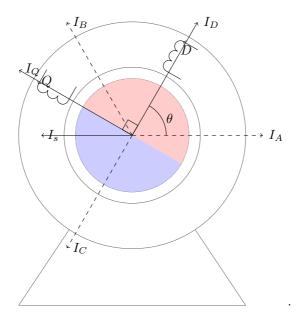

The controlled system is a Permanent Magnet Synchronous Motor from AMK. The desired controlled variables are torque and speed. The motor output speed can be expressed as a result of the developed electrical torque  $T_e$  through Equation 2.1 where  $\omega$  is the rotational speed of the rotor in rads/s,  $T_e$  is the torque developed by the motor, and  $T_l$  is the load torque. In our analysis, we will first model the motor currents as a vector  $I_s$  in the three-axis coordinate system shown in Figure 2.1. The current vector can then be represented as in Equation 2.3.  $T_e$  can be expressed as Equation 2.2, where P is the number of poles in the motor, and  $\lambda_r$  is the flux coupling between the stator and rotor.

$$\frac{d\omega}{dt} = \frac{T_e - T_L}{J_e q} \tag{2.1}$$

$$T_e = \frac{3P}{2} \lambda_r I_s \tag{2.2}$$

$$\vec{I_s} = \sqrt{\frac{2}{3}}(i_a e^{j0} + i_a e^{j2\pi/3} + i_a e^{j4\pi/3})$$

(2.3)

$$\vec{V_s} = \vec{R_s} \vec{I_s}(t) + \frac{d}{dt} L_s \vec{I_s}(t) + \lambda_r \omega$$

(2.4)

While this model of the motor is useful for analysis, and has been used in motor

control, it does not lend itself to dynamic control. This is partially because it offers little insight into the workings of the motor, and partly because it is overly complex, but primarily because it presents a nonlinear time variant system. To be able to apply control theory to the motor control system we will need to modify the model.

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \\ 0 \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos(\theta) & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta - \frac{4\pi}{3}) \\ -\sin(\theta) & -\sin(\theta - \frac{2\pi}{3}) & -\sin(\theta - \frac{4\pi}{3}) \end{bmatrix} \begin{bmatrix} I_{a} \\ I_{b} \\ I_{c} \end{bmatrix}$$

(2.5)

$$i_a + i_b + i_c = 0 (2.6)$$

$$i_c = -i_a - i_b \tag{2.7}$$

The first modification to be done is to realize that while there are three input currents, we only need two variables to parametrise the two-dimensional current vector  $I_s$ . Because the three phases are connected internally, the currents must sum to zero, as in Equation 2.6. We can therefore eliminate one variable from our system, and represent our current vector in a Cartesian coordinate system. The system chosen has it's primary axis  $(\alpha)$  on the A-axis of ABC system, and secondary  $(\beta)$  90 degrees counter clockwise. The transformation from ABC to the  $\alpha\beta$  system is called Clarke's transformation, and is seen in Equation 2.5.

$$i_{dq}^{2} = \sqrt{\frac{2}{3}}(i_{a}e^{j0} + i_{a}e^{j2\pi/3} + i_{a}e^{j4\pi/3})e^{j\theta}$$

(2.8)

$$\begin{bmatrix} i_d \\ i_q \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos(\theta) & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta - \frac{4\pi}{3}) \\ -\sin(\theta) & -\sin(\theta - \frac{2\pi}{3}) & -\sin(\theta - \frac{4\pi}{3}) \end{bmatrix} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix}$$

(2.9)

While Clarke's transform reduces the amount of variables to work with, it does not solve the primary problem of the ABC model. A direct  $\alpha\beta$ -based model would still have to output a sine wave response for a constant torque output. To solve this we let our coordinate system rotate with the rotor, affixing the  $\alpha$  axis to the rotor's north-south axis. The transformation from the ABC reference frame

Figure 2.1: ABC model of a Permanent Magnet Synchronous Motor

Figure 2.2: DQ model of a Permanent Magnet Synchronous Motor

to this rotating reference frame is called Park's transformation, and is found in Equation 2.9. The axes in this reference frame is referred to as the direct (d) axis, and the quaternion (q) axis, after it's orientation relative to the rotor flux's primary axis.

#### 2.2 Field-Oriented Control

$$T_e = \frac{3}{2} Pi_q (\lambda_r - (L_q - L_d)i_d)$$

(2.10)

$$T_e = \frac{3}{2} P i_q \lambda_r \tag{2.11}$$

When visualizing the motor currents in the DQ reference frame as in Figure 2.2, sine wave currents are reduced to two dc currents. In general, the d axis current controls rotor field strength, and the q current generates torque on the rotor. The torque developed is given by Equation 2.10.

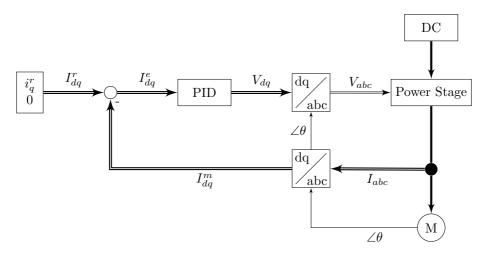

The most basic control loop implemented in this reference frame is shown in Figure 2.3. It is based on the assumption that when operating below the rated speed of the motor (18600 RPM for the AMK), it can be assumed for an ideal motor that controlling  $i_d$  to zero will yield an optimal control algorithm, and Equation 2.10 reduces to Equation 2.11.

This is the basis for Field Oriented Control. Feedback control is provided through measuring the phase currents, and using an encoder to measure the rotor position and perform Clarke's transformation to calculate  $I_{dq}$ . PID regulators can then be used to calculate the required output voltage  $V_{dq}$ .  $|V_{dq}|$  must allways be kept less than the DC motor supply.  $v_q$  should therefore be reduced to ensure this limitiation. Multiplying  $V_{dq}$  with the inverse Park's transform matrix yields the vector of output voltages  $V_{ABC}$  that is fed to the PWM generator driving the power transistors generating an output voltage. By setting  $i_{d_{ref}}$  to 0, and calculating  $i_{q_{ref}}$  with Equation 2.11, fast and correct torque response can be achieved up to the motor rated speed. If the motor is driven further,  $v_d$  will dominate  $v_q$ , degrading the inverter's ability to push  $i_q$ , decreasing the generated torque.

Figure 2.3: Flow diagram of a simple FOC inverter

### 2.3 Advanced Control Methods

$$v_d = R_s i_d + L_d \frac{di_d}{dt} - \omega L_q i_q \tag{2.12}$$

$$v_q = R_s i_q + L_q \frac{di_q}{dt} - \omega L_q i_d + \lambda \omega \tag{2.13}$$

The FOC model of the motor can be expressed as an optimization problem. Limited by the current rating of the motor, and the voltage of the DC supply, we want to minimize the current used to generate the requested amount of torque.

$$min |I_{dq}(T_e)| (2.14)$$

$$s.t T_e = T_{e_{ref}} + \epsilon (2.15)$$

$$i_q^2 + i_d^2 \le i_{s_{max}}^2 (2.16)$$

$$v_a^2 + v_d^2 \le v_{dc}^2 \tag{2.17}$$

If we insert Equation 2.12 and Equation 2.13 in Equation 2.17 the voltage constraint

can be restated as Equation 2.18.

$$\left[ \left( R_s i_q + L_d i_d \omega + \lambda \omega \right)^2 + \left( R_s i_d - L_d i_q \omega \right)^2 \right] \le v_{dc}^2$$

(2.18)

#### 2.3.1 Maximum Torque Per Ampere

While the assumption that controlling  $i_d$  to 0 will result in an optimal control scheme is not completely incorrect, we can see from Equation 2.10 that it is not the whole truth. If we want to achieve optimal torque control while minimizing the applied current, we must make use of reluctance torque, the torque generated by the second term of the equation. As we increase the amount of applied torque current, the optimal setpoint for  $i_d$  is actually slightly negative. Equation 2.19 from [18] shows the equation calculating an optimal  $i_d$  setpoint when disregarding any disturbances and parameter errors. It is derived from the Figure 2.4a, showing the path of this algorithm in black and a constant torque of 10Nm in blue. The algorithm is called the Maximum Torque Per Ampere path, and minimizes current draw for a given torque value.

$$i_{d_{MTPA}} = \frac{\lambda}{2(L_q - L - d)} - \sqrt{\frac{\lambda^2}{4(L_q - L_d)^2} + i_q^2}$$

(2.19)

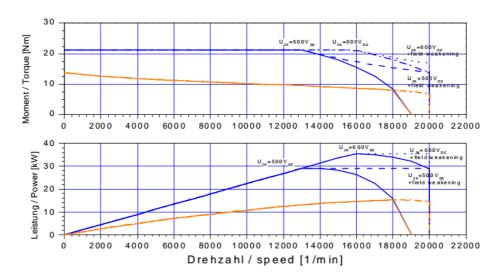

The limits of the AMK motor system are displayed in Figure 2.4b. The green line shows the 100A current limit, while the red and orange lines represent the voltage constraint when  $V_{dc} = 550V$  at 19000RPM and 16000RPM, respectively.

## 2.3.2 Field Weakening Control

As can be seen from Figure 2.4b, as the speed increases, the voltage limit ellipse constricts. In ordinary FOC, as outlined earlier, this causes the motor to lose torque and stabilize at some constant speed less than the no-load speed of the motor if 0  $i_d$  is applied. As can be intuited from Figure 2.4b, it is possible to reach higher speeds than the rated speed of the motor. If one were to apply some negative  $i_d$  current, the current vector would be moved left in the plane, allowing the controller to follow the voltage limit curve upwards, generating more torque. This technique is called field weakening, as it works by weakening the permanent

magnet field generated by the rotor. Care should be taken to limit the duration and strength of field weakening, as this will heat up the stator magnets, and can permanently weaken them.

(b) System limits at a speed of 16000 and 20000RPM

Figure 2.4: FOC parameter curves

Being able to operate above the maximum rated speed of the motor is beneficial, as it allows us to increase the gearbox reduction of the car, yielding higher output torque, and faster acceleration, while retaining the car's top speed. Gnist is designed for a top speed of 115km/h with a gear reduction of approximately 15.5:1, yielding a motor top speed of about 20~000RPM. As shown in Figure 2.5 the motor loses power at about 18~600~RPM. This necessitates field weakening action.

Figure 2.5: The torque vs speed plot of an AMK DD5 motor [1]

Field weakening control can be implemented in several ways. The algorithms can be grouped based on their working principle into four groups[13]:

**Feed-forward** These algorithms estimate the back-emf and required  $i_d$  current based on speed and/or current measurements. While the back-emf is estimated, no feedback is used, as the voltage is used to directly apply the following current. These methods are generally fast and stable, but are sensitive to parameter deviations, temperature and inductor saturation.

Feedback These algorithms estimate the back-emf based on speed and/or current measurements. A feedback controller is used to controll the applied  $i_d$ . These methods are not as fast as feed-forward, and offer poor transient response. They are however more effective, as they utilize the DC-link voltage better by eliminating steady-state error. They are also less sensitive to parameter deviations, temperature and inductor saturation.

**Hybrid** In an attempt to get the best of both worlds, these methods use a combination of the preceding methods. For example, a feed-forward estimate can be modified by a feedback regulator, yielding faster step response while eliminating steady state-errors.

Advanced techniques Other, more advanced control-theory based algorithms may be employed. They generally offer further benefits over the hybrid

method, while requiring significantly more computing power.

As seen in Table 2.1, all algorithms have some redeeming attributes. Since this is a prototype project, the advanced algorithms were discarded early on. However, the hybrid field weakening algorithm outlined in [18] was considered possible to implement.

|                          | Feed-forward | Feedback | Hybrid | Advanced |

|--------------------------|--------------|----------|--------|----------|

| Parameter sensitivity    | _            | +        | +      | ++       |

| Transient response       | ++           | -        | +      | ++       |

| Steady state error       | _            | +        | +      | ++       |

| Tuning complexity        | ++           | +        | -      | _        |

| Computational complexity | ++           | +        | -      | _        |

| Design complexity        | ++           | +        | -      | _        |

Table 2.1: Choice matrix for field weakening calculation algorithms.

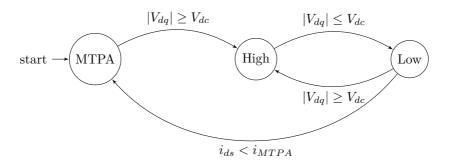

Figure 2.6: State diagram of the proposed voltage-follower FW algorithm.

The proposed algorithm tracks the output voltage of the PID regulator in Figure 2.3, comparing it with the DC supply voltage. The governing state machine is shown in Figure 2.6. In normal operation, the MTPA  $i_d$  setpoint is passed on, allowing optimal control when inside the operating limits. When the voltage limitation is reached and  $|V_{dq}| >= V_{dc}$ , field weakening operation is started. In the "High" state, the output voltage magnitude is too high, and d current is applied to reduce it. When in this state, the next  $i_d$  is decided by Equation 2.20. This is essentially an integration only PID controller, attempting to reduce the speed error. The proposed FW algorithm therefore requires the torque input to be governed by a speed controller. This is done to solve an issue that makes simpler FW approaches have problems winding down from FW mode. In the "Low" state, the motor is operating below the voltage limit. The  $I_{dq}$  vector is moved left toward

MTPA curve by Equation 2.21. When the MTPA curve is hit, and  $i_{d_t} = i_{d_{MTPA}}$ , control is returned to the MTPA algorithm. This algorithm allows the inverter to effectively track the system limits.

$$i_{d_t} = i_{d_{t-1}} - \alpha(\omega_r - \omega) \tag{2.20}$$

$$i_{d_t} = i_{d_{t-1}} + \beta(\omega_r - \omega) \tag{2.21}$$

# 2.4 System modelling

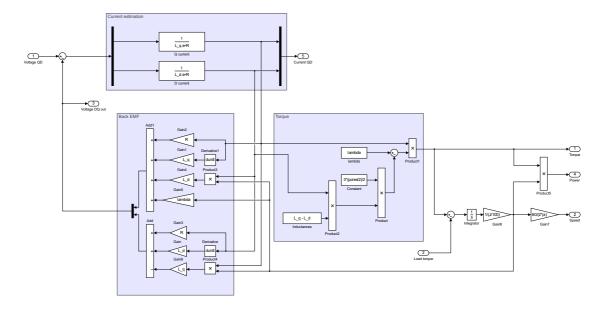

Several attempts have been made at constructing a comprehensive model of the motor controller system. For his 2015 master's thesis, Lars Helge Opsahl developed a Simscape Power Systems-based model. This model computed AC waveforms, switching stage performance and motor response. This system was tried adapted to the new motors, but due to the power stage modelling, simulation performance was extremely poor. The source of the poor simulation performance, the power stage PWM signals, forces the simulation step size to grow extremely small to be able to catch the system dynamics. A 1 second long simulation could easily take 2 minutes to compute. While 2 minutes for 1 second is not that bad, it is often required to do longer runs of 10s or more, increasing simulation time to 20 minutes. As work had to be focused on the development of the system hardware rather than simulation, it was decided not to pursue this model further.

The motor simulation work was later returned to, with the aim of finding an accurate model with higher simulation performance. On the assumption that the only way to alleviate the performance issue is to avoid modelling the power stage modulation, or implement some way of simulating it's effects, a new model was designed. By abstracting the power stage output as an ideal, bounded, voltage source, the total simulation time for a 1s simulation is reduced from 2 minutes to 15 seconds, a speed boost of 800%. This new model represents the motor dynamics in the DQ reference frame, rather than the ABC frame, as this reduces the amount of computations required.

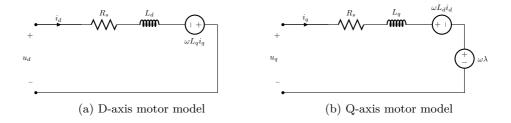

Figure 2.7: D and Q axis models, from page 328 of [13]

#### 2.4.1 Motor Model

Figure 2.8 shows the motor model. Based on the equivalent circuit in Figure 2.7, the motor phase coils in the DQ plane are modeled as a first order RL filter. The back emf voltage is estimated based on Equation 2.13 and Equation 2.12, and subtracted from the input voltage. While it is in reality generated over the length of the coil, the lack of any capacative elements in the circuit allows us to make this simplification. Equation 2.10 is used to calculate developed torque, and integrated to calculate output speed. The instantaneous motor output power is calculated by Equation 2.24, with  $T_e$  given in Nm, and  $\omega$  in rad/s. The speed value is then scaled from rad/s to RPM before output. As the motor phases are modelled as a filter, it is possible to input both idealized DC voltages, and realistic pulse width modulated signals. If desired this model could therefore be used to model other vector control systems using more advanced output modulation techniques than PWM.

$$\omega = \int \alpha \tag{2.22}$$

$$\omega = \int T_e/J \tag{2.23}$$

$$P_{mech} = \omega T_e \tag{2.24}$$

Figure 2.8: Motor model

#### 2.4.2 Controller

The modelled control system uses a PI controller to regulate the phase voltages. The PI references are generated by the a PI speed controller, and the MTPA and Field Weakening algorithms. Before calculating the error vector, the  $i_q$  reference is corrected to ensure a request with magnitude lower than 100A. The PI current regulator is set up with integral clamping.

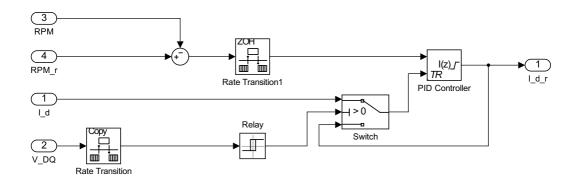

#### 2.4.3 Field Weakening

The field weakening algorithm described in subsection 2.3.2 is not trivial to implement in Simulink because of the state storage implied. However, a rough equivalent using switches and relay blocks to control the error input of a PID regulator has been developed for testing purposes. During testing this has allowed the simulated motor speed to exceed it's 18600 RPM limitation.

Figure 2.9: Simulink controller model overview

Figure 2.10: Field weakening approximation

# 3. System Requirements

This chapter will represent the requirements and functionality deemed necessary, based on the information in chapter 2, and experiences testing and tuning the 2015 inverter system.

# 3.1 Power system

The power system requirements were explored further in the authors' prestudy [20].

**Functionality** The power system must be able to output a variable voltage controlled by the central controller system. Assembly time should be considered when designing these systems.

**Load** The finished system should be capable of handling both the continuous and peak current loads of the motors.

**Bandwidth** The switching stage must be able to switch at a high enough frequency that stable control can be achieved.

**Safety** All Power systems should be designed to safely withstand it's working voltage.

All components of the inverter designed to carry phase power should be designed to carry the motor's rated current continuously, and its peak current for 3 seconds (the maximum time the car will use at peak torque).

When designing the high voltage systems of the car, all PCBs populated by both high and low voltage systems should have at least 4mm isolation zones around all borders, as well as coating the PCB with a conformal coating to eliminate creepage.

# 3.2 Digital Interface

The inverter needs to be able to receive setpoints and commands from the rest of the car and the test crew via CAN. In addition to ordinary setpoint commands, status monitoring and test functionality should be in place. As the inverter produces a lot of data, a separate high bandwidth interface should be in place for testing.

**Functionality** The inverter interface should be able to adjust parameters, setpoints and state settings. A simple interface should be available to change regulator parameters and monitor state data.

Load Data transmission and reception should not interfere with normal operation.

**Bandwidth** The high-bandwidth interface should be able to send all relevant data at full speed. The CAN interface should not overload the rest of the car.

**Safety** Requests that may jeopardize safe operation of the inverter should not be fulfilled.

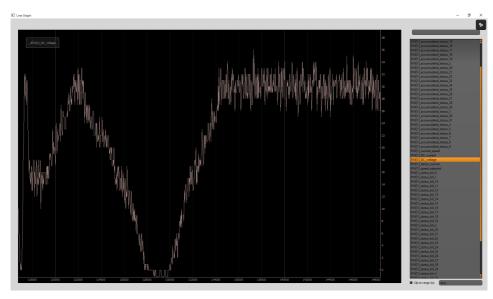

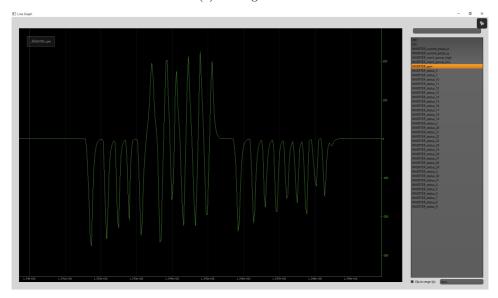

Revolve designs it's own analysis software that permits streaming and on-the-fly innterpretation of data from the car's CAN network. An inverter plugin should be designed for this software to allow easy access to state and parameter data. In adition, it's line graph plugin can be utilized for display of state data. A potential high bandwidth interface should be designed so as to be compatible with Analyze.

# 3.3 Physical Interface

The inverter must be able to interface with the motor encoders and temperature sensors. To simplify the ECU design, the inverter physical interface should mirror that of the AMK inverter. During testing season it will be useful to have programming ports available for each inverter in the casing.

**Functionality** The inverter must interface correctly with the motors, and CAN bus. External connectors should be available for a separate high speed interface, and programming. Connectors should be compatible with AMK alternative.

**Load** The external connectors should be made with high-quality connectors and shielded wiring to be noise-resistant.

**Safety** All internal connections should be done with high-quality connectors and wiring. Loose wiring inside the inverter can be a safety hazard.

All low-voltage outside connectors should be made with the same Deutch autosport connectors as the AMK inverter casing, to allow quick replacement should there be a need to. High quality connectors will also reduce clutter, problems and wear and tear during testing, saving precious hours of debugging.

# 3.4 Control system

The inverter control system should be able to regulate the motor output torque. Changes should be made to last years control system to ensure operation within the motor limits. Implementation of MTPA and field weakening algorithms should also be attempted.

**Functionality** The motor controller should regulate torque within the system limits.

Bandwidth The controller should have a high enough bandwidth to allow stable, efficient control, but not so fast that computing time jitter, interrupts or slower tasks causes the system to miss deadlines.

**Safety** The controller should allow safety shut downs, and guarantee safe operation in every plausible situation.

To reduce ECU coding complexity, and allow torque derating based on speed, the controller interface should mirror the AMK interface. Accordingly, the torque setpoint should be set by a PI speed regulator within limits dictated by the ECU. While this adds some complexity, it acts as a safety-feature, and allows hotswapping the two inverter systems.

# 3.5 Safety features

As the inverter directly controls the current in to and out of the battery, it is critical that errors are detected and acted upon. Overcurrent or overvoltage errors

could cause battery fires or damage the motor beyond repair. The inverter should act appropriately as fast as possible once an error is detected

**Functionality** The inverter should be able to detect overcurrent, overvoltage and overtemperature errors. Any errors should be signaled to the test crew, and appropriate action should be taken to avert damage.

**Bandwidth** The detection time constant should be chosen according to the failure cause dynamic.

Safety Error handling action should be taken before the end of the next control period after detection. Any action taken should not jeopardize the system or driver.

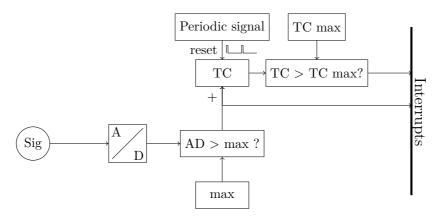

When an error state is discovered, the inverter should either reduce torque, cut torque to 0, or shut off the power stage. The phase currents are the fastest changing states in the system. Considering the phase current time constant of 3.5ms, an error checking algorithm running more often than 1kHz should be fast enough to catch any state threshold violation fast enough to perform reparative action.

# 3.6 System Architecture

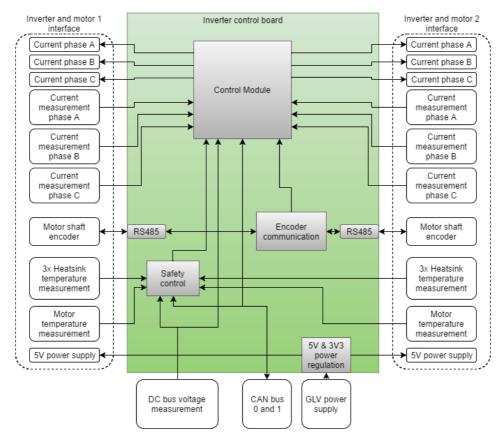

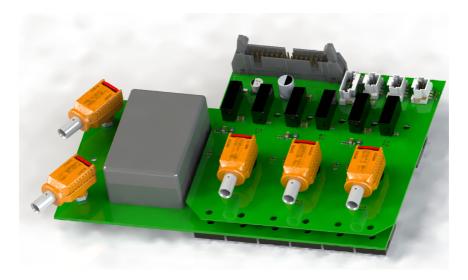

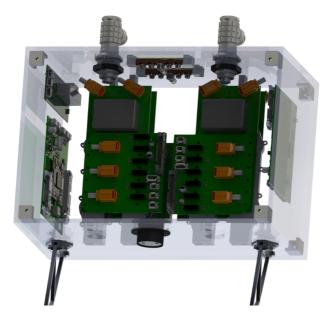

Mirroring the overall design of the 2015 inverter, the R16 is divided into a Control Card, a Gate Driver Board, and a Power stage. This allowed the design work to be segmented into a simulation-heavy power system, innovative gate driver system, and complex computing platform. The gate driver board also serves as the isolation barrier between the two others. This reduces the restrictions and design constraints on the control card. In addition, the inverter system should include the additional safety circuits required by the FSAE rules.

Control Card The control card contains all computing power in the inverter. It should be able to read all necessary sensors, and output a control signal to the power stage via the gate driver card. To allow switching between SoC and microcontroller solutions, a slot-in solution allows swapping the computing section of the board.

Gate Driver The 2015 inverter used 3 Semikron gate driver boards controlling one phase each. To shorten assembly time, the R16 will feature a single three-channel gate driver for each inverter. For the same reason, the gate driver should slot on top of the Power Board with headers. To reduce cable clutter all power stage temperature and current sensors are connected to the gate driver PCB and wired to the Control Card through a single cable bundle.

**Power Board** The power board constitutes the power stage of the R16. It connects power transistor legs, DC link capacitor, and motor phases through a PCB, and presents a detachable interface through the Gate driver. This board is designed to tolerate the high currents passing from the battery to the motor phases.

Additional Systems In addition to internal control safety, a system allowing the monitoring and safe charging or discharging of the inverter DC link capacitors is required. In the inverter, this system consists of the Voltage Indicator Circuit (VIC), discharge circuit, and shutdown circuit interlocks.

# 4. Hardware design

#### 4.1 Current sensors

The motor controller requires feedback from all motor currents. The electromagnets in the motors are connected in a wye-configuration, as seen in Figure 4.1. Therefore only two currents need to be measured, the last phase current can be computed by Kirchhoff's current law, as in Equation 4.1.

$$I_a + I_b + I_c = 0$$

$I_c = -(I_a + I_b)$  (4.1)

The pedal sensors controlling the torque output of earlier cars have had less than 1000 steps from 0 to full torque without the driver mentioning any sensitivity problems. In addition, the motor connected to these cars were a 250Nm motor, more than 10 times more powerful than the current motor. In light of this, a torque ripple of 1/100th of the maximum output, or 0.21Nm, should have acceptably low impact on driver performance. With a maximum phase current of  $100A_{RMS}$ , the maximum acceptable current ripple becomes  $1.5A_{pk-pk}$ . Therefore a current sensor system with a precision lower than 1.5A/LSB should be sufficient. While the maximum current through the motor should not exceed  $100A_{RMS}$ , experience from 2015 indicates that momentary spikes in the current due to fast switching transients may exceed twice that value. The

Figure 4.1: Motor's internal wye connection

Figure 4.2: A closed loop hall effect sensor

maximum nominal current rating of the sensor should therefore be chosen higher than the peak value of the motor rating of 141A. The peak current rating of the

| Nominal current | >141A               |

|-----------------|---------------------|

| Peak current    | > 300 A             |

| Bandwidth       | $> 25 \mathrm{kHz}$ |

| Accuracy        | < 1.5 A/LSB         |

| Noise           | $1.5A_{pk-pk}$      |

Table 4.1: Current sensor requirements

sensor must be higher than 300A. The sensor bandwidth needs to be higher than the fastest switching frequency planned for the inverter.

Current measurements can typically be done in two ways, current shunt measurement, or current transducers. In a current shunt measurement, current is passed through a high power, low resistance resistor, and the resulting voltage is amplified and measured. In a current transducer the magnetic field generated by the flowing current is measured and transformed by a hall-effect sensor into a voltage signal that is read directly, or a smaller current signal that may be measured via a current shunt. Using a current shunt is lighter and smaller, but complicates PCB layout. By applying current shunt measurements directly one also has to account for the considerable common mode voltages on the signal, while transducers typically are completely isolated from the high voltage system.

|                 | HO-S 150           | LA 150-P           |

|-----------------|--------------------|--------------------|

| Nominal current | 150A               | 150A               |

| Current range   | +/-375A            | +/-212A            |

| Bandwidth       | $100 \mathrm{kHz}$ | $150 \mathrm{kHz}$ |

| Noise           | +/-0.5%            | < +/ - 0.4%        |

| Supply voltage  | 5V                 | +/-15V             |

| Weight          | 32g                | 35g                |

Table 4.2: Current sensor core data, LA 150-Pweight with adaptor PCB

Because it is critical that these sensors work and show correct results, current transducers were preferred over shunts. In the project report, two designs were considered, and the Lem LA 150-P chosen. LA 150-P is a compensation sensor with a bipolar voltage supply. It was later discovered that the LA sensor does not satisfy the measurement range specification. It is possible, but expensive to supply the required +/-15V power source. After reevaluating the sensitivity requirements and supply complexity, it was decided to replace the LA 150-P sensors with a non-compensated sensor. These sensors can be powered by the already present 5V supply. With proper calibration these sensors achieve better than 1% precision. With a 400A range, and 12 bit ADC, like the one in the Atsam, this

results in a sensor system with better than 1A/LSB precision, and 4A max error. In cooperation with a LEM automotive sales representative, several sensor solutions were considered. Finally LEM proposed the HO-S 150 sensor. Its most important data can be seen in Table 4.2.

## 4.2 Encoder

To measure the motor angle, each motor comes mounted with a Heidenhain ECI1118 encoder. This encoder features built-in self checks, and communicates via the advanced EnDat 2.2 protocol. The following information is gathered from the Heidenhain EnDat primer[7].

#### 4.2.1 Endat

"The EnDat interface is a digital, bidirectional interface for encoders. It is capable both of transmitting position values as well as transmitting or updating information stored in the encoder, or saving new information. Thanks to the serial transmission method, only four signal lines are required. The data is transmitted in synchronism with the clock signal from the subsequent electronics. The type of transmission (position values, parameters, diagnostics, etc.) is selected through mode commands that the subsequent electronics send to the encoder."

The Encoder Data (EnDat) system specifies a voltage supply, standard pinout, communications protocol and certain encoder specifications. Most EnDat encoders are developed and sold by DR. JOHANNES HEIDENHAIN GmbH. The subsequent electronics - the user electronics - is responsible for supplying the required 5V voltage and RS485 transcievers, but there are FPGA IP's available to implement the communication protocol.

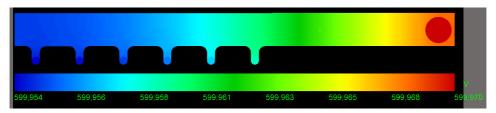

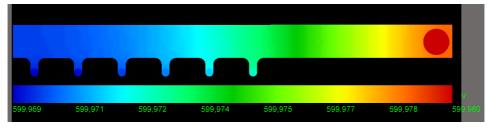

EnDat communicates via a dual RS485 hardware link. By using time skew compensation, to offset signal transmission time through the link, data rates up to 16MHz can be achieved by an EnDat 2.2 master.

The EnDat protocol allows serial communication with an absolute encoder, in addition, most EnDat encoders allow storing a position offset in the internal memories. In this way, the encoder 0 position can be aligned with the rotor magnetic field.

These features makes it ideal for motor control applications in an EV. The alternative absolute encoder interfaces are typically slower, and incremental encoders requires the car to be rolled before working, which is not ideal.

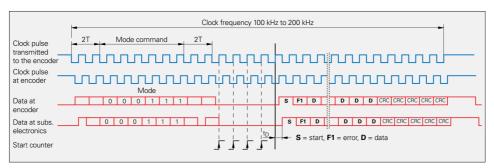

Figure 4.3: The EnDat serial protocol format. From page 6 in [7]

Figure 4.4: The SSC emulating a bidirectional serial protocol. From page 1065 of the Atsam E70N21 datasheet [2]

As a result of it becoming clear that the inverter had to communicate with an EnDat encoder came late in the development process, an attempt had to be made to emulate the protocol. Communicating with the encoder requires sending two clock cycles with 0-bit data, then transmitting a three bit mode command, and its inverse, before a new two-bit cycle of 0-bits. The controller then waits for an unspecified amount of time, while clocking the encoder, until the encoder responds with the command result, some status bits, and a checksum value. The time delay before the response varies with the command excecuted. The command sequence not aligning two an 8 or 9 bit structure makes emulating this communication interface difficult,

an issue that is compounded by the variable delay, and continued clocking. This is not a form of communication supported in most serial communication modules.

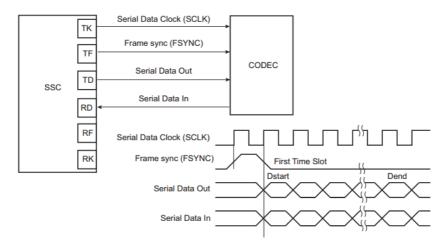

The protocol was attempted emulated by the Synchronous Serial Controller in the Atsam. This module is made to be as flexible as possible, and allows the user to program his or her own serial interface. As seen in Figure 4.4, the module features one receive and transmit module, with both modules sporting a data line, clock line, and select line. The select lines can be programmed to signal various states in the reception and transfer buffer. When simulating the EnDat protocol, the transmit flag was used to assert the RS485 bus, enabling the bus driver when transmitting, and releasing it when receiving. The transmit clock was used to generate the clock bus signal, and to drive the internal receive clock, synchronizing the two buffers. The transmit message format is highly customizable. The length can be adjusted from 2 to 32 bits, and appended and prepended with various bit patterns. By transmitting a 6-bit message with two 0-bits before and after transmission, the command transmission could be successfully emulated. No good solution for the bus waiting was found, but an interrupt may be used to trigger reception.

While an output message that looked correct was transmitted to the encoder, no coherent answer message was ever received. As the EnDat protocol is extensive, and there is strict timing and correctness restraints, the reason for this was probably some error in the way data was transmitted, either in the RS485 transciever setup, or the setup of the SSC module. It was clear that an alternate method of implementing the EnDat controller was needed.

Texas Instruments has a line of ARM9-based processors containing a small programmable logic arera called the Industrial Communication SubSystem. This allows the processor to implement more involved communication protocols like Ethernet or EnDat without locking it into the hardware. These also come with premade libraries for motor control, allowing implementation of FOC for AC motors. This would have required learning another microcontroller platform, and reimplementing the nearly finished controller source code on this new platform, however. It was therefore not considered further.

Another solution was provided by Heidenhain themselves. Mazet, a german electronics and software company has developed several FPGA IPs for use with EnDat encoders. These act as master controllers, and communicate externally with SPI or parallel bus interfaces. As we had a compatible FPGA development board, and the atsam has an abundance of modules supporting SPI communication, this was

seen as a much more viable solution.

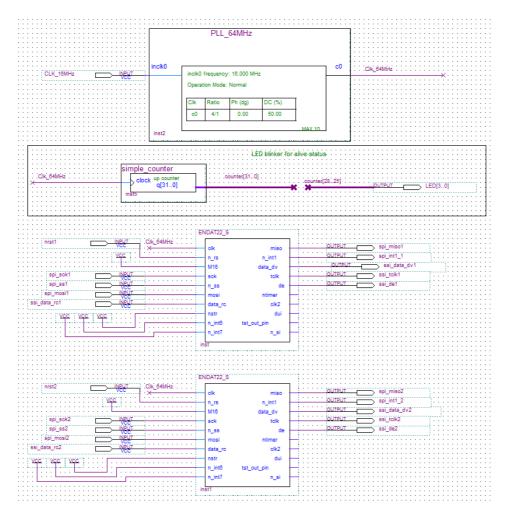

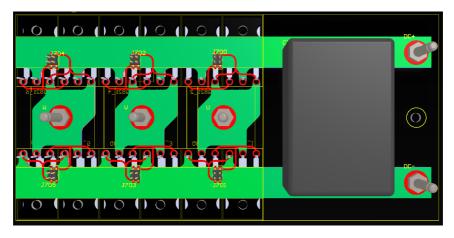

#### 4.2.2 Altera MAX10

The FPGA IP required to communicate with the encoder was aquired by a sponsor-ship deal with Mazet and Heidenhain. The chosen FPGA on which to implement was an Altera MAX10, as there were a development kit for this FPGA available to the authors. While the MAX10 series does not feature a large number of logic elements, the entire series is available in QFP packaging, making PCB manufacturing possible within the team's production capabilities. The EnDat 2.2 master IP does not require a very large amount of logic elements, so even with two instances of the IP, all the MAX10 variants have a sufficiently large amount of elements to do the job.

The IP contained the HDL design of the communication protocol in enchrypted HDL, which was translated into a netlist and usable code using Synplify Premier. The resulting HDL code was then imported to Quartus and implemented in the block diagram shown in Figure 4.5. As each control card handles two inverters, two instances of the communication protocol IP is required on a single chip, keeping the hardware count low. The IP prefers a running frequency of 64 MHz, so a PLL was inserted to scale the clock frequencies provided from the 16 MHz clock on the control card. In addition to the encoder IPs and the PLL, a counter has been added to blink some LEDs on the board, so that a quick glance is enough to verify that the chip is alive. The results of the compilation of the full MAX10 system on a 10M16 variant of the MAX10 series is shown in Table 4.3.

|                      | Used | Available |

|----------------------|------|-----------|

| Total logic elements | 4649 | 15840     |

| Total registers      | 1957 |           |

| Number of pins       | 25   | 101       |

Table 4.3: Compilation restults of the MAX10

The encoder communication IP is provided with a SPI interface, making the connection to external controllers simple. It also includes the option of a parallel-bus interface, for a faster communication protocol when used with on-chip controllers inside an FPGA or a SoC. This is something that will be desired when the entire control system is implemented on a SoC, so that external systems can be reduced to a minimum.

Figure 4.5: The final block diagram of the encoder communication system

# 4.3 Control Card and Insert

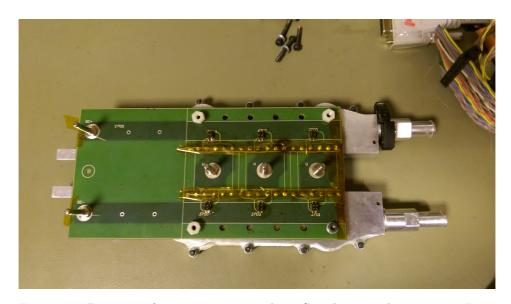

Figure 4.6: Inverter control card with Atsam insert

# 4.3.1 Specifications

The control board is the main processing node in the inverter, making it the most complex PCB in the system. To complete all necessary tasks, it should provide the following features:

- Header for Atsam insert and Enclustra Mercury ZX5.

- Power supply

- Car communication

- USB connectivity

- Isolation

- Encoder interface

- Safety system

- Voltage measurement

## 4.3.2 Design

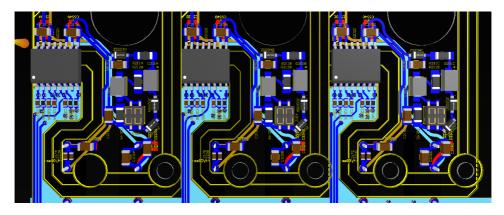

The control board PCB was built on the work done in the previous semester [20], but due to changes in the specification, a redesign was necessary. The design of the Control card is largely dominated by overall design decisions made by the team over the last three years. This simplifies the design process for all members, and minimizes the necessary parts stockpile. This also facilitates debugging and repairs, as it quells the tendency of electronics members to become gurus of their own system, allowing them to quickly recognise modules in others' designs. The main control module on the board is based on the footprint of Enclustra's Mercury ZX5, and the two 168-pin headers in the centre of the board are the mounting for the insert. An overview of the board is given in Figure 4.7.

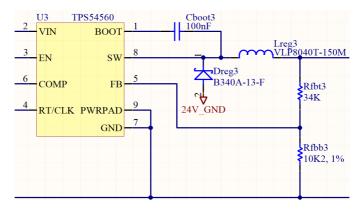

#### Power supply

The power supply is needed to drive the board, as well as supplying power to the gate drivers. The voltage regulators are based on Revolve NTNU reference designs, using a TI Webench-design incorporating the TPS54560 buck-regulator, using the GLV 24V as input. There are two 5V regulators: one supplying the control board itself, and one dedicated to supplying the two gate drivers the board is interfacing. To supply the board's 3.3V needs, a similar buck-regulator is implemented, but with a modified feedback bridge through the Rfbb3 and Rfbt3 in Figure 4.8, altering the output voltage, keeping all other parameters identical. These three voltage regulators, backed up by a second 3.3V regulator on the insert provide ample power to the low-voltage elements of the inverter.

#### Communication with the car

Figure 4.7: Inverter control card overview

The inverter interfaces the car in two ways: Can buses and a few signals directly from the ECU. Both the ZX5 module and the Atsam controllers have built-in CAN controllers, but neither have physical transceivers. Due to their high current consumption, and to reduce CAN bus stub lengths, these must be placed outside the controller, and as close to the outside connector as possible.

The transceiver used is the Texas Instuments' ISO1050 transceiver[12], the standard for all the systems in the car. There are two CAN buses in the car, and the control card must support up to two controllers on each PCB. There are therefore four chips on the board, with an additional transceiver to connect the Atmega safety

| J50       |                |

|-----------|----------------|

| 12        | Shutdown+      |

| 11        | Shutdown-      |

|           | PWR EN 1 1 24  |

| 10        | PWR EN 2 1 24  |

| 8         | INV EN 1 24    |

| 8 7       | TQ LIM EN 1 24 |

|           | GND            |

| ō.        | PWR EN 1 2 24  |

| 3         | PWR EN 2 2 24  |

| 6 5 4 3 2 | INV EN 2 24    |

| 3         | TQ LIM EN 2 24 |

| 2         | GND            |

| 1 .       |                |

| ECU       |                |

Figure 4.9: ECU and shutdown header

Figure 4.8: 3.3V regulator

controller to one of the buses. The transceivers are placed as close to the header as possible, so that the total stub length in the car is kept short, without forcing placement of termination. If the stub lengths are too long, reflections at the end of the stub may occur, corrupting data.

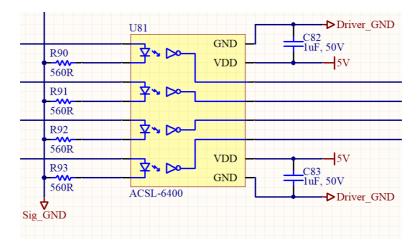

The AMK inverter requires four enable signals to function properly. These have been implemented on the R16 inverter as well, so that the ECU and torque vectoring systems have an identical interface to the inverter, regardless of which is currently situated in the car. The signals are transmitted at 24V, so they are scaled down to the motor controller's 3.3V input level through an optocoupler. In addition, the car's shutdown circuit is taken in to the board through the same header.

#### Isolation

According to the FSAE rules[16], EV4.1.7 all high-voltage areas must be sufficiently separated from low-voltage areas. As the control board includes the measuring circuit of the DC bus, this section of the board has been separated with a 6mm separation barrier in all layers of the PCB. In addition, high frequency optocouplers have been used to isolate the gate driver from the control board.

#### **Encoder** interface

The controller needs to know the position of the rotor in order to do correct calculations. The encoder mounted in the motors communicates on RS485 with differential lines, so a set of SP3485 half-duplex Transcievers[9] are placed between the header

and the MAX10 containing the encoder interface IP. This is teh required physical interface of the encoders, and the required interface software implemented on the MAX10 is further described in section 4.2.

#### Safety systems

There are several sensor measurings and safety features required for the inverter to operate properly. The control card thus needs to provide a well-functioning interface for these. The connection to the sensors themselves are done via the gate driver header, but some manipulation of the signals are needed on the board. The temperature sensors are NTC or PTC sensors, and the second resistor in the voltage divider is placed on the control board.

The current sensors work at 5V, but the Zynq and Atsam have a maximum ADC reading value of 0.5V and 3.3V, respectively. The output signal from the sensors are scaled through an INA337[10], so that the sensor voltage level does not go higher than what the control unit can handle. The formula for this conversion is  $G = \frac{2R_2}{R_1}$ . The sensors output a maximum of 5V, and with  $R_2 = 127k\Omega$  and  $R_1 = 400k\Omega$ , the level does not go beyond the Atsam's limit. By changing the values to  $R_2 = 20k\Omega$  and  $R_1 = 400k\Omega$ , the gain will be 0.1, keeping within the Zynq's limits. The overcurrent signal from the sensors is input directly to the Atmega (running at 5V), and put through a voltage divider to 3.3V before reaching the control insert.

An Atmega processor is implemented on the board to offload some processing tasks from the Atsam processors on the insert. It reads temperature sensors, DC voltage and overcurrent indicators from the sensors, and reports logging data over the CAN bus. The circuitry around this chip is fairly simple, and the code is presented in section 5.2

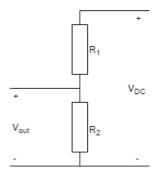

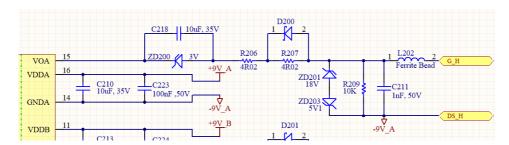

#### Voltage measurement

Figure 4.10: Voltage divider

The voltage measurement is done with a voltage divider over the DC bus, scaling it down to an acceptable level. As the input limit on the Atsam is 3.3V and the accumulator delivers voltages in the 600V range, a divider such as the one in Figure 4.10 with  $R_1 = 1200k\Omega$  and  $R_1 = 3.9k\Omega$  gives the ability to measure spikes

up to about 1kV, which should cover the irregularities from the accumulator with a good margin.

$$V_{out} = V_{in} \cdot \frac{R_2}{R_1 + R_2} \tag{4.2}$$

$$V_{in} = V_{out} \cdot \frac{R_1 + R_2}{R_2} = 3.3 \text{V} \cdot \frac{1203900}{3900} \approx 1031 V$$

(4.3)

After the voltage divider, an optical isolation amplifier from Avago, ACPL-C87[19] is used. This outputs a differential voltage signal, so an INA826[11] is used to transform it to a single-ended voltage level. Since scaling happens in the voltage divider, no further gain is needed on the instrumentation amplifier.

## 4.3.3 Insert

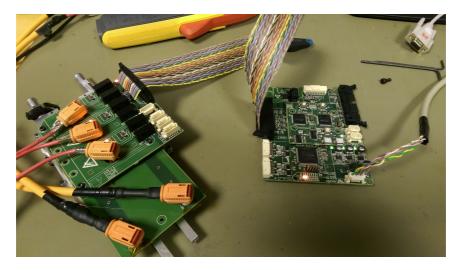

In addition to the ZX5 module, a backup solution was required, should the development of the Zynq code be slower than expected or fail. This backup came in the form of an in-house designed insert based on the Atmel SAMe70 microcontroller, used in systems troughout the car.

In order for the control board to be compatible with both the ZX5 module and the insert, the latter was designed around the same headers and footprint as the ZX5. The ZX5 features several physical interfaces that is not required for the inverter to work, such as SDRAM and ethernet transceivers, so these were left out of the Atsam insert, in order to keep it as simple as possible. The insert contains two microcontrollers and all circuitry required for these to work properly. USB-USART bridges are added to mirror the USB physical on the ZX5, and Mini-USB headers placed to be able to use the insert without the carrier card, for development purposes. This feature is further backed by a 3.3V regulator connected to one of the USB headers and a set of four indicator LEDs per microcontroller.

## 4.3.4 Issues and experiences