# System Scenario Based Application Mapping

Solveig Fure

Master of Science in ElectronicsSubmission date:December 2015Supervisor:Per Gunnar Kjeldsberg, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## **Description of Master Thesis**

Candidate name: Solveig Fure

Title: System Scenario Based Application Mapping

In system scenario based design dynamic application behavior is exploited to optimize the application's execution costs (e.g., performance and energy consumption). Through code inspection and profiling, different dynamic scenarios are identified and optimized at design-time. Furthermore, techniques for scenario prediction and switching are developed. At run-time the application and platform are reconfigured according to the dynamically predicted scenario.

This master assignment is based on a project assignment in the previous semester that included a literature study of system scenario based design and experiments with two dynamic applications using a model developed for dynamic voltage and frequency scaling. This work shall be continued with a description of a general methodology for application profiling for detection of dynamic application behavior and its cause. The methodology shall be applied to selected codes from the SPEC CPU 2006 benchmark suite and possibly additional applications.

Co-supervisor: Yahya H. Yassin

Supervisor: Per Gunnar Kjeldsberg

## Abstract

During the past decade, the processing requirements of embedded real-time systems have become more and more challenging; not only in terms of performance, but also regarding the energy efficiency. The dynamic nature of many of these systems has been recognized as an important feature to take advantage of. Scenario-based design is a well-known design methodology dealing with this. Identifying different use-case scenarios to optimize for is a strategy that has been used for a long time. Lately, another kind of scenario-based strategy has emerged; so-called *System scenarios*. Instead of classifying the behavior of a system through several use-cases, the actual costs of the system is considered, like resource usage or quality requirements. By thoroughly characterizing and analyzing the system behavior at design-time, the different system scenarios can be recognized at runtime without much overhead. The system can then be tailored to the identified scenario by employing the optimal settings that have been determined at design-time. It must however be enough exploitable dynamism present in the application to make up for the system scenario overhead.

The system scenario research field has well described theoretical design methodologies, even considering multiple cost dimensions. It can however be a long distance between the theoretical methodologies and an actual design process, especially when the dynamic cost is multi-dimensional. There is a considerable increase in the design complexity from adding just one more cost dimension to the design, motivating the need for a precise and concrete methodology. This thesis presents methods for detecting and exploiting dynamism in applications through profiling and code inspection, and the results from applying these methods on four applications, where three of them are a subset of the SPEC  $CPU^{TM}$  2006 integer benchmarks. The focus is on exploring both memory and CPU dynamism. Identifying the dynamism in an application can become very complex when considering multi-dimensional dynamism. An extension to the system scenario methodology which addresses this problem is therefore suggested. The scenario identification step of the original methodology is split into several smaller steps and executed separately for each of the considered dynamisms. This way the designer does not have to keep the entire design space in mind, but can focus on each kind of dynamism separately. Sub-scenarios are identified for each kind of dynamism, and then combined to form a scenario set where the total dynamism is exploited. The methodology is targeted at simple single-core platforms.

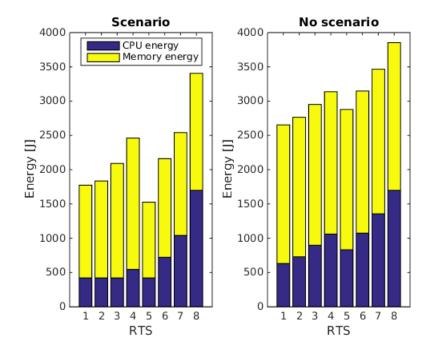

Several papers present promising results of the system scenario methodology when only considering CPU optimizations such as Dynamic Voltage and Frequency Scaling (DVFS). For applications requiring much memory however, DVFS can become infeasible as it means longer stand-by time for the memory. Memory typically contributes significantly to the total energy consumption, which motivates the recent introduction of memory system scenarios with dynamically reconfigurable memories. In this work, the dynamism in applications that are *both* memory and computationally intensive are exploited by combining DVFS and memory reconfigurations. Much CPU and memory dynamism is identified in the considered benchmark applications, and up to 31% of the total energy is saved by applying the modified system scenario methodology. Up to 47% is saved for some of the low-workload situations. Characteristics of an Intel Pentium processor and CACTI memory models are used to estimate the energy savings.

## Sammendrag

I løpet av de siste tiårene har kravene som stilles til innvevde systemer blitt stadig mer utfordrende, både hva angår ytelse og energieffektivitet. Mange av disse systemene har imidlertid dynamiske egenskaper som kan utnyttes. Den scenario-baserte design metodikken er et velkjent hjelpemiddel for å håndtere dette. Den tradisjonelle varianten går ut på å klassifisere oppførselen til et system gjennom såkalte bruker-scenarioer, for å deretter kunne optimalisere systemet avhengig av behov. Senere har en annen variant, med såkalte system scenarioer, begynt å få oppmerksomhet. I stedet for å dele inn i scenarioer basert på ulik oppførsel, ser man på variasjoner i den faktiske kostnaden til systemet. I løpet av design-fasen karakteriserer og analyserer man systemet grundig, slik at de ulike scenarioene som skulle oppstå i det ferdige systemet (altså i bruks-fasen) kan kjennes igjen uten mye ekstraarbeid. I design-fasen finner man også de optimale konfigurasjonene for hvert scenario. Det ferdige systemet kan dermed i bruks-fasen enkelt tilpasses scenarioene som kjennes igjen ved å ta i bruk disse forhåndsbestemte konfigurasjonene. Denne fordelingen av kontroll mellom design-fasen og bruks-fasen er sentral for system scenario-metodikken.

Forskningen på system scenarioer har resultert i veldefinerte teoretiske designmetodikker som skal fungere godt selv for å utnytte dynamikk i flere dimensjoner. Avstanden mellom en teoretisk metodikk og den faktiske design prosessen kan imidlertid være stor, da spesielt hvis flere former for dynamikk skal utnyttes samtidig. Kompleksiteten i designprosessen øker betydelig bare man tar én ekstra dynamisk kostnad med i betraktningen. En presis og konkret metodikk kan i så fall forenkle designprosessen. I denne rapporten presenteres metoder for å karakterisere og analysere to ulike former for dynamikk, nærmere bestemt i CPU- og minnebruk, samt en optimaliseringsteknikk for å utnytte dynamikken best mulig med en gitt platform. Dette testes og demonstreres på et utvalg applikasjoner, hvorav tre er hentet fra SPEC CPU<sup>TM</sup> 2006. Det blir fort mye å tenke på dersom man skal identifisere og karakterisere flere former for dynamikk samtidig. For å redusere dette problemet foreslås det derfor her en utvidelse av system scenario metodikken. Forslaget går ut på å splitte opp identifikasjonsprosessen i flere mindre steg for hver av dynamikk-dimensjonene som betraktes. Slik trenger ikke designeren å tenke på alle dimensjonene samtidig, men kan fokusere på hver dynamikk for seg. Under-scenarioer som utnytter hver form for dynamikk enkeltvis identifiseres, og blir deretter kombinert til et sett med scenarioer som utnytter den totale dynamikken. Metodikken er tiltenkt enkle énkjernes-platformer. Karakteristikken til en Intel Pentium prosessor samt minnemodeller fra CACTI brukes for å estimere energibesparelsene metodikken gir for nevnte applikasjoner.

I flere publikasjoner er det blitt vist lovende resultater for system scenario-metodikken, men det er ofte kun CPU-optimaliseringer som benyttes, f.eks. DVFS (dynamisk spenningog frekvensskalering). Dersom en applikasjon krever mye minne vil ikke alltid DVFS alene gi gode resultater, siden det innebærer lengre standby-tid for minnet. Siden energifor-

vi

bruket i minnet kan utgjøre en stor del av det totale energiforbruket har dynamisk konfigurerbart minne nylig blitt introdusert i system scenario-sammenheng. I dette arbeidet kombineres DVFS med ulike konfigurasjoner av dynamisk minne for å kunne utnytte dynamikken i applikasjoner som er både CPU- og minneintensive. Det identifiseres mye dynamikk i utvalget applikasjoner, både i CPU- og minnebruk, hvorav mye kan utnyttes. Opptil 31% av den totale energien spares i implementasjoner som designes vha. den modifiserte system scenario-metodikken. Opptil 47% spares i de mindre krevende situasjonene som oppstår i applikasjonene.

### Preface

This report is the result of a master thesis work conducted through the fall of 2015. It concludes my Master of Science degree in Electronics, at the Department of Electronics and Telecommunications, NTNU. Some parts of this report are taken from a system scenario project conducted during the spring of 2015. More specifically; the first part of the abstract and introduction, the theory chapters on system scenario development and DVFS, and the developed prime number application.

The focus of the master thesis is slightly different from the project work. Whereas I in my project work used a quite platform-directed approach, this thesis is more general in terms of hardware. The prime number application studied in the project work is studied further in this thesis. Additionally, three SPEC2006 benchmark applications are selected for system scenario design. The RTS identification techniques used in the project work had to be changed somewhat in order to design system scenarios without being able to test on a platform. Other applications also required a more general approach. Much work has been put down to make the benchmarks run on my premises, getting an understanding of how they work and whether or not the dynamism could be taken advantage of. Additionally, dynamic memories are introduced as a system knob

I would like to thank my supervisor Per Gunnar Kjeldsberg for all the guidance throughout this work. He introduced me to the concept of System Scenarios, which immediately caught my interest, and then suggested this project after considering my background and experience. Choosing to move on with the same topic and supervisor for my master thesis was an easy decision that I have not regretted. Thanks for all input and ideas, both regarding the theory and academics, the structure of the master work, and the report formalities.

I would also like to thank my co-supervisor Yayha H. Yassin. We had some very useful discussions where he shared his findings with me and evaluated my ideas.

Disclaimer: The SPEC performance results in this paper do not comply with the SPEC reporting rules [1].

viii

## Contents

|   | Des                                    | cription of Master Thesis                   | i                                                  |

|---|----------------------------------------|---------------------------------------------|----------------------------------------------------|

|   | $\mathbf{Abs}$                         | stract                                      | iii                                                |

|   | San                                    | nmendrag                                    | v                                                  |

|   | Pre                                    | face                                        | vii                                                |

|   | $\operatorname{List}$                  | of abbreviations                            | xiii                                               |

| 1 | <b>Intr</b><br>1.1<br>1.2              | <b>oduction</b><br>Contribution             | <b>1</b><br>3<br>4                                 |

| 2 |                                        | ory and previous work                       | <b>5</b>                                           |

|   | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | System scenario design methodology          | $9 \\ 9 \\ 11 \\ 11 \\ 12 \\ 13 \\ 13 \\ 14 \\ 16$ |

|   | 2.6                                    | Other related work                          | 16                                                 |

| 3 | Plat<br>3.1<br>3.2<br>3.3              | tform and profilers         Intel Pentium M |                                                    |

|          | 3.4          | Profile  | ers                                                                                                               | 27              |

|----------|--------------|----------|-------------------------------------------------------------------------------------------------------------------|-----------------|

|          |              | 3.4.1    | Zoom                                                                                                              | 27              |

|          |              | 3.4.2    | Valgrind Massif                                                                                                   | 27              |

|          |              | 3.4.3    | Valgrind Cachegrind                                                                                               | 28              |

| 4        | <b>A</b>     | .1:      |                                                                                                                   | 20              |

| 4        |              |          | nethodology                                                                                                       | <b>29</b><br>31 |

|          | $4.1 \\ 4.2$ | •        | n requirements and characteristics                                                                                |                 |

|          | 4.2          |          | rio identification                                                                                                |                 |

|          |              | 4.2.1    | DVFS dynamism                                                                                                     | 32              |

|          |              | 4.2.2    | Memory dynamism                                                                                                   |                 |

|          | 4.0          | 4.2.3    | Scenario identification summary                                                                                   |                 |

|          | 4.3          | -        | ration and exploitation $\ldots$ |                 |

|          | 4.4          |          | tion                                                                                                              |                 |

|          | 4.5          | Switch   | 8                                                                                                                 |                 |

|          | 4.6          | Theor    | etical evaluation of the methodology                                                                              | 42              |

| <b>5</b> | Арг          | olicatio | ons                                                                                                               | 45              |

|          | 5.1          |          | number checker                                                                                                    | 46              |

|          |              | 5.1.1    | DVFS dynamism                                                                                                     | 47              |

|          |              | 5.1.2    | Memory dynamism                                                                                                   |                 |

|          |              | 5.1.3    | Exploration and Exploitation                                                                                      |                 |

|          |              | 5.1.4    | Prediction and Switching                                                                                          | 49              |

|          |              | 5.1.5    | Results                                                                                                           | 51              |

|          |              | 5.1.6    | Changed assumptions                                                                                               |                 |

|          | 5.2          |          | mmer                                                                                                              |                 |

|          | 0.2          | 5.2.1    | DVFS dynamism                                                                                                     |                 |

|          |              | 5.2.2    | Memory dynamism                                                                                                   |                 |

|          |              | 5.2.3    | Exploration and Exploitation                                                                                      |                 |

|          |              | 5.2.4    | Prediction and Switching                                                                                          |                 |

|          |              | 5.2.5    | Results                                                                                                           | 62              |

|          |              | 5.2.6    | Other observations                                                                                                | 63              |

|          | 5.3          | 429.m    |                                                                                                                   | 65              |

|          |              | 5.3.1    | DVFS dynamism                                                                                                     | 66              |

|          |              | 5.3.2    | Memory dynamism                                                                                                   | 70              |

|          |              | 5.3.3    | Exploration and Exploitation                                                                                      | 71              |

|          |              | 5.3.4    | Prediction and Switching                                                                                          | 72              |

|          |              | 5.3.5    | Results                                                                                                           | 76              |

|          |              | 5.3.6    | Other observations                                                                                                | 76              |

|          | 5.4          | 464.h2   |                                                                                                                   | 79              |

|          | 0.1          | 5.4.1    | DVFS dynamism                                                                                                     | 79              |

|          |              | 5.4.2    | Memory dynamism                                                                                                   | 82              |

|          |              | 5.4.3    | Exploration and Exploitation                                                                                      | 84              |

|          |              | 5.4.4    | Prediction and Switching                                                                                          | 86              |

|          |              | 5.4.5    | Results                                                                                                           |                 |

|          |              | J. 1.0   |                                                                                                                   | 00              |

| 6            | <b>Disc</b><br>6.1<br>6.2<br>6.3<br>6.4 | cussion and Future Work         Applications         Memory related         CPU related         Methodology | <b>91</b><br>91<br>92<br>94<br>94 |

|--------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 7            | Con                                     | clusion                                                                                                     | 97                                |

| Aŗ           | open                                    | dix 1                                                                                                       | .03                               |

| $\mathbf{A}$ | Mis                                     | cellaneous 1                                                                                                | .05                               |

|              | A.1                                     | Dynamism in memory accesses                                                                                 | 105                               |

|              | A.2                                     | Prime number probabilities                                                                                  | 106                               |

|              | A.3                                     | Controlling the benchmarks                                                                                  | L07                               |

|              |                                         | A.3.1 How to run HMMER                                                                                      | 107                               |

|              |                                         | A.3.2 How to run MCF                                                                                        |                                   |

|              |                                         | A.3.3 How to run H.264                                                                                      | 108                               |

|              | A.4                                     | MCF data set generator                                                                                      | 108                               |

|              | A.5                                     | Viterbi algorithm                                                                                           | 108                               |

|              | A.6                                     | CACTI                                                                                                       | 108                               |

## List of abbreviations

| <b>IoT</b> Internet of Things                     |

|---------------------------------------------------|

| <b>RTS</b> Run Time Situation                     |

| TCM Task Concurrency Management9                  |

| <b>TN</b> Thread Node                             |

| <b>TF</b> Thread Frame                            |

| <b>DVFS</b> Dynamic Voltage and Frequency Scaling |

| <b>DFS</b> Dynamic Frequency Scaling              |

| <b>DVS</b> Dynamic Voltage Scaling13              |

| NUMA Non-Uniform Memory Access                    |

| <b>TDP</b> Thermal Design Power                   |

| HMM Hidden Markov Model                           |

| MCF Minimum Cost Flow                             |

| <b>CPI</b> Cycles Per Instruction                 |

# Chapter 1 Introduction

Energy efficiency is becoming increasingly important in a wide range of computer systems. For data centres and servers, the significant cost of power for computation and cooling is a big motivation to reduce energy [2]. At the other extreme, the fast developments within mobile battery-powered devices require more and more performance with a very limited battery-capacity [3]. The vast opportunities with future Internet of Things (IoT) developments make energy efficiency even more relevant. Power management is therefore a critical consideration when designing many of today's computer systems. As a result, there are several features available in modern hardware that can be used to reduce power. Efficient and smart software control is however required to take full advantage of this potential, and power management has thus been recognized as an important research field.[4]

Maintaining the reliability of an embedded system while saving energy is a big challenge, especially with the ever increasing complexity of both the applications and the platforms on which they run. Many embedded system applications have dynamic performance requirements. When a system cannot adapt its configurations to different workloads at run-time it means that it must be designed to always accommodate for the worst-case scenario. This leads to expensive systems that use a lot more energy than necessary much of the time. On the other hand, if the system is able to adapt its configurations at runtime to the current workload, there is a big potential to reduce the energy consumption. Signal processing systems often have dynamic processing requirements that should be exploited, e.g. multimedia decoders like JPEG and H.264. Especially when decoders are placed in handheld devices and the energy budget is limited, smart power management is important. These applications are typically dynamic due to for-loop structures with input-dependent ending conditions, resulting in a number of iterations that is unknown at design-time. Much energy can however be saved if one is able to take advantage of this dynamism; the worst case workload can easily be as much as ten times the best case workload in a modern streaming application.<sup>[5]</sup>

Creating optimal power management mechanisms that take advantage of such dynamic behavior is not a trivial task. Often, sufficient information is not available at designtime, and completely postponing the decision until run-time gives too much run-time overhead. The *System Scenario* design [6] is introduced as a methodology to take better advantage of the dynamic nature of embedded system applications, while keeping the necessary overhead at an acceptable level. An important feature of this methodology is that the workload analysis and system optimization is performed *both* at design-time and run-time. At design-time, the system's execution is divided into possible system scenarios, representing typical workload behaviors, based on cost analysis and profiling. Optimal system configurations are then found for each scenario. At run-time, when a particular scenario is recognized, the corresponding system configurations are applied. The system can thus be optimized at run-time with an acceptable overhead. A more detailed explanation of the methodology is given in Chapter 2.

The run-time configurability of the system is characterized by a set of *system knobs*. Dynamic Voltage and Frequency Scaling (DVFS), introduced in 1990 [7], is the most common platform configuration used within the system scenario methodology [8]. By decreasing the clock frequency of a processor and thus enabling a corresponding down-scale in the supply voltage, the power consumption can be reduced when performance requirements are low. The later developments with smaller feature sizes, lower operating voltages, more leakage current, and better sleep modes have however made DVFS by itself less useful, and the effects more difficult to model [9]. Furthermore, as pointed out by Snowdon et al. [10], the huge range of different applications makes the power and performance that depend on the exact instruction mix of the application. For a simple application, the exact behavior on a given platform can be characterized at design-time [11]. If the application is more complex and/or depends on dynamic input data, this might be difficult or even impossible. This is where the system scenario methodology comes in.

There are many other possible system knobs, e.g. memory-related configurations as suggested by Filippopoulos et al. in [12]. In [13] they present an application-independent memory-aware system scenario methodology to exploit dynamic memory requirements. Memory energy is reduced significantly by adapting run-time reconfigurable memory banks according to the predicted scenarios. The future developments within reconfigurable platforms can provide an even better foundation for system scenarios. Heterogeneous cores and customization through for example accelerators and dynamically configurable logic have been recognized as promising ways of improving energy efficiency. Multiple cores and customization are predicted to be the main drivers for microprocessor performance in the future [4]. A reconfigurable cache architecture is suggested in [14], concluding that dynamically changing write-strategy and replacement-strategy are feasible techniques. It is reasonable to believe that the system scenario design methodology will be used to exploit multi-dimensional dynamism, i.e. using multiple system knobs concurrently. The result can easily be a sub-optimal system knob setting unless a thorough and well-structured scenario exploration has been carried out. E.g., when DVFS and dynamic memory are used as system knobs, the feasibility of a DVFS setting depends on the current memory setting, and vice versa. The complexity of such designs makes it necessary with a precise and concrete methodology.

Finding suitable applications to evaluate such a methodology can be a challenge by itself. The SPEC benchmark suites contains a variety of the most important types of program behavior, and has become an industry standard for measuring processor and compiler performance. SPEC  $CPU^{TM}$  2006 [15] is SPEC's newest benchmark suite, composed of a wide range of different benchmark tests and inputs that are all based on actual, relevant applications [16]. The benchmarks are characterized by large input datasets and long

3

execution times (compared to CPU2000). Given that there is some exploitable dynamism present in these applications, they should provide a suitable measure for evaluating the system scenario methodology.

#### **1.1** Contribution

The intention of this work is to analyze the dynamism in a set of applications, develop system scenario implementations where the dynamism is exploited, and based on the gathered experiences suggest modifications or extensions to the system scenario methodology.

System scenarios represents a quite new field of research, so much of the previous work investigates system scenarios with a very theoretical approach. Additionally, most previous work is focused on scenario prediction based on control variables. Data variable based prediction is however necessary in many dynamic systems. In this work, the dynamic CPU and memory requirements are found for a set of applications through profiling and code inspection. Both data and control variables that cause dynamism are recognized. The considered applications are three of the SPEC2006 integer benchmarks, in addition to a prime number detection application. The procedure for detecting CPU and memory dynamism is somewhat generalized and suggested as an extension to the original system scenario identification step. A slightly modified version of the traditional system scenario methodology is further used to develop system scenario implementations. The modifications come as a consequence of the dynamism to be exploited and the nature of the applications.

The traditional system scenario methodology is well described for one-dimensional dynamism [6]. The complexity of identifying the scenarios and optimizing the platform does however increase drastically when adding more dimensions to the cost function. E.g., the memory energy consumption modelled in [13] depends on the execution time, so that introducing DVFS into the memory scenario design will also affect the memory energy. This report presents a methodology that is closely related to the traditional methodology [6], but with some modifications in order to better deal with multi-dimensional dynamism. The methodology is developed and presented using DVFS and dynamically reconfigurable memory, but other system knobs can also be used.

The whole process is described, from identifying the benchmarks that are the most promising candidates for system scenario development, to the actual results of such scenario implementations. The objective with the implementations is to achieve significant reductions in energy consumption through dynamic run-time reconfiguration of the platform, while preserving the performance requirements (deadlines). It is demonstrated how both data variables and control variables can be used to detect/predict scenarios, and how these variables can be found through profiling and code inspection. A considerable amount of the work is related to the design-time scenario exploration and exploitation steps, in which the optimal system settings are found.

#### The following list summarizes the contributions of this work:

- Evaluation of the suitability of Intel Pentium M for system scenario-based DVFS. Maximum CPU energy reduction through DVFS is estimated to 34%.

- Methods for finding CPU and memory dynamism using various profilers.

- Adaptations of the traditional system scenario design methodology in order to identify and exploit multi-dimensional dynamic behavior, targeting CPU and memory dynamism specifically.

- Algorithms for exploring and exploiting the possible platform configurations.

- Analysis of the CPU dynamism in a prime number checking application. The developed system scenario implementation reduces the CPU energy consumption with 20.2% compared to a static implementation.

- Delayed scenario prediction through loop unrolling to reduce the rate of scenario mispredictions. Demonstrated on the prime number checker.

- Analysis of the CPU and memory dynamism in three SPEC CPU 2006 applications. Suggested system scenario implementations obtain energy reductions up to 31.2%.

#### **1.2** Report structure

The rest of the report is structured as follows: First, the results of a literature survey on system scenarios, DVFS and dynamic memory configurations are presented in Chapter 2. Chapter 3 describes the memory and CPU models of the assumed platform and briefly outlines the profilers that are used. Chapter 4 presents the general methodology that is used for identifying, exploring and exploiting dynamic behavior, with special focus on the deviations from the original methodology. Chapter 5 describes each of the applications that are studied and the system scenario design decisions and assumptions that are made. The resulting system scenario implementations with corresponding energy reductions are also presented in this chapter. Chapter 6 discusses the presented methods and results, and suggests future work. Finally, Chapter 7 concludes the report.

### Chapter 2

### Theory and previous work

#### 2.1 System scenario design methodology

The design process for energy efficient dynamic systems can get quite complex, so following a general design methodology can be useful. In this section, the system scenario design methodology is presented thoroughly.

Gheorghita et al. defines system scenarios as follows[6]:

System scenarios group system behaviors that are similar from the multidimensional cost perspective, such as resource requirements, delay and energy consumption, in such a way that the system can be configured to exploit this cost similarity.

A dynamic embedded system typically has varying execution costs depending on the input and the state of the system. If the functions describing these variations are not known at design-time the system must be implemented based on worst case costs. By utilizing a scenario driven design process however, the dynamic properties of the embedded system can be identified and accounted for already in the the design-phase, which makes it possible to exploit the dynamism at run-time. This two-phased partitioning is a characteristic feature of the system scenario methodology.

The methodology and terminology presented in this section is based on work by Gheorghita et al. [5, 6].

#### 2.1.1 Design-time

At design-time, the systems behavior is analyzed and classified from a possibly multidimensional cost perspective, that usually involves energy consumption and workload. The system's behavior is divided into Run Time Situations (RTSs) that can be recognized through run-time observable variables (RTS parameters). The system execution is thus a sequence of RTSs. A dynamic system typically has many different RTSs, and each of these can be identified and treated as units with associated costs. The number of RTSs can however be enormous even for simple systems, which is why RTSs with similar costs should be grouped together in a *System scenario*.

At run-time, the next scenario to be executed is predicted from the RTS parameters; a set of system parameters that can be both data and/or control-related. By recognizing a scenario *before* its execution, the system can be configured for optimal execution of this particular scenario. The optimization happens by adjusting so-called *system knobs*, which are hardware or software settings that can be changed at run-time. Some examples are:

- Supply voltage

- Clock frequency

- Mapping to processing elements

- Memory organization

- Code transformations

- Executing different versions of the code (e.g. compiled with different optimization settings)

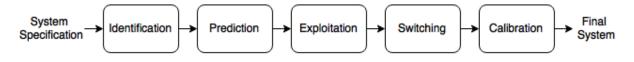

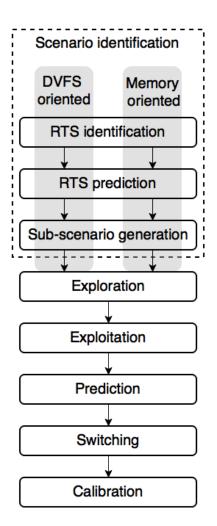

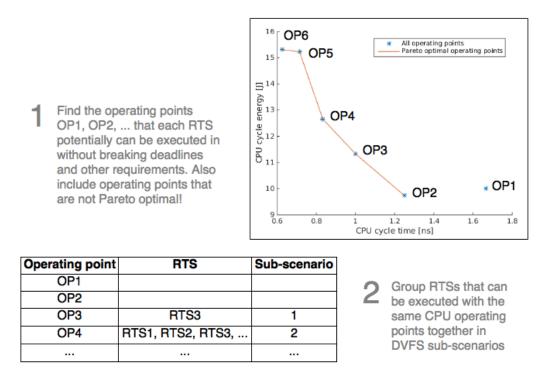

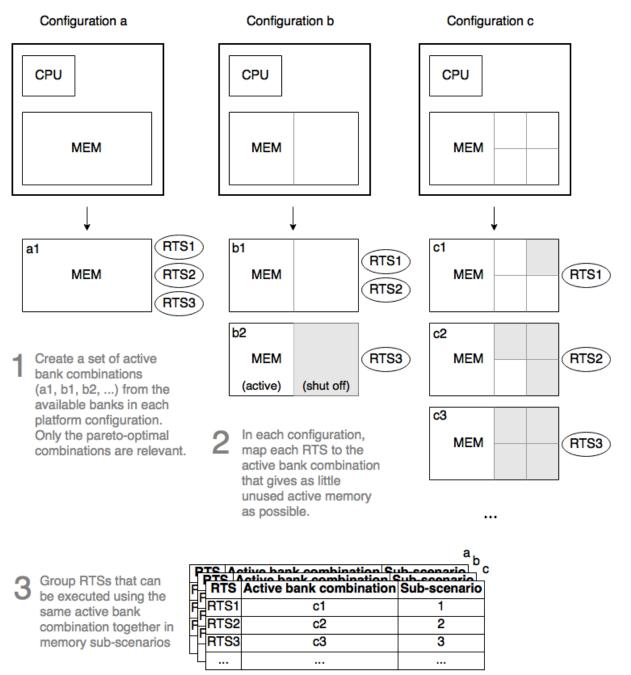

From a system specification to a final system, the design-time phase can be divided into the steps shown in Figure 2.1. Following is a description of each of these steps.

Figure 2.1: Overview of the system scenario methodology at design-time. Simplification of figure from [5, p.19].

#### Scenario identification

The identification step can be divided into RTS parameter discovery and RTS clustering. The RTSs are discovered through profiling and code inspection, and the relevant RTS parameters are selected. Extensive profiling may be necessary to discover how the dynamic nature of a complex application is best exploited. By evaluating the application's RTSs thoroughly at design-time, one can avoid spending unnecessary run-time resources on detecting dynamism. Scenarios are constructed by clustering the RTSs that have similar costs. The overhead costs and frequency of occurrence should be considered, to the extent that is possible at such an early stage.

Detecting *every* possible RTS at design-time might be impossible (or at least infeasible) for complex systems, which motivates the need for a backup scenario. This scenario will typically have high performance so that it can accommodate for any given situation. By implementing a backup scenario the system can give hard guarantees even for unforeseen behavior.

#### Prediction/detection

To be able to configure the system before a scenario occurs, a scenario predictor that can run along-side the application at run-time must be developed. The predictor will monitor the selected RTS parameters and from these determine the optimal future system scenario. The quality of this predictor must be traded off against the run-time prediction overhead. Should the prediction fail, the mentioned backup scenario can be used.

#### 2.1. SYSTEM SCENARIO DESIGN METHODOLOGY

For systems where all possible RTSs have been identified and the prediction function is applied after all RTS parameters are known, the prediction accuracy will be 100%. This is called scenario *detection*. Often the scenarios will be detected too late when using this approach.

Developing a predictor/detector might influence the already determined scenario set, e.g. some of the scenarios may be too difficult to recognize. The scenario set should therefore be re-evaluated and maybe redefined. The energy consumption of the predictor/detector depends on the exact implementation. A few alternatives are somewhat discussed in Section 3.3.

#### Exploitation

After a predictor has been developed, the optimal application and platform settings that should be applied for each scenario must be found. A scenario should not be optimized completely independent of the rest of the scenario set, but with the scenario switching in mind. Otherwise, the system configurations for each scenario may become too different to even allow run-time switching. Several scenarios are typically combined in this step and the RTSs might even have to be completely remapped to the scenarios now that the actual configuration options are known.

#### Switching

Based on the obtained scenario prediction and exploitation, smart and effective mechanisms for switching between the scenario configurations must be developed. Switching to a better suited scenario may not always be a good idea. The gain of the scenario switch must be weighted to the associated costs of switching. The amount of time in which this new scenario will be optimal has much influence on the decision, as well as the necessary overhead it takes to do the switching. This can vary a lot depending on the actual configurations that must be made. E.g., frequency scaling, voltage scaling or changing the state of a memory bank (active, sleep, shut down) will all require different amounts of time and energy. It may again be necessary to reconsider the scenario set now that the switching overhead can be taken into account. Maybe some scenarios must be merged because of the associated switching costs.

#### Calibration

Some scenario systems also include a *Calibration* step. At design-time, a calibration routine is then developed, which can evaluate the current set of scenarios by observing how the system performs at run-time. In case some unforeseen behavior must be incorporated into the scenario set, the calibration routine can add, remove or change the system scenarios.

#### 2.1.2 Run-time

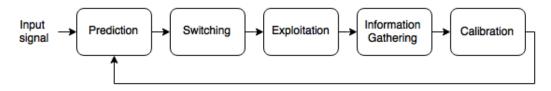

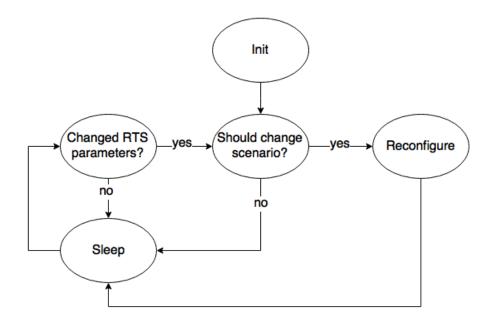

At *Run-time*, the classification found at design-time is used to take advantage of the dynamism of the system. The identified set of RTS parameters are monitored so that the system scenario of the predicted RTS can be selected. The run-time phase can be

organized quite similarly to the design-time phase, as shown in Figure 2.2. Following is a description of each of these steps.

Figure 2.2: Overview of the system scenario methodology at run-time. Simplification of figure from [5, p.19].

#### Prediction

Based on actual RTS parameter values, a scenario is selected from the pre-determined scenario set. The parameter evaluation can be continuous, periodic or event-triggered.

#### Switching

If the predicted scenario is different from the current, and if the cost of switching to this scenario is lower than the benefit of this scenario, the switch should be performed.

#### Exploitation

At run-time, this step simply involves running the system with the optimal system scenario settings, so that the current state of the application is exploited.

#### Information Gathering and Calibration

In complex and very dynamic systems, a calibration routine can be used to further optimize the scenarios. The calibration should happen sporadically, based on run-time statistics found by information gathering mechanisms.

#### 2.1.3 Cost

Within each scenario the system configurations are fixed, meaning that all RTSs in a given scenario will have the same expected cost. The resource usage of this scenario must be sufficient for the worst-case RTS of the scenario, which means that this worst-case RTS determines the expected cost of all the situations within its scenario. Usually, one or more of the following costs are considered:

- Processing cycles

- Energy consumption

- Memory accesses

- Heat production

- Expected quality of result

- Timing/deadlines and cost of missing deadlines

If the cost is a sum of several variables, it can be represented as a weighted sum or as an N-dimensional Pareto set. The latter is more difficult to implement, but might be advantageous with a multidimensional cost in order to avoid inconsistencies and suboptimal scenario sets [5, p.19].

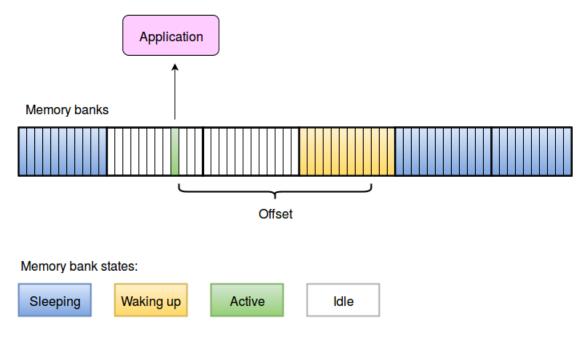

#### 2.1.4 Memory-aware system scenarios

Filippopoulos et al.[12, 13] proposes memory-awareness as an extension to the established system scenario methodology, by including memory costs in the design exploration. Using this extended methodology on an epileptic seizure predictor and a Viterbi encoder they are able to reduce the memory energy consumption with 40 to 70%[12]. The memory access pattern and data reuse size are some of the characteristics that are used to identify RTSs. In [13] the methodology is demonstrated on a set of multimedia benchmarks, resulting in a reduction of 35 to 55% in memory energy consumption. An extended memory model with state-of-the-art memories is presented and used for the scenario exploration. Different system knobs are suggested to be used in a memory-aware system scenario design methodology; e.g., mapping data to different memory banks, turning on and off memory banks, employing memory sleep modes, and tuning the operating frequency exactly to the access frequency needed.

#### 2.1.5 Task Concurrency Management (TCM)

TCM is a methodology closely related to the system scenario methodology. TCM is developed by IMEC and its partners [17], addressing the problem of mapping dynamic and concurrent tasks on multiple processors for energy-constrained real-time embedded systems. To adapt the scheduling to the dynamism in the tasks, the scheduling is split into two phases; design-time and run-time scheduling. As already described, this twophased strategy is also characteristic for the system scenario methodology. Following is a summary of the main TCM concepts, adapted from [17].

#### TCM Work flow

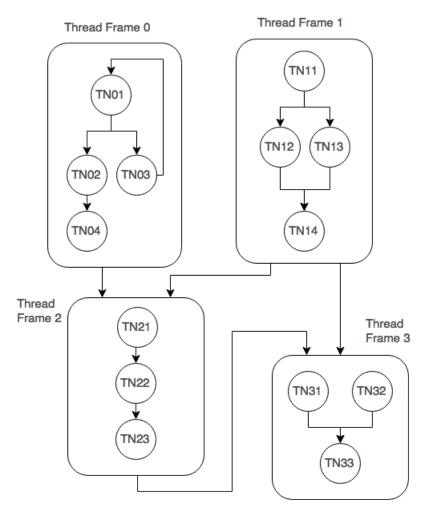

Four separate stages make up the TCM work flow; gray-box system model construction (system-level modelling), concurrency improving transformations (system model optimization), design-time scheduling and run-time scheduling. At the high-level specification, the application is represented as a set of Thread Frames (TFs). Each TF is partitioned into a set of Thread Nodes (TNs). These are the basic low-level scheduling units. The methodology then seeks to schedule the TNs onto a set of homogeneous or heterogeneous processors, both cost-optimal and constraint-driven.

#### Gray-box modelling

A Multi-Task Graph (MTG) model is created at design-time (first step). This is a twolevel hierarchical task graph, specifying the application at a gray-box abstraction level. The intention of the gray-box model is to hide irrelevant parts of the code, i.e. parts that are deterministic and independent of input or situation, making it easier to focus on the non-deterministic, dynamic parts. This technique can be very useful when identifying dynamic behavior in system scenario design if the application code is complex.

Neither the classic black-box or the white-box models are suited to represent an application during TCM. The abstraction level needs to be something in between; hence the gray-box model is used. The gray-box model has two abstraction levels, as shown in Figure 2.3. At the high-level, the model represents the application by dividing it into a set of TFs. These are typically functions (or several functions), and must not contain any non-deterministic external interactions. At the lower level, the gray-box model partitions the TFs into TNs, which are characterized by constant execution times and energy consumptions, and are therefore considered as black-boxes. The TFs however are considered as white-boxes, as all of their internal structures are visible in the model. The dynamic behavior inside these TFs can be captured in system scenarios. The hierarchical combination of white- and black-boxes makes up the gray-box model [17].

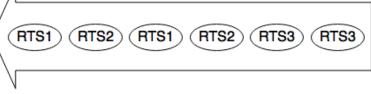

Figure 2.3: Example of how the thread frames and thread nodes can be organized in a gray-box model. Simplification of figure from [17, p.50].

According to [17], TFs and TNs are typically identified as follows: All dynamic task creation, explicit synchronization and external trigger events are identified. These are the

boundaries of the TFs, and so the TFs are found between these events, typically wrapped by functions. The TFs should be maximally sized pieces of functionality. To identify TNs, some insights of how the application works is necessary. A TN is a maximal set of connected operations where the worst-case behavior and actual behavior are similar enough, giving a somewhat deterministic execution latency. Deciding the TN granularity is however a complex task, and the reader is referred to [17] for a more detailed description.

#### Two-phase scheduling

Pareto curves of the TFs and their Pareto-optimal schedules of TNs are generated at design-time, and the run-time scheduler simply dispatches specific schedules instead of generating schedules on the fly. This is the essence of two-phase scheduling. The run-time scheduling will happen at the granularity of TFs. When a new TF is initiated because of external events, the scheduler selects active scenarios from the input data, and schedules them so that deadlines are reached and energy consumption is within a constraint[17, p. 48]. By separating the design-time and run-time scheduling the system becomes more flexible at run-time, and can to some extent accommodate for unforeseen timing demands. By selecting the optimal combination of Pareto points the energy cost of a specific timing constraint usually spanning multiple TFs can be minimized. The computation complexity and overhead at run-time are also minimized.

#### 2.2 Scaling frequency and voltage

The next section describes dynamic frequency and voltage scaling and thus gives a theoretical foundation and motivation for some of the system configurations performed. Before going into the theory of Dynamic Voltage and Frequency Scaling (DVFS), some important power and energy equations are presented in the current section. These equations will also be used in Section 3.1.1 to create a CPU power model.

#### 2.2.1 Power and energy

The power dissipated in a two-terminal element at any time is given by the product of the voltage v(t) across its terminals and the current i(t) running through it:  $p(t) = v(t) \cdot i(t)$  [18, p. 16, p.27, p.595]. Correspondingly, the average power consumption P of an electronic system is given by Equation 2.1, where I is the average current and V is the supply voltage.

$$P = I \cdot V \tag{2.1}$$

Power is by definition the rate at which energy is consumed [18, p. 17], so by multiplying the average power P with some time interval T, the total energy is found:

$$E = P \cdot T \tag{2.2}$$

Total power P dissipated per time by an integrated circuit can be expressed as the sum of static power  $P_{static}$  and dynamic power  $P_{dynamic}$  [19], as shown in Equation 2.3.

$$P = P_{dynamic} + P_{static} \tag{2.3}$$

Static power is consumed whenever the circuit is powered, regardless of circuit activity, while the dynamic power results from charging and discharging of capacitors [18, p.603]. In logic gates, the static power dissipation  $P_{static}$  is proportional to  $V^2$ , according to the simplification given in [18, p. 604]. Static power is also proportional to the leakage current  $I_{leak}$ :

$$P_{static} = V \cdot I_{leak} \tag{2.4}$$

$I_{leak}$  is the current that leaks through transistors that are switched off. It exists whenever the chip is powered, but is independent of frequency [20]. The leakage is mainly set by the sub-threshold current of the transistor, which depends on threshold voltage, channel physical dimensions,  $V_{DD}$  and many other factors [21]. Leakage current is rather complex to model, and is not investigated further here.

Dynamic power on the other hand is more straightforward, and can be expressed as shown in Equation 2.5[19, 18].

$$P_{dynamic} = V \cdot I_{dynamic} = A \cdot C \cdot V^2 \cdot f \tag{2.5}$$

A is the activity factor, C is transistor gate capacitance, V is the supply voltage and f is the operating frequency. As the voltage is squared, reducing this factor leads to a significant dynamic power reduction. Dynamic power scales linearly with frequency.

By combining Equation 2.4 and Equation 2.5 and multiplying with a time interval T, we can calculate the energy consumption of a chip as shown in Equation 2.6 and Equation 2.7.

$$E = P \cdot T = (P_{dynamic} + P_{static}) \cdot T = (AC \cdot V^2 \cdot f + V \cdot I_{static}) \cdot T$$

(2.6)

$$E = P \cdot T = V \cdot I \cdot T = V \cdot (I_{dynamic} + I_{static}) \cdot T$$

(2.7)

DVFS has the potential to reduce both static and dynamic power dissipation as both sizes depend on voltage and/or frequency.

#### 2.2.2 Without static power

By assuming that the static power is very small relative to the dynamic power (which can be true for high frequency operation [19]), the energy equations can be simplified:

$$E = P \cdot T = P_{dynamic} \cdot T = AC \cdot V^2 f \cdot T \tag{2.8}$$

The frequency can be written as f = cycles/T, where cycles is the number of clock cycles used during time T. This gives:

$$E = AC \cdot V^2 \cdot cycles \tag{2.9}$$

Note that this equation is independent of time and frequency.

#### 2.2.3 With static power

The potential energy savings from DVFS are not necessarily that straightforward. Recent developments in processor and memory technologies have made the ratio of dynamic power to static power smaller, so that optimizing voltage and frequency to reduce the dynamical power consumption makes less overall impact. Processor clock frequencies are more saturated, sleep modes are improving, and the dynamic power range is decreasing[9]. All of these developments limit the potential power reductions from DVFS. Experimental results also show that the gains from DVFS are smaller than predicted by simplistic power models like that in Equation 2.9 [19, 9].

By including the power consumption due to leakage current (Equation 2.4), the energy calculations get a lot more complicated, and the time T spent on a task has to be taken into account.

#### 2.3 Dynamic Voltage and Frequency Scaling

DVFS is a well-known technique for reducing energy consumption while meeting the performance requirements of dynamic applications. By changing the frequency and voltage of the CPU dynamically, the performance can be adjusted to the current workload. Dynamic Frequency Scaling (DFS) and Dynamic Voltage Scaling (DVS) are variants of this.

To determine a suitable scaling factor, it is important to know how much power the system uses while performing a given task at different operating points, as well as the time the system is allowed to spend doing it. Information like task arrival time, deadline, and workload, are usually not known in advance with general-purpose computing systems, but with embedded systems they might be, which makes a good foundation for system scenario-based design. Traditional DVFS systems tend to work either fully dynamically, only based on run-time information [22, 23] or statically based on design-time analysis [24]. System scenario-based DVFS is a combination of these approaches. Equation 2.9 in the previous section shows that the energy from dynamic power scales quadratically to the operating voltage, so a lot of energy can be saved by adjusting this factor. Equation 2.9 also shows that dynamic energy is unaffected by reducing the frequency, but if the increased execution time can give less waiting time for the next task, there will be less energy spent while waiting.

The frequency reduction can happen when CPU cycles would otherwise be wasted, e.g., when the CPU is waiting on peripherals. The resulting power reduction must be sufficient to both make up for the time it takes to switch and for the extra time it takes to run the task at a lower frequency. Without being able to reduce voltage, lowering the frequency is not likely to lead to a reduction in energy. It can be seen from Equation 2.9 that when assuming no static power, the energy consumption is not dependent on time or frequency, so with constant voltage the energy is actually constant for a given task, no matter how fast it is performed. The only difference between performing a task fast and slow is thus the energy consumed while waiting for the next task (idle time). The energy contribution from static power is independent of frequency [20], but increases linearly with the execution time (Equation 2.7). However, when voltage is also reduced, a significant energy impact can be obtained due to the  $V^2$  factor in the dynamic power equation. Exactly how much a voltage reduction impacts the total power consumption of a platform varies from system to system. There are many publications on this, but most are using quite platform-specific models [10, 11, 19].

Snowdon et al. describes in [10] a model that can predict the execution time and power consumption at any voltage-frequency operating point, given the workload execution at another voltage-frequency operating point, on a low-power embedded platform. The model is based on using the platform's performance counters, which monitor and count certain events at run-time, e.g., bus transactions and CPU stall cycles. It is concluded that the limited number of performance counters cannot capture the whole system behavior. Proper model calibration is therefore essential for accurate results.

Castagnetti et al. [19] show that energy can be saved using DVFS, but that the gains are much smaller than the simplistic models predict, as there is a portion of the power consumption of the chip that does not scale with the frequency. Reducing the processor frequency leads to reduced energy dissipation in the core, but the increased execution time can also result in increased energy consumption from other components. Miyoshi et al. [25] analyzes the run-time effects of frequency scaling on performance, power and energy. Their results show that when voltage is kept constant, on a PowerPC-based embedded system it is more energy efficient to run at a low frequency, while on a Pentium-based high performance PC system, it is more energy efficient to run at the highest performance state (Race to Idle). This is explained by introducing a metric called *Critical power slope*. This metric determines whether it is beneficial to run fast and wait in idle-mode, or to run slow and thus minimize idle-mode time. Voltage scaling is also discussed to some extent.

#### 2.4 Memory organizations

Memory organization has been recognized as an important design topic when it comes to reducing energy consumption. In general, memory contributes considerably to the total system energy consumption; from 35% to 65% for different architectures according to [13]. This section briefly describes some of the techniques that are used to increase the performance and reduce the power consumption of memories today.

The fast advances within processor performance during the last few decades has lead to a big gap between processor and memory bandwidth [26]. The introduction of *memory hierarchies* has become the major resolution to this problem. A memory hierarchy provides a smart compromise between fast and big memories by organizing memories with different speed and sizes into different levels. Fast memories are expensive, so they are kept small and located close to the CPU. Further away from the CPU, the memories become slower and larger. Smart strategies are used to keep the data that is most likely to be accessed close to the CPU. Usually, the data contained in each level is a subset of the next lower level. The *cache* is at the highest level of the memory hierarchy, i.e. it is the memory closest to the processor, except the processor's internal registers. There can be several cache levels, with increasing access times and sizes as we move down the hierarchy, but all the cache levels are usually integrated on the processor chip. Hardware controlled cache hierarchies are typically incorporated in today's high-end embedded processors [17]. The next level down in the hierarchy is the main memory.

Scratchpad memories can be used as an alternative to cache hierarchies. A scratchpad memory is similar to a level one cache as it is the memory closest to the CPU apart

from the internal registers. As opposed to caches however, there is usually no copy of the scratchpad data in the main memory, so that the memory access latencies are determined by where the data is stored. A system using scratchpads will therefore have non-uniform, but predictable memory access latencies. A cache hierarchy system on the other hand will typically have homogeneous access latency, but with an uncertainty associated to how far down in the hierarchy the data must be searched for. The required logic for a scratchpad memory is significantly less than for a cache of the same size [17]. So far, the scratchpad memories have not made it to mainstream processors, but they can be found in embedded systems and special-purpose processors such as GPUs. [26].

A tendency is to design more domain specific and heterogeneous memory architectures, e.g. by making use of scratchpads. With such architectures, the memory access time usually depends on the location of the relevant memory relative to the processor, which is why they are classified as Non-Uniform Memory Access (NUMA) architectures. It is predicted that these designs will become important in the future [27]. Deciding where to map data becomes a more difficult task that has to be handled by the designer or compiler, but much energy can be saved if one is able to exploit the heterogeneity [17, p. 197]. As demonstrated in [12], this can be achieved through the system scenario methodology.

Many modern memory systems support different power modes and power gating, so that memory banks can be either shut off completely, or put in sleep modes on an individual basis. There are SRAM memories that can be put into retention states to save power while not erasing data. Alternatively they can be shut off completely to save more power, but without keeping the data. It is predicted that leakage currents will become a dominant source of energy consumption [4, 17]. By introducing memories that support several energy states, e.g., standby, sleep and power down, at least the memory leakage power can be reduced drastically. A memory architecture is described in [17, p.197-200] where the memory is partitioned into memory sub-arrays, with energy states that are managed by a hardware controller. It takes ten cycles to wake up a memory sub-array from a sleep state, in which the energy consumption is 162 times less than in standby state. An overview of the current state of reconfigurable memory can be found in [28]. It has been shown that accessing data in smaller memories requires less energy than big memories, which is a good argument for partitioning memory into several memory banks. Additionally, this enables a parallelization of memory accesses, and more fine-grained control of memory sleep states.

The memory use characteristics of an application can have big variations, e.g., in the number of loads and stores, and the size and use of currently allocated memory. Being able to exploit the dynamic memory requirements of an application can therefore lead to big energy reductions which can have a considerable effect on the total energy consumption. The way data is assigned to available memory banks is an important aspect, affecting both the energy per access, the possibility of data conflicts, and the number of banks that must be active. Techniques for estimating the required memory size to store concurrently alive elements in an application are presented in [29]. Filippopoulos et al.[13] use detailed memory models to construct a reconfigurable memory platform. Applications are analyzed at design-time to identify different execution paths that cause variations in memory usage. An algorithm for exploring different memory organizations is also presented. This algorithm uses Equation 2.10 to calculate the overall energy consumption of all memory banks in a configuration:

$$E = \sum_{all}^{memories} (N_{rd} \cdot E_{Read} + N_{wr} \cdot E_{Write} + (T - T_{LightSLeep} - T_{DeepSLeep} - T_{ShutDown}) \cdot P_{leak_{Active}} + T_{LightSleep} \cdot P_{leak_{LightSleep}}$$

$$+ T_{DeepSleep} \cdot P_{leak_{DeepSleep}} + T_{ShutDown} \cdot P_{leak_{ShutDown}} + N_{SWLight} \cdot E_{LightSleepToActive} + N_{SWDeep} \cdot E_{DeepSleepToActive} + N_{SWShutDown} \cdot E_{ShutDownToActive})$$

$$(2.10)$$

$N_{rd}$  and  $N_{wr}$  are the numbers of reads and writes, where the corresponding energy is given by  $E_{Read}$  and  $E_{Write}$ . T is the total time, and  $T_{LightSLeep}$ ,  $T_{DeepSLeep}$  and  $T_{ShutDown}$ are the time intervals spent in each of the sleep and shut down modes. Correspondingly,  $P_{leak_{Active}}$ ,  $P_{leak_{LightSleep}}$ ,  $P_{leak_{DeepSleep}}$  and  $P_{leak_{ShutDown}}$  are the power consumptions of the modes.  $N_{SWLight}$ ,  $N_{SWDeep}$ ,  $N_{SWShutDown}$  are the number of switches to active state, where the energy of each switch are given by  $E_{LightSleepToActive}$ ,  $E_{DeepSleepToActive}$  and  $E_{ShutDownToActive}$ . Note that the memory energy consumption in Equation 2.10 depends on the execution time, so that introducing DVFS into the scenario design will affect the memory energy.

#### 2.5 SPEC CPU 2006

SPEC CPU<sup>TM</sup> 2006 [15] is a benchmark suite developed from real-life applications and workloads. It is intended as a measure for comparing computational intensive performance across a wide range of hardware. A variety of different benchmarks are included for measuring the performance of a system's processor, memory subsystem and compiler. Composing a representative workload was important to the designers of the SPEC benchmark [15]; the workload has to be both diverse enough to capture relevant run cases, and at the same time relatively compact as even high-level architectural simulations are time consuming. The size, both in terms of bytes of code and number of instructions varies a lot (some of the benchmarks are in the range of a few trillion instructions[30]). The benchmark suite can be divided into integer benchmarks (SPECint®2006) and floating point benchmarks (SPECfp®2006), consisting of 12 and 19 benchmark tests respectively. In [31], all the benchmarks are characterized and analyzed in terms of instruction composition and performance, viewing the workload from each benchmark as a whole.

#### 2.6 Other related work

As mentioned, Borkar et al. [4] predicts a trend towards heterogeneous microprocessors. Transistor size can still be decreased, but the transistor threshold voltage and thereby also the transistor power can not. To still be able to improve power and performance characteristics, a solution is to include processing elements with different power and performance characteristics on a chip. Then the most optimal processing element can be chosen to execute a task or application, while the unused processing elements are powered off. The cost of moving data will have a critical effect on the achievable performance of such a system. Data must be moved efficiently up and down the memory hierarchy, as well as between processing elements that are used. When the supply voltage is downscaled, and thereby also the frequency, the energy spent on moving data becomes more dominant. This effect can be reduced by keeping data as local as possible to the processor, e.g. by increasing the register and cache sizes. This is contrary to the general idea of keeping registers small and fast, but it makes sense with a downscaled CPU frequency[4]. Borkar et al. also recommends DVFS for smaller cores used for throughput, but not large cores as it would "dramatically reduce single-thread performance".

The activity patterns of servers seem promising for system scenario design. According to Barroso et al. [32] servers usual operate at 10-50% of maximum utilization. Being completely idle or operating near the level of maximum utilization is very rare. The energy efficiency at the most common operating point (20-30% utilization) is actually less than half the energy efficiency at peak performance, which indicates a mismatch that must be addressed. The CPU fraction of total server power is however no longer dominant, so it is important that a power down-scale can happen also at the other components, e.g., network switches, disk drives and DRAMs. Disk drives are unfortunately infeasible to spin-down due to the latency and energy penalties of spinning them up again [32].

DVFS is a well-documented power saving technique, but run-time dynamic application is limited, and the development with complex platforms, transistor scaling and improved idle/sleep modes reduces its relevancy. In [9] it is even predicted that manufacturers will abandon DVFS in favour of ultra low-power sleep modes. However, by applying the DVFS technique within a system scenario environment, the shortcomings can be alleviated.

Many applications have resource requirements that are more or less platform-dependent due to different instruction sets, functional units and more. To avoid getting tied to one specific platform, Hamers et al. [33] suggests two different ways of characterizing an application: Using domain knowledge or automated characterization. Using domain knowledge means to use ones understanding of an application to identify what causes its dynamism. E.g. for a H.264 video stream decoder, the size of a frame causes differences in the workload independently of the platform, and is therefore used as a relative measure on performance requirement. Automated characterization requires only limited domain knowledge. A functional execution profile of each frame is collected using an instrumented platform that records the control-flow behavior at run-time. This characterization is datadependent, and not platform-dependent [33].

# Chapter 3 Platform and profilers

Selecting a suitable platform is crucial in the system scenario design methodology. The platform should be highly configurable, even at run-time, while being able to meet the demands of the application. In this work, a platform with only one computational unit is considered. Having several independent computational units allows for much more flexibility; tasks might be scheduled to different cores depending on required performance, and cores can be turned on and off depending on current (and future) application requirements.

#### 3.1 Intel Pentium M

An Intel Pentium M processor is used as reference processor in this work. Pentium M is a family of 32-bit x86 single-core microprocessors that are well suited for DVFS [34]. The current and future generations of Intel Pentium M Processors support the *SpeedStep Technology*. This technology allows the application software to control the operating frequency and voltage of the processor in order to adapt the CPU performance to changing workload and requirements.

Table 3.1 shows the available frequency and voltage combinations of Intel Pentium M. These are from now on referred to as *operating points*. The processor core unavailability time is  $10\mu$ s for a change of operating point [34].

| Frequency [GHz] | Voltage [V] | TDP [W] |

|-----------------|-------------|---------|

| 1.6             | 1.484       | 24.5    |

| 1.4             | 1.420       |         |

| 1.2             | 1.276       |         |

| 1.0             | 1.164       |         |

| 0.8             | 1.036       |         |

| 0.6             | 0.956       | 6       |

Table 3.1: Intel SpeedStep operating points as provided by [34]. TDP is explained in Subsection 3.1.1

#### 3.1.1 Power estimations

The only power characteristics found for Intel Pentium M is the Thermal Design Power (TDP). TDP is defined as the peak thermal power, and is typically used when designing CPU cooling systems. The TDP is not necessarily the same as the maximum power; it is possible for the processor to consume more than the TDP for a time interval short enough to make it "thermally insignificant" [35]. In [36], the TDP of a set of processors is compared to the geometric mean power consumed with a suite of server workloads. In average, the TDP is 30% higher than the mean power consumption. The relative CPU power reductions presented in this work are calculated based on the assumption that the average power consumption will be proportional to the TDP at each operating point. Unfortunately, Intel only gives the TDP of 1.6GHz and 0.6GHz operation. According to [34], the dissipated power will be approximately proportional to the square of the voltage between these operating points. This statement could not be verified for the given TDP values, probably because it is based on a simplified power equation that does not account for static power (Equation 2.5). The remaining TDP values are therefore calculated more accurately in the rest of this subsection. The following assumptions are made:

- $TDP = AC \cdot f \cdot V^2 + P_{static}$  (Equation 2.3 and 2.5)

- $AC = k_1$  is constant

- $P_{static}$  is proportional to  $V^2$  (very simplified; see Section 2.2.1), i.e.  $P_{static} = k_2 \cdot V^2$ where  $k_2$  is a constant

This gives:

$$TDP = AC \cdot f \cdot V^2 + P_{static} \tag{3.1}$$

$$=k_1 \cdot f \cdot V^2 + k_2 \cdot V^2 \tag{3.2}$$

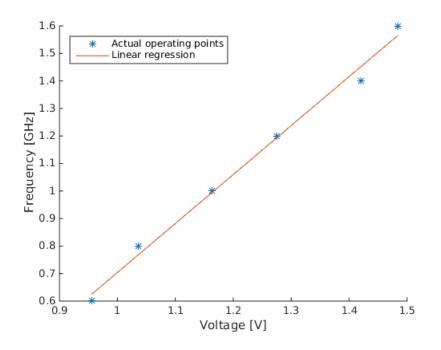

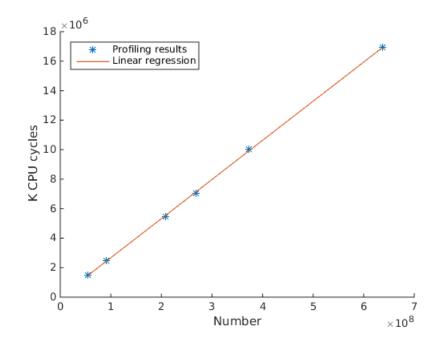

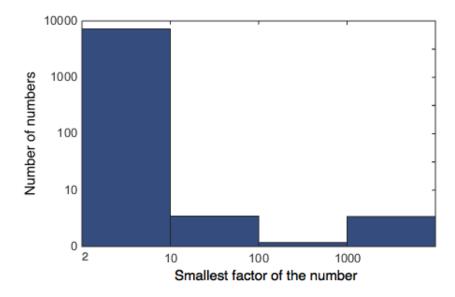

The operating voltages increases almost linearly with increased frequencies, so the relationship between voltage and frequency is simplified through linear regression to the expression shown in Equation 3.3 and Figure 3.1. All calculations are made with frequency in GHz for better readability.

$$f = 1.779 \cdot V - 1.075 \qquad [\text{GHz}] \tag{3.3}$$

By inserting Equation 3.3 into 3.2 the following expression is found:

$$TDP = k_1 \cdot (1.779 \cdot V - 1.075) \cdot V^2 + k_2 \cdot V^2 \tag{3.4}$$

$$= k_1 \cdot 1.779 \cdot V^3 + (k_2 - k_1 \cdot 1.075) \cdot V^2 \tag{3.5}$$

$$=k_3 \cdot V^3 + k_4 \cdot V^2 \tag{3.6}$$

Then, by using these two conditions from Table 3.1;

$$TDP = 24.5$$

when  $V = 1.484$

$TDP = 6$  when  $V = 0.956$

Figure 3.1: Linear regression of Intel Pentium M operating points.

$k_3$  and  $k_4$  are found:

$$k_3 = 8.636 \tag{3.7}$$

$$k_4 = -1.691 \tag{3.8}$$

This gives:

$$TDP = 8.636 \cdot V^3 - 1.691 \cdot V^2 \tag{3.9}$$

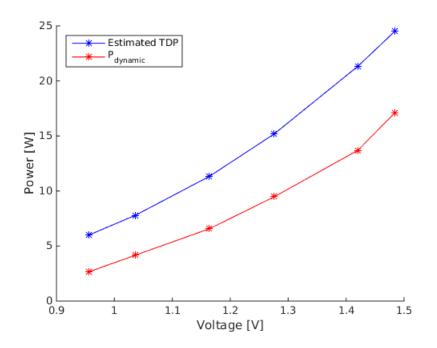

Alternatively, if assuming that the static power consumption can be neglected, the power consumption at each operating point can be calculated using Equation 2.5 ( $P_{dynamic} = AC \cdot f \cdot V^2$ ). The AC product found from the TDP calculations is used ( $k_1 = 4.85$ ), as well as the voltage-frequency pairs given in Table 3.1. Figure 3.2 compares this  $P_{dynamic}$  to the estimated TDP of Intel Pentium M.

| Frequency [GHz] | Voltage [V] | TDP [W] |

|-----------------|-------------|---------|

| 1.6             | 1.484       | 24.5    |

| 1.4             | 1.420       | 21.3    |

| 1.2             | 1.276       | 15.2    |

| 1.0             | 1.164       | 11.3    |

| 0.8             | 1.036       | 7.8     |

| 0.6             | 0.956       | 6.0     |

Table 3.2: Intel SpeedStep operating points with the estimated TDP.

Given perfect conditions (e.g. no waiting for memory or synchronization) the CPU's energy consumption when running an application can be reduced significantly by using

Figure 3.2: Estimated TDP of the Intel Pentium M operating points compared to calculated  $P_{dynamic}$

the low-power operating points. As shown in Equation 3.13, if the lowest performance operating point is used instead of the highest, the CPU energy consumption is reduced with 34.7%. If the increased execution time means reduced idle time (e.g., waiting for synchronization or peripherals), the energy reductions will be even bigger.

$$E = P \cdot T = P \cdot \frac{cycles}{frequency} \tag{3.10}$$

$$E_{highPerformance} = 24.5 \cdot \frac{cycles}{1.6 \cdot 10^9} = cycles \cdot 15.3125 \cdot 10^{-9}$$

(3.11)

$$E_{lowPerformance} = 6 \cdot \frac{cycles}{0.6 \cdot 10^9} = cycles \cdot 10 \cdot 10^{-9}$$

(3.12)

$$\left(1 - \frac{E_{lowPerformance}}{E_{highPerformance}}\right) \cdot 100\% = 34.7\% \tag{3.13}$$

It is here assumed that the number of CPU cycles (cycles) is constant, regardless of the operating point.

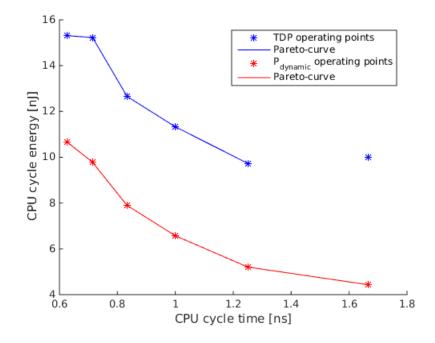

The operating points of the Intel Pentium M can also be presented as in Figure 3.3, by comparing the CPU energy per clock cycle of each operating point. Here it can be seen that, when trading off time against energy, all TDP operating points except 0.6GHz (to the right) are Pareto-optimal. The energy reduction found in Equation 3.13 is therefore even higher (36.4%) if using 0.8GHz operation as the *lowPerformance* mode. Reduced CPU idle time can still make it beneficial to operate at 0.6GHz. All the  $P_{dynamic}$  operating points are Pareto-optimal, which is as expected considering Equation 2.5. Many assumptions have been made in order to estimate the missing TDPs, so the actual TDPs might not

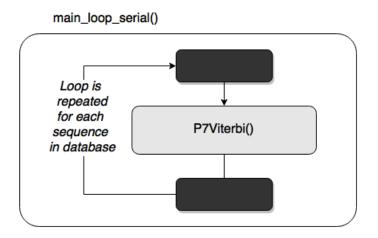

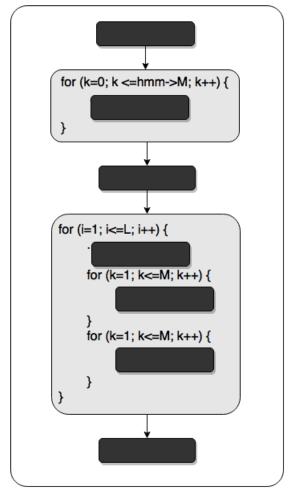

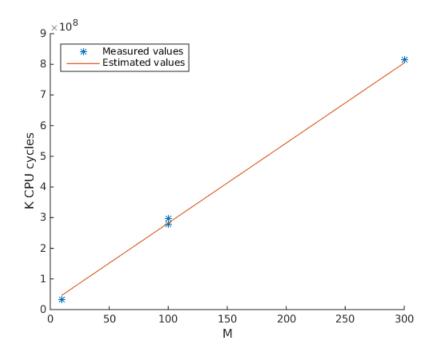

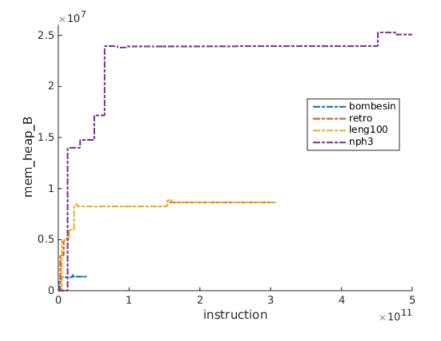

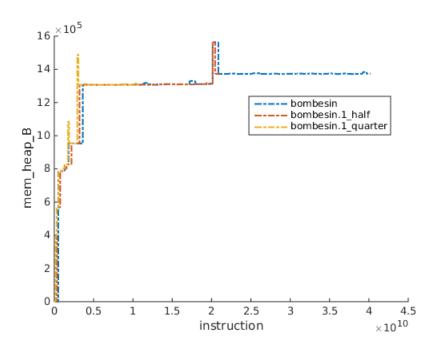

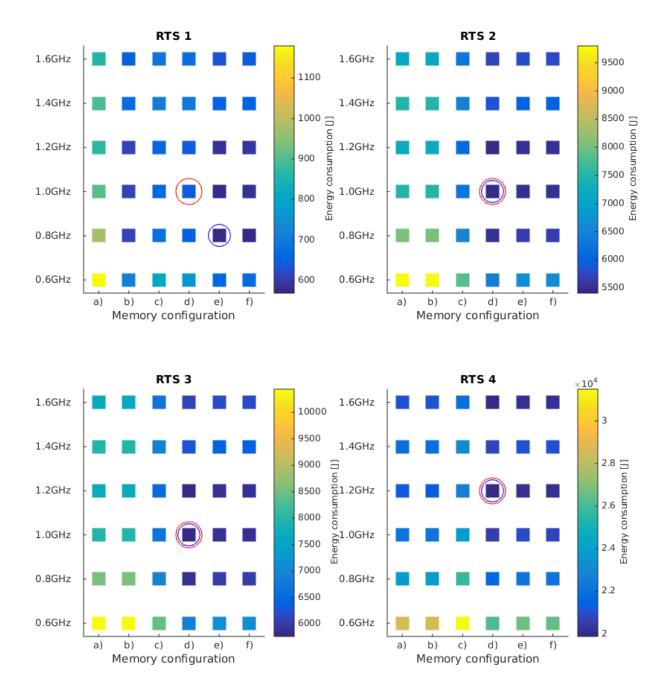

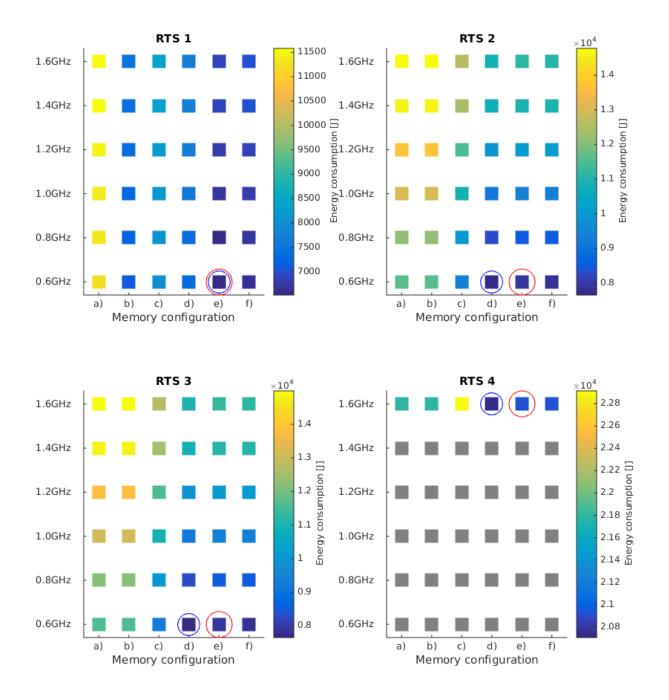

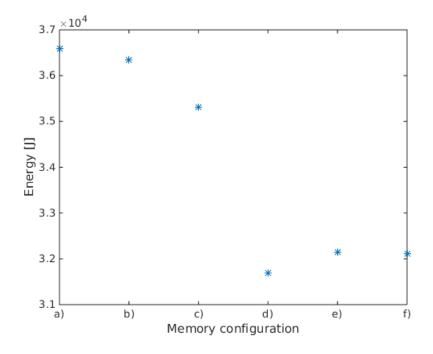

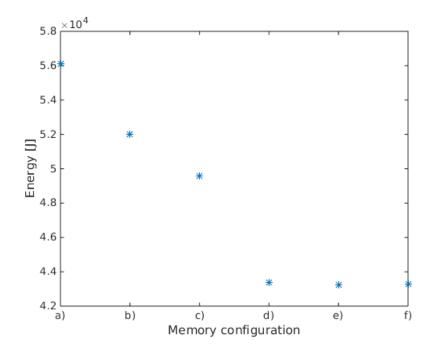

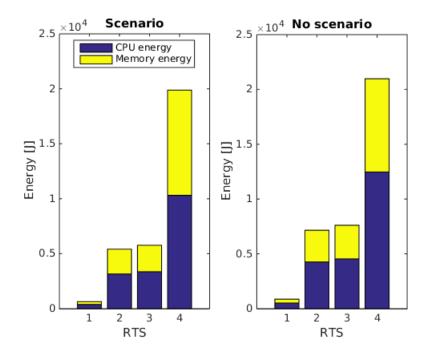

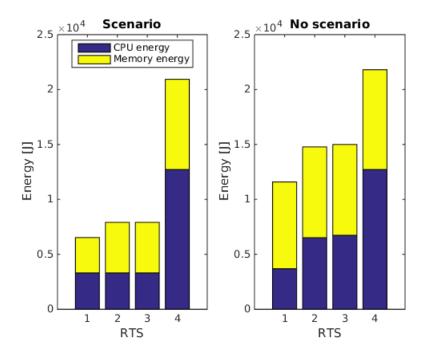

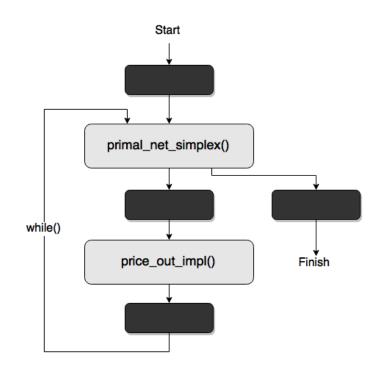

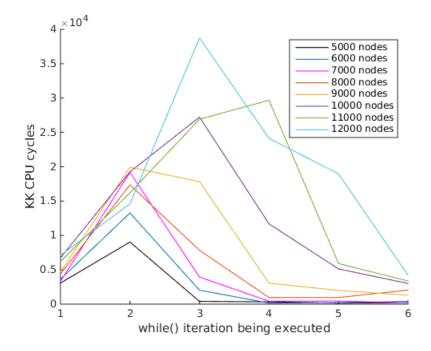

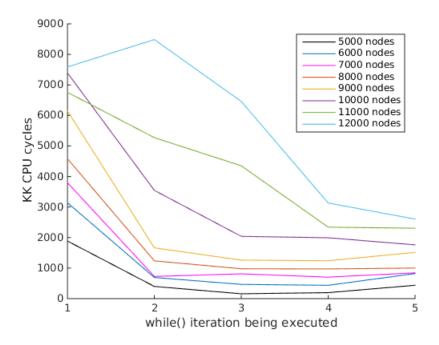

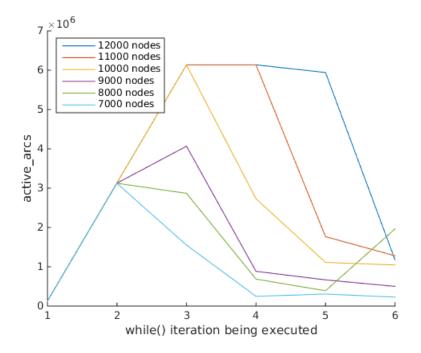

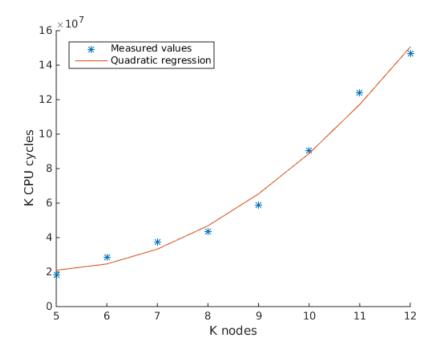

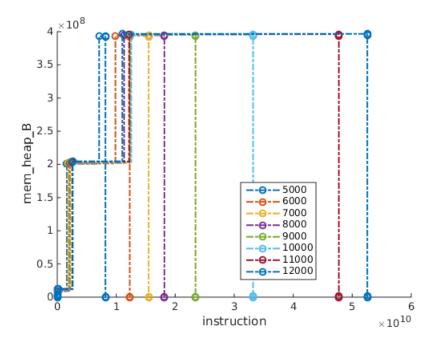

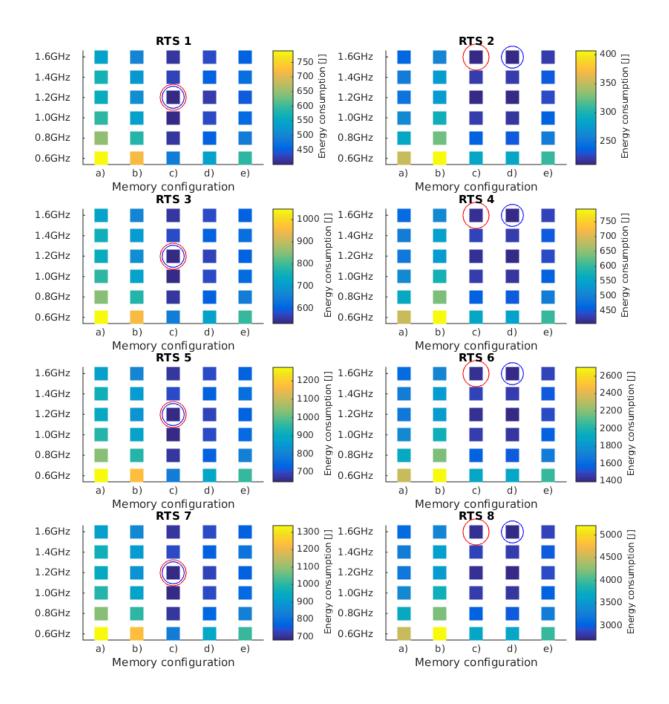

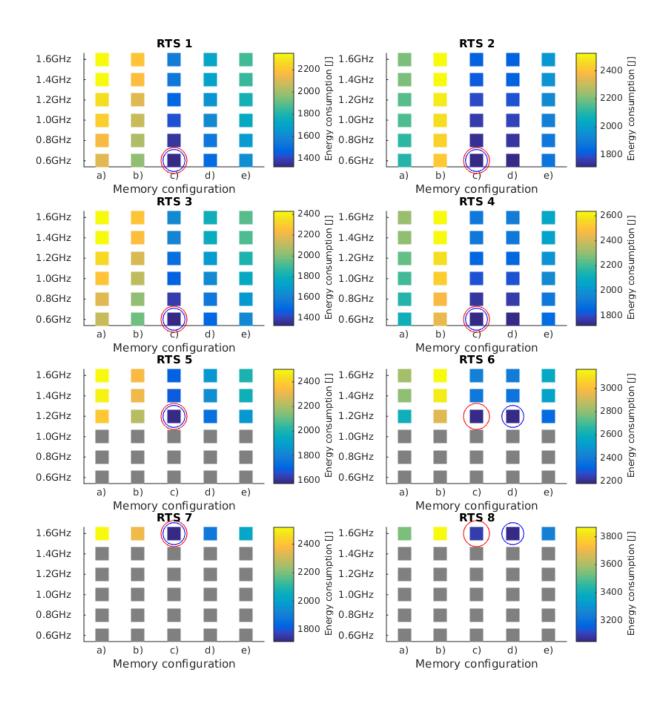

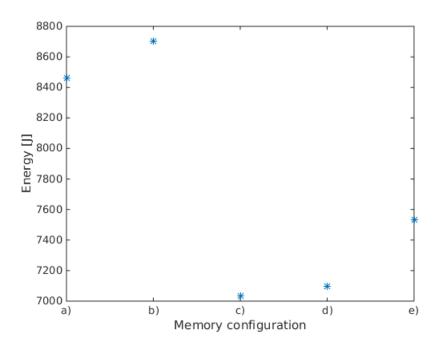

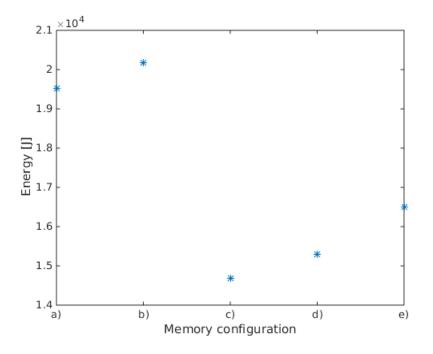

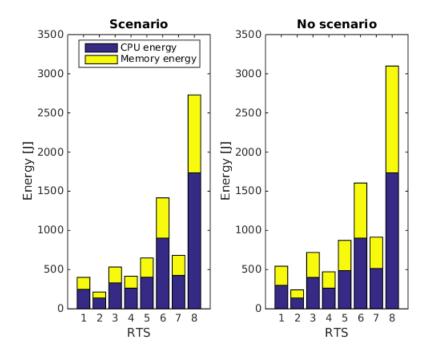

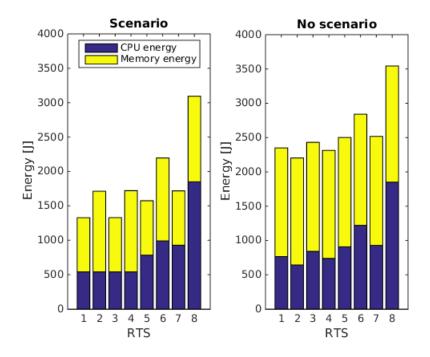

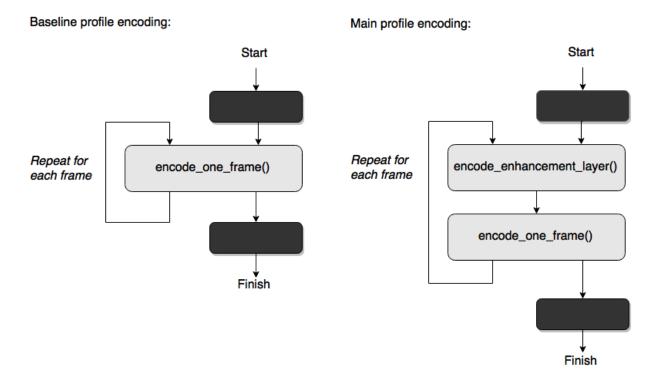

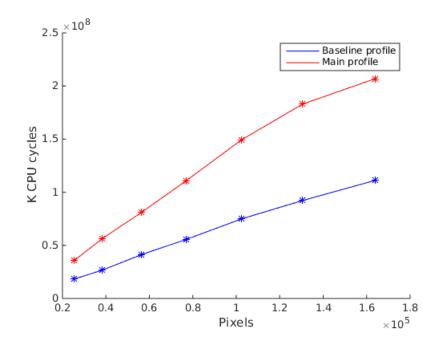

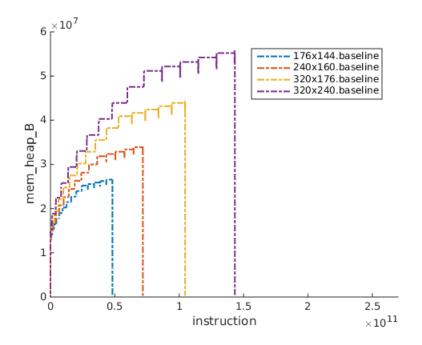

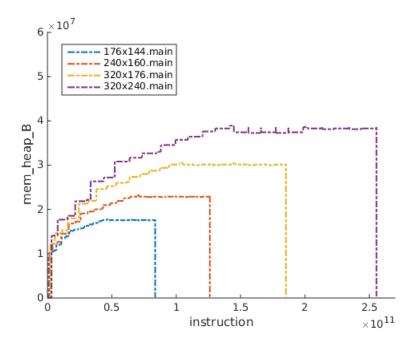

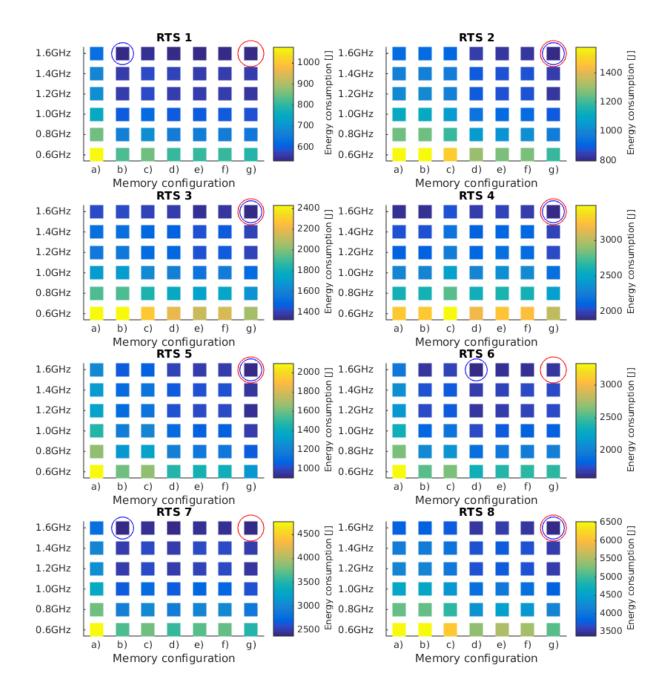

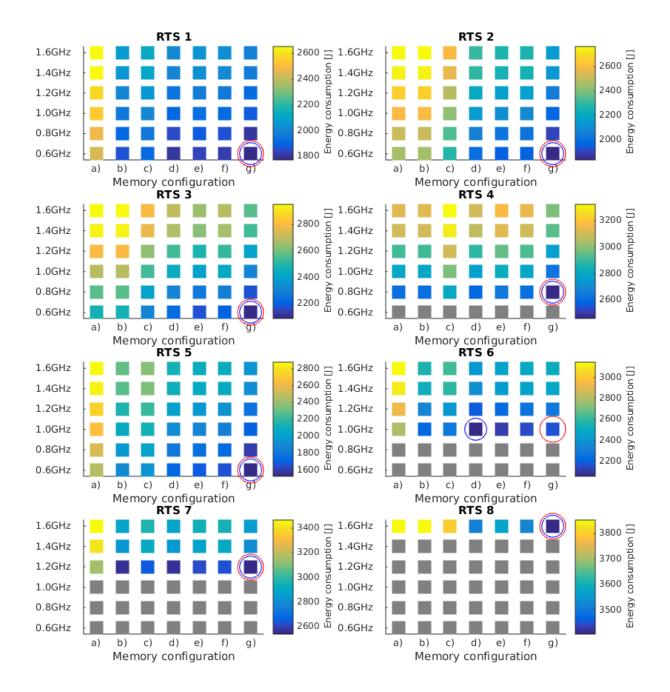

correspond entirely with the estimated. It is for example possible that the estimate of the 0.6GHz operating point is not Pareto-optimal because the estimate of the 0.8GHz operating point is more energy efficient than it should be. However, accurate CPU energy estimation is not part of the scope of this thesis, so further investigation of this is left for future work. The TDP operating points will be used to estimate the system scenario results.