## Adaptive Beamforming Using the Recursive Least Squares Algorithm on an FPGA

Andreas Bertheussen

Master of Science in ElectronicsSubmission date:June 2015Supervisor:Bjørn B. Larsen, IETCo-supervisor:Erik Narverud, Kongsberg Defence Systems<br/>Lars Lundheim, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## Assignment text

This text details a Masters thesis proposal put forward by Kongsberg Defence Systems (KDS) for the spring semester of 2015. The task is intended for students in their final year at the Institute of Electronics and Telecommunication at NTNU. Required skills are digital signal processing and preferably VHDL along with Matlab programming.

When receiving radio signals it is sometimes desirable to cancel out signals from certain directions in space while maintaining the rest of the spectrum. One could achieve this by making use of an array of antenna elements. The purpose of this system is to reduce the mean power of the signals in the directions where the sources that are to be canceled are located, while maintaining the rest of the spectrum. This can be done by exploitation of destructive interference demanding an array that is designed so that the incoming signals of the different antennas will be out of phase with each other. In order to achieve this destructive interference the signals have to be scaled and phase shifted by weights, and then added together. Both the signals and the weights will be complex numbers. The algorithm should find a set of weights that corresponds to a minimization of the mean power of the signals in the directions of the sources that are to be canceled.

It is intended that the task is limited to developing and implementing one or several variations of a recursive least squares null-steering algorithm on an FPGA and comparing the performance and complexity of these versus the analytical approach. It is expected that a Matlab simulation is developed first and used to assess the suggested design. The results from the simulation may then be used as a basis for implementation and test on a real FPGA, and the resulting performance compared to the performance estimates. A reference data set will be provided for the performance assessment.

## Summary

This thesis describes the design and implementation of a five-channel beamformer using a Space-Time Adaptive Processing (STAP) filter with Recursive Least Squares (RLS) as the adaptive algorithm. The objective of the algorithm is to compute of a set of filter weights for a STAP filter, such that the channels are filtered and combined into a signal with minimized power. Two test signal sets containing a high-powered jammer signal and a noise floor are used for performance evaluation. Three goals are set for this thesis; comparison of RLS to Sample Matrix Inversion (SMI) algorithm when used in a beamformer, comparison of various architectures which implement RLS, and the implementation and test of one of the architectures for a Xilinx Virtex 6 XC6VLX240T-1 Field-Programmable Gate Array (FPGA)

Simulations comparing RLS to SMI show that a beamformer using RLS performs the same as a beamformer using SMI for 3-5 antennas (channels) and 1-4 temporal taps in the STAP filter.

Litterature review shows that conventional RLS is unsuitable for FPGA implementation due to numerical instability. Comparison of IQRD-RLS, FQRD-RLS and MCFQRD-RLS architectures which are claimed to be stable RLS variants, shows that IQRD-RLS is the least computationally expensive of the algorithms.

IQRD-RLS is implemented using Givens rotations in a systolic array architecture. Floating point, fixed point and CORDIC-based Givens rotation algorithms are compared with regard to speed and area, and floating point is chosen. Hardware simulations reveal that the filter weights returned by IQRD-RLS exhibit a drift, and is *not* stable in finite-precision arithmetic. The main cause is accumulated quantization error from the forgetting factor and its inverse ( $\lambda^{\pm 1/2}$ ).

The IQRD-RLS systolic array is reduced to a (stable) QRD-RLS systolic array, approximately halving the number of systolic array nodes. Filter weights are not computed directly by QRD-RLS, and are instead recovered from the QRD-RLS least squares filtering error output by the method of weight flushing.

Results show that the QRD-RLS systolic array using 14 mantissa bits is sufficient as it performs equivalently to conventional RLS using double precision (53 mantissa bits). If only 11 mantissa bits are used, the output power increases by 3.3 dB. The final design can operate at sample rates from 19.4 MHz to 24.6 MHz, for a mantissa precision range of 14 to 11 bits. At this rate, the QRD-RLS systolic array can converge and output filter weights in 5.3  $\mu$ s, significantly faster than the target of 100  $\mu$ s. It is found that the current design has fully utilized its speed potential/limit due to the recursive nature of the algorithm. Processing of signals at the desired rate of 125 MHz would require changes to the algorithm itself. The implementation size is such that a 5-channel QRD-RLS array with one tap can fit on the FPGA. Channel-interleaving is proposed as a method to reduce system size, at the expense of slower operation.

All hardware is designed, simulated and tested using Simulink together with Xilinx System Generator and its co-simulation and hardware-in-the-loop features.

## Sammendrag

Denne oppgaven beskriver design og implementasjon av en fem-kanals stråleformer som benytter et rom- og tids-adaptivt filter (STAP) med rekursiv minste kvadraters metode (RLS) som adaptiv algoritme. Målet til algoritmen er å finne filtervektene til STAP-filteret slik at kanalene filtreres og kombineres til ett signal med minimert effekt. To sett med testsignaler som inneholder et kraftig jammesignal og støygulv brukes for å vurdere ytelsen. Tre mål er satt for oppgaven; sammenlikning av RLS-algoritmen med direkte invertering av korrelasjonsmatriseestimat (SMI), sammenlikning av forskjellige arkitekturer for implementasjon av RLS, og implementasjon og test av én av arkitekturene på en Xilinx Virtex 6 XC6VLX240T-1 Field-Programmable Gate Array (FPGA).

Simuleringer som sammenlikner RLS med SMI viser at en stråleformer som bruker RLS har tilsvarende ytelse som SMI når det brukes 3-5 antenner (kanaler) og 1-4 tapper (tidsforsinkelser) i STAP-filteret.

Med grunnlag i litteratur vurderes konvensjonell RLS som uegnet for implementasjon på FPGA på grunn av numerisk ustabilitet. Sammenlikning av arkitekturene IQRD-RLS, FQRD-RLS og MCFQRD-RLS, som påstås å være stabile varianter av RLS, viser at IQRD-RLS krever minst regnekraft.

IQRD-RLS implementeres ved bruk av Givens rotasjoner i en "systolisk array"-arkitektur. Flyttall, fastkomma og CORDIC-baserte metoder for Givens rotasjon sammenliknes med hensyn til implementasjonens hastighet og størrelse, og flyttall velges. Simulering av maskinvare viser at filtervektløsningene fra IQRD-RLS-arrayet drifter vekk fra korrekt løsning og at IQRD-RLS derfor er ustabilt. Hovedårsaken er akkumulert kvantiseringsfeil fra glemmefaktoren og dens inverse ( $\lambda^{\pm 1/2}$ ).

IQRD-RLS-arrayet forenkles til et (stabilt) QRD-RLS systolisk array, noe som halverer antallet noder brukt i arrayet. Filtervekter beregnes ikke direkte av QRD-RLS, men må i stedet hentes ut fra QRD-RLS arrayet sin impulsrespons.

Resultater viser at 14 bit mantisse er tilstrekkelig for at det QRD-RLS systoliske arrayet har en ytelse tilsvarende konvensjonell RLS med dobbel presisjons aritmetikk (53 bits mantisse). Reduksjon til 11 bit mantisse øker uteffekten med 3.3 dB. Maskinvareimplementasjonen kan operere opp til 19.4 MHz til 24.6 MHz avhengig av mantissepresisjon fra 14 til 11 bit. Ved denne raten kan systemet konvergere og finne filtervektene innen 5.3  $\mu$ s, som er betydelig raskere enn målsetningen på 100  $\mu$ s. Det er også funnet at den aktuelle implementasjonen har nådd hastighetsbegrensningen forårsaket av QRD-RLS-algoritmens rekursive definisjon. For å håndtere signaler ved ønsket rate på 125 MHz må selve QRD-RLS-algoritmen modifiseres. Implementasjonens størrelse er slik at et QRD-RLS array med 5 kanaler og en tap får plass på aktuell FPGA. Kanalinterleaving er foreslått som metode som vil redusere størrelsen, på bekostning av redusert hastighet.

All maskinvare er designet, simulert og testet ved bruk av Simulink med Xilinx System Generator og dets funksjonalitet for ko-simulering og simulering med FPGA i sløyfa.

## Preface

This thesis is submitted for the degree of Master of Science (MSc) at the Norwegian University of Science and Technology (NTNU). This work has been carried out during the spring semester of 2015 with supervision and guidance by Assoc. Professor Bjørn B. Larsen and Professor Lars M. Lundheim (NTNU) as well as Erik Narverud, systems engineer at Kongsberg Defence Systems (KDS). KDS defined the assignment and supplied the hardware needed for implementation and test.

When I started on this thesis, I had no experience with beamformers or adaptive filters. Working out the implementation details from math to hardware has been challenging and very rewarding. I'd like to thank my supervisors Bjørn, Lars and Erik for their guidance and advice. In particular, I'd like to thank Lars for his constructive and detailed feedback on matters relating to signal processing theory.

Trondheim, Norway, June 2015 Andreas Bertheussen

## Contents

|     | Lists of figures, tables and algorithms                        | ix   |

|-----|----------------------------------------------------------------|------|

|     | Abbreviations and notation                                     | xiii |

| 1   | Introduction                                                   | 1    |

| 1.1 | Motivation                                                     | 1    |

| 1.2 | Goals                                                          | 1    |

| 1.3 | Tools                                                          | 2    |

| 2   | Theory                                                         | 3    |

| 2.1 | The Space-Time Adaptive Processing (STAP) filter               | 3    |

| 2.2 | The Minimum Mean Square Error (MMSE) criterion                 | 4    |

| 2.3 | Algorithms for solving MMSE problems                           | 5    |

| 2.4 | Givens rotation                                                | 8    |

| 2.5 | CORDIC algorithm                                               | 9    |

| 2.6 | QR-decomposition                                               | 10   |

| 2.7 | QR-decomposition-based RLS (QRD-RLS)                           | 11   |

| 2.8 | Inverse QRD-RLS (IQRD-RLS)                                     | 11   |

| 2.9 | Systolic array implementation of RLS algorithms                | 13   |

| 3   | Design                                                         | 15   |

| 3.1 | Requirements                                                   | 15   |

| 3.2 | Test signal set                                                | 16   |

| 3.3 | Sample Matrix Inversion (SMI) vs Recursive Least Squares (RLS) |      |

|     | performance                                                    | 17   |

| 3.4 | RLS parameters                                                 | 20   |

| 3.5 | MATLAB and Simulink simulation of IQRD-RLS                     | 23   |

| 3.6 | Hardware implementation considerations                         | 26   |

| 3.7 | Implementation of floating point complex IQRD-RLS              | 30   |

| 3.8 | Implementation of floating point complex QRD-RLS               | 33   |

| 3.9 | Improving speed                                                | 36   |

| 4   | Conclusion and further work                                    | 39   |

| 4.1 | Result overview                                                | 39   |

| 4.2 | Algorithmic improvements                                       | 40   |

| 4.3 | Implementation improvements                                    | 40   |

| 4.4 | Beamforming performance and result validity                    | 42   |

| 4.5 | RLS convergence speed and STAP filter update rate              | 44   |

| 4.6 | Workflow and tools                                             | 44   |

| 4.7 | Future work                                                    | 46   |

|     | References                                                     | 48   |

| Α           | Simulink models                                           | 49 |

|-------------|-----------------------------------------------------------|----|

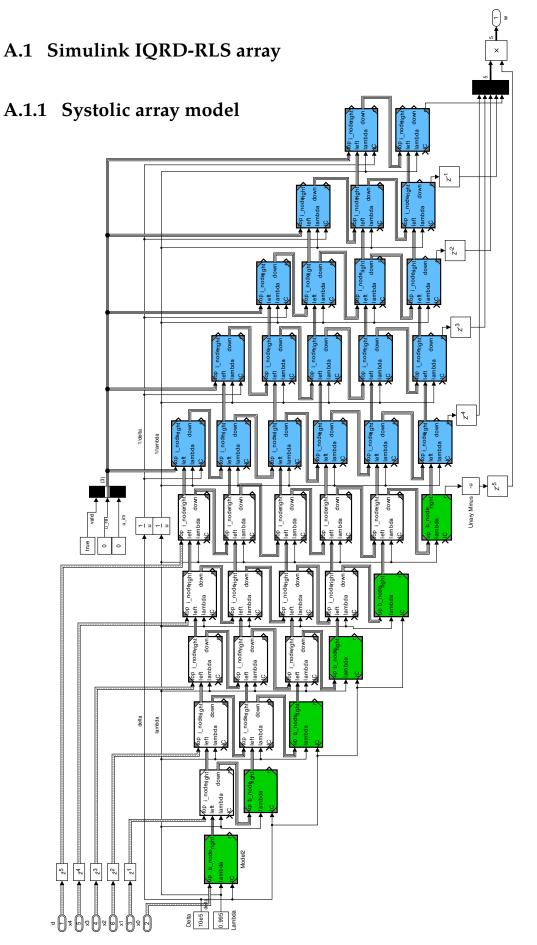

| A.1         | Simulink IQRD-RLS array                                   | 49 |

| A.2         | Simulink QRD-RLS array with weight flushing               | 52 |

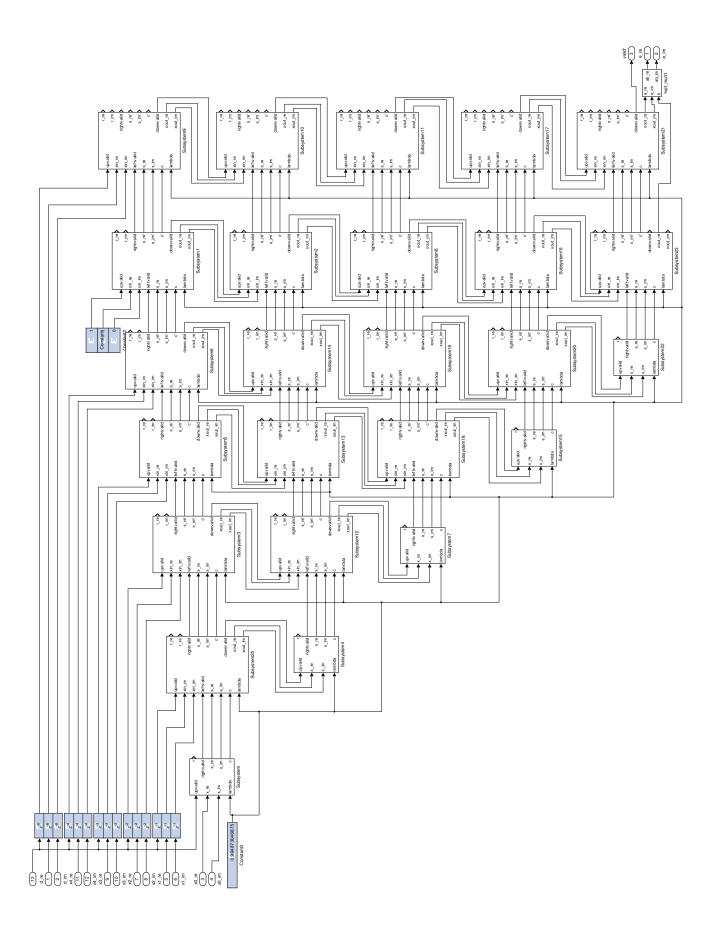

| В           | System Generator (hardware) models                        | 57 |

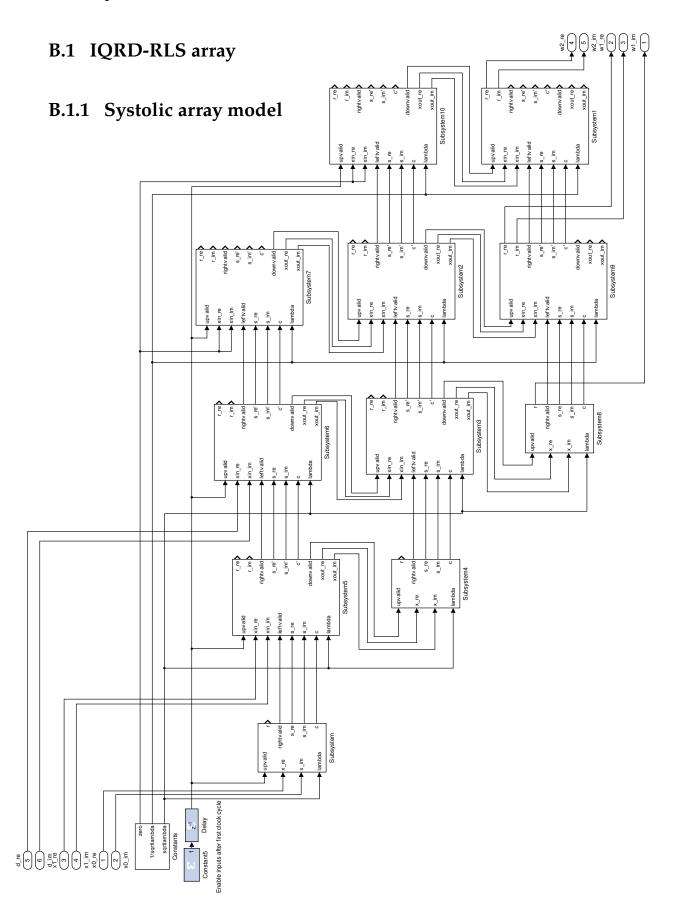

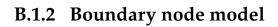

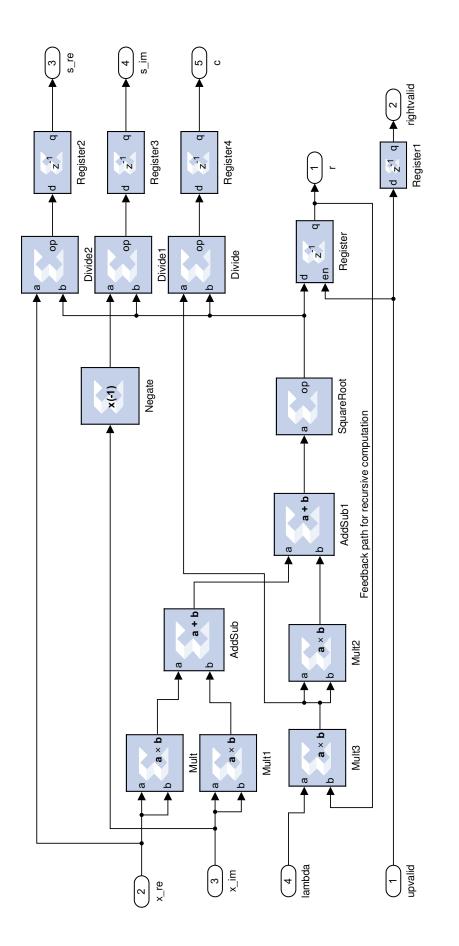

| <b>B.</b> 1 | IQRD-RLS array                                            | 57 |

| B.2         | QRD-RLS array with weight flushing                        | 60 |

| С           | MATLAB source code                                        | 65 |

| <b>C</b> .1 | STAP expansion processing code                            | 65 |

| C.2         | SMI processing code                                       | 66 |

| C.3         | Conventional RLS processing code                          | 67 |

| C.4         | Double precision boundary and internal node models        | 68 |

| C.5         | Limited precision boundary and internal node models       | 69 |

| C.6         | Double precision CORDIC boundary and internal node models | 70 |

| C.7         | IQRD-RLS systolic array simulator                         | 71 |

| <b>C.8</b>  | QRD-RLS systolic array simulator                          | 74 |

| C.9         | Miscellaneous utility functions, dependencies             | 77 |

| D           | Other                                                     | 79 |

| D.1         | Breakdown of conventional RLS complexity                  | 79 |

| D.2         | Implementation of CORDIC-based QRD-RLS                    | 79 |

## Figures

| 2.1        | A STAP filter with <i>M</i> channels and <i>N</i> taps.                                                                                                                                                                                                                                                   | 3  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2<br>2.3 | MMSE block diagram<br>Examples of givens rotation. On the left is the general case, and on<br>the right is the special case when the rotation is used to annihilate                                                                                                                                       | 4  |

| 2.4        | the $e_2$ dimension.<br>Examples of QRD-RLS (top) and IQRD-RLS (bottom) systolic array                                                                                                                                                                                                                    | 8  |

| 2.1        | structures for $MN = 3$ . Latencies can be added as suggested with blue dotted lines.                                                                                                                                                                                                                     | 14 |

| 3.1        | System diagram showing the multi channel radio front-end, the                                                                                                                                                                                                                                             |    |

| 3.2        | adaptive beamformer and the GNSS decoder.<br>Modified STAP filter modelled after the MMSE criterion. Adaptive                                                                                                                                                                                             | 15 |

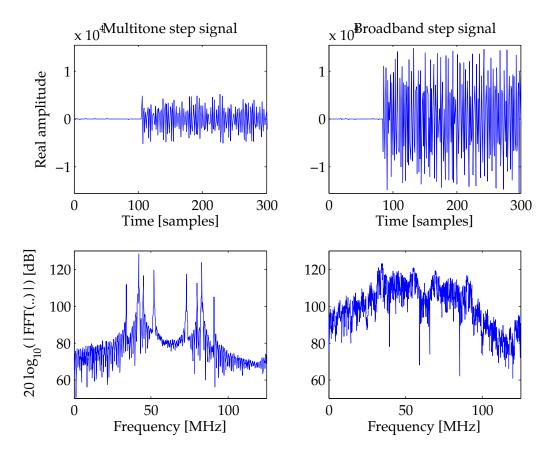

| 3.3        | algorithm (not shown) is used to update weights $w_{m,n}$ .<br>Test signals showing a multitone signal (left) and a broadband                                                                                                                                                                             | 16 |

|            | signal (right). The time domain plots (top) show the step in power near sample 100, while the FFT plots (bottom) show relative                                                                                                                                                                            |    |

| 3.4        | differences between the spectra. Only reference channel is shown.<br>Surfaces show output power from SMI (red) and RLS (blue)<br>algorithms for different channel/tap configurations. Within each                                                                                                         | 17 |

|            | plot are four surfaces, the blue RLS results for $\lambda = 0.995$ (lower) and $\lambda = 0.999$ (upper), and the red SMI results for $K = 125$ (lower) and                                                                                                                                               | 18 |

| 3.5        | K = 500 (upper).<br>Filter weight magnitude behavior for $M = 2$ , $N = 1$ configuration,<br>multi-tone test signal. Left graph shows both filter weights at the<br>moment when the jammer is activated. Right graph shows the                                                                            | 10 |

|            | steady state variation in a single weight $ w_0 $ .                                                                                                                                                                                                                                                       | 19 |

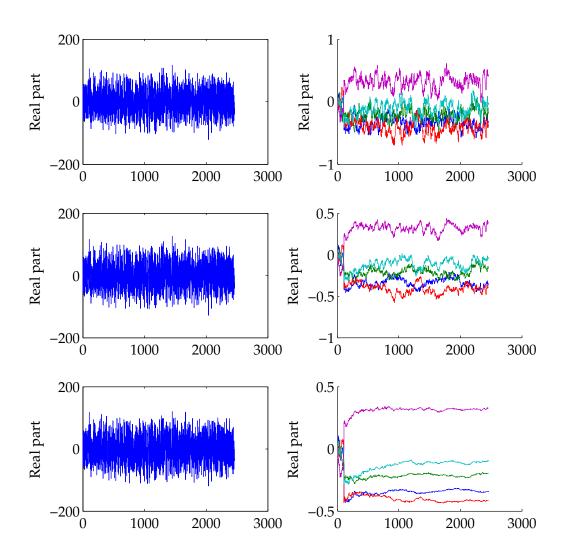

| 3.6        | Real component of beamformer output $e[i]$ (left), and filter weight<br>behavior (right) for multi-tone signal, $M = 5$ , $N = 1$ , $\lambda = 0.99$ and<br>varying $\delta \in \{10^5, 10^6, 10^8\}$ from top to bottom. Colors blue, green,                                                             |    |

| 3.7        | red, cyan, purple correspond to weights $w_0$ through $w_4$ .<br>Real component of beamformer output $e[i]$ (left), and filter weight<br>behavior (right) for multi-tone signal, $M = 5$ , $N = 1$ , $\delta = 10^5$ and<br>varying $\lambda \in \{0.98, 0.995, 0.999\}$ from top to bottom. Colors blue, | 20 |

| 3.8        | green, red, cyan, purple correspond to weights $w_0$ through $w_4$ .<br>Computational complexity per iteration for IQRD-, FQRD- and                                                                                                                                                                       | 22 |

| 3.9        | MCFQRD-RLS algorithms with $M = 5$ , and varying number of taps $N$ .<br>Dependency graph showing a single iterations of a IQRD-RLS                                                                                                                                                                       | 24 |

|            | systolic array structure for $MN = 3$ .                                                                                                                                                                                                                                                                   | 25 |

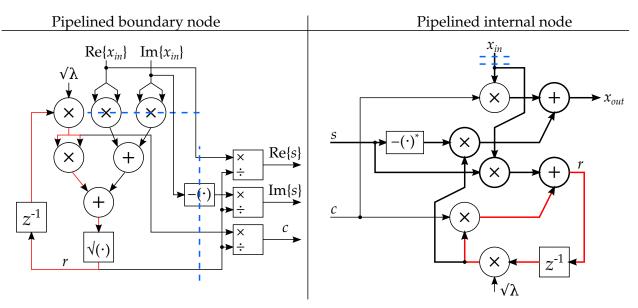

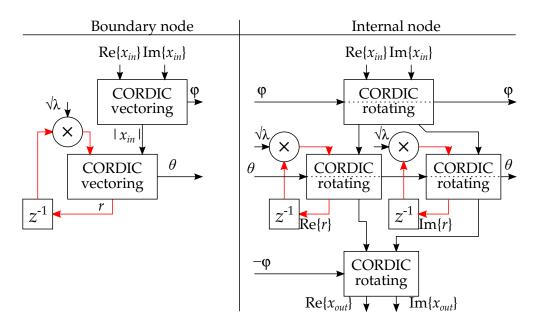

| 3.10       | Possible architectures for the boundary nodes (left) and internal<br>nodes (right). CORDIC on top, Givens rotation on bottom. Loops                                                                                                                                                                       | 27 |

| 3.11       | highlighted in red. Thick lines represent complex numbers.<br>Node construction for bounday and internal nodes implementing<br>algorithm 2.5. Bold lines for multipliers and adders indicate<br>complex operations which are not expanded for simplicity. Loops                                           | 27 |

|            | complex operations which are not expanded for simplicity. Loops drawn in red.                                                                                                                                                                                                                             | 30 |

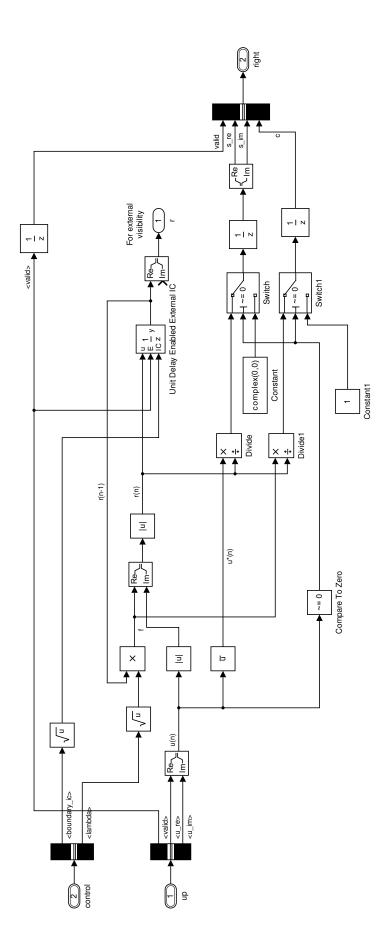

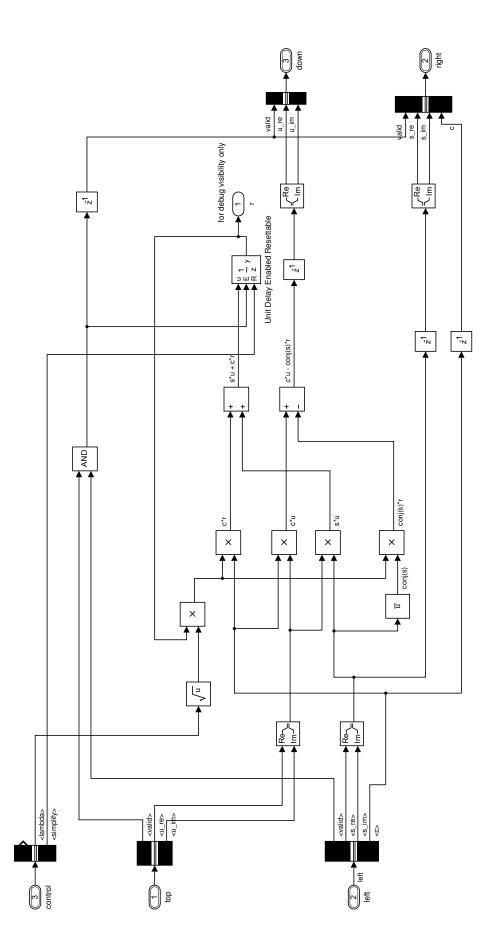

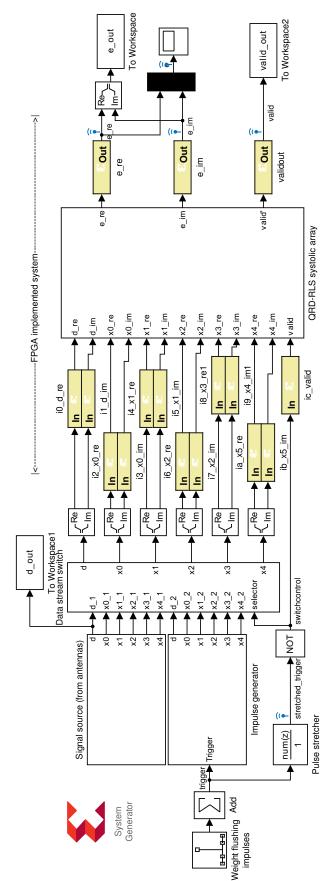

| 3.12 | Diagram of designed system. The systolic array portion (indicated)            |    |

|------|-------------------------------------------------------------------------------|----|

|      | is designed for hardware.                                                     | 31 |

| 3.13 | Real value of filter weights $w_0$ (blue) and $w_1$ (green) from two          |    |

|      | overlaid simulations for $M = 2$ , $N = 1$ . 6 bit exponent, 12 bit           |    |

|      | mantissa, $\lambda^{1/2} = 0.989990234375$ (quantized). The two cases         |    |

|      | show $\lambda^{-1/2} = 1.01025390625$ (weights drifting away from 0) and      |    |

|      | $\lambda^{-1/2} = 1.009765625$ (weights drifting towards zero).               | 32 |

| 3.14 | Diagram of designed system with a QRD-RLS systolic array                      |    |

|      | and weight flushing. The systolic array portion (indicated) is                |    |

|      | implemented in hardware.                                                      | 34 |

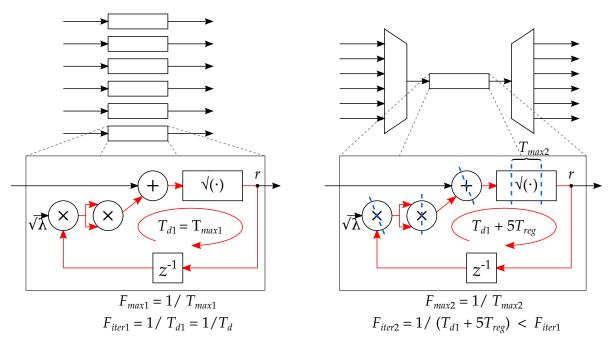

| 3.15 | Added latency (left) and redistributed latency (right). Blue dotted           |    |

|      | lines represent cycles of latency.                                            | 37 |

| 3.16 | Boundary and internal nodes showing where extra latency is                    |    |

|      | added. Added latency is shown with blue dotted lines.                         | 38 |

| 4.1  | Illustration on how the size of a system (left) can be reduced by             |    |

|      | channel interleaving (right). Blue dotted lines represent added               |    |

|      | pipeline registers. Adding 5 pipeline registers reduces logic to ½th.         | 42 |

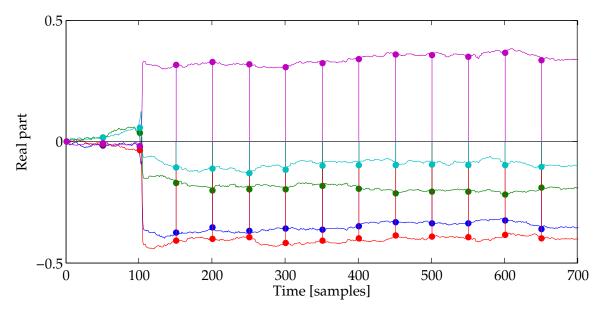

| 4.2  | Comparison of filter weights from conventional RLS algorithm to               |    |

|      | filter weights flushed from hardware implementation of QRD-RLS                |    |

|      | array. Multi-tone test signal, $\lambda = 0.998$ , $M = 5$ , $N = 1$ , 14 bit |    |

|      | mantissa. Colors blue, green, red, cyan, purple correspond to                 |    |

|      | weights $w_0$ through $w_4$ .                                                 | 43 |

| 4.3  | Comparison of beamformer output from conventional RLS (red),                  |    |

|      | and hardware simulation of QRD-RLS array (blue). Multi-tone test              |    |

|      | signal, $\lambda = 0.998$ , $M = 5$ , $N = 1$ , 14 bit mantissa.              | 45 |

| D.1  | Boundary and internal nodes for CORDIC based systolic array.                  | 80 |

|      |                                                                               | 00 |

## Tables

| 3.1 | Computational complexity per iteration for possible QR                        |    |

|-----|-------------------------------------------------------------------------------|----|

|     | decomposition based RLS algorithms. <i>M</i> is the number of channels        |    |

|     | (excluding reference), N is number of taps per channel. [, ]                  | 23 |

| 3.2 | Overview of the delay and resource consumption for square root,               |    |

|     | multiplication and addition operators, for fixed and floating point formats.  | 29 |

| 3.3 | Overview of the input-output delay and resource consumption for               |    |

|     | boundary and internal nodes for various mantissa widths (Mant.)               |    |

|     | [bit], as reported by synthesis tools (no place/route). Exponent              |    |

|     | width is 6 bits.                                                              | 36 |

| 3.4 | Power output for different systolic array dimensions (M,N) and                |    |

|     | mantissa precision. Multi-tone test signal, $\lambda = 0.995$ quantized to 11 |    |

|     | bit mantissa in all cases.                                                    | 37 |

| 4.1 | Overview of resource consumption and max delay for boundary                   |    |

|     | and internal nodes for various mantissa widths (Mant.) [bit], as              |    |

|     | reported by place and route tools. Exponent width is 6 bits.                  | 39 |

| D.1 | Breakdown of conventional RLS arithmetic operations                           | 79 |

## Algorithms

| 2.1 | The conventional RLS algorithm                                                                        | 7  |

|-----|-------------------------------------------------------------------------------------------------------|----|

| 2.2 | Complex givens rotation. Left side rotates $(a, b)$ to zero $b$ , resulting                           |    |

|     | in $(r, 0)$ and rotation parameters <i>c</i> and <i>s</i> . The right side uses <i>c</i> and <i>s</i> |    |

|     | to rotate a different vector $(f, g) \rightarrow (r, s)$ .                                            | 11 |

| 2.3 | The QRD-RLS algorithm                                                                                 | 12 |

| 2.4 | The IQRD-RLS algorithm                                                                                | 12 |

| 2.5 | QRD-RLS and IQRD-RLS boundary node operation (left) and                                               |    |

|     | internal node operation (right) using givens rotations. Inverse                                       |    |

|     | internal nodes of IQRD-RLS use $\lambda^{-1/2}$ , all others use $\lambda^{1/2}$                      | 13 |

|     |                                                                                                       |    |

## Abbreviations

| FPGA                        | Field-Programmable Gate Array        |

|-----------------------------|--------------------------------------|

|                             | 8                                    |

| FIR                         | Finite Impulse Response              |

| KDS                         | Kongsberg Defence Systems            |

| RLS Recursive Least Squares |                                      |

| SMI                         | Sample Matrix Inversion              |

| LUT                         | Look-Up Table                        |

| STAP                        | Space-Time Adaptive Processing       |

| MMSE                        | Minimum Mean Square Error            |

| DMI                         | Direct Matrix Inversion              |

| CORDIC                      | Coordinate Rotation Digital Computer |

| LMS                         | Least Mean Squares                   |

| GNSS                        | Global Navigation Satellite System   |

| WE                          | Weight Extraction                    |

| SRF                         | Square Root Free                     |

|                             |                                      |

## Notation and units

Notation that is extensively used is summarized here.

| i                             | Imaginary unit or time (iteration) index                                                                                                          |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| $x[i], \mathbf{A}[i]$         | Discrete-time signal (1D or vector/matrix)                                                                                                        |

| $\chi^*$                      | Complex conjugate of <i>x</i>                                                                                                                     |

| $\mathbf{I}_p$                | Identity matrix with number of columns/rows given by <i>p</i>                                                                                     |

| $\mathbf{A}^{H}$              | Hermitian transpose of matrix or vector, = $(A^*)^T$                                                                                              |

| $\mathbf{A}^{-T}$             | Transpose of matrix inverse, = $(A^{-1})^T$                                                                                                       |

| C, S                          | $c = \cos(\theta), s = \sin(\theta)$ , rotation factors for Givens rotation                                                                       |

| М                             | Number of channels excluding reference channel                                                                                                    |

| Ν                             | Number of filter taps per channel                                                                                                                 |

| λ                             | Forgetting factor for conventional RLS algorithm                                                                                                  |

| Κ                             | Window length for correlation estimate in SMI algorithm                                                                                           |

| δ                             | Used for RLS initialization or diagonal loading term in SMI                                                                                       |

| arctan( <i>y</i> , <i>x</i> ) | Inverse tangent with two arguments, covering all quadrants. Equal to $\arctan(y/x)$ for positive $y$ and $x$ . Also known as $\texttt{atan2}()$ . |

Decibel quantities are relative to some reference. The reference is denoted in the unit. For instance, the quantity  $P_{out}$  [dB<sub>noise</sub>] implies the calculation  $10 \log(P_{out}/P_{noise})$ .

## 1 Introduction

### 1.1 Motivation

Many types of passive disturbances or interference can impair the function of a radio system, such as shadowing, multipath effects, variable propagation speeds and others. Disturbances can also be caused by radio transmitters, accidentally or intentionally. Intentional disturbances are commonly called *jamming*. Jammers may use one or several strategies to disturb the target radio system, such as single tone, multi tone, narrowband or broadband signals and frequency sweeps. A jammer could emit a signal which overpowers and spoofs the original signal, or a signal that will exceed the dynamic range of the receiver. A jammer could also replay the original signals, creating artificial multipath effects.

For a radio receiver that must function in an environment with jammers, it is desirable to suppress disturbances originating from certain directions or disturbances in certain frequency bands. This can be achieved using an antenna array where the signal from each individual antenna is filtered and combined so that the interference is canceled through destructive interference. The filtering operation for each channel can be a single complex multiplication, or a more general complex FIR (Finite Impulse Response) filter. The filter coefficients may be computed based on prior knowledge of the direction and/or frequency band of the interference and desired signal, or they may be adaptively computed by an algorithm, based on the received signals. The process of finding the appropriate weights is called *beamforming*, since the choice of weights controls the antenna array's sensitivity in both direction and frequency.

The assignment was proposed by KDS (Kongsberg Defence Systems), a Norwegian supplier of defence-related systems. KDS has several radio communication products, and are naturally interested in anti-jamming measures. KDS has supplied test signal sets and a Xilinx Virtex 6 Field-Programmable Gate Array (FPGA) development board for this thesis.

### 1.2 Goals

The goals set for this thesis are:

- Compare performance Recursive Least Squares (RLS) with the reference algorithm Sample Matrix Inversion (SMI) (the *analytical approach*).

- Compare various architectures for implementing RLS on the FPGA.

- Implement and test a suitable architecture on the FPGA.

## 1.3 Tools

Mathworks MATLAB R2012b is used throughout to write and run scripts that implements various algorithms. A MATLAB extension called Simulink is used to create and simulate block diagram models.

The target hardware for the implementation is a Xilinx Virtex 6 ML605 development board. The board contains many peripherals, but only the Virtex 6 XC6VLX240T-1 FPGA and the included debugging connectivity is used for this thesis.

The Virtex 6 series FPGAs contain an array of (re)configurable logic blocks (CLBs) connected to a programmable switch matrix for signal routing. Each CLB contains two *slices*, and each slice contains four 6-input look-up tables (LUTs), eight register flip flops (Reg.), multiplexers and carry logic. Some slices contain additional memory and shift register functionality. There is also a special type of slice named *DSP48E1* (DSP48 for short) which implements multiply-accumulate functionality. The XC6VLX240T-1 device has a total capacity of 150720 LUTs (37680 slices), as well as 768 DSP48 slices. These are the basic resources of the FPGA. Functionality implemented using LUTs is referred to as a *fabric* implementation.

The FPGA configuration is typically derived from hardware description languages like VHDL or Verilog. For this thesis, an extension to Simulink called *System Generator* is used. This extension is developed by Xilinx and includes a hardware block library containing functions such as adders, multipliers, dividers and other functions which can be synthesized for Xilinx FPGAs. When a Simulink model is constructed using these blocks, it can be processed using System Generator resulting in a synthesizable VHDL description of the model. The conventional Xilinx ISE toolchain can then used to process the VHDL, resulting in a configuration which can be loaded into the FPGA. In this way, System Generator works as a translator from the Simulink block diagram format to a more conventional VHDL description of a system.

System Generator is also able to accurately simulate the hardware blocks within the Simulink environment by using the Xilinx ISim HDL simulator in the background. System Generator can also be used do a hardware-in-loop simulation. This means that System Generator takes the block diagram model and generates a FPGA configuration which is loaded onto the FPGA. When the model is simulated in Simulink, the signals that are entering/leaving the hardware blocks is routed to/from the physical FPGA across its debug interface. This method is used to check that the implementation matches simulation results.

## 2 Theory

This chapter holds theory that will be referred to and/or applied in later chapters. The theory behind least squares filtering is described, followed by the Sample Matrix Inversion and Recursive Least Squares algorithms which can be used to solve the least squares problem.

The Givens rotation and CORDIC algorithms are explained as they can be used to realize QR-decomposition. QR-decomposition is explained since it is the core of the QRD-RLS and IQRD-RLS algorithms which are practical implementations of the RLS algorithm.

### 2.1 The Space-Time Adaptive Processing (STAP) filter

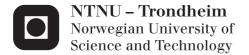

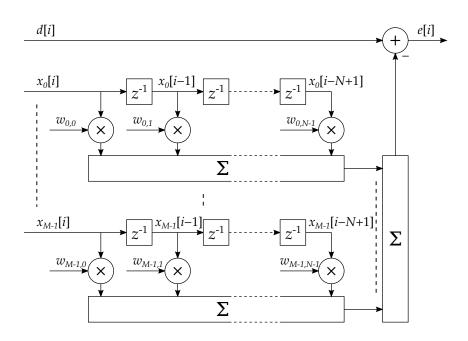

STAP [1,ch12] is an extension to the *M*-channel beamformer which introduces tapped delay line (FIR) filters of order *N* instead of a simple complex gain factor for each channel. The STAP filter linearly combines multiple channels into a single channel, and can adjust the phase and frequency response (gain) by modifying the weights  $w_{m,n}$ . The space-time filtering structure is shown in **figure 2.1**.

**Figure 2.1** A STAP filter with *M* channels and *N* taps.

Mathematically, it may be described by:

Chapter 2. Theory

$$e[i] = \sum_{m=0}^{M-1} \sum_{n=0}^{N-1} w_{m,n}^* x_m[i-n]$$

or more simply  $e[i] = w^H x[i]$

Here, we have chosen to define the  $MN \times 1$  vector x[i] as a snapshot of the signal available from the delay elements in the STAP structure at time *i*:

$$\boldsymbol{x}[i] = \begin{bmatrix} \begin{bmatrix} x_0[i] & x_1[i] & \cdots & x_{M-1}[i] \end{bmatrix}^T \\ \begin{bmatrix} x_0[i-1] & x_1[i-1] & \cdots & x_{M-1}[i-1] \end{bmatrix}^T \\ \vdots \\ \begin{bmatrix} x_0[i-N+1] & x_1[i-N+1] & \cdots & x_{M-1}[i-N+1] \end{bmatrix}^T \end{bmatrix}$$

(2.1)

Similarly, the filter weights are also formed into a  $MN \times 1$  vector:

$$\boldsymbol{w} = \begin{bmatrix} \begin{bmatrix} w_{0,0} & w_{1,0} & \cdots & w_{M-1,0} \end{bmatrix}^T \\ \begin{bmatrix} w_{0,1} & w_{1,1} & \cdots & w_{M-1,1} \end{bmatrix}^T \\ \vdots \\ \begin{bmatrix} w_{0,N-1} & w_{1,N-1} & \cdots & w_{M-1,N-1} \end{bmatrix}^T \end{bmatrix}$$

In STAP the filter weights are adapted by an algorithm based only on the input x. In that case the weight vector changes over time and is denoted w[i].

### 2.2 The Minimum Mean Square Error (MMSE) criterion

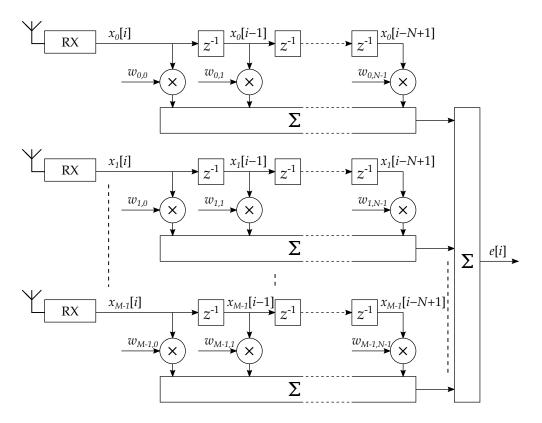

Consider the general filter  $y[i] = w^H x[i]$ . This filter can represent a FIR filter when elements of x are samples of the same signal at different times. It can also represent a linear combiner if elements of x are taken from different signals. It can also represent a combination of the two, like the STAP structure described earlier.

Figure 2.2 MMSE block diagram

A new signal d[i] is introduced as the *desired* signal, and the difference, or *error*,  $e[i] = d[i] - w^H x[i]$  is computed as illustrated in **figure 2.2**. The MMSE criterion is used to find the required properties of the filter weight values which minimize the squared error  $E[|e[i]|^2] = E[e[i]e^*[i]]$ .

$$E[e[i]e^*[i]] = E\left[d[i]d^*[i] - 2w^H x[i]d^*[i] + w^H x[i]x^H[i]w\right]$$

$$E[e[i]e^*[i]] = E\left[d[i]d^*[i]\right] - 2w^H E\left[x[i]d^*[i]\right] + w^H E\left[x[i]x^H[i]\right]w$$

$$= \sigma_d^2 - 2w^H r_{xd} + w^H R_{xx}w$$

Stationarity is assumed. The minimum of  $|e[i]|^2$  is found by setting its gradient equal to zero, and solving for w.

$$\nabla_{\boldsymbol{w}} E[\boldsymbol{e}[\boldsymbol{i}]\boldsymbol{e}^*[\boldsymbol{i}]] = 0 = -2\boldsymbol{r}_{xd} + 2\boldsymbol{R}_{xx}\,\boldsymbol{w}$$

Which is fulfilled when  $w = w_{opt}$  according to:

$$\boldsymbol{R}_{xx} \boldsymbol{w}_{opt} = \boldsymbol{r}_{xd} \qquad \Leftrightarrow \qquad \boldsymbol{w}_{opt} = \boldsymbol{R}_{xx}^{-1} \boldsymbol{r}_{xd} \tag{2.2}$$

Equation (2.2) is known as the Wiener-Hopf equation.

#### 2.3 Algorithms for solving MMSE problems

The expressions in equation (2.2) depend on the statistical properties  $R_{xx}$  and  $r_{xd}$  which describe the data. The Sample Matrix Inversion and Recursive Least Squares algorithms presented in this section are two approaches to estimating these statistics, resulting in the optimal filter weights.

#### 2.3.1 The Sample Matrix Inversion (SMI) algorithm

The SMI algorithm uses the simple estimators of equation (2.3) to estimate  $R_{xx}$  and  $r_{xd}$ . The estimates are then used in place of  $R_{xx}$  and  $r_{xd}$  in equation (2.2) to directly compute  $w_{opt}$ . This is referred to as Sample Matrix Inversion and sometimes also Direct Matrix Inversion (DMI).

$$\hat{R}_{xx}[i] = \frac{1}{K} \sum_{j=i-K+1}^{i} x[j] x^{H}[j] \qquad \hat{r}_{xd}[i] = \frac{1}{K} \sum_{j=i-K+1}^{i} x[j] d^{*}[j]$$

(2.3)

Inversion of  $\hat{R}_{xx}[i]$  may be problematic since the estimators do not guarantee non-singularity. One commonly proposed technique to avoid singular matrices is [1][2,ch7.3][3] termed *diagonal loading*. It is done by adding a small term  $\delta I$  to the estimate  $\hat{R}_{xx}$  before inverting it.

#### 2.3.2 The Recursive Least Squares (RLS) algorithm

The RLS algorithm [1,p273][4,p209][5] applies MMSE but starts with a slightly different formulation, so that the solution can be expressed on a recursive form. This means the solution is found in terms of modifications to the previous solution. Let a new scalar signal f[i] be defined as:

$$f[i] = \sum_{j=0}^{i} \lambda^{i-j} e^{2}[j]$$

(2.4)

e[j] is the error signal and  $\lambda \in (0, 1)$  is a "forgetting factor" which exponentially reduces the importance of previous squared errors. A value of  $\lambda$  very close to 1 means that

Chapter 2. Theory

the algorithm responds slower to change; it has longer memory. A small value has the opposite effect. By minimizing f[i] with respect to w, it can be shown [4,ch5.2] that the solution must satisfy a modified Wiener-Hopf equation:

$$\mathbf{R}'_{xx}[i] \, \mathbf{w}'[i] = \mathbf{r}'_{xd}[i] \qquad \Leftrightarrow \qquad \mathbf{w}'[i] = (\mathbf{R}'_{xx}[i])^{-1} \mathbf{r}'_{xd}[i]$$

where  $R'_{xx}[i]$  and  $r'_{xd}[i]$  are the sample autocorrelation of x[i] and sample cross correlation between x[i] and d[i], on a form that is exponentially weighted similarly to the error signal of equation (2.4):

$$\boldsymbol{R}_{xx}'[i] = \sum_{j=0}^{i} \lambda^{i-j} \boldsymbol{x}[j] \boldsymbol{x}^{H}[j] \qquad \boldsymbol{r}_{xd}'[i] = \sum_{j=0}^{i} \lambda^{i-j} \boldsymbol{x}[j] d^{H}[j]$$

It is possible to write  $R'_{xx}[i]$  and  $r'_{xd}[i]$  in a recursive form. The term corresponding to "now" index *i* can be taken out of the summation:

$$\begin{aligned} \mathbf{R}'_{xx}[i] &= \sum_{j=0}^{i} \lambda^{n-j} \mathbf{x}[j] \mathbf{x}^{H}[j] \\ &= \lambda \sum_{j=0}^{i-1} \lambda^{(n-1)-j} \mathbf{x}[j] \mathbf{x}^{H}[j] + \mathbf{x}[i] \mathbf{x}^{H}[i] \\ &= \lambda \mathbf{R}'_{xx}[i-1] + \mathbf{x}[i] \mathbf{x}^{H}[i] \end{aligned}$$

The same can be done for  $r'_{xd}[i]$ :

$$r'_{xd}[i] = \sum_{j=0}^{l} \lambda^{i-j} x[j] d^{H}[j] = \lambda r'_{xd}[i-1] + x[i] d^{H}[i]$$

We have here found an expression describing how  $R'_{xx}[i-1]$  and  $r'_{xd}[i-1]$  (previous timestep correlation matrices) can be updated to the current time step. To avoid computing the inverse  $(R'_{xx}[i])^{-1}$ , we apply the Woodbury matrix identity. To simplify notation, we define  $P[i] = (R'_{xx}[i])^{-1}$  and  $z[i] = r'_{xd}[i]$ .

$$(\mathbf{R}'_{xx}[i])^{-1} = \mathbf{P}[i] = \frac{1}{\lambda} \mathbf{P}[i-1] - \frac{\frac{1}{\lambda} \mathbf{P}[i-1] \mathbf{x}[i] \mathbf{x}^{H}[i] \frac{1}{\lambda} \mathbf{P}[i-1]}{1 + \mathbf{x}^{H}[i] \frac{1}{\lambda} \mathbf{P}[i-1] \mathbf{x}[i]}$$

$$= \frac{1}{\lambda} \mathbf{P}[i-1] - \frac{1}{\lambda} \mathbf{K}[i] \mathbf{x}^{H}[i] \mathbf{P}[i-1]$$

Where we have defined

$$K[i] = \frac{P[i-1]x[i]}{\lambda + x^H[i]P[i-1]x[i]}$$

The denominator here is a scalar making the expression somewhat simpler to compute. By multiplying up the denomitator, we can show that:

$$\begin{split} \boldsymbol{K}[i] + \frac{1}{\lambda} \boldsymbol{K}[i] \boldsymbol{x}^{H}[i] \boldsymbol{P}[i-1] \boldsymbol{x}[i] &= \frac{1}{\lambda} \boldsymbol{P}[i-1] \boldsymbol{x}[i] \\ \boldsymbol{K}[i] &= \left(\frac{1}{\lambda} \boldsymbol{P}[i-1] - \frac{1}{\lambda} \boldsymbol{K}[i] \boldsymbol{x}^{H}[i] \boldsymbol{P}[i-1]\right) \boldsymbol{x}[i] \\ \boldsymbol{K}[i] &= \boldsymbol{P}[i] \boldsymbol{x}[i] \end{split}$$

By inserting previous results in the modified Wiener-Hopf equation, we can find a recursive expression for the filter weights which does not require a matrix inversion:

$$w'[i] = (R'_{xx}[i])^{-1}r'_{xd}[i]$$

$$= P[i]z[i]$$

$$= P[i](\lambda z[i-1] + x[i]d[i])$$

$$= \lambda P[i]z[i-1] + P[i]x[i]d[i]$$

$$= \lambda \left(\frac{1}{\lambda}P[i-1] - \frac{1}{\lambda}K[i]x^{H}[i]P[i-1]\right)z[i-1] + P[i]x[i]d[i]$$

$$= \underbrace{P[i-1]z[i-1]}_{w'[i-1]} - K[i]x^{H}[i]\underbrace{P[i-1]z[i-1]}_{w'[i-1]} + \underbrace{P[i]x[i]}_{K[i]}d[i]$$

$$= w'[i-1] - K[i]x^{H}[i]w'[i-1] + K[i]d[i]$$

$$= w'[i-1] + K[i](d[i] - w'^{H}[i-1]x[i])$$

$$= w'[i-1] + K[i]\epsilon[i]$$

Note that the scalar signal  $\epsilon[i]$  represents the error output from filtering the current input signal with the previous filter. It is termed the *a priori* error signal. The a priori error is multiplied with the *gain matrix* K[i] in order to modify the filter weights. The conventional RLS algorithm is summarized in algorithm 2.1 [5].

$$P[-1] = \delta^{-1}I$$

$$w'[-1] = \begin{bmatrix} 1 & 0 & \cdots & 0 \end{bmatrix}^{T}$$

for each timestep  $i \ge 0$  do

$$K[i] = \frac{P[i-1]x[i]}{\lambda + x^{H}[i]P[i-1]x[i]}$$

$$w'[i] = w'[i-1] + K[i] (d[i] - w'^{H}[i-1]x[i])$$

$$P[i] = \operatorname{Tri} \left(\frac{1}{\lambda} \left(P[i-1] - K[i]x^{H}[i]P[i-1]\right)\right)$$

$$e[i] = d[i] - x^{H}[i]w'[i] \text{ (apply filter weights to signal)}$$

end for

#### Algorithm 2.1 The conventional RLS algorithm

The initialization of the *P* diagonal with  $\delta^{-1}$  is performed to bring it close to its final value when the signal power range is known in advance. Tri() signifies that only one triangular half of the matrix needs to be calculated, while the other triangular section

Chapter 2. Theory

is filled in with the complex conjugate due to the hermitian symmetry of the matrix P [5,p510].

### 2.4 Givens rotation

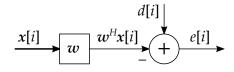

A Givens rotation [6] is a matrix transformation (named after Wallace Givens) which rotates two rows of a matrix. It can be used to transform matrices to an upper triangular or lower triangular form as part of a QR-decomposition. For an example of a Givens rotation, consider the illustration in **figure 2.3** (a). Here, the vector  $(a, b) = ae_1 + be_2$  is rotated by  $\theta$ , creating a new vector (x, y).

**Figure 2.3** Examples of givens rotation. On the left is the general case, and on the right is the special case when the rotation is used to annihilate the  $e_2$  dimension.

Mathematically, this clockwise<sup>1</sup> rotation can be described by left-multiplication with a rotation matrix as follows:

$$\begin{bmatrix} x \\ y \end{bmatrix} = \begin{bmatrix} \cos(\theta) & \sin(\theta) \\ -\sin^*(\theta) & \cos(\theta) \end{bmatrix} \begin{bmatrix} a \\ b \end{bmatrix} = G_{\theta} \begin{bmatrix} a \\ b \end{bmatrix}$$

The givens rotation may be applied to *n*-th and *m*-th row in any matrix of size *p*, by defining the rotation matrix as the identity matrix  $I_p$  (of size *p*), with elements  $G_{\theta n,n} = c = \cos(\theta)$ ,  $G_{\theta n,m} = s = \sin(\theta)$ ,  $G_{\theta m,n} = -s^* = -\sin^*(\theta)$  and  $G_{\theta m,m} = c = \cos(\theta)$ : (zero values are omitted)

$$G_{\theta} = \begin{bmatrix} I_n & & & \\ & C & & S & \\ & & I_{m-n-1} & & \\ & -S^* & & C & \\ & & & & I_{p-m-1} \end{bmatrix}$$

The transform will only affect the *m*-th and *n*-th row, and will transform each column individually, for example if:

In some cases the Givens rotation is defined for counterclockwise rotation, for which the sine terms are exchanged.

$$\begin{bmatrix} x & r \\ y & s \end{bmatrix} = \mathbf{G}_{\theta_0} \begin{bmatrix} a & f \\ b & g \end{bmatrix}, \text{ then we have } \begin{bmatrix} x \\ y \end{bmatrix} = \mathbf{G}_{\theta_0} \begin{bmatrix} a \\ b \end{bmatrix} \text{ and } \begin{bmatrix} r \\ s \end{bmatrix} = \mathbf{G}_{\theta_0} \begin{bmatrix} f \\ g \end{bmatrix}$$

#### 2.5 CORDIC algorithm

The CORDIC algorithm [7] (Coordinate Rotation Digital Computer) is an implementation that can compute a real-valued Givens rotation. Like the Givens rotation, it can be used to perform a QR-decomposition. We start from the Givens rotation by angle  $\theta$ , and rewrite it in terms of tan( $\theta$ ):

$$\begin{bmatrix} x \\ y \end{bmatrix} = \begin{bmatrix} \cos(\theta) & \sin(\theta) \\ -\sin(\theta) & \cos(\theta) \end{bmatrix} \begin{bmatrix} a \\ b \end{bmatrix} \Rightarrow \begin{cases} x = a\cos(\theta) + b\sin(\theta) \\ y = -a\sin(\theta) + b\cos(\theta) \end{cases}$$

$$x = \cos(\theta)(a + b\tan(\theta)) \quad (2.5)$$

$y = \cos(\theta)(b - a\tan(\theta))$  (2.6)

The CORDIC algorithm can implement Givens rotations by computing equation (2.5) and 2.6 iteratively, but restricting each iteration to angles  $\theta = d_i\beta_i$  chosen so that  $\beta_i = \arctan(2^{-i})$  and  $d_i \in \{-1, 1\}$ . When the  $\cos(\theta)$  term is omitted, each iteration is reduced to an addition and bit shift. The first iteration uses  $\tan(\beta_0) = 1, \beta_0 = 45^\circ$ . The next iteration uses  $\tan(\beta_1) = 0.5, \beta_1 = 26.56...^\circ$  and so on with smaller and smaller angles.

The key to CORDIC is how  $d_i$  is chosen. In the *vectoring mode*,  $d_i$  is chosen to be sign( $y_{i-1}$ ). Each iteration will therefore compute ( $x_i, y_i$ ) where the y-component goes toward 0. If the input vector is (a, b), the result approaches ( $K\sqrt{a^2 + b^2}$ , 0). Here,  $K = \prod_{i=0}^{k-1} \cos(d_i\beta_i)$  which accounts for the  $\cos(d_i\beta_i)$  factors in each iteration for a total of k iterations. By computing  $\theta_i = \sum_{j=0}^{i} d_j\beta_j$ , the total accumulated angle is also found. This way the original vector has been converted from rectangular to polar coordinates.

If  $d_i$  is instead chosen to be sign( $\theta - \theta_i$ ) where  $\theta$  is some desired rotation angle, the CORDIC is said to be in *rotating mode*. Each iteration will rotate the input vector (a, b) closer and closer to K(x, y), being the original vector rotated by  $\theta$ . If the desired rotation angle comes from a vectoring CORDIC algorithm, there is no need to compute  $\theta$ . Instead, the sequence  $d_i$  can be directly transmitted from vectoring to rotating CORDIC as described by Gao [8]. Gao also shows one method for making CORDIC handle *coarse rotation*, i.e. cases where a or b are negative.

The scaling factor *K* is shown in **equation (2.7)**, for *k* number of stages. Its inverse S = 1/K is used after the last stage to correct the result. Since  $\cos(\cdot)$  is even, the choices of  $d_i$  do not affect the result. For large  $k, K \approx 1.6467602...$  and  $S = 1/K \approx 0.6072529...$ . Typically, the number of stages is chosen to be one larger than the number of bits precision needed.

$$K = \prod_{i=0}^{k-1} \cos(d_i \arctan(2^{-i})) = \prod_{i=0}^{k-1} \frac{1}{\sqrt{1+2^{-2i}}}$$

(2.7)

### 2.6 QR-decomposition

A QR-decomposition is a factorization of a matrix *A* into the product *QR* where *Q* is an orthogonal matrix and *R* is an upper triangular matrix. Since *Q* is orthogonal, we also have  $Q^H A = R$ .

$Q^H$  may be constructed by a series of Givens rotations or CORDIC operations. This concept is shown for a 3 × 3 matrix below. In each step the two rightmost matrices are multiplied.

$$R = Q^{H}A = G_{3}G_{2}G_{1}A$$

$$= \begin{bmatrix} 1 & 0 & 0 \\ 0 & c_{3} & s_{3} \\ 0 & -s_{3}^{*} & c_{3} \end{bmatrix} \begin{bmatrix} c_{2} & s_{2} & 0 \\ -s_{2}^{*} & c_{2} & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 \\ 0 & c_{1} & s_{1} \\ 0 & -s_{1}^{*} & c_{1} \end{bmatrix} \begin{bmatrix} a_{0,0} & a_{0,1} & a_{0,2} \\ a_{1,0} & a_{1,1} & a_{1,2} \\ a_{2,0} & a_{2,1} & a_{2,2} \end{bmatrix}$$

$$= \begin{bmatrix} 1 & 0 & 0 \\ 0 & c_{3} & s_{3} \\ 0 & -s_{3}^{*} & c_{3} \end{bmatrix} \begin{bmatrix} c_{2} & s_{2} & 0 \\ -s_{2}^{*} & c_{2} & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} a_{0,0} & a_{0,1} & a_{0,2} \\ a_{1,0}^{*} & a_{1,1}^{*} & a_{1,2}^{*} \\ 0 & a_{2,1}^{*} & a_{2,2}^{*} \end{bmatrix}$$

$$= \begin{bmatrix} 0 & 0 & 0 \\ 0 & c_{3} & s_{3} \\ 0 & -s_{3}^{*} & c_{3} \end{bmatrix} \begin{bmatrix} a_{0,0}^{\prime} & a_{0,1}^{\prime} & a_{0,2}^{\prime} \\ 0 & a_{1,1}^{\prime} & a_{1,2}^{\prime} \\ 0 & a_{2,1}^{\prime} & a_{2,2}^{\prime} \end{bmatrix}$$

$$= \begin{bmatrix} a_{0,0}^{\prime} & a_{0,1}^{\prime} & a_{0,2}^{\prime} \\ 0 & a_{1,1}^{\prime \prime \prime} & a_{2,2}^{\prime \prime} \end{bmatrix}$$

In the first step, the Givens rotation  $G_1$  that affects all of row 2 and 3 is chosen based on vector ( $a_{1,0}, a_{2,0}$ ) (highlighted in blue) so that element  $a_{2,0}$  becomes zero (shown underlined in subsequent line). This same processing step repeats until all elements under the diagonal in the first column are zeroed, before continuing with the second column.

In general, each step takes a vector (a, b), rotates it to (r, 0), and applies the same rotation angle to the other vectors occupying the same rows. The rotation angle is  $\arctan(b, a)$ , but explicit computation of  $\arctan(\cdot)$  is in fact not required. By use of basic trigonometric relationships with the illustration of **figure 2.3** (b), we find that:

$$r = \sqrt{a^2 + b^2}$$

$c = \frac{a}{\sqrt{a^2 + b^2}}$   $s = \frac{b}{\sqrt{a^2 + b^2}}$

Clearly, *s* and *c* can be found directly without any trigonometric function. An algorithm for Givens rotation for the case when *a* and *b* are complex is presented by Bindel et.al [6], and is shown in **algorithm 2.2**.

if b = 0 then

r = cf + sg

c = 1; s = 0; r = a  $s = -s^*f + cg$

else if a = 0 then

$s = -s^*f + cg$

$c = 0; s = sign(b^*); r = |b|$  else

$c = |a|/\sqrt{|a|^2 + |b|^2}$   $s = sign(a)b^*/\sqrt{|a|^2 + |b|^2}$

$r = sign(a)\sqrt{|a|^2 + |b|^2}$

**Algorithm 2.2** Complex givens rotation. Left side rotates (a, b) to zero b, resulting in (r, 0) and rotation parameters c and s. The right side uses c and s to rotate a different vector  $(f, g) \rightarrow (r, s)$ .

CORDIC can also be used for QR-decomposition, performing the same function as **algorithm 2.2**. First assume real matrix elements. In the first step of the earlier example, applying CORDIC in vectoring mode to  $(a_{1,0}, a_{2,0})$  (highlighted in blue) gives the result  $(a'_{1,0}, 0)$  and the angle  $\theta_1 = \arctan(a_{2,0}, a_{1,0})$ . CORDIC in rotating mode can then take this  $\theta_1$  angle and rotate the remaining vectors  $(a_{1,1}, a_{2,1}) \rightarrow (a'_{1,1}, a'_{2,1})$  and  $(a_{1,2}, a_{2,2}) \rightarrow (a'_{1,2}, a'_{2,2})$ . This is repeated to bring all elements under the diagonal to zero, just like with **algorithm 2.2**. Handling of complex values is described in more detail by Rader, Gao and Maltsev [9, 10, 11].

### 2.7 QR-decomposition-based RLS (QRD-RLS)

The QRD-RLS algorithm implements the RLS recursion by use of a QR-decomposition. It is described by **equation (2.8)** [12,ch10]:

$$\begin{bmatrix} \mathbf{R}[i] & \mathbf{p}[i] & \mathbf{s}[i] \\ \mathbf{0}^T & \alpha[i] & \gamma[i] \end{bmatrix} = \mathbf{Q}[i] \begin{bmatrix} \lambda^{1/2} \mathbf{R}[i-1] & \lambda^{1/2} \mathbf{p}[i-1] & \mathbf{0} \\ \mathbf{x}^T[i] & d[i] & 1 \end{bmatrix}$$

(2.8)

A QR-decomposition is applied to the right hand side matrix, which consists of the square root exponentially weighted covariance matrix R and p from the previous iteration, a constant column vector  $[0, \dots, 0, 1]^T$ , and the current data x[i] and d[i] which the algorithm is to operate on.

The QR-decomposition generates  $\alpha[i] = \gamma[i]\epsilon[i]$  and  $\gamma[i]$  explicitly.  $\epsilon[i]$  is the a priori estimation error in conventional RLS, which relates to the a posteriori error by the conversion factor  $\gamma[i]^2$  according to  $e[i] = \gamma^2[i]\epsilon[i]$ . It follows [12,ch3] that the a posteriori error can be calculated from the QR-decomposition result by  $e[i] = \gamma[i] \cdot \alpha[i]$ .

The algorithm is summarized in algorithm 2.3.

### 2.8 Inverse QRD-RLS (IQRD-RLS)

The IQRD-RLS algorithm is an implementation of the RLS recursion, which also makes use of a QR-decomposition. It builds on the QRD-RLS algorithm by appending an

$$R[-1] = \delta^{1/2}I$$

for each timestep  $i \ge 0$  do

$$\begin{bmatrix} R[i] \\ \theta^T \end{bmatrix} = Q[i] \begin{bmatrix} \lambda^{1/2}R[i-1] \\ x^T[i] \end{bmatrix}$$

{Find and apply  $Q[i]$ , update  $R[i]$ }

$$\begin{bmatrix} p[i] & s[i] \\ \alpha[i] & \gamma[i] \end{bmatrix} = Q[i] \begin{bmatrix} \lambda^{1/2}p[i-1] & 0 \\ d[i] & 1 \end{bmatrix}$$

{Apply  $Q[i]$ , find  $\alpha[i]$ ,  $\gamma[i]$ }

$$e[i] = \gamma[i] \cdot \alpha[i]$$

{Calculate error signal}

end for

Algorithm 2.3 The QRD-RLS algorithm

"inverse" matrix that can compute the optimal weights directly. It it is described by **equation (2.9)** [12,ch10]:

$$\begin{bmatrix} \widetilde{R}[i] & \widetilde{R}^{-T}[i] \\ \boldsymbol{0}^{T} & \boldsymbol{v}^{T}[i] \end{bmatrix} = \boldsymbol{Q}[i] \begin{bmatrix} \widetilde{R}[i-1] & \widetilde{R}^{-T}[i-1] \\ \widetilde{\boldsymbol{x}}^{T}[i] & \boldsymbol{0}^{T} \end{bmatrix}$$

(2.9)

$\widetilde{R}$  consists of the square-root exponentially weighted covariance matrices R and p from QRD-RLS and the scalar  $\gamma[i]$ . The rightmost columns contain  $\widetilde{R}^{-T} = (\widetilde{R}^{-1})^T$ , and as a consequence, scaled weights  $-w[i]/\gamma[i]$  appear in the rightmost column of  $\widetilde{R}^{-1}$  (or the bottom row of  $\widetilde{R}^{-T}$ ). The inverse matrix uses  $\lambda^{-1/2}$  instead of  $\lambda^{1/2}$  as forgetting factor.

$$\widetilde{\mathbf{R}}[i] = \begin{bmatrix} \lambda^{1/2} \mathbf{R}[i] & \lambda^{1/2} \mathbf{p}[i] \\ \mathbf{0}^T & \gamma[i] \end{bmatrix} \qquad \widetilde{\mathbf{R}}^{-T}[i] = \begin{bmatrix} \lambda^{-1/2} \mathbf{R}^{-T}[i] & \mathbf{0}^T \\ -\mathbf{w}[i]/\gamma[i] & 1/\gamma[i] \end{bmatrix}$$

$$\widetilde{\mathbf{x}}^T[i] = \begin{bmatrix} \mathbf{x}^T[i] & d[i] \end{bmatrix}$$

The algorithm is summarized in algorithm 2.4.

$$\begin{split} \widetilde{R}[-1] &= \begin{bmatrix} \delta^{1/2} I & \mathbf{0} \\ \mathbf{0}^T & \mathbf{0} \end{bmatrix} \\ \widetilde{R}^{-1}[-1] &= \begin{bmatrix} \delta^{-1/2} I & \mathbf{0} \\ \mathbf{0}^T & \mathbf{0} \end{bmatrix} \\ \text{for each timestep } i \geq 0 \text{ do} \\ &\begin{bmatrix} \widetilde{R}[i] \\ \mathbf{0}^T \end{bmatrix} = \widetilde{Q}[i] \begin{bmatrix} \lambda^{1/2} \widetilde{R}[i-1] \\ \widetilde{x}^T[i] \end{bmatrix} \\ \begin{bmatrix} \widetilde{R}^{-T}[i] \\ v'^T[i] \end{bmatrix} = \widetilde{Q}[i] \begin{bmatrix} \lambda^{-1/2} \widetilde{R}^{-T}[i-1] \\ \mathbf{0}^T \end{bmatrix} \\ \\ &\begin{bmatrix} \widetilde{R}^{-T}[i] \\ v'^T[i] \end{bmatrix} = \widetilde{Q}[i] \begin{bmatrix} \lambda^{-1/2} \widetilde{R}^{-T}[i-1] \\ \mathbf{0}^T \end{bmatrix} \\ \\ & \mathbf{W}[i] = -\gamma[i] \cdot - \mathbf{W}[i]/\gamma[i] \\ \\ \text{Found in } \widetilde{R}[i] \text{ and } \widetilde{R}^{-T}[i] \\ \\ \\ & \text{end for} \end{split}$$

### Algorithm 2.4 The IQRD-RLS algorithm

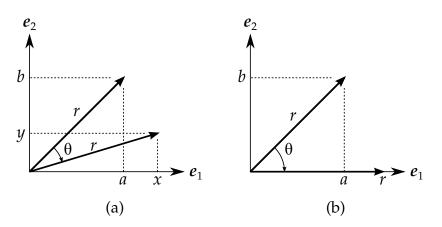

### 2.9 Systolic array implementation of RLS algorithms

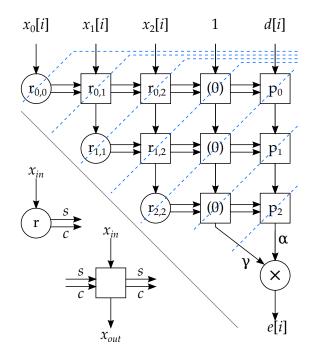

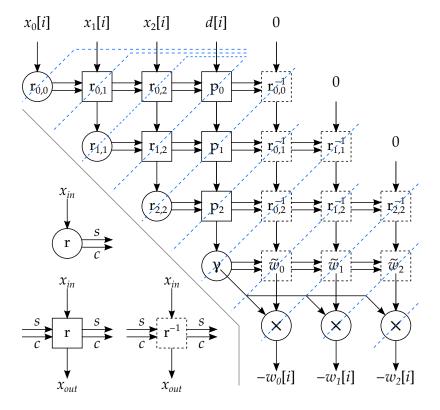

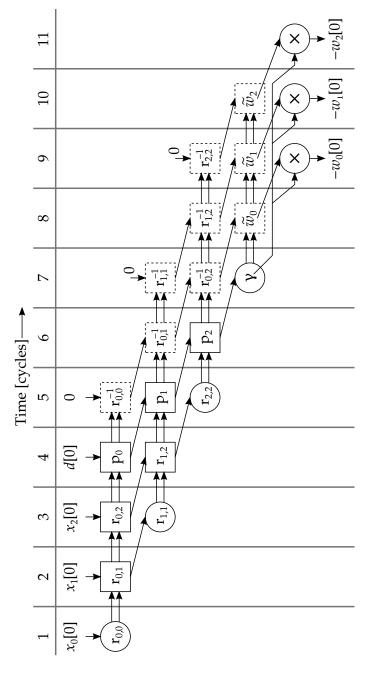

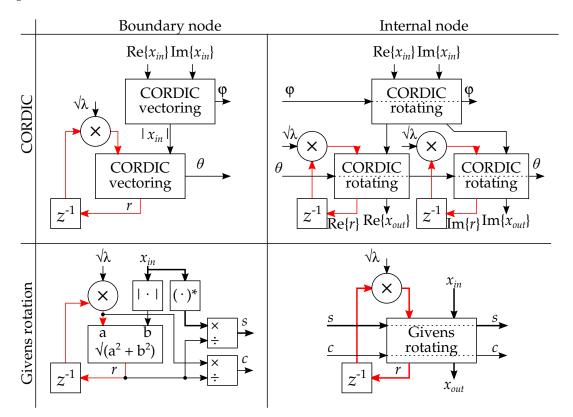

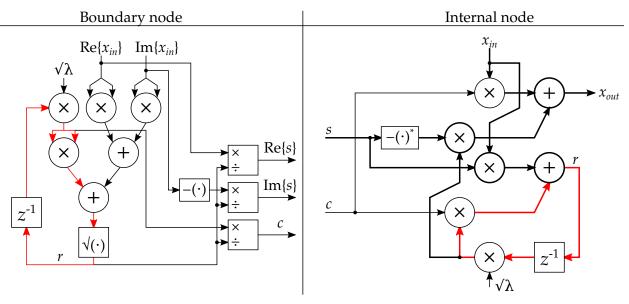

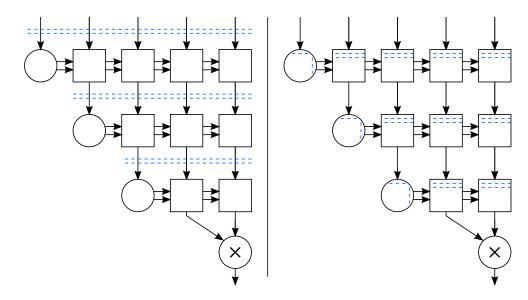

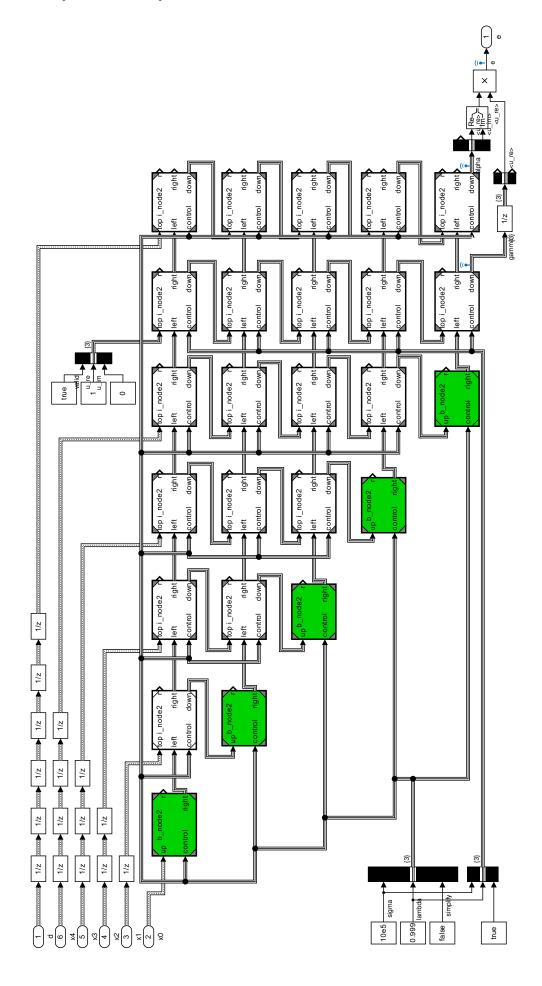

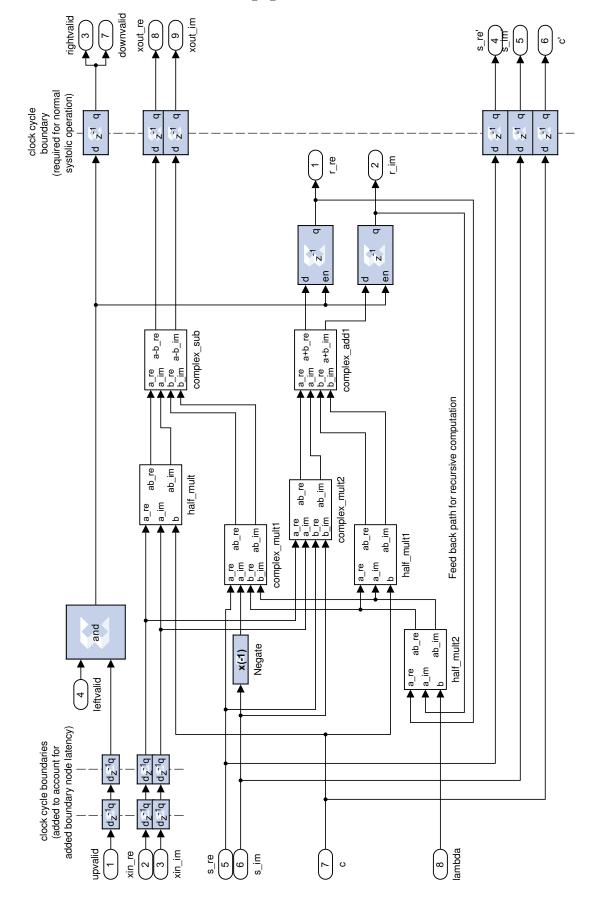

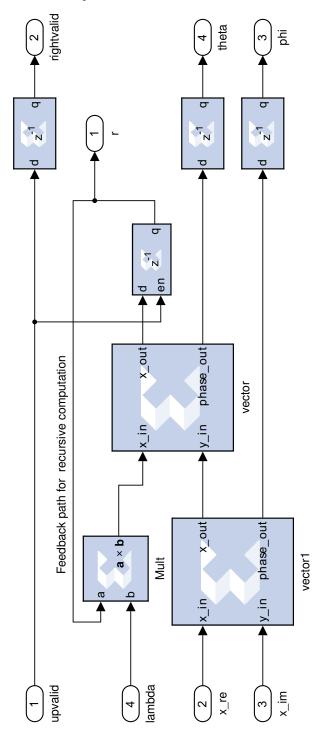

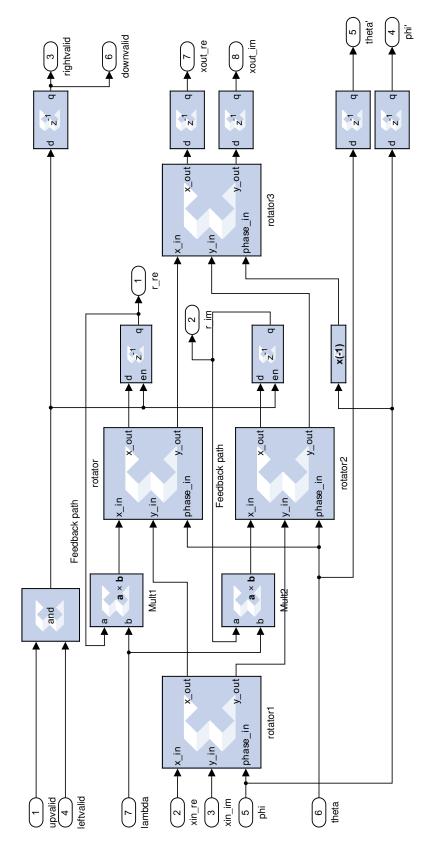

The QRD-RLS and IQRD-RLS algorithm may be implemented by using a systolic array architectures shown in **figure 2.4**. Figure is adapted from Harteneck and Stewart, and Ma and Parhi [13, 12]. The array consists of two types of nodes; boundary nodes (circles), and internal nodes.

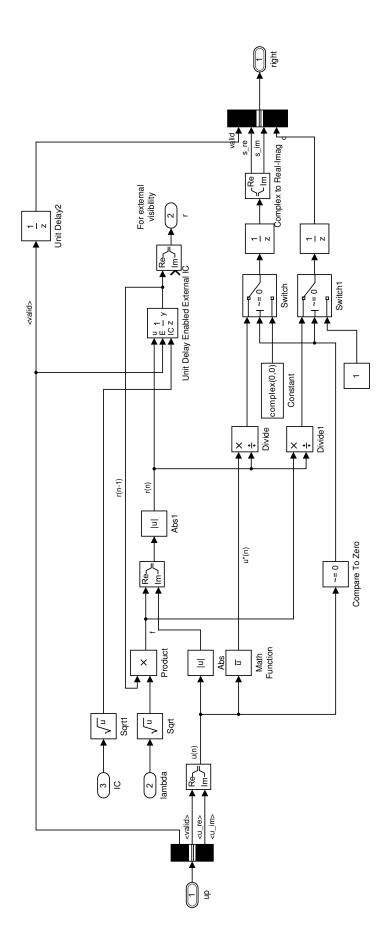

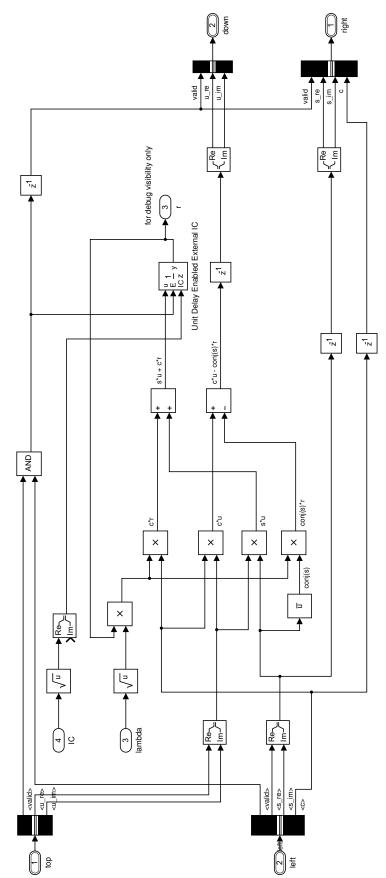

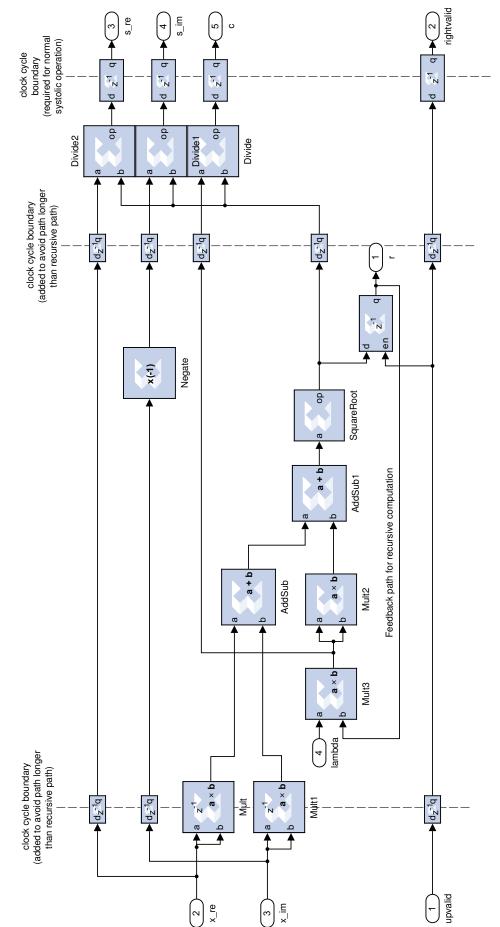

Every labeled node stores a recursive variable indicated by the label, corresponding to elements from the matrices of **equation (2.8)** or **equation (2.9)** depending on which system is implemented. The recursive path from the previous iteration to the next includes a multiplication by the square root of the forgetting factor  $\lambda^{\pm 1/2}$ . This is contained within each node and not shown in the figure. Nodes labeled  $p_m$  store elements of p, etc. For instance, at any given iteration i, node  $p_0$  computes  $p_0[i]$  by using the previous value weighted with the forgetting factor;  $\lambda^{1/2} \cdot p_0[i-1]$ . Column nodes marked (0) in the QRD-RLS do not have any recursive variable, and the value used in the QR-decomposition is a constant 0.

The boundary nodes compute *c* and *s* parameters for a Givens rotation of the vector  $(\lambda^{1/2}r_{n,n}[i], x_{in}[i])$  where  $r_{n,n}[i]$  is the variable stored in the node, and  $x_{in}[i]$  is the signal received from the nodes top input. Internal nodes propagate *c* and *s* parameters to the right, and apply the received *c* and *s* parameters to rotate the vector  $(\lambda^{\pm 1/2}r_{m,n}[i], x_{in}[i])$ . Again,  $r_{m,n}[i]$  is the internal variable and  $x_{in}[i]$  is the nodes top input. The internal nodes drawn with dotted lines represent  $\widetilde{\mathbf{R}}^{-T}$  of equation (2.9) and use  $\lambda^{-1/2}$ , while all other nodes use  $\lambda^{1/2}$ .

Boundary and internal node operation may be described in a new algorithm, similar to the givens rotation from algorithm 2.2. If we assume that boundary nodes  $r_{n,n}$  are initialized with real, non-negative numbers and connected like shown in figure 2.4, it follows that they will remain real and positive, leading to simplifications shown in algorithm 2.5. Here, the multiplication with the square root forgetting factor is included.

|                                                                 | 1+1/2                                                                            |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------|

| if $x_{in} = 0$ then                                            | $r = cA^{\pm i/2}r + SX_{in}$                                                    |

| $c = 1; s = 0; r = \lambda^{1/2}r$                              | $r = c\lambda^{\pm 1/2}r + sx_{in}$ $x_{out} = -s^*\lambda^{\pm 1/2}r + cx_{in}$ |

| else if $r = 0$ then                                            | c = c                                                                            |

| $c = 0; s = \operatorname{sign}(x_{in}^*); r =  x_{in} $        | s = s                                                                            |

| else                                                            |                                                                                  |

| $c = \lambda^{1/2} r / \sqrt{(\lambda^{1/2} r)^2 +  x_{in} ^2}$ |                                                                                  |

| $s = x_{in}^* / \sqrt{(\lambda^{1/2}r)^2 +  x_{in} ^2}$         |                                                                                  |

| $r = \sqrt{(\lambda^{1/2}r)^2 +  x_{in} ^2}$                    |                                                                                  |

**Algorithm 2.5** QRD-RLS and IQRD-RLS boundary node operation (left) and internal node operation (right) using givens rotations. Inverse internal nodes of IQRD-RLS use  $\lambda^{-1/2}$ , all others use  $\lambda^{1/2}$

Chapter 2. Theory

A benefit of the systolic array is its regularity and locality. Blue dotted lines in **figure 2.4** shows how latency can be added so that each node only has to provide its results to its neighbors during one cycle, without the need for global signals except the clock. This reduction of signal path length and delay gives an increase in the possible execution speed. A consequence is that inputs at the top of the array must be delayed by different amounts.

**Figure 2.4** Examples of QRD-RLS (top) and IQRD-RLS (bottom) systolic array structures for MN = 3. Latencies can be added as suggested with blue dotted lines.

## 3 Design

### 3.1 Requirements

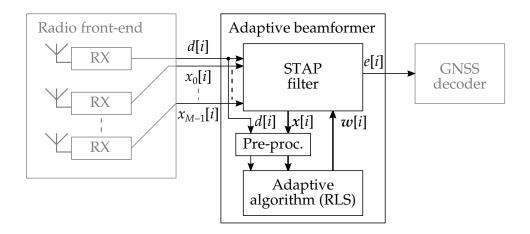

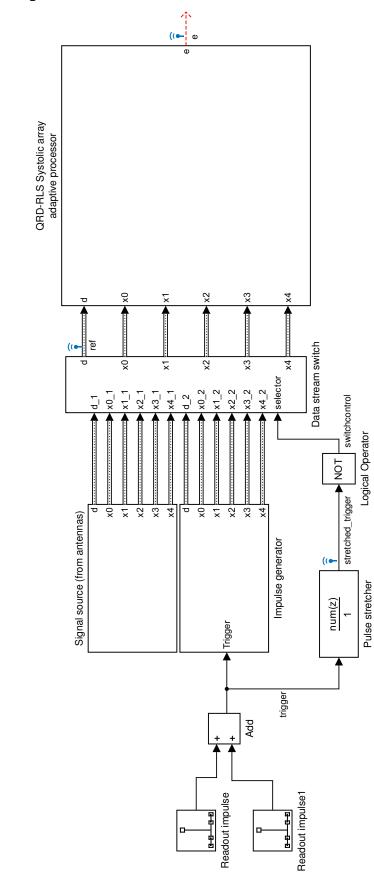

This section describes the problem from the assignment text in more detail. The beamformer, which is the focus of this thesis, is shown in relation to surrounding systems in **figure 3.1**. Each antenna is followed by a digital demodulator which downmixes and samples the received RF signals. This is contained in the radio front-end block.

**Figure 3.1** System diagram showing the multi channel radio front-end, the adaptive beamformer and the GNSS decoder.

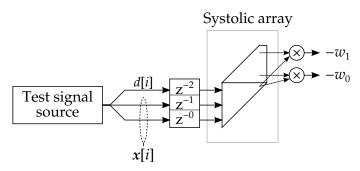

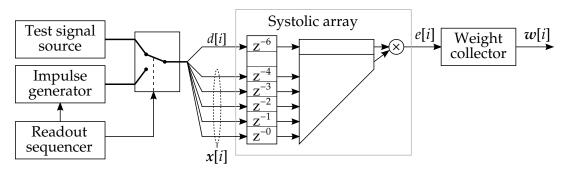

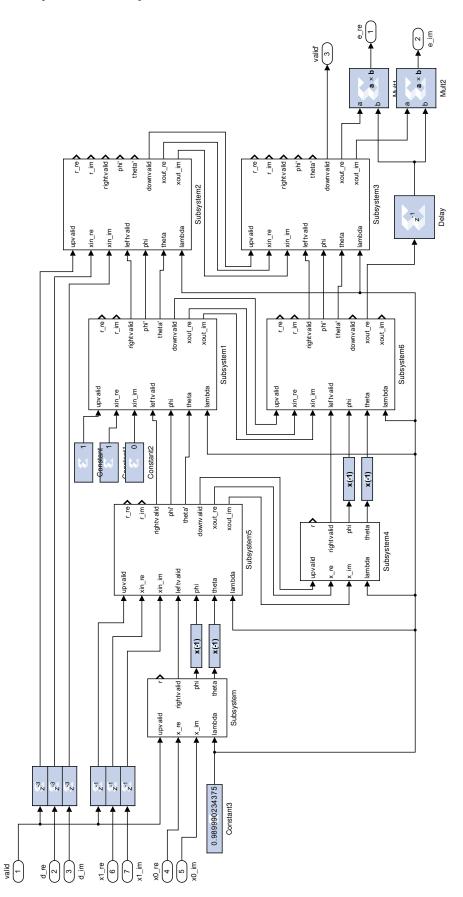

The STAP filter is shown in more detail in **figure 3.2**. It is a combination of the STAP filter described in **section 2.1**, and the MMSE criterion of **section 2.2**. The first channel is designated as the reference channel d[i]. Signals from the remaining M channels at N sample times (taps) are grouped into the  $1 \times MN$  vector x[i] according to **equation (2.1)**. The STAP filter computes  $e[i] = d[i] - w[i]^H x[i]$  which is passed on to the downstream signal processing which can further decode and demodulate the desired signal.

Signals d[i] and x[i] are also passed to the adaptive algorithm. The objective of this algorithm in this system is to find the filter weights w[i] that minimize the power in e[i], which is equivalent to least squares filtering if e[i] is considered to be the error signal. Least squares filtering can be performed with many algorithms[1], for instance Sample Matrix Inversion (SMI), Least Mean Squares (LMS), genetic algorithms or Recursive Least Squares (RLS). This thesis is limited to considering RLS which compared to the other methods has fast convergence speed but high computational load.

The desired signal is supposed to be a spread-spectrum Global Navigation Satellite System (GNSS) signal. A pre-processor is drawn in **figure 3.1** that will "hide" this desired signal in the signal passed on to the adaptive algorithm, via an unspecified method. The desired signal is hidden to prevent the beamformer from suppressing it. The test signals used in this thesis do not contain GNSS signals, only only jammer

**Figure 3.2** Modified STAP filter modelled after the MMSE criterion. Adaptive algorithm (not shown) is used to update weights  $w_{m,n}$ .

and noise floor. For this reason, the pre-processor can be assumed to pass d[i] and x[i] through unmodified.

A total of M + 1 = 6 antennas are available, of which the first is designated as the reference antenna. The number of taps N is suggested to be in the range 1-4. d[i] and x[i] are complex, discrete-time signals available at a rate of 125 MHz. The data is available in signed integer format, with 16 bits for each of the real and imaginary parts. It is desired for the system to find a solution to the filter weights within 0.1 ms after the jammer is enabled.

### 3.2 Test signal set

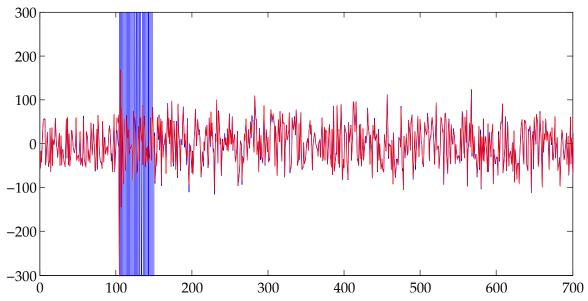

Test signals were provided by KDS to use for evaluation of the algorithms performance. Two sets of signals were supplied, each containing different jammer signal characteristics. Each set consisted of six channels, one for each of the antenna. Both data sets start with approximately 100 samples of uncorrelated noise floor, followed by a strong jamming signal from a single direction that does not move. The noise floor samples were approximately in the value range  $\pm 60$  for each of the real and imaginary part. Description of each signal set follows.

### 3.2.1 Multi-tone step from static jammer

In the left column of **figure 3.3** it can be seen that the jammer signal amplitude spans roughly  $\pm 5000$  in both the real and imaginary components (imaginary part not shown).

3.3 Sample Matrix Inversion (SMI) vs Recursive Least Squares (RLS) performance

Distinct tones/peaks are visible in the spectrum. This signal is referred to as the *multi-tone* test signal.

#### 3.2.2 Broadband step from static jammer

This data set was similar to the Multi-tone in that it is a static scenario with a power step, but the spectrum is broader and the signal amplitude and power is greater. It is illustrated in the right column of **figure 3.3**. The jammer signal amplitude spans approximately  $\pm 15000$  in both the real and imaginary components (imaginary part not shown). This signal is referred to as the *broadband* test signal.

**Figure 3.3** Test signals showing a multitone signal (left) and a broadband signal (right). The time domain plots (top) show the step in power near sample 100, while the FFT plots (bottom) show relative differences between the spectra. Only reference channel is shown.

# 3.3 Sample Matrix Inversion (SMI) vs Recursive Least Squares (RLS) performance

To evaluate the performance of RLS, the SMI method is used as a reference. RLS was compared with SMI by applying both algorithms to the test data sets, with varying antenna/tap configurations, K and  $\lambda$  parameters. Performance is quantified by first

#### Chapter 3. Design

estimating the time-averaged power level of the reference channel when jammer is *not* active. This section of the signal will be referred to the *noise* portion of the signal. The power level at the beamformer output e[i] is then estimated using the same method on a section where both noise and jammer signals are present on the input. This number is then converted to decibels relative to the noise power level and is used for comparisons. Signal power is estimated with **equation (3.1)** where f[i] is the chosen section of the signal.

$$P = \frac{1}{N} \sum_{i=k}^{k+N-1} f[i] f^*[i]$$

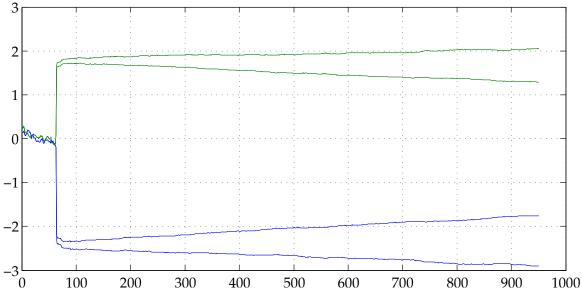

(3.1)

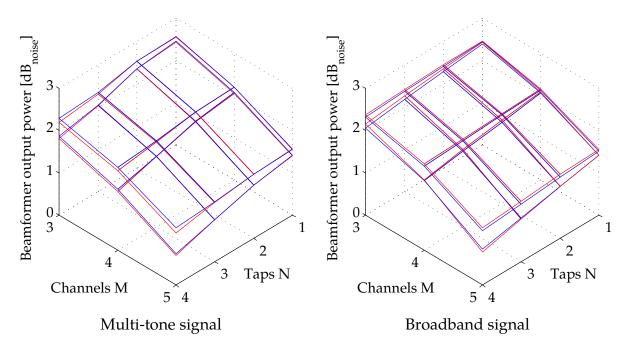

RLS was implemented according to **algorithm 2.1**, and MATLAB code is included in **appendix C.3**. The additional signals introduced by STAP filter taps were created using code in **appendix C.1**. For the comparison, a causal SMI was used as in **equation (2.3)**, with code included in **appendix C.2**. A principal difference between RLS and SMI is that RLS uses an exponential window for estimating the correlation matrices, while SMI uses a rectangular window. This makes direct comparison difficult, since the rectangular window length *K* has no direct relationship to the exponential forgetting factor  $\lambda$ . To handle this, values of *K* and  $\lambda$  were chosen to get approximately similar performance. From the plot in **figure 3.4**, it is seen that SMI with *K* = 125 performs similarly to RLS with  $\lambda$  = 0.995. The same is true for *K* = 500 and  $\lambda$  = 0.999. This is seen by the two sets of red/blue planes overlapping.

**Figure 3.4** Surfaces show output power from SMI (red) and RLS (blue) algorithms for different channel/tap configurations. Within each plot are four surfaces, the blue RLS results for  $\lambda = 0.995$  (lower) and  $\lambda = 0.999$  (upper), and the red SMI results for K = 125 (lower) and K = 500 (upper).

3.3 Sample Matrix Inversion (SMI) vs Recursive Least Squares (RLS) performance

**Figure 3.4** also shows how the output power is reduced as taps and channels are added. For the broadband signal, additional taps have very little effect. An interesting observation is that the performance for multi-tone and broadband test signals is quite similar, despite the broadband jammer power being approximately 10 times stronger.

The absolute performance is not the main point here, since this can be changed by modifying *K* and  $\lambda$ . The point is that an RLS-based beamformer can perform equivalently to an SMI algorithm by selecting  $\lambda$  appropriately. In **figure 3.4** this is seen by the close overlap of red and blue surfaces.

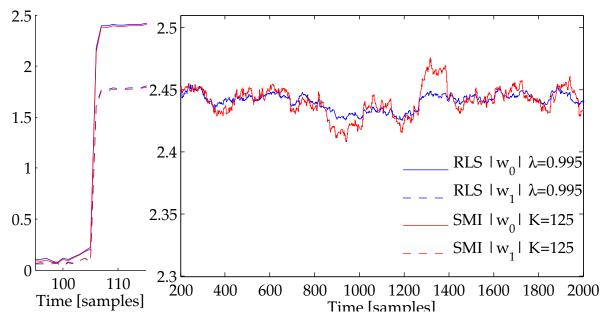

Another aspect besides steady state performance, is the transient performance of the algorithm. To demonstrate this, the filter weights produced by SMI and RLS were compared and are presented in figure 3.5.

**Figure 3.5** Filter weight magnitude behavior for M = 2, N = 1 configuration, multitone test signal. Left graph shows both filter weights at the moment when the jammer is activated. Right graph shows the steady state variation in a single weight  $|w_0|$ .

From the left part of the figure it is clear that RLS and SMI behave similarly with regards to convergence time, as they both converge within 3-4 samples. SMI and RLS filter weights stay around the same average value, but it is noted that SMI filter weights vary more than those produced by RLS. The variations themselves are caused by the uncorrelated noise in the channels and the variance present in any statistical estimator, and the same effect is also observed with the broadband test signal. This suggests that RLS and SMI react to noise differently.

A conclusion that can be drawn from these results is that RLS can perform equivalently to SMI on the test signals. For further development of an RLS implementation, comparison to conventional RLS is sufficient.

### 3.4 RLS parameters

Adjustable parameters for RLS consist of the forgetting factor  $\lambda$ , the initialization value  $\delta^{-1}$  in the inverse correlation matrix P and the initial filter weights w[-1]. We can set  $w[-1] = \begin{bmatrix} 0 & \cdots & 0 \end{bmatrix}^T$  to start the system with no particular beamforming, effectively eliminating the signals from all except the reference antenna.

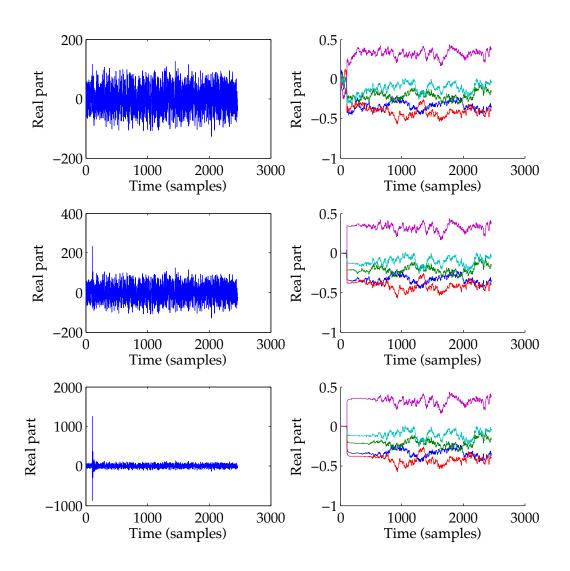

To illustrate the effect of the  $\delta$  parameter, a range of simulations with different values for  $\delta$  are shown in **figure 3.6**.

**Figure 3.6** Real component of beamformer output e[i] (left), and filter weight behavior (right) for multi-tone signal, M = 5, N = 1,  $\lambda = 0.99$  and varying  $\delta \in \{10^5, 10^6, 10^8\}$  from top to bottom. Colors blue, green, red, cyan, purple correspond to weights  $w_0$  through  $w_4$ .

In all the simulations the beamformer output stabilizes on the same range of values approximately between  $\pm 100$ . The effect of  $\sigma$  is seen in the beamformer output around

sample 100. When the jammer is enabled, an excursion is visible for  $\delta \in \{10^6, 10^8\}$ . The cause of the excursion is that the inverse correlation matrix P is initialized for a much higher power than is present in the input signal. The algorithm is therefore less sensitive to the relatively weak jammer, until P converges to reflect the actual signal power level.

This dynamic is also seen in the filter coefficients. For  $\delta \in \{10^6, 10^8\}$  the weights start out smoothly, but gradually become more erratic. To get useful results,  $\delta$  is chosen so that the algorithm converges to the noise power level before the jammer is enabled.  $\delta = 10^5$  was found to be acceptable.

When  $\lambda$  is varied as shown in **figure 3.7**, there is no dramatic effect on the beamformer output amplitude, but filter weight behavior is quite different. When  $\lambda$  is closer to 1, the weights become more stable. From the derivation of RLS,  $\lambda$  is the constant which is used to weight the previous correlation matrix estimates. According to Haykin [5, p450],  $1/(1 - \lambda)$  can be thought of as the "memory" of the algorithm, thus a high  $\lambda$  should be expected to give more stable results.

### 3.4.1 Complexity and stability considerations

Conventional RLS has complexity  $O(q^2)$  where q is the degrees of freedom, i.e. the number of filter weights MN. For the system considered in this thesis the complexity is therefore  $O((NM)^2)$ . An overview of one possible breakdown of the calculations required by the RLS algorithm from **algorithm 2.1** was created, and is included for reference in **appendix D.1**. The total number of multiplications are  $3q^2 + 3q$ , and the number of additions are  $2q^2 + 2q$ . The single division and a few of the additions and multiplications have one real operand, and will as such require slightly less resources to implement than the remaining complex operations.

There does exist other algorithm variants that are mathematically equivalent to RLS, but use different internal variables and behave differently when implemented with limited numeric precision. The conventional RLS algorithm suffers from instability caused by limited precision, as described by Diniz [4, ch16] and Haykin [5, ch12]. Apolinário [12, ch2] states that instability in conventional RLS is encountered even with double precision floating point arithmetic.

Two other classes of algorithms that implement RLS are described in litterature. The first is the lattice filter. This variant was not considered in depth because it cannot output filter weights, and it also tends to be unstable [12, ch5.7]. The last class is the QRD-RLS filter of which several variants exist. Three variants of QRD-RLS were found in the litterature, and are compared;

- (QRD-RLS [12, 5], described in section 2.7.)

- IQRD-RLS, known as the *inverse* or *square root* QRD-RLS algorithm [12, 5], described in **section 2.8**.

**Figure 3.7** Real component of beamformer output e[i] (left), and filter weight behavior (right) for multi-tone signal, M = 5, N = 1,  $\delta = 10^5$  and varying  $\lambda \in \{0.98, 0.995, 0.999\}$  from top to bottom. Colors blue, green, red, cyan, purple correspond to weights  $w_0$  through  $w_4$ .

- FQRD-RLS, a *fast* QRD-RLS version utilizing the time shifting property of the input data [14, 12].

- MCFQRD-RLS, a *multi-channel* FQRD-RLS variant [15, 12].

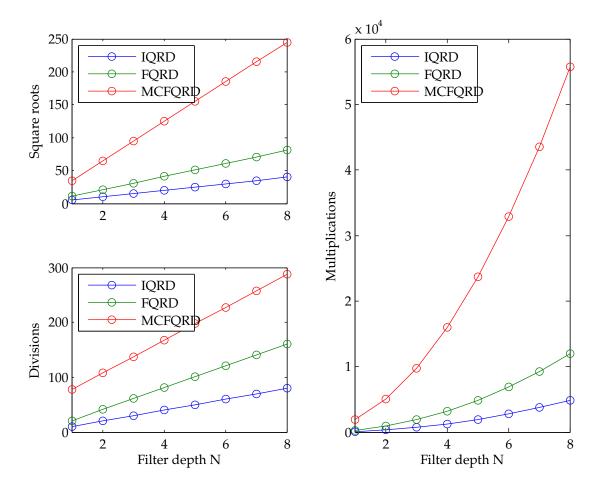

At first, QRD-RLS was not considered since it only computes the beamformer output e[i], and not w[i]. The inverse QRD-RLS is an extension to QRD-RLS that produces w[i] as part of its normal operation. For the fast variants, an additional procedure is required to extract the weights of the algorithm at a selected point in time. An overview of the computational complexity of the different algorithms is shown in **table 3.1**. "Filtering" refers to generation of e[i], while "WE" refers to the process of *weight extraction*.

| Table 3.1         Computational complexity per iteration for possible QR decomposition             |

|----------------------------------------------------------------------------------------------------|

| based RLS algorithms. <i>M</i> is the number of channels (excluding reference), <i>N</i> is number |

| of taps per channel. [15, 14]                                                                      |