### Wideband Harmonically Tuned Power Amplifier Design Based on GaN Technology for use in Envelope Tracking

**Richard Samuelsen**

Master of Science in Electronics Submission date: June 2015 Supervisor: Morten Olavsbråten, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

### **Problem Description**

Assignment title: Wideband Harmonically Tuned Power Amplifier Design Based on GaN Technology for use in Envelope Tracking

In many radio systems the efficiency of the power amplifier is extremely important. When a power amplifier is driven near its maximum output power, it will generate higher order harmonic frequency components. A way to increase the efficiency of the amplifier is to tune these components to a desired outcome. In class-F and class- $F^{-1}$ , also called harmonically tuned power amplifiers, the impedance of the harmonic components are tuned at the output of the amplifier. This will adjust the shape of the current and voltage, making the amplifier as efficient as possible. This is inherently a narrowbanded technique. Challenges regarding high efficiency operation will become present when designing a wideband power amplifier.

Harmonically tuned power amplifiers with static drain bias voltage will reach maximum efficiency around peak output power. In order to increase efficiency for lower input power the drain bias voltage can be decreased. The decrease of drain bias voltage will stimulate the transistor to enter compression for lower input signals, which in turn will produce harmonics. This technique is called envelope tracking.

The tasks of this assignment are:

- Study the principles of a harmonically tuned amplifier.

- Learn how to use simulation software (Keysight ADS).

- Design and simulate a power amplifier which exhibits maximum efficiency over a relatively large bandwidth.

- Make a layout of the amplifier and manufacture it.

- Measure and characterize the power amplifier.

Specifications for the PA:

| Center Frequency $(f_0)$ | 2.2 GHz                       |

|--------------------------|-------------------------------|

| Bandwidth (3 dB)         | 800 MHz                       |

| Output Power $(P_{out})$ | > 40 dBm within the bandwidth |

| Gain                     | > 12 dB within the bandwidth  |

| Input match $(S_{11})$   | < -10 dB within the bandwidth |

| Efficiency               | as high as possible           |

Supervisor: Associate Professor Morten Olavsbråten Issued at: Department of Electronics and Telecommunications, NTNU, Norway

### Summary

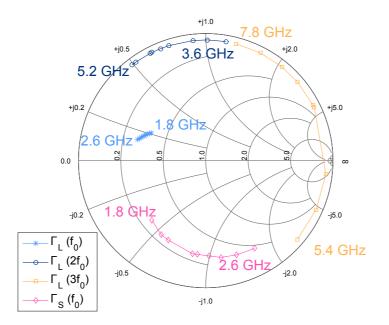

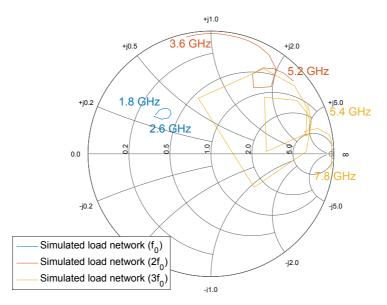

In this thesis, the design, simulation and measurements of a harmonically tuned 10 W wideband high efficiency power amplifier employing envelope tracking is presented. The simulations and design were carried out with the use of the CAD tool Keysight ADS. The optimal impedances for  $f_0$ ,  $2f_0$  and  $3f_0$  were mapped for both source and load with the help of the load pull technique, and matching networks were designed to try to model the optimal impedances. The matching networks consists of microstrip transmission lines and passive components.

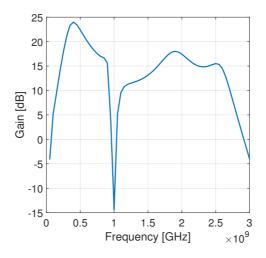

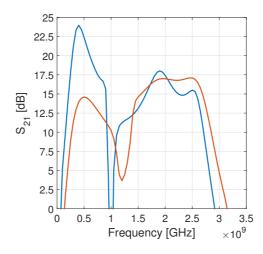

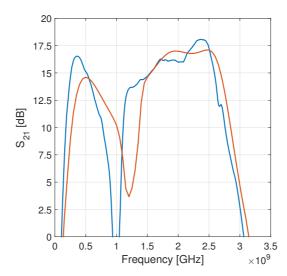

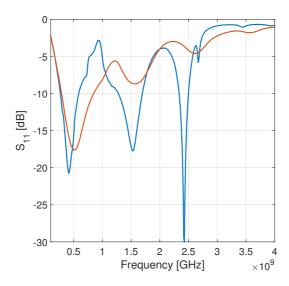

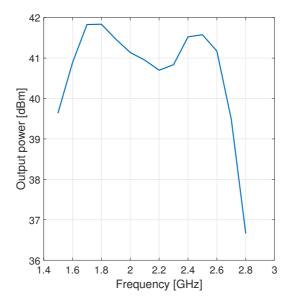

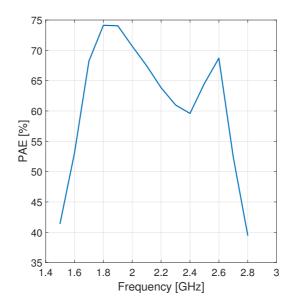

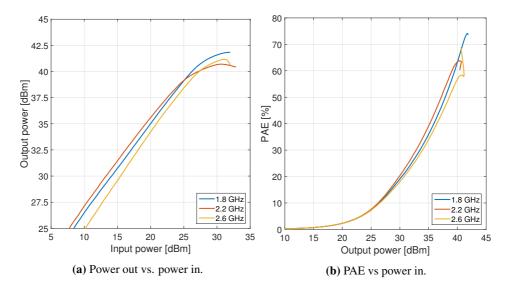

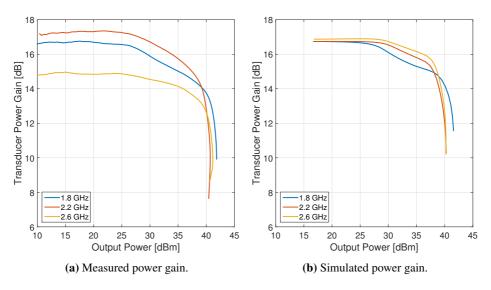

Simulations of the design with lossy components showed an average peak power added efficiency (PAE) of 67% from 1.8 GHz to 2.6 GHz while maintaining 40 dBm (10 W) output power. The final realized design was measured to deliver an average peak PAE of 66% from 1.8 GHz to 2.6 GHz while maintaining 40 dBm output power. The highest measured output was 41.8 dBm (15.1 W) at 1.8 GHz. For the small signal performance the gain was measured to be a maximum of 18.2 dB at 2.4 GHz and maintain 12 dB gain from 1.1 GHz to 2.65 GHz. A 3 dB bandwidth of 1.05 GHz, from 1.55 GHz to 2.6 GHz, was measured for the small signal gain. The input match ( $S_{11}$ ) requirement in the specifications was not fulfilled as this proved to be extremely hard, if not impossible while still fulfilling the rest of the specifications. A solution to reduce  $S_{11}$  is proposed at the cost of less gain and efficiency.

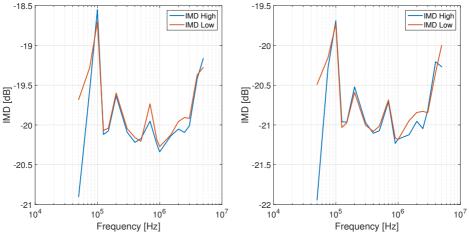

Microwave power amplifiers obtain maximum efficiency when operating close to the saturation point. For fixed bias amplifiers the saturation point is close to the maximum output power of the device. The saturation point is dependent on the supply voltage for the amplifier and by modulating the supply voltage high efficiency can be achieved for lower output power levels. Two schemes are used in this thesis to modulate the supply voltage, namely envelope tracking and power tracking. The strengths, weaknesses and the increase in efficiency are explored for the two methods for both two tone and 16-QAM signals. Two tone baseline measurements were taken at 1.8 GHz, 2.2 GHz and 2.6 GHz with a fixed supply voltage while the PA was close to 1 dB compression. This resulted in a PAE of 53%, 52%and 47%. Employing the tracking schemes to the amplifier resulted in a PAE of 63%, 59%and 53% for envelope tracking and 60%, 59% and 51% for power tracking. A 16-QAM baseline was established and resulted in 37%, 22% and 30% for the same frequencies as the two tone test. With the use of envelope tracking the PA was measured to have a PAE of 53%, 39% and 47%. The power tracking scheme resulted in a PAE of 48%, 32% and 39%. The measurements for the tracking schemes shows that the techniques are viable for complex modulation schemes with the use of linearization techniques.

### Sammendrag

I denne oppgaven ble design, simulasjon og målinger av en harmonisk tilpasset 10 W bredbåndet høy-effektivitets effektforsterker med implementasjon av envelope tracking utført. Simulasjonene ble utført ved hjelp av CAD programmet ADS levert av Keysight. De optimale impedansene for  $f_0$ ,  $2f_0$  og  $3f_0$  ble kartlagt ved hjelp av load pull, og tilpassningsnettverk ble designet for å modellere de optimale impedansene. Tilpassningsnettverket består av microstrip transmisjonslinjer og passive kretskomponenter.

Ikke-ideelle simuleringer av designet resulterte i en gjennomsnittlig maksimal power added efficiency (PAE) på 67% fra 1,8 GHz til 2,6 GHz med mer enn 40 dBm (10 W) utgangseffekt. Det endelige utlegget ble målt til å ha en gjennomsnittlig maksimal PAE på 66% fra 1,8 GHz til 2,6 GHz med overkant av 40 dBm (10 W) utgangseffekt. Den høyeste leverte effekten ble målt til 41,8 dBm (15,1 W) ved 1,8 GHz. Småsignalforsterkningen ble målt til en maksimal verdi på 18,2 dB ved 2,4 GHz og opprettholdt 12 dB forsterkning fra 1,1 GHz til 2,65 GHz. En 3 dB båndbredde på 1,05 GHz fra 1,55 GHz til 2,6 GHz ble oppnådd i målinger. Kravet til inngangstilpassningen ( $S_{11}$ ) ble ikke opprettholdt da dette viste seg å være veldig vanskelig, om ikke umulig gitt resten av spesifikasjonene. En potensiell løsning for å redusere  $S_{11}$  er foreslått på bekostning av forsterkning og effektivitet.

Mikrobølge effektforsterkere når maksimal effiktivitet når utganseffekten nærmer seg metningspunktet. For forsterkere med konstant forsyningsspenning er metningspunktet nær maksimal utgangseffekt. Metningspunktet er avhengig av forsyningsspenningen og ved å modulere denne kan høy effiktivitet oppnås for lavere utgangseffekter. To forskjellige funksjoner er brukt for å modulere forsyningsspenningen til forsterkeren, nemlig envelope tracking og power tracking. Styrkene, svakhetene og økningen i effektivitet er utforsket for begge metodene for både to tone og 16-QAM signaler. Målingsgrunnlaget for to-tone testen ble gjennomført på 1,8 GHz, 2,2 GHz og 2,6 GHz med resulterende PAE målinger på 53%, 52% og 47%. Ved å bruke tracking metodene på effektforsterkeren ble PAE målt til 63%, 59% og 53% for envelope tracking og 60%, 59% og 51% for power tracking. 16-QAM målingsgrunnlaget ble foretatt med statisk bias for de samme frekvensene som to-tone målingene. Disse målingene førte til en PAE på 37%, 22% og 30%. Ved å bruke envelope tracking ble effektforsterkeren målt til å ha en PAE på 53%, 39% og 47%. Med power tracking ble PAE målt til 48%, 32% og 39%. Målingene av forsterkeren med modulert forsyningsspenning viser at metoden er effektiv med tanke på å øke effektiviteten, men lineariseringsteknikker må bli brukt får å redusere de tilførte ulinearitetene.

### Preface

This thesis is submitted in partial fulfilment with the requirements for the degree of Master of Science (MSc) at the Department of Electronics and Telecommunications, Norwegian University of Science and technology (NTNU). The work was carried out in the time period January 2015 to June 2015, under the supervision of Asc. Prof. Morten Olavsbråten, who is with the Department of Electronics and Telecommunications at NTNU.

#### Acknowledgement

First and foremost I would like to thank Asc. Prof. Morten Olavsbråten for his valuable help and input with this thesis. His vast knowledge on the topic of RF power amplifiers helped me to find a good solution and motivate me to solve the problem presented. His enthusiasm combined with his willingness to give comprehensive, detailed answers to my questions were of great importance to me. A special thanks goes to all the wonderful people I have studied with here at NTNU, making these years unforgettable. I would like to thank my family and friends back in Horten for their great support during my 5 year period in Trondheim. I would also like to thank PhD cand. Dragan Mitrevski for help with troubleshooting some of the measured results. Lastly I would like to thank the people at the electronics and prototype laboratory who manufactured the microstrip PCB for the amplifier.

Trondheim, Norway, June 2015. Richard Samuelsen

### Table of Contents

| Pr | oblen                                                | n Description                                                                                                                                                                                                                                           | i                                                                |

|----|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Su | mma                                                  | ry                                                                                                                                                                                                                                                      | iii                                                              |

| Sa | mmei                                                 | ndrag                                                                                                                                                                                                                                                   | iv                                                               |

| Pr | eface                                                |                                                                                                                                                                                                                                                         | v                                                                |

| Та | ble of                                               | f Contents                                                                                                                                                                                                                                              | viii                                                             |

| Li | st of 7                                              | <b>Fables</b>                                                                                                                                                                                                                                           | ix                                                               |

| Li | st of I                                              | Figures                                                                                                                                                                                                                                                 | xii                                                              |

| Ał | obrevi                                               | iations                                                                                                                                                                                                                                                 | xiii                                                             |

| 1  | <b>Intro</b><br>1.1                                  | oduction<br>Outline of the thesis                                                                                                                                                                                                                       | 1<br>3                                                           |

| 2  | The                                                  | ory                                                                                                                                                                                                                                                     | 5                                                                |

|    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8 | S-parameters         Stability         2.2.1         Stability Circles         Gain         Matching         Efficiency         Linearity         Memory effects         Amplifier Classes         2.8.1         Class-A         2.8.2         Class-AB | 5<br>6<br>7<br>8<br>10<br>11<br>11<br>12<br>14<br>14<br>14<br>14 |

|    |                                                      | 2.8.3 Class-AB                                                                                                                                                                                                                                          | 15                                                               |

|    |        | 2.8.4 Class-C                                            | 15 |

|----|--------|----------------------------------------------------------|----|

|    | 2.9    | Class-F amplifier                                        | 15 |

|    | 2.10   | Envelope tracking                                        | 17 |

|    |        |                                                          | 21 |

|    |        |                                                          | 22 |

|    |        | 2.11.2 Measuring Power Amplifiers and use of attenuation | 23 |

|    | 2.12   | Calibration                                              | 23 |

|    |        |                                                          |    |

| 3  |        | gn of the power amplifier                                | 25 |

|    | 3.1    | Cree CGH40010                                            | 25 |

|    | 3.2    | Choice of gate bias voltage                              | 25 |

|    | 3.3    | Substrate                                                | 26 |

|    | 3.4    | Stability                                                | 26 |

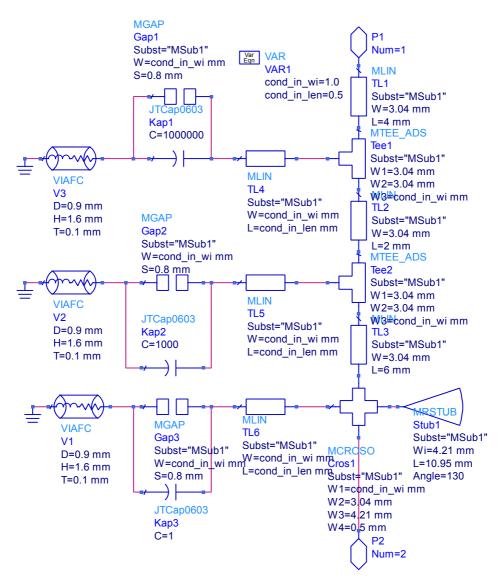

|    | 3.5    | Bias network                                             | 29 |

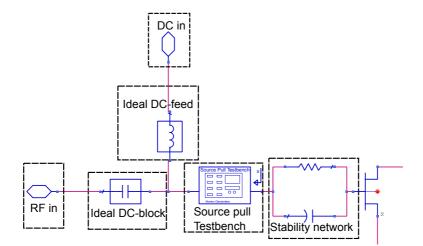

|    | 3.6    | Load Pull and Source Pull benches                        | 31 |

|    | 3.7    | Matching                                                 | 34 |

|    | 3.8    | Matching for larger small signal gain bandwidth          | 37 |

|    |        |                                                          |    |

| 4  | Resu   | llts                                                     | 39 |

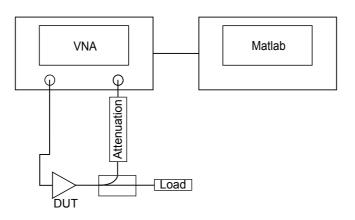

|    | 4.1    | Method for measurements                                  | 39 |

|    |        | 4.1.1 Small signal measurement method                    | 39 |

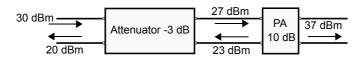

|    |        | 4.1.2 Large signal method                                | 41 |

|    |        | 4.1.3 Tracking method                                    | 42 |

|    | 4.2    |                                                          | 45 |

|    | 4.3    | Small signal measurements                                | 47 |

|    | 4.4    | Large signal measurements                                | 48 |

|    | 4.5    | Tracking results                                         | 52 |

|    |        | 4.5.1 16-QAM tracking results                            | 53 |

| _  | ~.     |                                                          |    |

| 5  |        | ussion                                                   | 55 |

|    | 5.1    |                                                          | 55 |

|    | 5.2    |                                                          | 56 |

|    |        | 5.2.1 Simulations                                        | 56 |

|    |        | 5.2.2 Measurements                                       | 57 |

| 6  | Con    | clusion                                                  | 63 |

| U  | 6.1    |                                                          | 64 |

|    | 0.1    |                                                          | 04 |

| Bi | bliogr | raphy                                                    | 67 |

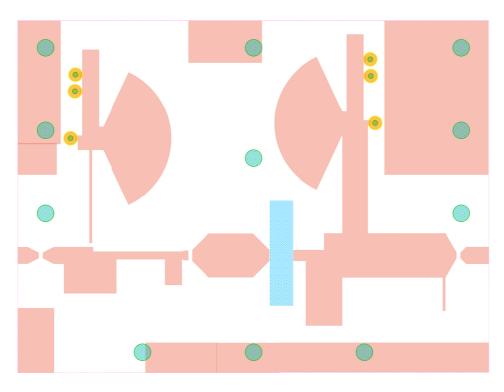

| Ap | pend   | ix A - Layout of the PA                                  | 70 |

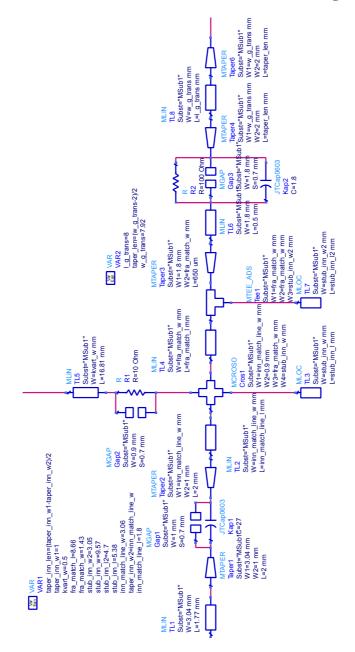

| Ap | pend   | ix B - Schematic of the source matching network          | 71 |

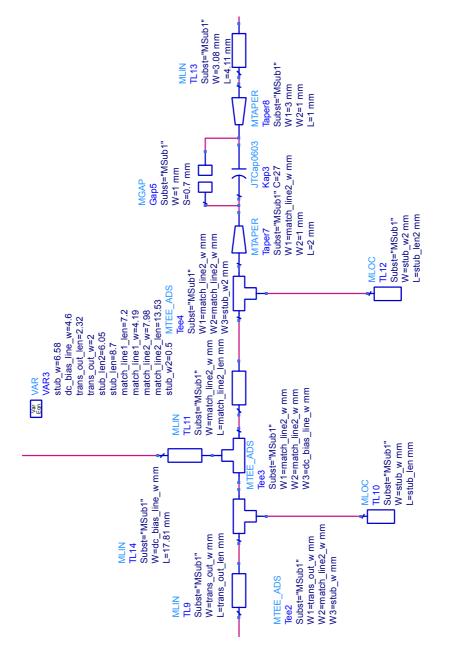

| Aŗ | pend   | ix C - Schematic of the load matching network            | 72 |

| Aŗ | pend   | ix D - Schematic of the bias network                     | 73 |

### List of Tables

| 1.1 | Specification for the PA                                                  | 2  |

|-----|---------------------------------------------------------------------------|----|

| 3.1 | Substrate parameters used in the simulations.                             | 26 |

| 3.2 | Simulated optimal impedances with the use of load and source pull bench.  | 34 |

| 3.3 | Goals used in the simulator to modify the gain of the PA                  | 37 |

| 4.1 | Equipment used for the small signal measurements                          | 39 |

| 4.2 | Equipment used for the large signal test bench.                           | 41 |

| 4.3 | Equipment used for the tracking test bench.                               | 44 |

| 4.4 | Small signal specification for the PA                                     | 47 |

| 4.5 | Summarized table for both simulated and measured large signal results.    |    |

|     | The gain measure is power gain. * denotes simulated results               | 50 |

| 4.6 | PAE measurements for different tracking schemes given the same output     |    |

|     | power. Simulated results are obtained with a static drain bias of 28 V.   | 52 |

| 4.7 | Measured and simulated IMD for the DUT. Results are presented in the      |    |

|     | format of: low frequency IMD, high frequency IMD. All values are mea-     |    |

|     | sured in dBc                                                              | 53 |

| 4.8 | PAE measurements for 16-QAM.                                              | 53 |

|     |                                                                           | 00 |

| 6.1 | Specifications for the PA and measured realized PA. The efficiency num-   |    |

|     | ber is based on PAE and is the average peak PAE within the bandwidth.     |    |

|     | The center frequency is calculated from the highest gain in the specified |    |

|     | bandwidth. * denotes the results given the frequency band 1.8 GHz to 2.6  |    |

|     | GHz                                                                       | 63 |

|     |                                                                           | 00 |

### List of Figures

| 2.1  | An arbitrary N-port network [13].                                                                                                              | 6  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Scattering Parameters for a 2-port network [6].                                                                                                | 6  |

| 2.3  | Stability circles on the output of a conditionally stable device (a) $ S_{11}  < 1$                                                            |    |

|      | when $Z_L = Z_0$ and (b) $ S_{11}  > 1$ when $Z_L = Z_0$ [13]                                                                                  | 8  |

| 2.4  | General transistor amplifier circuit [13]                                                                                                      | 10 |

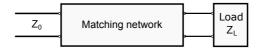

| 2.5  | Network matching an arbitrary load to a transmission line [2]                                                                                  | 10 |

| 2.6  | Output spectrum of a PA showing IMD products [1]                                                                                               | 12 |

| 2.7  | Amplifier response showing 1 dB compression point and 3rd order inter-                                                                         |    |

|      | cept point [1]                                                                                                                                 | 13 |

| 2.8  | Operating points of the different classes [10]                                                                                                 | 15 |

| 2.9  | Ideal class-F waveforms.                                                                                                                       | 16 |

|      | Schematic of a typical ET scheme employed on a RF amplifier [1] [7].                                                                           | 17 |

| 2.11 | Waveform of a two tone signal                                                                                                                  | 18 |

|      | Power dissipation for an amplifier with static drain bias                                                                                      | 18 |

| 2.13 | Power dissipation for an amplifier with dynamic drain bias                                                                                     | 19 |

| 2.14 | Efficiency for a multi level bias amplifier [1].                                                                                               | 19 |

| 2.15 | PAE for a simulated PA with supply voltage steps of 2 V. The red line                                                                          |    |

|      | depicts a envelope tracking scheme and the green line depicts a power                                                                          |    |

|      | tracking scheme.                                                                                                                               | 20 |

| 2.16 | Tracking functions for both ET and power tracking given an ideal transistor.                                                                   | 22 |

| 3.1  | IV curves for the CGH40100 transistor.                                                                                                         | 26 |

| 3.2  | High pass filter stability network.                                                                                                            | 27 |

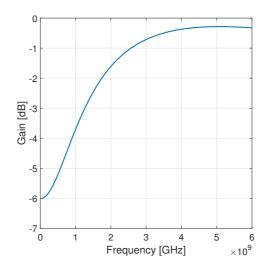

| 3.3  | High pass filter stability network frequency response                                                                                          | 28 |

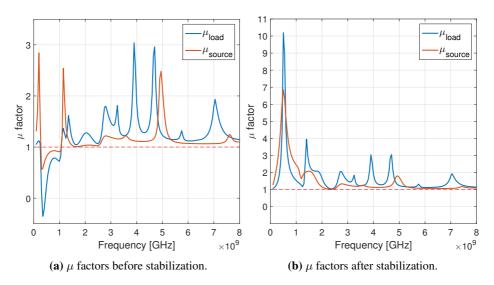

| 3.4  | $\mu$ factors plotted for the amplifier before and after stabilization                                                                         | 29 |

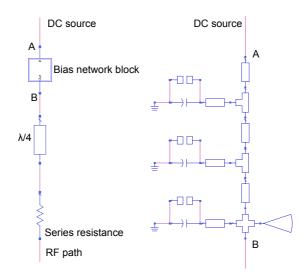

| 3.5  | Bias network. On the left hand side is a block diagram of the entire bias network which is connected between the DC source and RF path. On the |    |

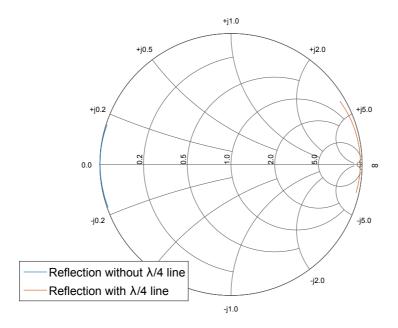

| 3.6  | right hand side is the inner works of the bias network block Reflection of the bias network. Blue colored line is the network without          | 30 |

|      | the $\lambda/4$ line and orange line is the network with the $\lambda/4$ line                                                                  | 31 |

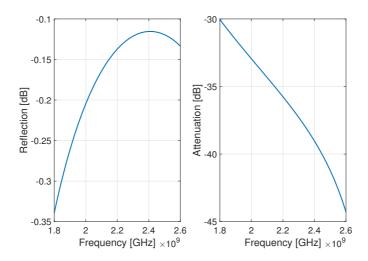

|      |                                                                                                                                                |    |

| 3.7          | Both forward reflection and gain/attenuation plotted in dB for the bias net-<br>work.                                                                      | 32       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.8<br>3.9   | Method for finding the optimal load impedances                                                                                                             | 33<br>33 |

| 3.10         | Optimal impedances plotted in a Smith chart for 1.8 to 2.6 GHz. All impedances move counterclockwise when frequency increases.                             | 35       |

| 3.11         | Small signal gain for the simulated amplifier with the modelled optimal source and load matching.                                                          | 35       |

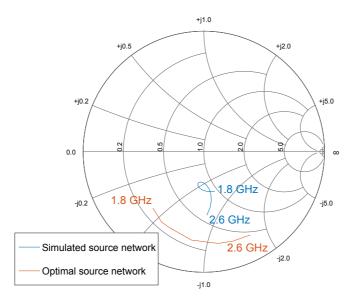

| 3.12         | $\Gamma_S$ plotted for both simulated and optimal network. Blue line moves clockwise.                                                                      | 36       |

|              | $\Gamma_L$ plotted for the load simulated network                                                                                                          | 37       |

|              | network for wider 3 dB gain bandwidth                                                                                                                      | 38       |

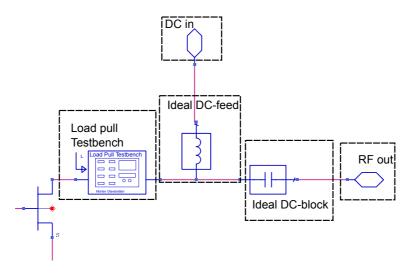

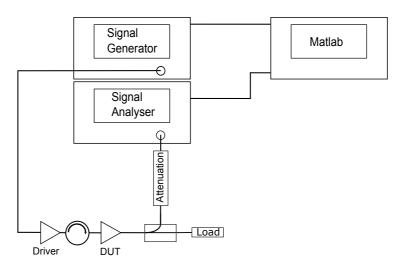

| 4.1<br>4.2   | Small signal test bench setup.       Large signal test bench setup.                                                                                        | 40<br>41 |

| 4.3<br>4.4   | Tracking test bench                                                                                                                                        | 42       |

| 4.5<br>4.6   | tracking                                                                                                                                                   | 45<br>46 |

| 4.7          | given a one tone signal                                                                                                                                    | 46<br>47 |

| 4.8          | The measured $S_{21}$ is coloured blue. The simulated is coloured orange<br>The measured $S_{11}$ is coloured blue. The simulated is coloured orange       | 48       |

| 4.9          | Maximum power out vs. frequency measured for one tone                                                                                                      | 49<br>50 |

| 4.10<br>4.11 | Maximum PAE vs. frequency measured for one tone Both power out and PAE of the amplifier for a small set of frequencies                                     | 50       |

| 4 1 2        | given a one tone signal                                                                                                                                    | 51<br>51 |

|              | IMD versus tone spacing frequency for 28 V and 22 V drain voltage                                                                                          | 52       |

| 5.1<br>5.2   | Possible solution to the $S_{11}$ specification                                                                                                            | 56       |

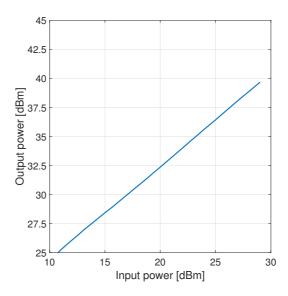

| 5.2          | gain compression.                                                                                                                                          | 59       |

| 5.3          | Ideal RF envelope for a two tone signal. The arrow denotes the problem area which makes envelope tracking require infinite bandwidth for perfect tracking. | 62       |

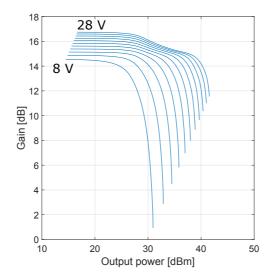

| 6.1          | Simulated power gain swept for supply voltages of 8 to 28 V with a 2 V                                                                                     |          |

| 0.1          | step. The lowest gain corresponds to a supply voltage of 8 V. The red line is the tracking function for constant gain of 14 dB.                            | 65       |

### Abbreviations

| AC     | = | Alternating Current               |

|--------|---|-----------------------------------|

| ACPR   | = | Adjacent Channel Power Ratio      |

| ADS    | = | Advanced Design Systems           |

| CAD    | = | Computer-Aided Design             |

| DC     | = | Direct Current                    |

| DUT    | = | Device Under Test                 |

| ET     | = | Envelope Tracking                 |

| GaAs   | = | Gallium Arsenide                  |

| GaN    | = | Gallium Nitride                   |

| HEMT   | = | High Electron Mobility Transistor |

| IM     | = | Intermodulation                   |

| IMD    | = | Intermodulation distortion        |

| OP-AMP | = | Operational Amplifier             |

| PA     | = | Power Amplifier                   |

| PAE    | = | Power Added Efficiency            |

| PAPR   | = | Peak to Average Power Ratio       |

| PCB    | = | Printed Circuit Board             |

| QAM    | = | Quadrature Amplitude Modulation   |

| RF     | = | Radio Frequency                   |

| RFPA   | = | Radio Frequency Power Amplifier   |

| Si     | = | Silicon                           |

| SOLT   | = | Short, Open, Load, Through        |

| TRL    | = | Through, Reflect, Line            |

| VNA    | = | Vector Network Analyser           |

|        |   |                                   |

## Chapter ]

### Introduction

Wireless communication is very much a big part of living in the 21st century. Smartphones and notebooks are widespread and have undergone a revolution, leaving them with high performance and diverse functionality. More features and higher performance comes with a cost of increased power consumption, requiring higher battery capacity for the same battery life. The increased power consumption comes from the use of more complex modulation schemes with high peak to average power ratio making the amplifier work in several dB's back off, where the efficiency is low. In recent years focus have been shifted to reduce the physical dimensions of the portable devices, which directly affects the battery capacity negatively. Battery life and environmentally friendly efficient operation can be as important as raw performance for a personal product. Hence, efficiency has become one of the central topics in the wireless communication industry.

The power amplifier (PA) is a key component in wireless communication systems such as smartphones and notebooks. It will often be the governing component in the output stage of a transmitter from a performance point of view, and will determine system characteristics such as linearity, gain and efficiency. In many wireless systems the PA will, next to the screen, be the system component which requires the most power in a wireless device. This has become apparent in later years, especially for smartphones, with the introduction of LTE. LTE sacrifices efficiency for increased performance by using a complex modulation scheme. Increasing the efficiency of the PA for the wireless communication system will effectively increase the battery life of the devices, giving increased market value for the early adopters of the efficiency increasing techniques.

Different characteristics of the PA are important in different scenarios. High efficiency is important for more than increasing battery life, for instance in designing a base station. Increased efficiency in the base station PA will directly decrease the power dissipation, reducing the need for cooling. Complex cooling systems require large amounts of space, are expensive to design and produce, and increase the upkeep cost of the base station. On the other hand output power might be equally important for applications which rely on

long range transmission in noisy environments, and efficiency might be a secondary design goal for such a PA. A constant concern for the designers of power amplifiers are the strict linearity specifications. These are a result of the explosive growth in the number of radio systems, making the designated channels for each communication system relatively small in the frequency domain. All wireless systems must comply with the industry standard so that interference between wireless systems does not occur.

In order to accomplish high efficiency the power amplifier must be driven into nonlinear region and be subject to gain compression. This will generate harmonics of higher order, which will increase the nonlinearities. These higher order harmonics are exploited to increase the efficiency of the PA. The exploitation of harmonics has resulted in a class of amplifier known as class-F, which will be explored in this thesis. In such a design the harmonics are used to shape the drain voltage and current to minimize the overlap between their waveforms, thus reducing the power dissipation of the device and increasing efficiency. Highly efficient operation will only occur for the highest output power levels. Envelope tracking (ET) aims to increase efficiency for the PA by reducing the supply voltage as the output power is reduced and thus resulting in the PA operating at or near the highly efficient nonlinear area for a wide dynamic range of output power.

The transistor used for the power amplifier in this thesis is a Gallium nitride (GaN) high electron mobility transistor (HEMT). GaN HEMT has been commercially available for the last decade. This technology offers improved characteristics in several areas compared to the more traditional gallium arsenide (GaAs) and silicon (Si) technologies. Some improved characteristics are higher breakdown voltage and higher output power which will contribute to higher efficiency as well as less complex amplifier designs.

| Center Frequency $(f_0)$ | 2.2 GHz                       |

|--------------------------|-------------------------------|

| Bandwidth (3 dB)         | 800 MHz                       |

| Output Power $(P_{out})$ | > 40 dBm within the bandwidth |

| Gain                     | > 12 dB within the bandwidth  |

| Input match $(S_{11})$   | < -10 dB within the bandwidth |

| Efficiency               | as high as possible           |

Table 1.1: Specification for the PA

#### **1.1** Outline of the thesis

The following gives a brief introduction to the outline of this thesis.

- **Chapter 1, Introduction**. Consists of an introduction to the thesis and the motivation behind the work covered in the thesis.

- **Chapter 2, Theory**. Preliminary theory regarding the main topics covered in this thesis. This includes a brief introduction to basic microwave theory and an introduction to the most popular microwave power amplifier class operations. An introduction to the envelope tracking scheme is also presented.

- **Chapter 3, Design**. The process of designing a highly efficient wideband power amplifier is presented. Included in this chapter is the choice of bias voltage, ensuring stability for the amplifier, designing bias networks, a brief introduction to the load pull technique and designing a wideband matching network.

- Chapter 4, Results. This chapter covers the methods of how the measurements were obtained, preliminary adaptive static bias simulations and measured results for both drain tracking schemes.

- Chapter 5, Discussion. The results are discussed and challenges and possible sources of errors are explored. The discussion is split in three parts, one part is designated to the design while the other two are designated respectively to the simulation of the design and the measured results.

- Chapter 6, Conclusion. A conclusion to this thesis is given. Further topics and development for the work presented in this thesis are sketched.

# Chapter 2

### Theory

The work done in this paper encloses PA design, which can be described as active twoport networks with simple input and output. Therefore some preliminary theory regarding active two-ports and amplifiers in general will be presented in this chapter.

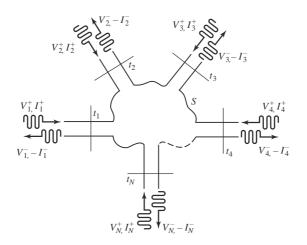

#### 2.1 S-parameters

S-parameters, or scattering parameters, are a mathematical method which allows for simplification of complex circuitry by characterizing it as a box with simple input and output. Measuring current and voltage accurately for higher frequencies is a challenging task. Sparameters are instead a measure of the incident and reflected power, which can be more easily quantified at microwave frequencies. A N-port network is shown in figure 2.1, where  $V_N^+$  is the amplitude of voltage wave incident on port N and  $V_N^-$  is the amplitude of the reflected voltage wave from port N. The scattering matrix, which contain the scattering parameters, are then defined in equation 2.1 and will contain  $N^2$  parameters. Each of the  $N^2$  S-parameters for the N-port network will contain a complex value representing magnitude and phase [13].

$$\begin{pmatrix} V_1^-\\ V_2^-\\ \vdots\\ V_N^- \end{pmatrix} = \begin{pmatrix} S_{1,1} & S_{1,2} & \cdots & S_{1,N} \\ S_{2,1} & S_{2,2} & \cdots & S_{2,N} \\ \vdots & \vdots & \ddots & \vdots\\ S_{N,1} & S_{N,2} & \cdots & S_{N,N} \end{pmatrix} \begin{pmatrix} V_1^+\\ V_2^+\\ \vdots\\ V_N^+ \end{pmatrix}$$

(2.1)

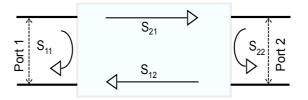

The most common use for S-parameters are the characterization of two-ports. In Figure 2.2 all the S-parameters for a 2-port network are outlined.  $S_{11}$  and  $S_{22}$  represents, respectively, the input and output reflection coefficients. While  $S_{21}$  and  $S_{12}$  represents the forward/reverse transmission coefficients. The measurements are only valid when all other ports are terminated to the characteristic impedance  $Z_0$ .  $S_{21}$  can be viewed as the gain of the two-port, while  $S_{12}$  is the reverse gain or reverse leakage [2] [8].

Figure 2.1: An arbitrary N-port network [13].

Figure 2.2: Scattering Parameters for a 2-port network [6].

#### 2.2 Stability

Instabilities are a major concern in PA designs and can lead to unwanted amplifier behaviour like oscillation. Oscillations can result in serious degradation of performance and equipment and is crucial to avoid. Instabilities in amplifiers occur if the source or load impedances have a negative real part, or equivalently  $|\Gamma_{in}| > 1$  or  $|\Gamma_{out}| > 1$  for any  $\Gamma_S$  or  $\Gamma_L$ . Both  $\Gamma_{in}$  and  $\Gamma_{out}$  are dependent on the matching network, which means that the stability of the amplifier will be dependent on the matching. In addition the matching network impedance will be frequency dependent, which ultimately results in stability to be frequency dependent [2] [13].

$$\Gamma_{in} = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L} = \frac{Z_{in} - Z_0}{Z_{in} + Z_0},$$

(2.2)

$$\Gamma_{out} = S_{22} + \frac{S_{12}S_{21}\Gamma_S}{1 - S_{11}\Gamma_S} = \frac{Z_{out} - Z_0}{Z_{out} + Z_0}.$$

(2.3)

Two cases for stability can be defined:

- Conditionally stable: Conditional stability occurs when the amplifier is stable only for some source and load impedances.

- Unconditionally stable: Unconditional stability occurs when the amplifier is stable for all passive source and load impedances.

Unconditional stability occur when either equation 2.4 and 2.5 are larger than 1 for all frequencies. In addition, a greater value of  $\mu$  can be said to indicate greater stability [2] [13].

$$\mu_{source} = \frac{1 - |S_{11}|^2}{|S_{22} - \Delta S_{11}^*| + |S_{12}S_{21}|} > 1,$$

(2.4)

$$\mu_{load} = \frac{1 - |S_{22}|^2}{|S_{11} - \Delta S_{22}^*| + |S_{12}S_{21}|} > 1,$$

(2.5)

$$\Delta = S_{11}S_{22} - S_{12}S_{21}. \tag{2.6}$$

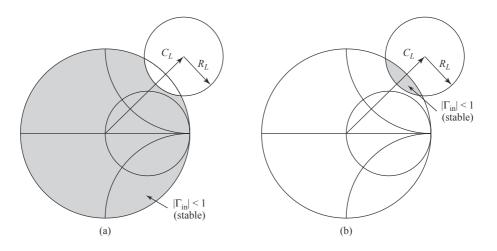

#### 2.2.1 Stability Circles

Stability circles can be employed to plot the boundary between stable/unstable region in the Smith chart. This is useful to visualize the stable region of the amplifier. A brief deduction of the stability circle equations will now be presented. To find the boundary first set  $\Gamma_{in} = 1$ :

$$\Gamma_{in} = \left| S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L} \right| = 1$$

(2.7)

which can be rewritten as

$$|S_{11}(1 - S_{22}\Gamma_L) + S_{12}S_{21}\Gamma_L| = |1 - S_{22}\Gamma_L|$$

(2.8)

By using the fact that  $\Delta$  is defined as the determinant of the scattering matrix, see equation 2.6, the above result can be written as follows:

$$|S_{11} - \Delta \Gamma_L| = |1 - S_{22} \Gamma_L| \tag{2.9}$$

By squaring both sides, simplifying the expression and completing the square one obtains:

$$\left|\Gamma_L - \frac{(S_{22} - \Delta S_{11}^*)^*}{|S_{22}|^2 - |\Delta|^2}\right| = \left|\frac{S_{12}S_{21}}{|S_{22}|^2 - |\Delta|^2}\right|$$

(2.10)

Detailed derivation of the full expression becomes cumbersome and can be found elsewhere [13]. An equation of the form  $|\Gamma - C| = R$  will represent a circle in the complex plane  $\Gamma$ . Equation 2.10 will therefore describe the output stability circle with a center  $C_L$ and a radius  $R_L$  [2][13].

$$C_L = \frac{(S_{22} - \Delta S_{11}^*)^*}{|S_{22}|^2 - |\Delta|^2},$$

(2.11)

$$R_L = \left| \frac{S_{12} S_{21}}{|S_{22}|^2 - |\Delta|^2} \right|.$$

(2.12)

The equations for source stability circles can be obtained by interchanging  $S_{11}$  and  $S_{22}$ .

$$C_S = \frac{(S_{11} - \Delta S_{22}^*)^*}{|S_{11}|^2 - |\Delta|^2},$$

(2.13)

$$R_S = \left| \frac{S_{12} S_{21}}{|S_{11}|^2 - |\Delta|^2} \right|.$$

(2.14)

**Figure 2.3:** Stability circles on the output of a conditionally stable device (a)  $|S_{11}| < 1$  when  $Z_L = Z_0$  and (b)  $|S_{11}| > 1$  when  $Z_L = Z_0$  [13].

Figure 2.3 shows two different cases where the device is conditionally stable. For case **a**, the device is stable in the centre of the Smith chart since  $|S_{11}| < 1$  when  $Z_L = Z_0$ . Therefore the unstable region will be inside the stability circle, while everything exterior to the stability circle will be in the stable range for  $\Gamma_L$ . The stable range is shaded in the figure. For case **b**, the device is unstable when  $Z_L = Z_0$  because  $|S_{11}| > 1$ . This means that the stable region must be the area of the Smith chart that intersects with the stability circle. For an unconditionally stable device the stability circle must either completely enclose the Smith chart or be completely outside of the Smith chart and the amplifier must be stable ( $|S_{11}| < 1$ ) in  $Z_0$  [2][13].

#### 2.3 Gain

Gain is the amplifiers ability to increase the power or amplitude of a signal. There are three different definitions for the gain of a power amplifier, *power gain, available power*

gain and transducer power gain.

Power gain is defined as the ratio of power delivered to the load to the power applied to the input of the amplifier. Which mathematically can be expressed as:

$$G = \frac{P_L}{P_{in}} = \frac{|S_{21}|^2 (1 - |\Gamma_L|^2)}{(1 - |\Gamma_{in}|^2)|1 - S_{22}\Gamma_L|^2}.$$

(2.15)

As can be seen by equation 2.15 the power gain is not dependent on  $\Gamma_S$ , but is dependent on  $\Gamma_L$ . This means that the power gain is independent from the input-impedance of the amplifier. This only holds true for idealized cases as both input and output matching impedance are dependent on each other.

Available power gain is defined as the ratio of the power available from the two-port network to the power available from the source. This gain measure does not depend on  $\Gamma_L$ , as can be seen by:

$$G_A = \frac{P_{avn}}{P_{avs}} = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2)}{|1 - S_{11}\Gamma_S|^2 (1 - |\Gamma_{out}|^2)}.$$

(2.16)

Available power gain assumes that both source and load are conjugately matched, which means that  $\Gamma_{in} = \Gamma_S^*$  and  $\Gamma_{out} = \Gamma_L^*$ .

The last measure is transducer power gain, which can be viewed as a combination of power gain and available gain. It is defined as the ratio of the power delivered to the load to the power available from the source. This measure is dependent on both  $\Gamma_L$  and  $\Gamma_S$ . Transducer power gain can be expressed as

$$G_T = \frac{P_L}{P_{avs}} = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2) (1 - |\Gamma_L|^2)}{|1 - \Gamma_{in} \Gamma_S|^2 |1 - S_{22} \Gamma_L|^2}.$$

(2.17)

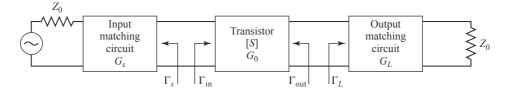

A single stage amplifier can be modelled as figure 2.4. The amplifier is based around a transistor. There are matching networks on both sides of the transistor which work to transform the input and output impedance to  $Z_0$ . Separate gain factors for each of these three elements can be defined. The gain of the matching networks are  $G_S$  and  $G_L$  for source and load respectively and are defined as

$$G_S = \frac{1 - |\Gamma_S|^2}{|1 - \Gamma_{in} \Gamma_S|^2},$$

(2.18)

and

$$G_L = \frac{1 - |\Gamma_L|^2}{|1 - S_{22}|\Gamma_L|^2}.$$

(2.19)

The transistor gain by itself can be expressed as:

$$G_0 = |S_{21}|^2. (2.20)$$

The overall transducer gain of the amplifier may then be written  $G_T = G_S G_0 G_L$ .

Figure 2.4: General transistor amplifier circuit [13].

#### 2.4 Matching

The problem of properly matching an amplifier can be complex, especially if wideband matching is required. Both discrete components and transmission lines are common in matching networks, but for higher frequencies, transmission lines are more widely used. The matching network is ideally lossless, and is usually designed so that the impedance seen into the matching network is  $Z_0$  to minimize reflection. In figure 2.5 an arbitrary load  $Z_L$  has been matched to a transmission line with an impedance of  $Z_0$ . The reflections to the left of the matching network are then eliminated, however there will be multiple reflections between the matching network and the load  $Z_L$  [2].

Figure 2.5: Network matching an arbitrary load to a transmission line [2].

From section 2.3 and equations 2.18, 2.19 and 2.20 it can be seen that when both source and load are matched to the characteristic impedance  $Z_0$ , the total gain of the amplifier is that of the transistor  $G_0$ . The source and load matching must be designed to the specific application of the amplifier. In the case of power amplifiers maximum gain and output power is desirable.

For maximum gain the matching done on the source of the amplifier will be the governing factor. From equation 2.18 it can be seen that maximum gain will be achieved when the input impedance  $\Gamma_{in}$  is conjugately matched with  $\Gamma_S$ .

$$\Gamma_{in} = \Gamma_S^* \tag{2.21}$$

For maximum power transfer to the load, matching on the load side of the amplifier will be the most important factor. To match to maximum power,  $\Gamma_L$  should be designed so that  $P_{out}$  is as high as possible. Maximum power match can be found by employing load-pulling, which is explained in greater detail in chapter 3.6.

$$\Gamma_{out} \Rightarrow max(P_{out}) \tag{2.22}$$

#### 2.5 Efficiency

A very important aspect of designing a power amplifier, or any electronics device today, is how efficienct it is at doing its job. A highly efficient amplifier will require less cooling and increase the time the device can run on battery power given the same output power. There are multiple ways to define efficiency for a power amplifier, but the most common are *drain efficiency* and *power added efficiency*. Drain efficiency is the RF output power divided by the DC input power, and is defined as:

$$\eta = 100 \cdot \frac{P_{OUT}}{P_{dc}}.$$

(2.23)

Drain efficiency does not take RF input power into account, so for a better model with respect to thermal dissipation and actual power applied to the amplifier, the RF input power needs to be included in the efficiency equation. Therefore power added efficiency (PAE), defined mathematically as:

$$PAE = 100 \cdot \frac{P_{OUT} - P_{IN}}{P_{dc}} = \eta \cdot \left(1 - \frac{1}{G}\right), \qquad (2.24)$$

will be used in this paper when efficiency is referred to. In the equation for power added efficiency G denotes the gain of the device. For high gain devices the PAE and drain efficiency will virtually be the same.

#### 2.6 Linearity

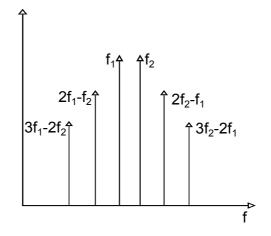

A linear amplifier is an amplifier whose output is proportional to the input. Nonlinearities can present itself in different ways. One way is the intermodulation distortion (IMD) products. These components are the result of applying a signal with more than one frequency component in its spectrum. To better visualize this, the output spectrum of an amplifier whose input signal consists of two different frequencies is depicted in figure 2.6. The frequency components  $f_1$  and  $f_2$  are the signals which are applied to the input of the amplifier. The other frequency components in the spectrum are a result of IMD. The IMD products, which have been limited to only include 5th order in figure 2.6, can be a serious limitation to linearity. If  $f_1$  and  $f_2$  are close in frequency, e.g. a spacing of 5 MHz at a center frequency of 2.4 GHz, the 3rd. order IMD products can become troublesome and hard to remove from the output spectrum.

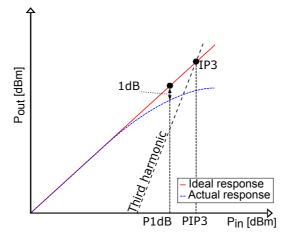

Linearity will also be impaired by the compression of the output signal which occur due to the saturation of the transistor. In figure 2.7 an idealized amplifier response and a more realistic non-ideal response of an amplifier has been plotted. In this figure the non-ideal response is called actual response. For the lower levels of input power the actual response of the amplifier will be linear and closely be that of an ideal response, which will result in low harmonic and IM distortion. However, at lower input levels the amplifier will operate inefficiently as well as having lower output power. In order to get higher efficiency the amplifier will need to be driven harder which will force the amplifier response into

Figure 2.6: Output spectrum of a PA showing IMD products [1].

compression. Harmonics with the frequency  $n \cdot f_0$ , where n is an integer, as well as IMD products will be added to the output spectrum of the amplifier. The harmonics can be exploited for better efficiency with the design of a good output matching network. This method will be described in section 2.9. It is important to note that there is a trade off between efficiency and linearity. For good linearity performance the amplifier will be significantly inefficient without the use of advanced linearization techniques like gate tracking or predistortion [1][14].

Two common measurements for nonlinearity are the 1 dB compression point and 3rd order intercept point. The 1 dB compression point is where the input power of the amplifier is such that the output power deviates 1 dB from the ideal amplifier response and represents the amplifier driven to medium distortion. The 3rd order intercept point is a fictitious point where the linear idealized gain of the device intercepts the linear third harmonic line. In figure 2.7 both the 1 dB compression point and the 3rd order intercept point are depicted.

#### 2.7 Memory effects

For an ideal nonlinear PA the gain will only be a function of the input signal. The gain response for an ideal nonlinear PA is plotted as the blue dotted line in figure 2.7. The gain of a real PA will also be given as a function of what is known as *memory effects*. Memory effects will add to the nonlinearities of a PA and will be the cause of deviation between static and dynamic characteristics. Any form of element that is capable of storing energy will introduce memory to the system. For instance, a heatsink can release heat into the device after high power operation. Another very common memory inducing element are inductors and capacitors. This can be directly seen from voltage equation for a capacitor

$$v_C(t) = \frac{1}{C} \cdot \int_{-\infty}^t i(t') \,\mathrm{d}t'.$$

(2.25)

Figure 2.7: Amplifier response showing 1 dB compression point and 3rd order intercept point [1].

The voltage at time t is proportional to all prior current values, and not just the instantaneous value [1][14]. There are other main causes for memory effects which can be characterized as:

- Modulation of supply rail

- Semiconductor trapping effects

- Dynamic thermal effects

The most common reason for memory effects and asymmetrical IM sidebands is modulation of supply rail. This can cause major linearity issues as the gain of the PA and the amount of compression will change. Modulation of the supply rail can be avoided by carefully designing the biasing network for the PA, as the reason for this modulation is that a portion of the RF signal propagates to the power supply [1][14].

The trapping effect is usually most apparent in a device if it is placed in cut-off region and then rapidly switched on into the linear region. The current can then be observed and is expected to reach steady state in a relatively fast response. Usually in a matter of picoseconds. The device may not actually reach steady state before microseconds, milliseconds or even seconds have passed. This is caused by electrons being "trapped" in the semiconductor channel. The electrons will be released in a seemingly random fashion, which will result in nonlinearities [1][14].

Fluctuations in device temperature is widely accepted to cause nonlinear effects. The gain of the DUT will be temperature dependent and adequate cooling is therefore critical. The semiconductor device will heat up and cool off for slower envelopes causing distortion to the signal based on previous states[1][14].

#### 2.8 Amplifier Classes

#### 2.8.1 Class-A

A class-A amplifier is an amplifier which the operating point is chosen so that the collector/drain current flows at all times, thus a conduction angle of  $360^{\circ}$ . It therefore operates in the linear portion of the amplifier characteristics and the signal will suffer minimal distortion. As mentioned in section 2.6 the trade off for linearity is efficient operation. This is where class-A amplifiers are inferior to the other classes. The maximum drain efficiency of a class-A amplifier with a supply voltage of  $V_{DD}$  can be calculated [7]:

First, define  $V_{max}$  as the peak voltage across the load  $R_L$  and require the output current to be positive:

$$I_{DC} = \frac{V_{max}}{R_L} \le \frac{V_{DD}}{R_L} \tag{2.26}$$

$V_{max}$  has to be less than the supply voltage  $V_{DD}$  for anything other than idealized cases because of the non-zero saturation voltage of the transistor. The power delivered from the supply may then be written:

$$P_{supply} = V_{DD}I_{DC} = \frac{V_{DD}^2}{R_L}$$

(2.27)

Now assume that the signal applied to the load is a sine wave. The RMS output power supplied to the load is then:

$$P_{load} = \frac{V_{max}^2}{2R_L} \le \frac{V_{DD}^2}{2R_L}$$

(2.28)

The overall efficiency can then be written as:

$$\eta = \frac{P_{load}}{P_{supply}} = \frac{V_{max}^2}{2V_{DD}^2} \le \frac{1}{2}$$

(2.29)

This means that the theoretical maximum *drain efficiency* of a class-A amplifier is 50% when the saturation voltage across the transistor is zero. The non-zero saturation voltage of the transistor, which can be several volts, will reduce the drain efficiency to less than 50%. The maximum efficiency which includes the non-zero saturation voltage can then be expressed as [7]

$$\eta_{max} = \frac{V_{DD} - V_{sat}}{2V_{DD}}.$$

(2.30)

#### 2.8.2 Class-B

The class-B amplifier is one in which the operating point is chosen so that the amplification takes place for only half the cycle. The conduction angle is then 180°. The drain efficiency of the class-B amplifier can be deduced similarly to that of the class-A amplifier. It is not included in this paper, but can be found in other literature [7]. The maximum drain efficiency is given by equation 2.31.

$$\eta = \frac{\pi}{4} \approx 78.5\% \tag{2.31}$$

Figure 2.8: Operating points of the different classes [10].

Class-B operation is significantly more efficient than class-A, while still offering useful linearity[7].

#### 2.8.3 Class-AB

The class-AB amplifier is a compromise between the class-A and class-B amplifier in both efficiency and linearity, and has been a popular class for RFPA designers for several generations. It has a conduction angle between  $180^{\circ} - 360^{\circ}$  depending on the operation point chosen by the designer. The operation point governs the maximum drain efficiency which will be between 50% - 78.5% [7] [9].

#### 2.8.4 Class-C

The class-C amplifier is characterised by the operating point being chosen such that the output current is zero for more than half of the input signal cycle given an input of a sine wave. This means that the conduction angle is less than  $180^{\circ}$ . This is accomplished by biasing below the cut off region. This class of amplifiers will result in significant distortion and thus will be unsuitable for applications where linearity is an issue. Theoretical maximum drain efficiency of 100% is possible, but in real life applications the efficiency is reduced to approximately 75%.

#### 2.9 Class-F amplifier

The class-F amplifier is a reduced conduction angle amplifier with load harmonic modulation, which means that the harmonics are used to shape the intrinsic voltage and current waveforms of the transistor so that minimal overlap between the waveforms occur. This overlap between current and voltage waveforms will materialize itself as added heat and power dissipation to the transistor, which will inhibit efficient operation. The power that is dissipated can be described mathematically as

$$P = V \cdot I. \tag{2.32}$$

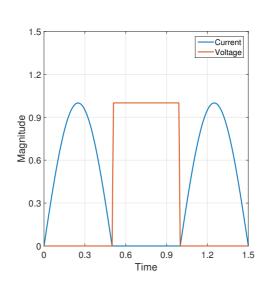

Figure 2.9: Ideal class-F waveforms.

An ideal class-F amplifier will have an efficiency of 100% which can be explained with figure 2.9. There will be no overlap between the current and voltage and thus no power dissipation in the transistor. In order to reach 100% efficiency  $n = \infty$  harmonics need to be perfectly tuned. The harmonics used in the tuning process needs to be generated from the transistor, which means that the transistor must be driven into compression so that it can distort the signal. To be able to achieve this kind of compression and distortion the transistor needs to be biased near the cut-off region and a suitably large input signal must be applied. Therefore the transistor is usually biased in deep class-AB or class-B region. As can be seen by figure 2.9 the drain voltage waveform will be ideally square shaped, while the drain-current will be half sine wave for a class-F design. This shaping of the intrinsic waveforms is achieved by reflecting all odd order harmonic components back to the drain node on the transistor. The even order harmonics must be shorted to ground. This will remove higher order harmonics from the output spectrum and a current shape of a half sine wave will be achieved. The reflection of the higher order odd harmonics will result in a square shaped drain-voltage. Because of the non ideal transistors and limited gain as frequency increases, this is impossible to achieve. However it is common to include harmonics in the order of 3 or 4 in the matching network design process. This will increase the efficient operation of the amplifier for larger input signals [1][7].

There is also a class called the inverse class-F or class- $F^{-1}$  which is based on the exact same principle as class-F. The only difference in operation is that the voltage is now shaped to a half wave sine and the current will be square shaped. The design of the amplifier will be similar to the class-F, but the output matching network must be designed to short odd

order harmonics and reflect even order harmonics. It is important to note that the phase of the current and voltage is extremely important to be able to minimize the overlap in both class-F and class- $F^{-1}$ . Too much of a phase-shift can seriously degrade the efficient operation because overlap between voltage and current will occur and power will be dissipated in the device.

#### 2.10 Envelope tracking

Envelope tracking (ET) is an efficiency enhancing technique which continually adjust the supply voltage of the amplifier in order to ensure that it is working at peak efficiency. ET has become more widespread in modern times as more complex modulation schemes with a higher peak to average power ratio (PAPR) are being used. Fixed bias RF amplifiers will operate at peak efficiency only when driven into compression, which complex modulation schemes with a high PAPR will not achieve for most of the signal. ET seek to make the RF amplifier work at peak efficiency for a wide range of signal power levels. This will however introduce more distortion as well as increased system complexity.

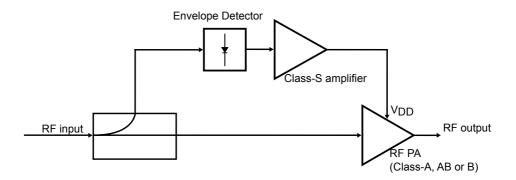

Figure 2.10: Schematic of a typical ET scheme employed on a RF amplifier [1] [7].

The main idea behind envelope tracking can be clarified with reference to figure 2.10. The RF input signal enters a coupler which splits the signal into two paths. One enters the RF PA and the other enters an envelope detector. The envelope detector can be made with a diode and a low pass filter. The diode ensures that only the positive part of the signal gets sent to the filter. The low pass filter extracts the low frequency components of the signal, which in this case is the signal envelope. The envelope is then amplified up to a suitable level so that it can modulate  $V_{DD}$  on the main RF PA. The envelope amplifier can for instance be an audio amplifier (class-S) or an amplifier with bandwidth in the MHz region. However, the critical design point is that the envelope amplifier needs to be highly efficient. This can be seen from equation 2.33 where an approximation for the total system efficiency is the envelope amplifier efficiency times RFPA efficiency.

$\eta_{tot} \approx \eta_{EnvAmp} \cdot \eta_{RF}$

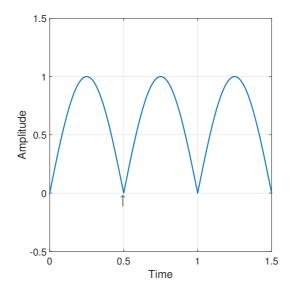

Figure 2.11: Waveform of a two tone signal.

Figure 2.12: Power dissipation for an amplifier with static drain bias.

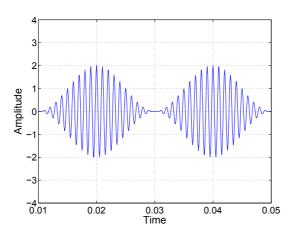

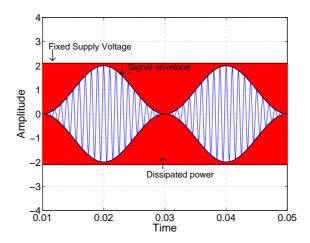

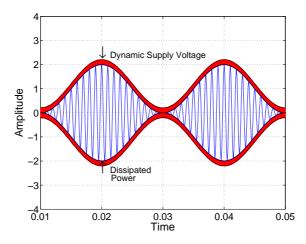

Now for an idealized example. Lets assume the output signal consists of the two tone signal plotted in figure 2.11. With a static drain bias voltage the dissipated power is plotted as the red area in figure 2.12. If the bias voltage now is allowed to track the envelope of the signal, the average dissipated power will be heavily reduced. This is shown in figure 2.13. One of the strengths of this technique is that the modulation of the drain voltage does not have to be very accurate. The voltage offset of the tracking function in comparison to the signal envelop decides the amount of distortion and how far into compression the envelope tracked amplifier operates. For instance, the tracking function can be made to follow the

Figure 2.13: Power dissipation for an amplifier with dynamic drain bias.

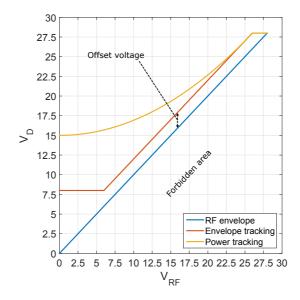

signal envelope closely by choosing a small offset. By increasing this offset compared to the signal envelope the envelope tracked amplifier will operate with less distortion. The offset voltage is shown in figure 2.16

Figure 2.14: Efficiency for a multi level bias amplifier [1].

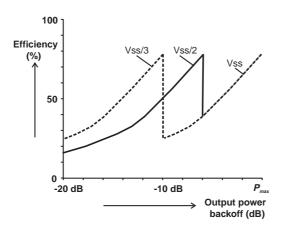

Figure 2.14 shows the efficiency of an ideal class-B amplifier with a simplified ET scheme versus the output power for three different drain bias voltages. The different bias voltages will all result in the same peak efficiency, but this will occur for different output power levels. By intelligently switching the bias voltage between the three levels one can achieve much higher efficiency for the low and medium powered output. For the few upper dB of

output power there will not be any bias switching and thus no increase in efficiency. A fully implemented envelope tracking scheme is based on dynamically adjusting the drain voltage for all output levels so that high efficiency can be obtained for a large output power range.

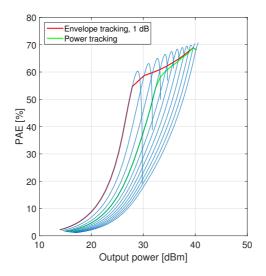

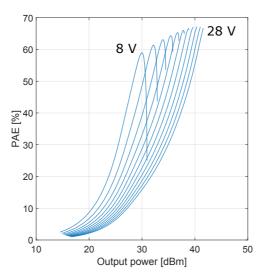

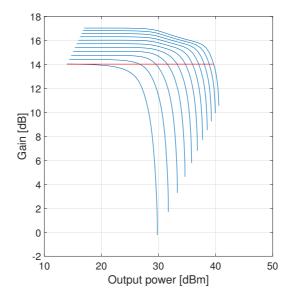

The effects of this can be seen in figure 2.15 where the drain bias voltage has been swept in equal steps for a simulated PA. The red line depicts the envelope tracking scheme tracking at 1 dB compression. This means that the amplifier will constantly be in 1 dB compression as long as envelope tracking occur. Tracking will stop at a chosen supply voltage when the output power level decreases past a set point and the amplifier will then follow the fixed bias PAE curve. This behaviour is shown as the red line following the PAE curve for the lowest supply voltage. The power tracking scheme will follow the curve for  $V_{DD}/2$ up to certain power level before tracking takes place. As the output power increases the difference between the two schemes will decrease. In this figure the effects of supply tracking are evident as efficiency is increased for lower power levels. The curves for the tracking schemes are approximated from simulations and are not identical with the tracking function of a real PA. An interesting possibility of tracking different drain function arises from this figure. Tracking at different PA characteristics is possible. E.g. tracking at peak efficiency is possible and the tracking function for this will follow the PAE peak for each supply voltage. Tracking at 2 dB compression is a possibility and will result in a higher PAE compared to 1 dB. It all depends on the purpose of the amplifier. For an ideal transistor the peak of the PAE curves of each supply voltage would be identical. The reason for the increase in peak PAE as the supply voltage increases is the knee voltage of the transistor not being equal to zero. The knee voltage will be a decreasing fraction of the supply voltage as it increases and thus the peak PAE will increase.

**Figure 2.15:** PAE for a simulated PA with supply voltage steps of 2 V. The red line depicts a envelope tracking scheme and the green line depicts a power tracking scheme.

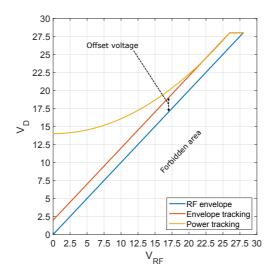

Figure 2.16 shows the tracking functions for an ideal transistor. The transistor is ideal in the sense that the saturation voltage is zero. This figure shows what the necessary drain voltage,  $V_D$ , needs to be as a function of the RF envelope voltage  $V_{RF}$  for a given tracking scheme. The envelope is defined as:

$$E = I + jQ, \tag{2.34}$$

for a signal operating with I/Q data and will consist of both negative and positive voltages. ET will track the absolute value of the envelope voltage and thus the tracking function is described as:

$$|E| = \sqrt{I^2 + Q^2}.$$

(2.35)

Because of the square root operation, ET will in theory require infinite bandwidth of the tracking amplifier to track perfectly. This is demanding on the tracking amplifier and therefore an alternative method of tracking was also explored and compared to ET, namely power tracking. Tracking the RF power of the amplifier can be done by using the tracking function:

$$P = |E|^2 = I^2 + Q^2. (2.36)$$

This method does not require any square root operation and will only demand the bandwidth of the RF envelope to track perfectly, thus making the tracking amplifier design simpler. The drawback of this method comes in the form of less efficiency compared to ET. This can be seen from figure 2.16 where the tracking functions are plotted and the power tracking voltage is higher than the ET scheme for low output power levels. For the higher power levels the power tracking scheme will follow the ET scheme almost identically. ET will follow the ideal envelope of the transistor with a given voltage offset. This offset will govern the amount of compression and efficiency for the envelope tracking scheme. The smaller this offset is, the closer the ET will follow the RF envelope and higher efficiency will be achieved at the cost of linearity and gain. The tracking functions are not allowed to track under the RF envelope as this will result in the amplifier gain collapsing. This area is called the forbidden area in the figure. For the idealized case the envelope tracking scheme will track down to the offset voltage chosen and up to  $V_{Dmax}$ . The power tracking will ideally track down to  $V_D/2$  and up to  $V_{Dmax}$ .

For the performance of the ET scheme it is extremely important that the modulated drain bias from the envelope amplifier gets properly synchronised with the RF signal. A minor unsynchronisation will contribute to signal distortion, less efficient operation and asymmetrical IM sidebands. This may be a major concern for modern radio systems as the requirements for IMD can be very strict.

#### 2.11 Measurements

In the following section errors connected to measurements and methods to minimize the errors are described.

Figure 2.16: Tracking functions for both ET and power tracking given an ideal transistor.

#### 2.11.1 Small signal measurements

A vector network analyser (VNA) was used to carry out the small signal measurements. The VNA measures the S-parameters for the device connected and consists of a transmitter, two RF-cables to connect the device under test (DUT), a receiver, an information panel and a control panel.

When conducting measurements there will always be some measuring errors. Some of the factors that contribute to measurement errors are repeatable over time, for instance loss in cables. The repeatable and predictable errors can be calibrated for and therefore mathematically eliminated. Some errors are random and cannot eliminated through calibration, for instance instrument noise. There are three types of error sources connected to measuring which concerns all types of equipment:

- Systematic errors

- Random errors

- Drift errors

*Systematic errors* are errors that are predictable and repeatable over time. These are caused by imperfections in the test setup and equipment. Common errors include signal leakage, reflection and the frequency response of cables and connectors. Systematic errors can be effectively removed by calibrating the equipment.

*Random errors* are errors that are unpredictable and non-repeatable over time. Causes for these errors can be hard to identify, but common causes are instrument noise and other noise sources. These errors cannot be calibrated for, but the impact can be reduced with

the use of averaging the measurements.

*Drift errors* are errors that occur when the external and/or internal parameters, like temperature, change after the equipment is calibrated. These errors can be minimized by having the test equipment in an environment with controlled temperature and frequent calibrations.

#### 2.11.2 Measuring Power Amplifiers and use of attenuation

When measuring a high power DUT such as power amplifiers, attenuation of the output is important in order to not damage the VNA. However, attenuators will introduce a source of inaccuracy. While the attenuation will be mathematically removed from the measurements with proper calibration, the measured data will suffer in accuracy. Each time the signal passes through the attenuator it will be brought closer to the noise floor of the VNA. This is not especially troublesome for the forward gain,  $S_{21}$ , as the attenuation only occurs once, but will become a bigger issue for the reflected wave on the output which will be attenuated multiple times.

# 2.12 Calibration

There are two common calibration kits that are employed for VNA calibration. SOLT (short, open, load and through) and TRL (trough, reflect and line). SOLT is the most common for coaxial interface, while TRL is more common in in-fixture and on-wafer environments [12].

**SOLT** consists of well defined short, open and load of a characteristic impedance. The calibration is easy to perform and offer calibration from DC up to the upper frequency limit of the equipment. To utilize SOLT calibration the short, open and load standards are connected one by one to each port on the VNA so that the VNA can measure them. When this is done the two reference planes are then connected together with the trough component. This enables the VNA to mathematically remove systematic errors for each path. SOLT calibration does offer good repeatability given sound calibration practices from the user, as well as ease of use and good accuracy of the calibration. SOLT may also be made to user specification and therefore be able to accommodate many different user requirements [12].

**TRL** is well suited to measure devices that are not connectorized or devices that does not share the same connector type as the measuring equipment. TRL does not require well defined calibration standards as SOLT does. However, TRL requires a short through component, preferable of zero length and at the same impedance as the line standard. It does also require a highly reflective standard as well as a line at the characteristic impedance of the system. The TRL calibration is often manufactured and characterised on the same material as the DUT. In comparison to SOLT, TRL is less straightforward to use, but offer a higher degree of accuracy and repeatability of the calibration [12].

# Chapter 3

# Design of the power amplifier

# 3.1 Cree CGH40010

The PA in this paper is based on the CGH40010 transistor from Cree. This is an unmatched, 10 W, gallium-nitride (GaN), high electron mobility transistor (HEMT). The transistor operates from a 28 V rail and is a general purpose transistor. Some of the features of the Cree CGH40010 includes[3]:

- Up to 6 GHz operation

- 16 dB Small Signal Gain at 2.0 GHz

- 14 dB Small Signal Gain at 4.0 GHz

- 13 W typical P<sub>SAT</sub>

- 65 % Efficiency at  $P_{SAT}$

- 28 V operation

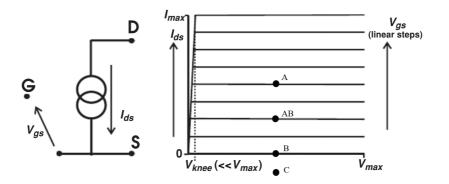

# 3.2 Choice of gate bias voltage

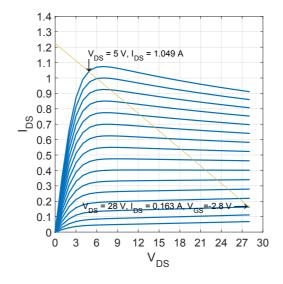

From section 2.8 and 2.9 it is clear that the transistor needs to biased in class AB or B in order to achieve harmonically tuned operation. Class AB operation was chosen to get a compromise between linearity and efficiency. According to the datasheet of the Cree CGH40100 transistor [3] a gate bias voltage of -3 V and higher will make the simulator model of the transistor conduct. Therefore a voltage sweep from -3 to -1.5 V with a 100 mV step was performed to plot the IV characteristics of the transistor. With a simple testbench in ADS, which measures the drain current versus drain voltage for each gate voltage specified, a gate voltage of  $V_{GS} = -2.8V$  was found to be a good point to bias the transistor with regard to class AB operation. This bias point will result in a drain current of

$I_{DS} = 163 \text{ mA}$ , a voltage swing from 5 V to 28 V and  $I_{DS_{max}} = 1049 \text{ mA}$ . The biasing point with its related simulated results are depicted in figure 3.1.

Figure 3.1: IV curves for the CGH40100 transistor.

#### 3.3 Substrate

For this amplifier the substrate was chosen to be flame retardant 4, also known as FR4. This substrate is very popular, inexpensive, versatile and retains its electrical properties in both dry and humid conditions. In table 3.1 the substrate parameters used in the simulations are listed.

| Н                   | Er  | Mur | Cond             | Т                  | $tan(\delta)$ |

|---------------------|-----|-----|------------------|--------------------|---------------|

| $1.6\cdot 10^{-3}m$ | 4.4 | 1.0 | $5.96\cdot 10^7$ | $36\cdot 10^{-6}m$ | 0.02          |

Table 3.1: Substrate parameters used in the simulations.

## 3.4 Stability

Now that a gate biasing point,  $V_{GS}$ , had been chosen, stability became an issue. In section 2.2 two methods of testing unconditional stability were introduced.  $\mu$  factors, given in equations 2.4 and 2.5, with the addition of stability circles were used to ensure stable operation for all frequencies. A design goal was set to always require the  $\mu$  factors to be greater than one. Two methods were utilized to provide stability in the design process.

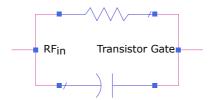

Figure 3.2: High pass filter stability network.

The first method is depicted in figure 3.2 and consists of a capacitor and a resistor in parallel, in series with the gate. The resistor will add attenuation for all frequencies. This helps the transistor in becoming stable, but will also introduce attenuation in the operational bandwidth of the amplifier, reducing the gain. A capacitor was added in parallel to the resistor, reducing the attenuation as frequency increases. Capacitors are components whose impedance will be dependent on both capacitance and frequency. The impedance of a capacitor can be calculated as

$$Z_C = \frac{1}{j\omega C} = \frac{1}{j2\pi fC},\tag{3.1}$$

where C is the capacitance of the capacitor and f is the frequency of the signal. The equivalent series impedance of the parallel stability network presented in figure 3.2 is given as

$$Z_{eq} = \frac{Z_C Z_R}{Z_C + Z_R} = \frac{\frac{1}{j\omega C}R}{\frac{1}{j\omega C} + R} = \frac{R}{1 + j\omega CR},$$

(3.2)

where  $Z_R$  is the impedance of the resistor given by

$$Z_R = R. (3.3)$$

From equation 3.2 it is seen that the impedance will be reduced for the high pass stabilizing network when the capacitance or the frequency increases. This is desirable as high gain in the operational frequency band is wanted for a PA. With regard to stability the reduced attenuation will not become an issue for higher frequencies as the transistor gain will decrease and therefore become inherently stable.