# FPGA Filter Design and Measurements with Emphasis on a Filter with Steep Transition Bands

#### **Andre Firing**

Master of Science in Electronics Submission date: May 2013

Supervisor: Bjørn B. Larsen, IET

Co-supervisor: Stig Rooth, Kongsberg Norspace AS

Tor Audun Ramstad, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

#### Design of Digital Systems Master's Thesis

# FPGA Filter Design and Measurements with Emphasis on a Filter with Steep Transition Bands

#### **Andre Firing**

Supervisors Bjørn B. Larsen, IET Tor A. Ramstad, IET Stig Rooth, Kongsberg Norspace

#### Norwegian University of Science and Technology

Faculty of Information Technology, Mathematics and Electrical Engineering Department of Electronics and Telecommunications

### **Abstract**

The objective of this thesis was to design and implement a digital bandpass filter with emphasis on steep transition bands. The goal of the design was to create a FPGA based digital alternative to an existing analog filter used in the Galileo Satellite Search and Rescue Transponder. This filter has a passband of 100 kHz centered at 70.98 MHz. The transition bands of the filter are approximately 50 kHz on both sides of the passband, ending in a stopband attenuation of at least 80 dB. The phase of the filter response is linear.

The proposed filter, called *Masterfilter*, was designed by applying multistage and multirate filtering techniques, including undersampling, signal mixing, decimation and interpolation. The filter was designed with a sampling frequency of 30 MHz, and the input signal was undersampled down to 10.98 MHz. The output of the Masterfilter was centered at 3.48 MHz, with a bandwidth of 100 kHz. Matlab was used to simulate the behavior and determine intermediate filter characteristics, while VHDL was used to implement the filter in hardware. To make the design fit the performance and spacial limitations of a space qualified FPGA, digital design optimization techniques such as pipelining and resource sharing were implemented. The filter was designed to be as general as possible, meaning that no vendor specific components were used in the design.

The digital filter was tested using several approaches, including impulse responses and tone testing of both internal filters and the complete filter system. The transfer function of the Masterfilter was verified using Modelsim simulations. In addition to these simulations, a version of the filter was implemented in an Altera Cyclone II FPGA, where the functionality of the filter, and the actual frequency response was determined. These results provided a transfer function for the complete filter system.

It was concluded that the filter did fulfill the requirements given, and that it would be a sufficient digital alternative to the existing analog filter in the Search and Rescue Transponder. An infinite attenuation, where the output transmitted a constant zero was measured at 39 kHz below the passband, at at 30 kHz above the passband. Some issues with timing were encountered when using certain optimization techniques. Therefore, it would be recommended that a device specific clocking logic should be used in an FPGA implementation.

## Sammendrag (Norwegian)

Bakgrunnen for denne masteroppgaven var design og implementering av et digitalt båndpassfilter med hovedvekt på minimale transisjonsbånd. Målet med oppgaven var å utvikle et FPGA-basert digitalt filter tilsvarende et analogt båndpassfilter, plassert i dagens Galileo Satellite Search and Rescue Transponder. Det digitale filteret skulle designes og implementeres for bruk på en romfartskvalifisert FPGA. Det eksisterende analoge filteret har en båndbredde på 100 kHz sentrert ved 70.98 MHz, med transisjonsbånd på 50 kHz. Dempingen i stoppbåndet skal være minst 80 dB, og faseresponsen skal være lineær.

Det foreslåtte digitale filteret, her kalt *Masterfilter*, ble utformet ved å benytte flertrinns filterteknikker, som blant annet undersampling, miksing, desimering og interpolering. Sampling frekvensen til filteret ble satt til 30 MHz, og inngangssignalet ble undersamplet til 10.98 MHz. Utgangssignalet av filteret ble sentrert om 3.48 MHz, med en båndbredde på 100 kHz. Matlab ble benyttet for å lage prototyper av interne filtere i designfasen, og det endelige filteret ble implementert i VHDL. For å oppfylle kravene til ytelse og plassbruk i en romfartskvalifisert FPGA ble digitale optimaliseringsteknikker benyttet. Dette omfattet blant annet pipelining og resource sharing. For å gjøre filteret så generisk som mulig, ble ingen leverandør-spesifike komponenter benyttet.

Filteret ble grundig testet ved blant annet test av pulsrespons og tonetesting av både interne komponenter og det samlede filtersystemet. Filterets overføringsfunksjon ble bestemt ved hjelp av simuleringer i Modelsim. I tillegg til disse simuleringene ble det også implementert en versjon av filteret i en Altera Cyclone II FPGA. Her ble funksjonalitet og frekvensrespons testet og kartlagt.

På grunnlag av de testresultatene som ble funnet i denne oppgaven ble det konkludert med at det foreslåtte digitale filteret ville være et tilstrekkelig alternativ til det eksisterende analoge filteret i dagens Search and Rescue Transponder. En uendelig demping ble målt for frekvenser 39 kHz under passbåndet, og 30 kHz over passbåndet. Det ble funnet noen utfordringer med timing i den fysiske implementeringen av filteret, og det anbefales at FPGA-spesifik klokkelogikk blir benyttet i en eventuell implementasjon.

## **Preface**

This paper was written as a master's thesis in design of digital systems at NTNU. The focus of my master's degree is FPGA design, and digital signal processing was a relatively new field for me before this thesis. This thesis was performed over the course of 20 weeks, without any related preceding specialization project.

The assignment was given by Kongsberg Norspace, under the supervision of Stig Rooth. The initial problem description was quite open, and further limitations were introduced throughout the semester. Also, it was decided that the focus of the thesis should mainly be FPGA based design of the filter, as this was most relevant considering previous experience and interests.

I would like to thank my thesis supervisors, Associate Professor Bjørn B. Larsen and Professor Tor A. Ramstad for helpful guidance, and Kongsberg Norspace for an interesting and challenging assignment. I would also like to thank Stig Rooth, Maxime Adadja and Espen Flo Eriksen for guidance and insight during this semester.

# **Contents**

| 1 | Intr | oduction                                | 3  |

|---|------|-----------------------------------------|----|

|   | 1.1  | Motivation                              | 3  |

|   | 1.2  | Problem Description                     | 4  |

|   | 1.3  | Report Structure                        | 4  |

| 2 | Sign | al Processing                           | 5  |

|   | 2.1  | Digital Sampling                        | 5  |

|   |      | 2.1.1 Signal Resolution                 | 5  |

|   |      | 2.1.2 Quantization and Noise            | 5  |

|   |      | 2.1.3 The Sampling Theorem              | 7  |

|   |      | 2.1.4 Sampling of Bandpass Signals      | 7  |

|   |      | 2.1.5 Noise in Bandpass Sampled Signals | 10 |

|   | 2.2  | Filtering                               | 10 |

|   |      | 2.2.1 FIR Filters                       | 11 |

|   | 2.3  | Signal Mixing                           | 13 |

|   | 2.4  | Decimation                              | 13 |

|   | 2.5  | Interpolation                           | 15 |

| • | ъ    | · ·                                     | 40 |

| 3 | _    | tal Design                              | 19 |

|   | 3.1  | Fixed-Point Representation              | 19 |

|   |      | 3.1.1 Overflow                          | 20 |

|   | 3.2  | Digital Signal Processing in an FPGA    | 20 |

|   |      | 3.2.1 Digital Mixing                    | 20 |

|   |      | 3.2.2 FPGA Clocking                     | 21 |

|   |      | 3.2.3 FPGA and Space Qualification      | 22 |

|   |      | 3.2.4 FPGA Architecture                 | 23 |

|   | 3.3  | Optimizing for Performance and Area     | 23 |

|   |      | 3.3.1 Pipelining                        | 24 |

|   |      | 3.3.2 Resource Sharing                  | 25 |

|   |      | 3.3.3 Constant Input Multipliers        | 26 |

| 4 | Exis | ting Analog Filter                      | 29 |

| 5 | Met  | hods and Tools                          | 31 |

| 6            | Prop         | posed Digital Filter                  | 33         |

|--------------|--------------|---------------------------------------|------------|

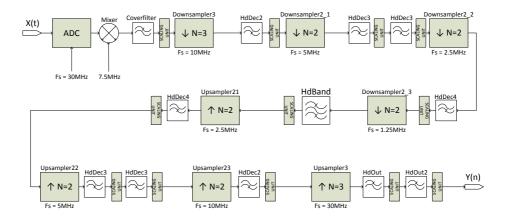

|              | 6.1          | Initial Sampling, Mixer and Filter    | 33         |

|              | 6.2          | Signal Decimation                     | 38         |

|              | 6.3          | Bandpass Filtering                    | 40         |

|              | 6.4          | Signal Interpolation                  | 41         |

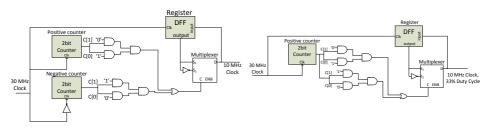

|              | 6.5          | Clock Hierarchy                       | 43         |

|              | 6.6          | Filter Specifications                 | 45         |

|              |              | 6.6.1 Group Delay                     | 45         |

|              |              | 6.6.2 Overflow                        | 45         |

|              |              |                                       |            |

| 7            | Synt         | thesis and Resource Optimization      | 47         |

|              | 7.1          | Initial Synthesis                     | 47         |

|              | 7.2          | Optimizations in HDL                  | 47         |

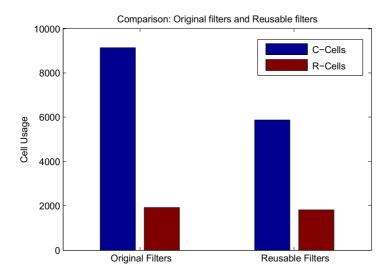

|              |              | 7.2.1 Resource Sharing                | 48         |

|              |              | 7.2.2 Filter Coefficient Optimization | 49         |

|              |              | 7.2.3 Optimizing for Performance      | 49         |

|              |              |                                       |            |

| 8            | Sim          | ulation and Verification              | 53         |

|              | 8.1          | Digital Simulation                    | 53         |

|              |              | 8.1.1 Impulse Responses               | 53         |

|              |              | 8.1.2 Tone Testing                    | 54         |

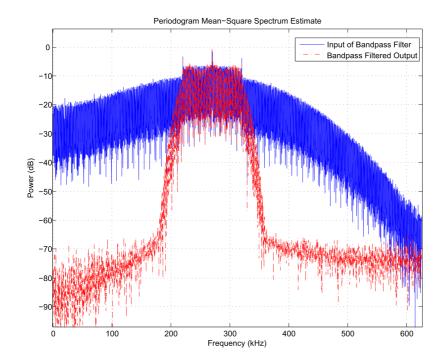

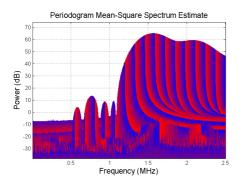

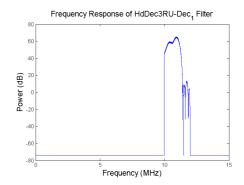

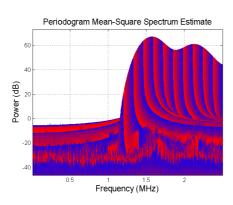

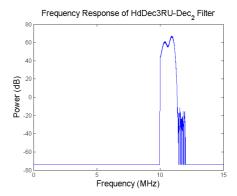

|              |              | 8.1.3 Spectrum Analysis               | 54         |

|              | 8.2          | FPGA-Testing                          | 56         |

|              |              |                                       |            |

| 9            | Disc         | ussion                                | 61         |

| 10           | Con          | clusions                              | 65         |

| 10           | Con          | Clusions                              | 0.5        |

| 11           | Furt         | ther Work                             | 67         |

| A            | Filte        | er Frequency and Phase Responses      | 69         |

| ъ            | <b>X7TTT</b> |                                       | <b>5</b> 2 |

| В            | VHI          | OL Simulation                         | 73         |

| C            | Filte        | er Optimization                       | 75         |

| D            | Test         | ing of the Filters                    | 77         |

| _            |              | Testing With Tones                    | 77         |

|              |              |                                       |            |

| $\mathbf{E}$ |              | DL Code                               | <b>79</b>  |

|              | E.1          | 10 MHz Clock Generator Code           | 79         |

| F            | Har          | dware Simulations                     | 81         |

| G            | Filte        | er FPGA Tests                         | 89         |

| R۵           | feren        | res                                   | 93         |

# **List of Figures**

| 2.1 ADC Quantization and Noise [2]                                                  |    |

|-------------------------------------------------------------------------------------|----|

| 2.2 Impact of Aliasing [1]                                                          |    |

| 2.3 Illustration of Bandpass Sampling [4]                                           | 9  |

| 2.4 Allowed and Forbidden Sampling Frequencies [1]                                  | 10 |

| 2.5 Impact of Tap Weights in an FIR Filter                                          |    |

| 2.6 FIR Filter Structure [3]                                                        | 12 |

| 2.7 Symmetric FIR Filter Structure [3]                                              | 13 |

| 2.8 Signal Mixer                                                                    |    |

| 2.9 Decimation by $D = 4$                                                           | 15 |

| 2.10 Decimation with a Highpass Filter                                              | 16 |

| 2.11 Illustration of Interpolation                                                  |    |

| 2.12 Frequency Placement After Upsampling by $N = 6 \dots \dots \dots$              |    |

|                                                                                     |    |

| 3.1 Clock Skew [10]                                                                 |    |

| 3.2 C-Cells and R-Cells in an RTAX2000S [14]                                        |    |

| 3.3 Pipelining [10]                                                                 | 25 |

| 3.4 Resource Sharing Illustration                                                   | 25 |

| 3.5 Resource Sharing, Continued                                                     | 26 |

| 4.1 Current Filter Response                                                         | 29 |

| 4.2 SART Converter Chain                                                            |    |

| 4.3 Expected Input Frequency Placement                                              |    |

|                                                                                     |    |

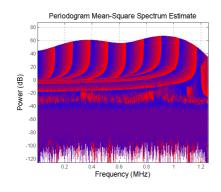

| 6.1 Aliased Signal at 30MHz Sampling                                                | 36 |

| 6.2 Down-Mixed Signal                                                               |    |

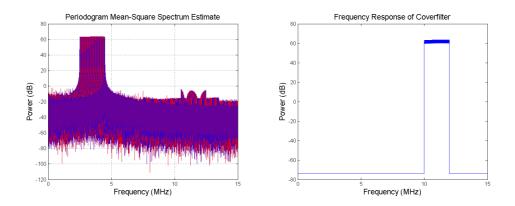

| 6.3 Mixer and Coverfilter                                                           | 37 |

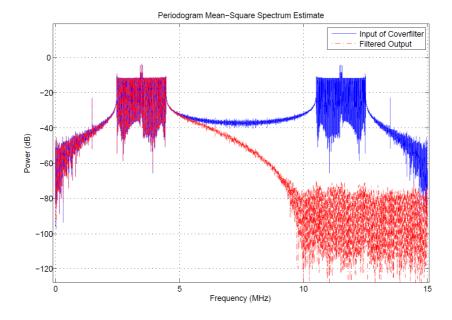

| 6.4 Signal after Coverfilter                                                        | 38 |

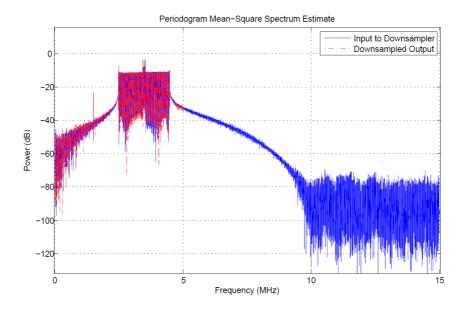

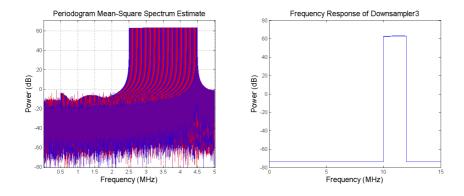

| 6.5 Signal at $F_s = 30$ MHz and $F_s = 10$ MHz                                     | 39 |

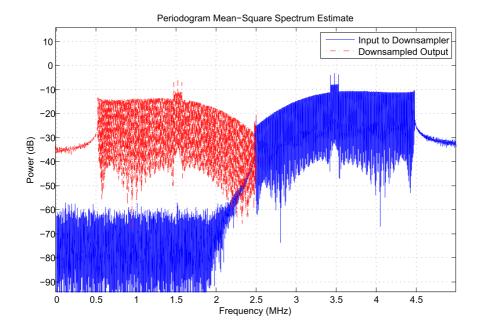

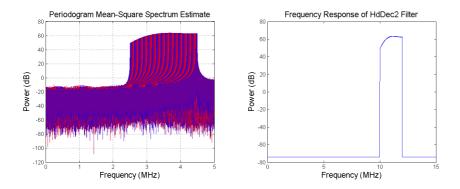

| 6.6 Signal at $F_s = 5 \text{ MHz} \dots \dots \dots \dots \dots \dots \dots \dots$ | 40 |

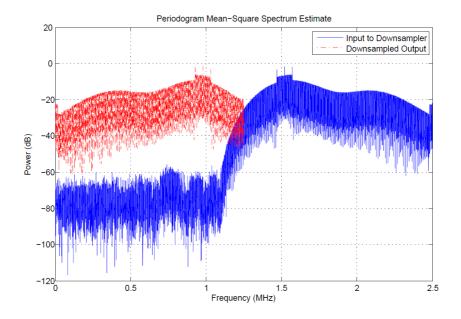

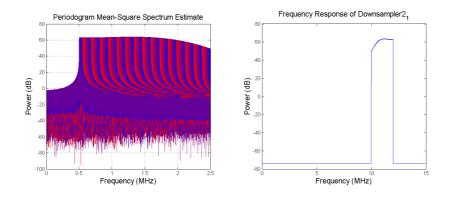

| 6.7 Signal at $F_s = 2.5 \text{ MHz}$                                               | 41 |

| 6.8 Signal After Bandpass Filtering                                                 | 42 |

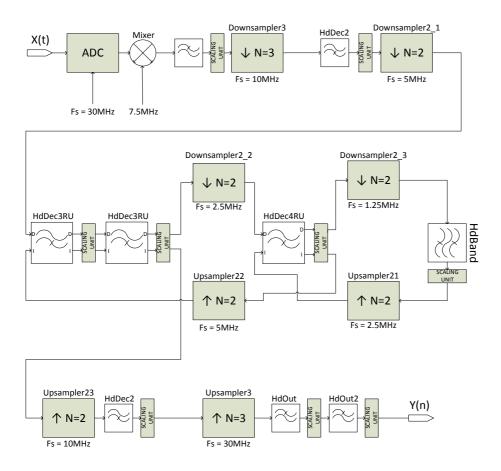

| 6.9 The Masterfilter                                                                | 43 |

| 6.10 Generation of 10 MHz Clock Signal                                              |    |

| 7.1 Improvement of Reusable Filters                                                 | 48 |

| <u>*</u>                                                                            |    |

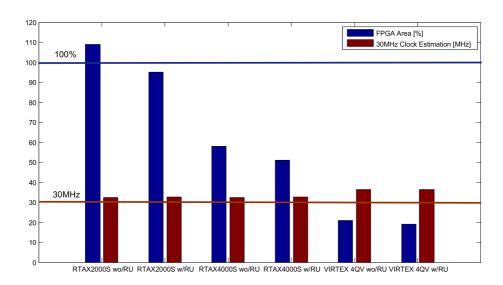

| 7.2 Area Usage and Performance for Space Qualified FPGAs                            |    |

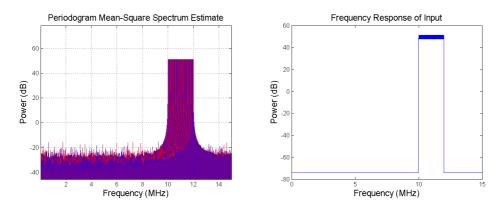

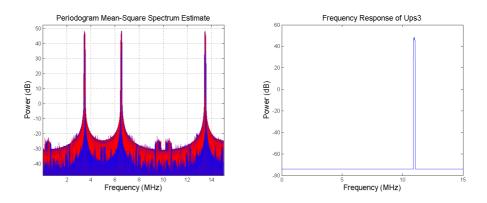

| 8.1          | Simulation input                                     | 54 |

|--------------|------------------------------------------------------|----|

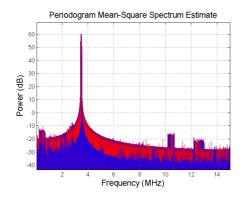

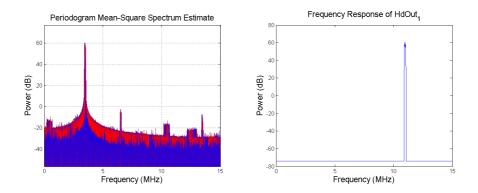

| 8.2          | Simulation Output                                    | 55 |

| 8.3          | Simulation Output, 7.5 MHz Offset                    | 56 |

| 8.4          | Testing Setup on FPGA                                | 57 |

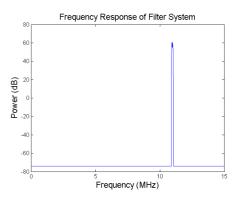

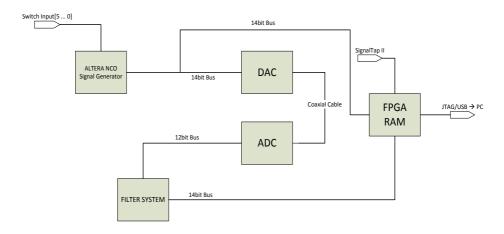

| 8.5          | Results from the FPGA-Testing                        | 58 |

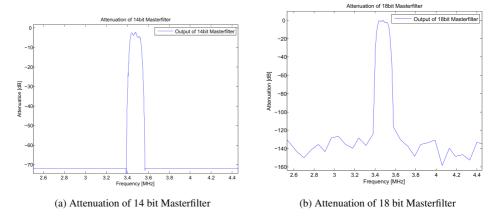

| 8.6          | Attenuation of Masterfilter                          | 59 |

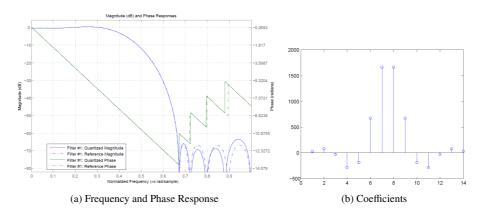

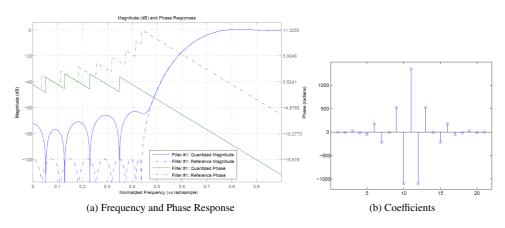

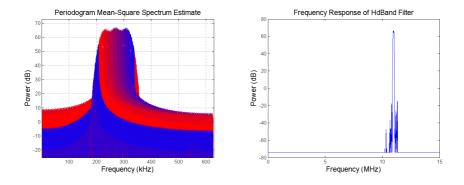

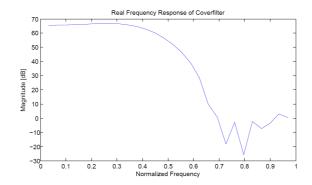

| A.1          | Theoretical Response of Coverfilter                  | 69 |

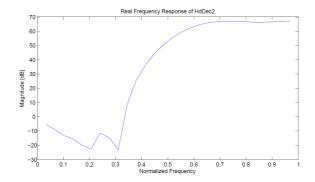

| A.2          | Theoretical Response of HdDec2                       | 69 |

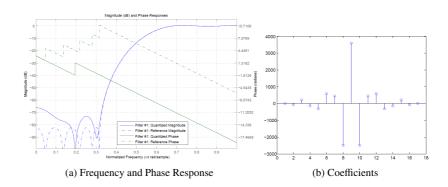

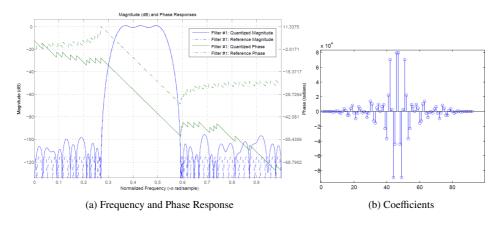

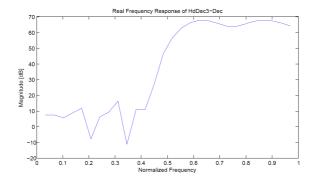

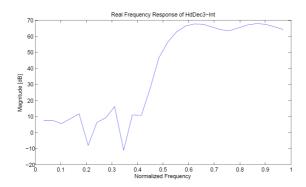

| A.3          | Theoretical Response of HdDec3                       | 70 |

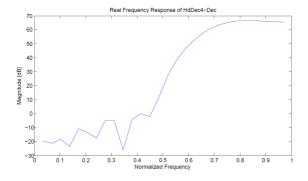

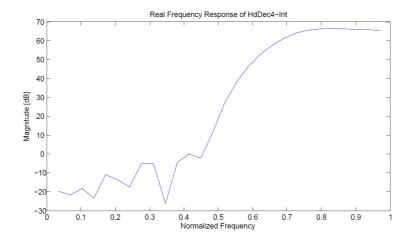

| A.4          | Theoretical Response of HdDec4                       | 70 |

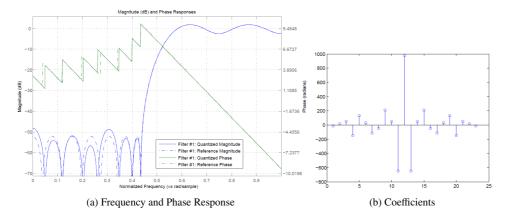

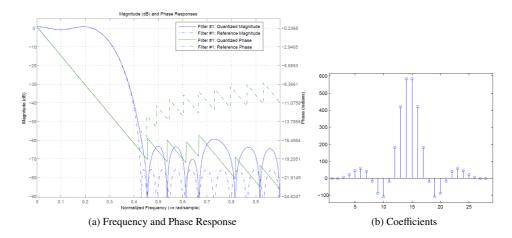

| A.5          | Theoretical Response of HdBand                       | 70 |

| A.6          | Theoretical Response of HdOut                        | 71 |

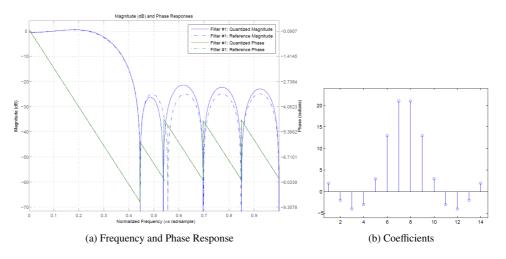

| A.7          | Theoretical Response of HdOut2                       | 71 |

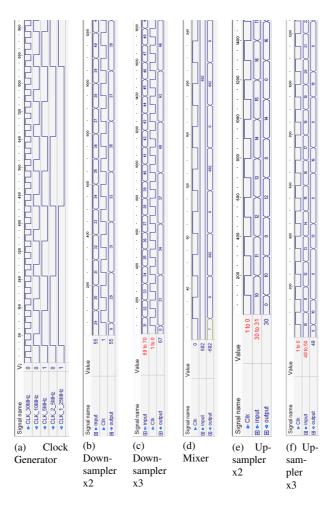

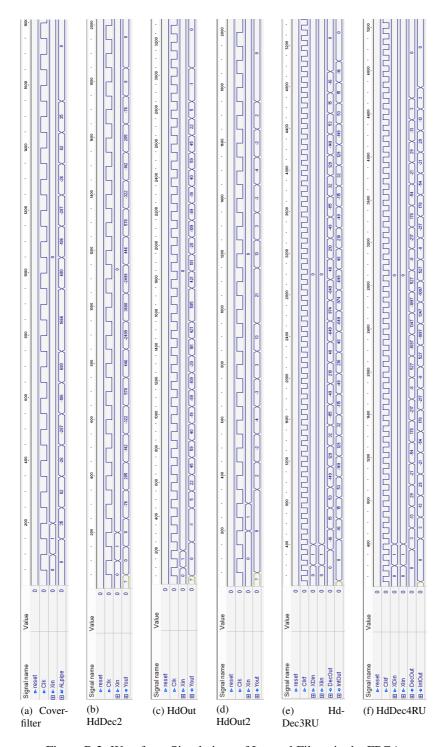

| B.1          | Waveform Simulations of Processing Units             | 73 |

| B.2          | Waveform-Simulations of Internal Filters in the FPGA | 74 |

|              |                                                      |    |

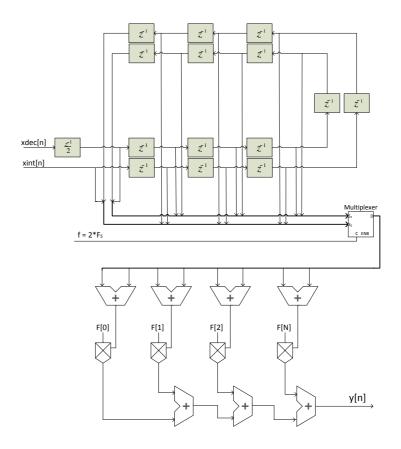

| C.1          | Reusable Decimation- and Interpolation Filter        | 75 |

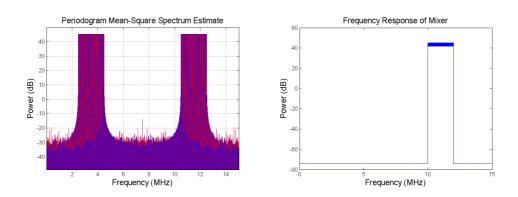

| F.1          | Mixer Output                                         | 81 |

| F.2          | Coverfilter Output                                   | 81 |

| F.3          | Downsampler3 Output                                  | 82 |

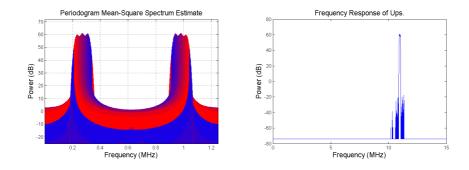

| F.4          | HdDec2 Decimation Output                             | 82 |

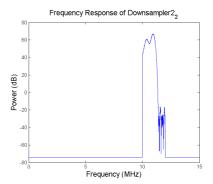

| F.5          | Downsampler2_1 Output                                | 82 |

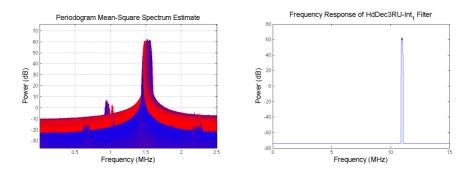

| F.6          | HdDec3RU Decimation Output, Stage 1                  | 83 |

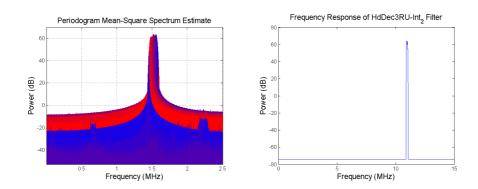

| F.7          | HdDec3RU Decimation Output, Stage 2                  | 83 |

| F.8          | Downsampler2_2 Output                                | 83 |

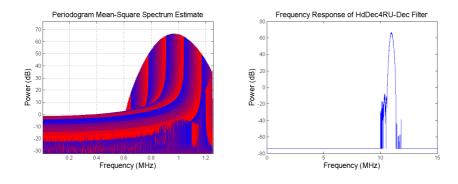

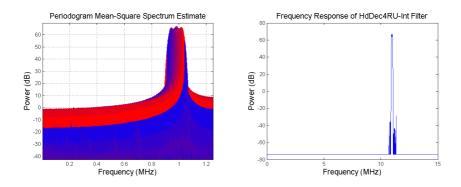

| F.9          | HdDec4RU Decimation Output                           | 84 |

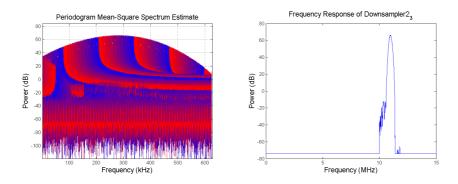

|              | Downsampler2_3 Output                                | 84 |

| F11          | Bandpassfilter Output                                | 84 |

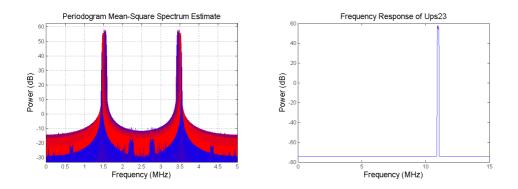

|              | Upsampler21 Output                                   | 85 |

|              | HdDec4RU Interpolation Output                        | 85 |

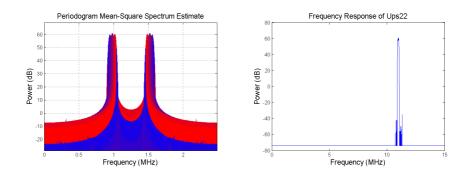

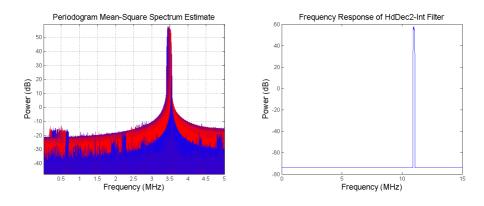

| F 14         | Upsampler22 Output                                   | 85 |

| F.14         | HdDec3RU Interpolation Output, Stage 1               | 86 |

| F.15         | HdDec3RU Interpolation Output, Stage 2               | 86 |

| F.10         | Upsampler23 Output                                   | 86 |

| Г.17<br>Г.10 | UdDas2 Intermelation Output                          | 87 |

|              | HdDec2 Interpolation Output                          |    |

|              | Upsampler3 Output                                    | 87 |

| F.20         | HdOut Output                                         | 87 |

| G.1          | Hardware Coverfilter Response                        | 89 |

| G.2          | Hardware HdDec2 Response                             | 89 |

| G.3          | Hardware HdDec3RU Response, Decimation Channel       | 90 |

| G.4          | Hardware HdDec3RU Response, Interpolation Channel    | 90 |

| G.5          | Hardware HdDec4RU Response, Decimation Channel       | 90 |

| G.6          | Hardware HdDec4RU Response, Interpolation Channel    | 91 |

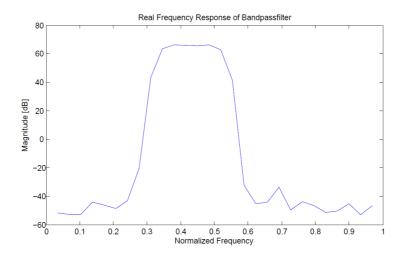

| G.7          | Hardware Bandpassfilter Response                     | 91 |

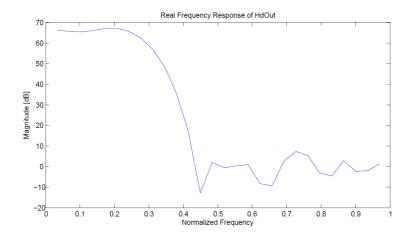

| G.8 | Hardware HdOut Response . |  |  |  |  |  |  |  |  |  |  |  |  | 92 |

|-----|---------------------------|--|--|--|--|--|--|--|--|--|--|--|--|----|

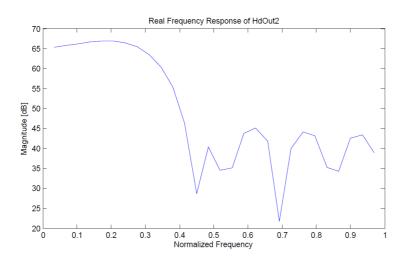

|     | Hardware HdOut2 Response  |  |  |  |  |  |  |  |  |  |  |  |  |    |

# **List of Tables**

| 3.1 | Space Qualified FPGAs                               | 3 |

|-----|-----------------------------------------------------|---|

| 6.1 | Direct Design of the Filter                         | 3 |

| 6.2 | Resulting Frequency Components After Sampling [MHz] | 5 |

| 6.3 | Interpolation Stages                                | 2 |

| 6.4 | Group Delay Summary                                 | 5 |

| 6.5 | Overflow Summary                                    | 6 |

| 7.1 | Initial Synthesis Report                            | 7 |

| 7.2 | Optimization by Filter Reusage                      | 9 |

| 7.3 | Original and Improved Filter Coefficients           | 9 |

| 7.4 | Improvement after Pipelining                        | 0 |

| 7.5 | Optimized Synthesis Report                          | 0 |

| 8.1 | Effect of Increasing Precision                      | 9 |

| D.1 | Tone-Test of Coverfilter                            | 7 |

| D.2 | Tone-Test of HdDec2                                 | 7 |

| D.3 | Tone-Test of HdBand                                 | 7 |

| D.4 | Tone-Test of HdOut                                  | 8 |

| D.5 | Tone-Test of HdOut2                                 | 8 |

| D.6 | Tone-Test of HdDec3RU                               | 8 |

| D.7 | Tone-Test of HdDec4RU                               | 8 |

## **List of Abbreviations**

ADC Analog to Digital Converter

**C-Cells** Combinatorial Cells (Actel)

**CORDIC** Coordinate Rotation Digital Computer

**DAC** Digital to Analog Converter

dBFS Decibels relative to full scale

**DSP** Digital Signal Processing

FIR Finite Impulse Response

FPGA Field-Programmable Gate Array

**F**<sub>s</sub> Sampling Frequency

**GPIO** General Purpose Input/Output

**HDL** Hardware Description Language

IIR Infinite Impulse Response

**IP** Intellectual Property

LO Local Oscillator

LTI Linear Time-Invariant

LUT Look-Up Table

MSB Most Significant Bit

**NCO** Numerically Controlled Oscillator

**PLL** Phase-Locked Loop

QML Qualified Manufactering Line

**RAM** Random Access Memory

R-Cells Register Cells (Actel)

**RHA** Radiation Hardened Assurance

RMS Root-Mean-Square

**RTL** Register Transfer Level

**SART** Search and Rescue Transponder

SAW Surface Acoustic Wave

SEL Single Event Latch-Up

SEU Single Event Upset

SNR Signal-to-Noise Ratio

SQNR Signal-to-Quantization-Noise Ratio

**TID** Total Ionizing Dose

TMR Triple Module Redundancy

VHDL Very-High-Speed Integrated Circuit Hardware Description Language

## **Chapter 1**

## Introduction

#### 1.1 Motivation

One of the most important components in any signal processing system is frequency sensitive filters. Filters are applied to exclude frequency components from a signal, and they are generally classified according to their frequency responses. A field where digital signal processing, and hence filtering is widely applied is in communication systems. Communication systems can be found in cellphones, broadcasting and even in space.

The concept of space communication systems brings forth new challenges in the filter design, such as reliable performance in extreme conditions. This is where digital signal processing has an advantage over traditional analog systems. As long as the system clock is held at a constant frequency, the behavior of the system will also remain stable, in contrast to analog systems which will drift significantly during changing temperatures. In satellite systems, analog components will have to be heated to a constant temperature to achieve reliable performance, which means bringing a heavy and energy costly heat source on board the satellite.

One application of space communication is the use of emergency transponders, which receives distress signals from one location on earth, filters the signal and transmits it back to a rescue central. This functionality can be found in some modern satellites, among them the new Galileo Satellites. One of the filters used in the Galileo Satellite Search and Rescue Transponder is a very narrow bandpass filter centered at 70.98 MHz, with a bandwidth of 100 kHz. The transition bands of the filter are approximately 50 kHz at both sides of the passband, with an attenuation exceeding 80 dB in the stopbands. To design a digital *finite impulse response* (FIR) version of this filter directly with the *Parks-McClellan* filter design algorithm [1] would require an extreme amount of filter stages, which would not be possible to implement in any of the current space qualified *Field Programmable Gate Arrays* (FPGA). To design a realizable digital filter with these specifications, advanced filter techniques and digital design methodology will have to be applied. However, the gain of reducing the area which will be climate controlled on the satellite will free up the weight- and power budget for other potential applications, which in turn makes the design efforts well worth while.

#### 1.2 Problem Description

The object of this thesis is to design an FPGA based digital filter suitable to replace the analog filter which is used in the current Galileo Satellite Search and Rescue Transponder. This filter has a very high quality factor, with a bandwidth of 100 kHz, transition bands of 50 kHz and a center frequency of 70.98 MHz. Since the filter is to be placed in a sensitive communication system, the filter will need to be strictly stable and have a linear phase. The filter is a second stage filter in the receiver chain, preceded by a 1.8 MHz bandpass surface acoustic wave (SAW) filter and a mixer. The input of this filter will therefore be a bandpass signal, with a bandwidth of 1.8 MHz centered at 70.98 MHz, and a sufficiently attenuated stopband. From preceding stages in the transponder chain, one can also expect to find undesired signal components at 741 MHz and 670 MHz. These components should be removed with this digital filter. Furthermore, the following specification should be fulfilled by the digital filter:

- $F_{S,FPGA} = 30 \text{MHz} \pm 5 \text{MHz}$

- The FPGA should use the same clock frequency for receiving and transmitting data externally.

- The design should fit into a space qualified FPGA, preferably an Actel RTAX2000S.

- The bandwidth of the passband should be approximately 100 kHz.

- The attenuation in the stopbands should be at least 80 dB, 50 kHz apart from the passband.

- The filter response should have a linear phase.

The filter should be designed and simulated with Matlab, and implemented in hardware using VHDL. The implemented filter should be verified by simulations of the VHDL code, and testing on an FPGA. The simulated performance of the filter should be characterized by its transfer function.

#### 1.3 Report Structure

The report will be structured as follows:

- Chapters 2 and 3 will handle the necessary signal processing and digital design theory needed for the design and testing.

- Chapter 4 will introduce the existing analog filter used in the Search and Rescue Transponder unit.

- In chapter 5, the tools used in the thesis are described.

- Chapter 6 describes the designed filter, and the reasons behind the design choices.

- In chapters 7 and 8 the physical performance estimations and simulation results are described.

- In chapters 9, 10 and 11 the results are discussed and conclusions are stated. Suggestions of further improvements are also described.

## Chapter 2

# **Signal Processing**

#### 2.1 Digital Sampling

One of the fundamental prerequisites of a digital signal-processing system is that the input of the system should be a digital signal. In contrast to analog signals, the digital signal consists of several quantized steps which represents the magnitude and frequency information of the signal.

#### 2.1.1 Signal Resolution

The granularity of the digital signal, or how similar the digital signal is to its original analog signal is dependent upon, among other parameters, how many bits which are used to represent the amplitude steps. These steps are called *quantization steps*, represented by [1]

$$\Delta = \frac{x_{max} - x_{min}}{2^b - 1} \tag{2.1.1}$$

where x is the input signal and b represents the number of bits which will represent the signal.  $\Delta$  defines the *quantizer step size*, which are determined by the *Analog to Digital Converter* (ADC).

Equation 2.1.1 suggest a significant increase in signal resolution as a result of increasing the bit width. This can be illustrated using a signal with an analog amplitude of 2 V. If a 2 bit digital signal is to represent this signal, there would only be four steps to represent this 2 V range. However, if a 16 bit digital signal is used to model this analog signal,  $2^{16}$  steps would be available. If the quantization is *linear* or *uniform*, meaning that each quantization step is of equal size, the granularity of the signal would be

$$\frac{2V}{2^{16}-1} = 3.05 \cdot 10^{-5} V = 30.5 \mu V$$

(2.1.2)

#### 2.1.2 Quantization and Noise

Since the number of quantization steps used to represent the signal cannot be infinite, a *quantization error* results from the analog to digital conversion, which is represented by

$$-\frac{\Delta}{2} \le e_q(n) \le \frac{\Delta}{2} \tag{2.1.3}$$

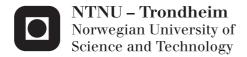

A graphical illustration of the quantization error resulting from an ADC can be seen in figure 2.1. Equation 2.1.3 only applies if the analog signal is located within the domain of the ADC. If the signal exceeds the ADC range, the quantization error will exceed the limits from equation 2.1.3. The signal is then clipped, which results in *overload noise* [1].

Figure 2.1: ADC Quantization and Noise [2]

The noise resulting from the quantization error is often analyzed together with the signal, as *signal-to-quantization-noise power*, *SQNR* [1]. The SQNR can be expressed as

$$SQNR = 10log_{10} \frac{P_x}{P_n} \tag{2.1.4}$$

where  $P_x$  is the signal power,  $E[x^2(n)]$ , and  $P_n$  is the power of the quantization noise [1]

$$P_n = \sigma_e^2 = \int_{-\frac{\Delta}{3}}^{\frac{\Delta}{2}} e^2 p(e) de = \frac{1}{\Delta} \int_{-\frac{\Delta}{3}}^{\frac{\Delta}{2}} e^2 de = \frac{\Delta^2}{12}$$

(2.1.5)

or, expressed as the root-mean-square (rms) quantization noise [2]

$$P_{n,rms} = \frac{\Delta}{\sqrt{12}} \tag{2.1.6}$$

Assuming that the quantization noise is uncorrelated to the input signal and that  $P_{n,rms}$  remains approximately as described in equation 2.1.6, a theoretical output *signal-to-noise* ratio (SNR) can be calculated for a given input at the ADC. For a rail-to-rail sinewave expressed as

$$v(t) = \frac{\Delta \cdot 2^N}{2} \sin(2\pi f t) \tag{2.1.7}$$

where N is the number of bits used to quantize the signal, the RMS value would be [2]

$$v_{rms} = \frac{\Delta \cdot 2^N}{2\sqrt{2}} \tag{2.1.8}$$

The SNR for an ideal ADC would then be expressed as [2]

$$SNR = 20\log_{10} \frac{v_{rms}}{P_{n rms}} \tag{2.1.9}$$

$$SNR = 20\log_{10} \frac{\Delta \cdot 2^{N}/2\sqrt{2}}{\Delta/\sqrt{12}}$$

(2.1.10)

which results in the commonly used formula for calculating the SNR over the dc to  $\frac{f_s}{2}$  bandwidth for quantized signals,

$$SNR = 6.02 \,\text{N} + 1.76 \,\text{dB}$$

(2.1.11)

Examining equation 2.1.11, it is apparent that the SNR will improve by approximately 6 dB for each bit added to quantize the signal. The constant 1.76 of equation 2.1.11 originates from the rail-to-rail sinewave at the input, and it will vary for other input signals.

#### 2.1.3 The Sampling Theorem

In addition to the voltage amplitude steps being sampled, it is also essential to know how often to sample these signals. The Sampling Theorem states that "A bandlimited continuous-time signal, with the highest frequency (bandwidth) B hertz, can be uniquely recovered from its samples provided that the sampling rate  $F_s \ge 2B$  samples per second" [1]. For lowpass signals, this implies that the sampling frequency should be twice the frequency of the highest frequency component of the signal. The sampling rate at which  $F_s = 2B$  is called the Nyquist rate [1].

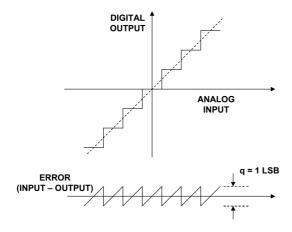

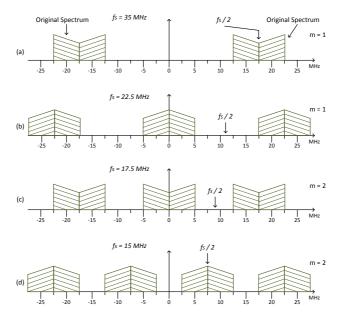

When an analog signal is sampled, the frequency components are repeated every  $kF_s$  frequency, where k is an integer [1]. If the original signal is sampled with a lower frequency than 2B, the resulting signal will contain interfering frequency components. This phenomena is called *aliasing*, which means that the frequency components are overlapping, and the resulting reconstructed signal will not be equal to the original signal. Aliasing is irreparable and should be avoided [3]. Figure 2.2 describes the process of sampling and reconstructing the original signal, with and without aliasing. Figure 2.2a shows a signal which is sampled with a sampling frequency that satisfies the sampling theorem, and figure 2.2b shows a signal sampled at a lower sampling rate than 2B.

#### 2.1.4 Sampling of Bandpass Signals

If one is to sample a signal with bandwidth 2B and center frequency  $F_c$ , where  $B << F_c$ , the traditional interpretation of the sampling theorem would suggest that the sampling frequency should be at least  $2(F_c + B)$ . This way the signal is treated as a lowpass signal, which assures that there will be no aliasing at all [4]. However, what the sampling theorem really states is that the sampling frequency needs to be twice the signal bandwidth, making the frequency at which the signal is centered irrelevant for the ability to preserve the signal

Figure 2.2: Impact of Aliasing [1]

information after sampling. This fact can be exploited to reduce the sampling frequency of bandpass signals significantly, as these signals can be *downsampled* with a sampling frequency of 2B or higher. However, the reduced sampling frequency brings forth new issues with mirroring, aliasing and noise.

The theory of bandpass sampling states that when sampling a signal at a rate of  $f_s$ , all frequency components in the analog domain will be mirrored down to the baseband, which is located at dc to  $\frac{f_s}{2}$  Hz [5]. To better understand the effects of mirroring, the term band position is introduced. This term refers to the fractional number of signal bandwidths which the lowest frequency of a bandpass signal is located from the baseband. A special case of band position is called *Integer Band Positioning*[5]. This approach first defines an integer m to be a multiple of the bandwidth,  $F_H = mB$  [1], where  $F_H$  is the highest frequency component of the signal. This integer m is the band position, and the original signal will be aliased and reflected for each band position, 0 to m-1. This is illustrated for a bandpass signal with several possible sampling frequencies in figure 2.3. These bands are also known as *Nyquist zones*. Notice that if the band of the original signal is placed within an even numbered Nyquist zone, the sampled signal at the baseband will be the inverse of the original signal [1]. The theoretical lowest sampling frequency is defined as  $F_s = 2B$ , but it should be noted that this only applies if there are no signal components at  $F_c \pm B/2$  [5].

Another limitation when using the theoretical minimum sampling rate is that any engineering imperfection, such as clock instability will cause aliasing due to the low margin of error in the  $\frac{F_S}{B}$  ratio [5]. These considerations leads to the fact that one does not have to use 2B as a goal in it self for the optimal sampling frequency.

To counter the sensitivity to engineering imperfections, a sampling scheme called Ar-bitrary  $Band\ Positioning$  is introduced. This line of thought states that the band positioning does not have to be strictly set by the signal bandwidth, leaving room for zero-magnitude frequency components at both sides of the signal. When selecting a sampling frequency which yields non-aliasing regions on both sides of the  $\frac{F_H}{B}$  rate, this extra bandwidth is

Figure 2.3: Illustration of Bandpass Sampling [4]

called the *guard band* [5]. This region safeguards against aliasing due to engineering imperfections, which is important as virtually all reference clocks are somewhat unstable. Arbitrary band positioning leads to the following two limitations of the sampling frequency  $F_s$  [1]

$$2F_H \le kF_s \tag{2.1.12}$$

$$(k-1)F_s \le 2F_L \tag{2.1.13}$$

These equations can be solved for k to show that  $k_{max} \le \frac{F_H}{B}$  [1].  $k_{max}$  is the maximum number of Nyquist zones that can fit in the range of dc to  $F_H$ . This leaves the minimum sampling rate to avoid aliasing effects as

$$F_{s,min} = \frac{2F_H}{k_{max}} \tag{2.1.14}$$

Equation 2.1.14 implies that the sampling frequency can be selected from a range of frequencies, limited by [1]

$$\frac{2F_H}{k} \le F_s \le \frac{2F_L}{k-1} \tag{2.1.15}$$

and

$$1 \le k \le \lfloor \frac{F_H}{B} \rfloor \tag{2.1.16}$$

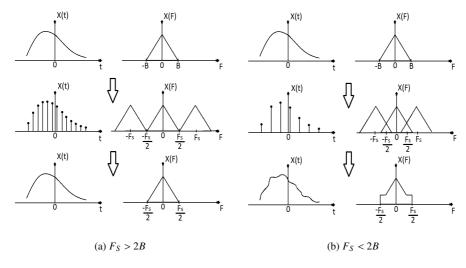

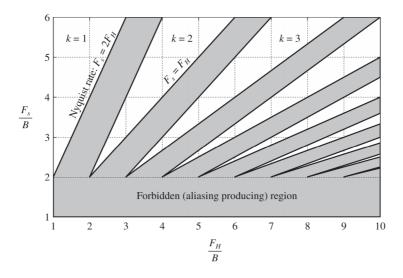

These limitations can be seen graphically in figure 2.4. It should be noted that even though guard bands are introduced and the limitations in figure 2.4 are upheld, clock instability when undersampling is critical.

Figure 2.4: Allowed and Forbidden Sampling Frequencies [1]

#### 2.1.5 Noise in Bandpass Sampled Signals

One of the fundamental requirements of bandpass sampling is that the sampled signal is, in fact, a bandpass signal and that the rest of the band is sufficiently attenuated. The reason for this is that all the wideband noise will also be combined into all of the Nyquist zones [5]. This will result in a degraded SNR in the baseband. The sampled SNR can be calculated as [5]

$$SNR \approx \frac{S}{N_p + (n-1)N_o} \tag{2.1.17}$$

where S is the spectral power density,  $N_p$  is the in-band noise power density,  $N_o$  is the outof-band noise power density and n is the integer band position. For systems with several Nyquist zones and where the noise power density is equally distributed over the whole spectrum, the SNR degradation can be roughly expressed as [5]

$$D_{SNR} = 10\log(n)\,\mathrm{dB} \tag{2.1.18}$$

This degradation of the SNR can consequently be reduced by increasing the sampling frequency, reducing the number of Nyquist zones between the original signal and the baseband.

#### 2.2 Filtering

One of the most fundamental components of any signal processing system is called a filter. A filter is a circuit which alters the attributes of a signal in the time- or frequency domain [3]. There are many types of filters, but in this thesis the focus will be set on digital, linear time-invariant (LTI) filters. LTI filters are generally divided into two types: *Finite Impulse Response* (FIR) filters and *Infinite Impulse Response* (IIR) filters [1]. Although IIR filters

are generally known to have lower sidelobes in the stopband than equally sized FIR filters, the thesis' problem description states that the filter should always be stable, and the phase of the filter should always be linear. This is always the case for FIR filters, while IIR filter have the possibility of being unstable as a result of their feedback-based structure [1].

#### 2.2.1 FIR Filters

An LTI FIR filter can be expressed mathematically as a convolution sum given by [3]

$$y[n] = x[n] * f[n] = \sum_{k=0}^{L-1} f[k]x[n-k]$$

(2.2.1)

or, expressed in the z-domain

$$Y(z) = F(z)X(z) \tag{2.2.2}$$

where

$$F(z) = \sum_{k=0}^{L-1} f[k]z^{-k}$$

(2.2.3)

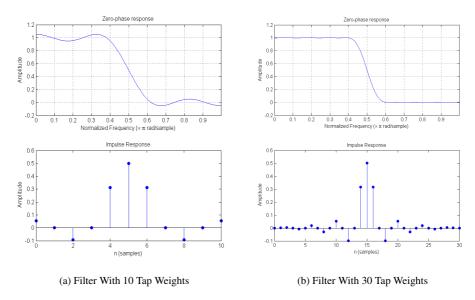

L is the number of *stages* of the filter, and f[k] is a set of constants which are called the filter coefficients, or *tap weights*. As the number of filter stages grows, the complexity of the filter also grows. On the other hand, when the number of stages grows, the attenuation and steepness of the filter also improves. This effect can be seen for a lowpass filter in figure 2.5.

Figure 2.5: Impact of Tap Weights in an FIR Filter

For extremely steep FIR filters, the number of coefficients can grow to the magnitude of  $10^4$  and higher, which imposes issues with area when realizing the filter. FIR filters tend

to use more tap wights than IIR filters, which makes them more expensive to implement. On the other hand, FIR filters have the advantage of being [6]

- Robust

- Inherently stable

- Easy to design for linear phase

- Common in digital applications

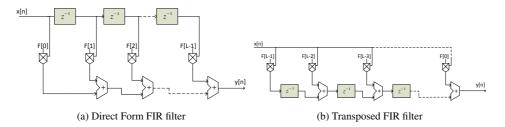

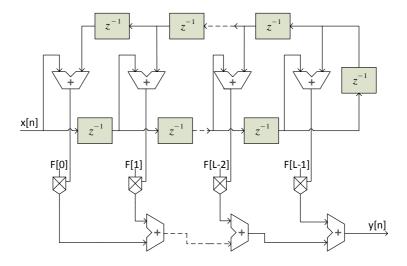

The FIR filter representation from equation 2.2.3 can be expressed as a circuit where x[n] is the input and y[n] is the output, as seen in figure 2.6a. Alternatively, one can alter the *direct form* FIR filter in figure 2.6a into the *transposed* structure in figure 2.6b [3]. This transposed FIR filter has an advantage of a significantly shorter critical path, which results in an increase in performance and throughput [3].

Another way of reducing the size of the FIR filter is to exploit the symmetry of the tap weights. As seen in figure 2.5, the tap weights are identical at both sides of the center tap weight (often described as the  $0^{th}$  sample [3]). This means that the tap weights are equal in pairs, and only half of the multiplications needs to be performed in order to produce the filter response. Coefficients can also be antisymmetric, and with both odd and even number of filter stages [3]. An FIR filter which exploits the symmetric properties of the tap weights can be seen in figure 2.7.

Figure 2.6: FIR Filter Structure [3]

An additional benefit of symmetric and antisymmetric filter coefficients is that they have a guaranteed linear-phase response. Linear-phase response means that the *group delay* is constant for every input frequency [3], which is quite important in for example communication systems, as signals might otherwise be distorted. The group delay of an N-tap FIR filter can be expressed as [4]

$$G = \frac{D}{2 \cdot f_s}$$

s (2.2.4)

where D is the number of time-delay elements in the delay line of the filter, and  $f_s$  is the sampling frequency. Ideally, the output of a linear-phase filter would simply be a time delayed and amplitude-scaled version of the input [1].

Figure 2.7: Symmetric FIR Filter Structure [3]

#### 2.3 Signal Mixing

Another important operation in signal processing of bandpass signals is the process of shifting the signal in the frequency domain. Frequency shifting is important in several settings. In a receiver it is very common to shift a bandpass signal down to a lower frequency, which allows for less demanding processing of the information contained in the signal. In a digital filter, this down-conversion, followed by a reduction of the sampling frequency is common to reduce the filter size. This is because the filter size is dependent upon the steepness of the filter as a function of the sampling frequency. This will be explained in section 2.4.

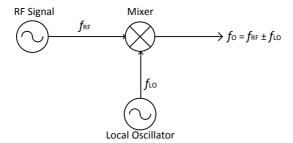

Frequency conversion can be achieved in both the analog and the digital domain with a component called a *mixer*. This three-port device receives a signal and multiplies it with a nonlinear or time-varying element and, ideally, outputs a signal consisting of the sum and difference of the two signals [7]. The multiplicand signal, which often originates in a *local oscillator* (LO), is in many real applications a sine wave with frequency  $f_{LO}$ . The mixing process is illustrated in figure 2.8.

In most cases, only one of the two frequency components,  $f_{RF} + f_{LO}$  or  $f_{RF} - f_{LO}$  are wanted, and the other component will have to be filtered out. In reality, more frequency components than just  $f_{RF} \pm f_{LO}$  might be generated as unwanted harmonic signals [7].

#### 2.4 Decimation

As mentioned in section 2.2.1, the number of tap weights needed to realize a digital FIR filter heavily depends upon how wide the transition band is, with respect to the sampling frequency. A direct form symmetric FIR filter would for instance need significantly more tap weights to obtain a transition band of 5 kHz at a 100 MHz sampling frequency, than if

Figure 2.8: Signal Mixer

the sampling frequency was set to 100 kHz. In fact, the size of the filter at the 100 MHz sampling frequency would probably not be feasible in any realistic system. However, in the case of bandpass signals, where the bandwidth of the signal carrying the actual information is much lower than the signal center frequency, there are techniques for reducing the number of tap weights.

Decimation, or downsampling is a multirate signal processing technique for reducing the sampling frequency of a signal by a factor D. The general formula for sample rate conversion can be expressed as [1]

$$y(mT_y) = \sum_{n = -\infty}^{\infty} x(nT_x)g(mT_y - nT_x)$$

(2.4.1)

where  $g(t) = sinc(\pi t/T_x)$ , and  $T_x$  is the original sampling period. This equation can be specialized for decimation of a factor D as [1]

$$y(mT_y) = y(mDT_x) = \sum_{k=-\infty}^{\infty} x(kT_x)g((mD-k)T_x)$$

(2.4.2)

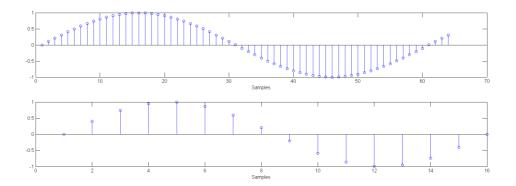

A simple illustration of decimation can be seen in figure 2.9, where a lowpass signal is decimated by a factor D = 4. Here one can observe that even though only the  $D^{th}$  sample is kept, the curvature of the signal and hence the frequency is maintained after downsampling. This is due to the fact that sampling theorem is still satisfied, as previously explained in section 2.1.3.

However, successful signal decimation is more than just arbitrarily reducing the sampling rate of the signal. If one assumes a signal with nonzero frequency components at all frequencies  $|F| \le F_s/2$ , a sample rate reduction of D would cause folded frequency components below  $F_s/2D$  [1]. This will cause aliasing when reconstructing the signal. To avoid this distortion, the bandwidth of the original signal will first have to be reduced to the resulting bandwidth after decimation. In other words, if the original signal bandwidth is  $F_s/2$ , a filter will be needed to reduce this bandwidth to  $F_s/2D$  by suppressing all other frequency components [1]. If the relevant bandpass signal is placed in the lower band, where  $|F| \le F_s/2D$ , a lowpass filter should be used, with the ideal frequency response [1]

$$H_D(\omega) = \begin{cases} 1, & |\omega| \le \pi/D \\ 0, & \text{otherwise} \end{cases}$$

(2.4.3)

Figure 2.9: Decimation by D = 4

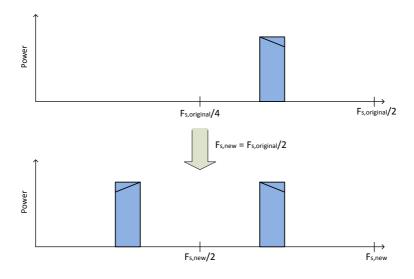

Another case of decimation is when the relevant bandpass signal is placed in the  $|F| > F_s/2D$  region. As explained in section 2.1.4, when sampling at a frequency  $F_s$ , all frequencies  $F \ge F_s/2$  will be folded down into the baseband. The folding attributes can be exploited in decimation to both scale down the sampling frequency and to reduce the frequency at which the signal is centered in one operation. This can be illustrated by decimating a signal with a factor of D = 2. Equation 2.4.2 suggests that frequencies of  $|F| \ge F_s/4$  would be folded down into the band  $|F| \le F_s/4$ . To avoid having the folded-down frequency components distorted by the frequencies which already occupies the band  $|F| \le F_s/4$ , a highpass filter with the following ideal frequency response should be applied before the downsampling process

$$H_D(\omega) = \begin{cases} 0, & |\omega| \le \pi/2\\ 1, & \text{otherwise} \end{cases}$$

(2.4.4)

This filter, along with the downsampling will ideally leave only the  $|F| \ge F_{s,original}/4$  frequency components in the baseband. However, as these signal components will be folded about  $F_{s,original}/4$ , the signal components will now be inverted. This means that the frequency component at the original  $F_{s,original}/2-1$  Hz would now be placed at 1 Hz, and the component at the original  $F_{s,original}/4+1$  Hz would be placed at the new  $F_{s,new}/2-1$  Hz. These folded frequency placements behave similarly as the undersampled signals discussed in section 2.1.4. The process of highpass decimation is illustrated in figure 2.10.

In the digital domain, the downsampling process of decimation can be achieved efficiently by only using every  $D^{th}$  sample of the signal. The digital filter needed, in both cases of where the relevant signal is placed, should be an FIR filter to maintain the linear phase response. There are no absolute requirements of the attenuation of the filter used in the decimation process, but the filter should be designed for the specific application it is meant for, and how much aliasing this application can withstand [8].

#### 2.5 Interpolation

The goal of signal interpolation is to increase the sampling frequency of the signal, while maintaining the signal information. Although interpolation resembles signal decimation,

Figure 2.10: Decimation with a Highpass Filter

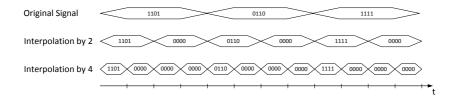

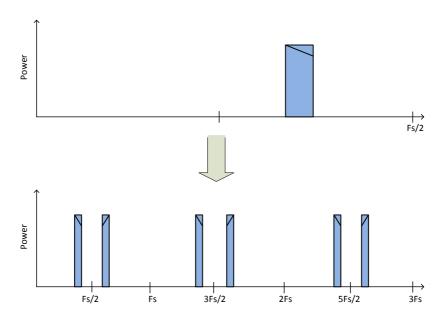

there are some vital differences. The first step of the interpolation process is to increase the sampling frequency, which is called *upscaling* or *upsampling* [9]. This can be done by placing the original samples at every  $N^{th}$  position, and inserting zeros in between each sample [9]. This process is illustrated in figure 2.11. In the frequency domain, the signal will be mirrored at every Nyquist interval. An illustration of this phenomena when upsampling by a factor of N = 6 can be seen in figure 2.12.

Figure 2.11: Illustration of Interpolation

The next step of the interpolation process is to filter the upscaled signal. Depending on the upscaling factor, there will be several mirrored signals within the bandwidth which needs to be removed. As with the decimation process, one can choose if the desired signal lies in the upper or lower part of the new bandwidth with the type of filter used in the filtering stage.

Figure 2.12: Frequency Placement After Upsampling by N = 6

# **Chapter 3**

# **Digital Design**

When working with digital signal processing, one of the first decisions to make is whether to use fixed-point representation, or floating-point representation of numbers. In a general sense, floating-point representation has a much higher accuracy than fixed-point representation [3]. This, however, comes at the cost of both performance and circuit complexity.

## 3.1 Fixed-Point Representation

Any integer can be represented as a fixed-point number through the formula for unsigned integer conversion [3]

$$X = \sum_{n=0}^{N-1} x_n 2^n \tag{3.1.1}$$

where N is the number of bits and  $x_n$  is a boolean that is either present or not for the  $n^{th}$  symbol. This formula will not apply to negative numbers, as there is no way to determine the sign of this binary number.

There are two common ways of representing signed numbers as fixed-point numbers, with *Signed-Magnitude* and with *Two's Complement*. Signed-magnitude representation uses equation 3.1.1 to convert the absolute value of the integer, and adds another *most significant bit* (MSB) which represents the sign of the number. The benefit of this representation is a simplified prevention of overflows [3]. On the other hand, this representation makes it more expensive to perform additions, since the process will have to be split up depending on which number is largest [3].

When using two's complement to represent signed numbers, the conversion from integer is done with the following equation

$$X = \begin{cases} \sum_{n=0}^{N-2} x_n 2^n & X \ge 0\\ -2^{N-1} + 1 + \sum_{n=0}^{N-2} x_n 2^n & X < 0 \end{cases}$$

(3.1.2)

This representation has the advantage of being able to add several signed numbers within the N-bit range without having to handle overflow, as long as the final output does not result in overflow [3]. It should be mentioned that there are other, more task-optimized ways of representing digital numbers, although two's complement is the most common in digital signal processing (DSP) applications [3].

#### 3.1.1 Overflow

An issue when using fixed-point representation for hardware filter design is the concept of *dynamic range overflow*, which determines how large numbers the filter will need to handle as a worst case. The worst case dynamic range growth can be expressed as [3]

$$G \le \log_2 \sum_{k=0}^{L-1} |f[k]| \tag{3.1.3}$$

where f[k] is the  $k^{th}$  coefficient and L is the filter order. The total number of bits needed to represent the filter is then the sum of the input bit width and this growth factor. If this condition is upheld, no overflow will occur, regardless of which number representation is used. However, equation 3.1.3 is quite pessimistic, as there is only one single input combination which achieves this maximum growth in output size.

The maximum allowed input  $X_{max}$  for a given filter internal bit width in the can also be derived from the dynamic range growth, as seen in equation 3.1.4.

$$X_{max} = \pm \frac{2^{N-1}}{\sum_{k=0}^{L-1} |f[k]|}$$

(3.1.4)

To avoid the possibility of overflow,  $X_{max}$  should be less than the maximum possible input, determined by the bit width.

In larger filter systems, where several filters are cascaded together to form a steep filter, there will have to be some scaling of the bit width. The reason for this is that the bit width would grow to an unfeasible size if not handled. For example, if a filter system with five stages, an input precision of eight bit and coefficients of eight bit would to be connected together without scaling, the output of the filter would sum up to

$$W_{input} + 5 \cdot W_{coefficient} = 48 \, \text{bit}$$

(3.1.5)

To counter this problem, a scaling unit could be placed at each filter output. One way of achieving this in a fixed point system is to divide the signal by a constant factor, here called the *scalingfactor*. This will not cause distortion, but it will reduce the signal amplitude, which in turn allows for reducing the bit width of the signal.

# 3.2 Digital Signal Processing in an FPGA

The general signal processing techniques and challenges relevant for this thesis were presented in chapter 2. However, as this thesis is focused upon *digital* signal processing and the techniques presented in the previous chapter are directed at general signal processing, some additional challenges will surface when working with an FPGA.

## 3.2.1 Digital Mixing

As explained in section 2.3, the mixing process consists of multiplying the original signal with a time-varying signal, often a sine wave. In a digital system, this sine wave will have to be sampled in the same manner as the input signal, and stored in registers. This suggests that the same issues as the ones described in section 2.1 also applies to this signal.

Of course, this multiplicand signal could be sampled with a much better resolution than the input signal at compile time to reduce the quantization errors, but to store this signal in the FPGA would require a vast memory. One way of reducing this error is to use CORDIC-based algorithms [3]. The *Coordinate Rotation Digital Computer* (CORDIC) algorithm is a very common algorithm used in applications such as pocket calculators and DSP-systems. Its main function is to calculate efficient ways of minimizing the quantization error when representing a time-varying function [3]. The CORDIC-architecture is well suited for implementation in an FPGA, but in the case of signal mixing with a predefined signal, the multiplicand signal could simply be calculated in the design process with the help of for example CORDIC-based algorithms in Matlab.

Another, more hands-on method of reducing the size and error of the multiplicand signal is to carefully choose the mixing factor and sampling frequency. If a sine wave is used to mix the input signal, one can exploit the fact that a sine wave is periodical. This would suggest that if for example the LO frequency is set to 15 MHz and the sampling frequency is set to 30 MHz, the LO would only need two samples per period, 1 and -1 to perfectly represent the signal. Consequently, the logic needed to represent this mixer would be very efficient in hardware, as a multiplication with 1 could be replaced by wires, and a multiplication by -1 for two's complement signed numbers consists of an inversion and an addition with 1.

#### 3.2.2 FPGA Clocking

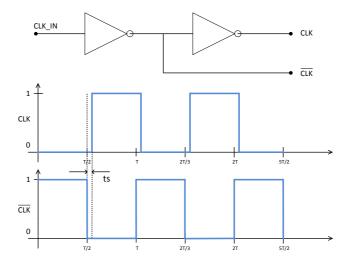

One of the fundamental differences between computer simulations and testing in an actual FPGA is the intricate timing in the physical system. Many digital systems employ a clock signal to coordinate the movement of data through the system [10]. This is called a synchronous design, and it is strictly necessary in for example digital FIR filters since all the time delay elements consists of clocked D-Flip Flops.

Figure 3.1: Clock Skew [10]

In a multistage FIR filter, stable timing is critical. An important issue with clocking in large systems is called *Clock Skew*. Clock Skew is where a clock signal is out of phase with the system reference [10]. This is a product of either long clocking paths, or from the clock signal propagating through logic with delay. This could for example be an inverter, which is common to use when synchronizing dataflow in cascaded logic. An example of clock skew in a circuit which generates an inverted clock signal can be seen in figure 3.1.

Clock skew can be reduced in several ways. Skew added as a result of long transmission paths within the FPGA can to some extent be reduced in the routing process. Timing-critical components can be grouped together, close to the clock source, and components which are communicating with each other can be placed close. Some modern synthesizer-tools have this option [3]. Also, many FPGAs have dedicated clock routing with low latency, which can be used to reduce clock skew. For example, Actels Antifuse FPGAs, including the RTAX2000S, lets the designer assign clock sources to a dedicated clock network which supports high fanout and minimal skew [11].

Clock skew due to delay in logic or clock generation can also be reduced by adding a *phase-locked loop* (PLL). The PLL is a component which detects differences in the signal phase between the clock source and the feedback from a given point in the delay line, and compensates for this difference at the source [10]. Many modern FPGAs have PLLs built in, and their outputs can be properly routed to dedicated clock hardware.

#### 3.2.3 FPGA and Space Qualification

One of the challenges facing FPGA-based designs for space applications is the limitations of the FPGA-technology. First off, the main difference between common FPGAs and space qualified FPGAs is the ability withstand significant radiation. The radiation affecting satellites is much stronger compared to the radiation experienced on earth. This means that random upsets, such as bit-inversion<sup>1</sup> in memory is prone to happen in digital electronics [12]. There are two common ways of countering this phenomena. The first method is to introduce error correction into the circuit, which checks each stored bit with majority voting at a given interval. This method costs both area, performance and energy. The other method of countering radiation is to build physically larger and more resilient FPGAs, which in turn means physically larger gates. This results in longer delays and lower performance, as well as reduced exploitable logical area.

Space-application FPGAs are often classified as either *radiation-tolerant* or *radiation-hard* [13]. Since space is a relatively new domain for FPGAs, the qualified devices with flight-heritage are sparse. Historically, Actel have been the sole supplier of radiation-hard FPGAs due to the high production cost and small market, but as the FPGA technology has developed and grown more popular, also major manufacturers such as Xilinx have started to develop suitable FPGAs. To be classified as a space-quality FPGA, the FPGA manufacturers needs to be classified with a qualified manufacturing line (QML) Class V with *radiation hardness assurance* (RHA) [13]. This implies, among other specifications, that the single event upset (SEU) limit should be above 37 *MeVcm*<sup>2</sup>/*mg*, and that the total ionizing dose (TID) should be tested for 300 krad for radiation-hard FPGAs and 100 krad for radiation-tolerant FPGAs. Actel's radiation-hard FPGAs are also equipped with *Triple Module Redundancy* (TMR), which means that each register cell in the FPGA has two

<sup>&</sup>lt;sup>1</sup>Bit-inversion is when a single bit is altered to the opposite value, hence a logic 1 becomes a logic 0, and a logic 0 becomes a logic 1.

other, equal master-slave clones [14]. These three cells acts as a single register cell to the user, but they can correct SEU-errors by using majority voting between themselves. If an error is detected in one of the cells, the majority value will be restored to all of the three cells.

Another important factor when choosing an FPGA for a space application is whether or not the FPGA has any flight heritage. Due to the fact that space hardware has a limited possibility of maintenance, the unit needs to work perfectly, all the time. Since failure is not an option, the safest bet for investors is usually the FPGA which already has proven it self stable in the field. A short list of radiation hardened, space qualified FPGAs which might be suitable for a large digital filter has been summarized in table 3.1 [14], [15]. In this table, the total ionizing dose is measured in krad, the single-event latch-up (SEL) immunity is given as  $MeVcm^2/mg4$  and the SEU is given as probability of upset/device/day in geostationary orbit.

| FPGA      | Size <sup>1</sup> | RAM [kB] | DSP Blocks | TID | SEL | SEU        | TMR |

|-----------|-------------------|----------|------------|-----|-----|------------|-----|

| RTAX2000S | 250000            | 288      | No         | 300 | 117 | $10^{-10}$ | Yes |

| RTAX4000S | 500000            | 540      | No         | 300 | 117 | $10^{-10}$ | Yes |

| Virtex4QV | 200448            | 6048     | 96         | 300 | 100 | $1.5^{-6}$ | No  |

Table 3.1: Space Qualified FPGAs

Note that the Xilinx Virtex4QV FPGA has less area than the Actel FPGAs. However, the Virtex FPGA has built in DSP-blocks, which can compensate for the lacking area. It should also be pointed out that the architecture of the Virtex FPGA is fundamentally different from the Actel FPGAs, as the Virtex FPGA uses a Look-up Table (LUT) architecture, rather than a *sea of modules* structure[14], [15].

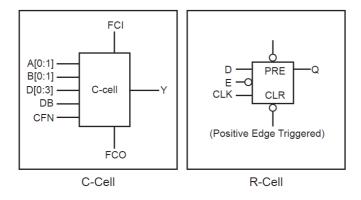

#### 3.2.4 FPGA Architecture

How the FPGA architecture is designed is highly dependent upon the manufacturer and what purpose the FPGA has. As explained in the previous section, space qualified FPGAs tend to be physically large to reduce the impact of radiation. Aside from this, there are several ways of organizing the synthesized logic inside the FPGA. In the Altera Axcelerator FPGA series, the modules are divided into *combinatiorial cells* (C-cells) and *register cells* (R-cells). These two building blocks can be used as a measurement of how much area the design will require of the FPGA. A *Register Transfer Level* (RTL) illustration of the different cells can be seen in figure 3.2.

## 3.3 Optimizing for Performance and Area

As mentioned in section 3.2.3, space qualified FPGAs are slow compared to the commercial FPGAs. In order to fulfill requirements in both area and performance, advanced synthesis and programming techniques must be utilized. In a multirate FIR filter several clock domains are used to act as the different sampling frequencies. This means that the

<sup>&</sup>lt;sup>1</sup>The sizes of the FPGAs are given as equivalent ASIC gates to the LUTs or C-/R-Cells

Figure 3.2: C-Cells and R-Cells in an RTAX2000S [14]

optimization focus will differ in each individual clock domain, since the slowest sampling frequency filters will not need to be compliant for the highest frequency domain. However, the lowest frequency-domain filter might be significantly larger than the highest frequency-domain filter. Consequently, the components with the highest clock frequency requirements should be optimized for performance, while the components with the lowest clock frequencies should be optimized for area, as long as they still satisfy the performance requirements.

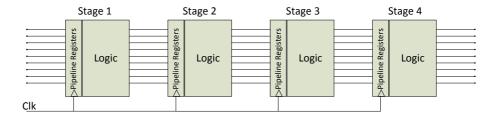

#### 3.3.1 Pipelining

A common performance optimization in sequential digital logic is based on trading area for performance. One way of achieving this is by dividing cascaded components into smaller sections separated with flip-flops, which allows for a faster system clock [10]. This technique is called *pipelining*. The frequency limit of a given cascaded datapath can be expressed as [10]

$$f < \frac{1}{t_{ff} + t_d + t_{su} + t_s} \tag{3.3.1}$$

where  $t_{ff}$  is the delay of the flip-flop,  $t_d$  is the delay through the combinatorial logic,  $t_{su}$  is the setup time and  $t_s$  is possible clock skew time. When using equation 3.3.1 for designs which contains slow and complex combinatorial logic, the factor  $t_d$  will be significantly dominant. In order to increase the throughput in such systems, pipelining can be used to divide the critical paths. To calculate the new frequency limit, equation 3.3.1 will now have to be used for the new, smaller datapaths separately. In the ideal case where a pipeline stage is added at  $t = t_d/2$ , and the remaining factors in equation 3.3.1 remains approximately constant, a frequency increase of up to 50% could be possible. An illustration of pipelining can be seen in figure 3.3.

Figure 3.3: Pipelining [10]

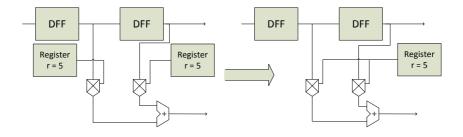

#### 3.3.2 Resource Sharing

One of the fundamental properties of the symmetric FIR filter is that coefficients are used twice<sup>1</sup> in the filter. However, in an FPGA with excessive potential performance this optimization can be extended to other logic blocks. By examining the coefficients of the filter one might see patterns which can be exploited to reduce area. The concept of resource sharing can be seen in figure 3.4.

In the case of figure 3.4, only one register is shared. Resource sharing can also be extended to include combinatorial logic as well. Depending on how the combinatorial logic is implemented in hardware, a multiplexer is often more efficient to implement than a multiplier, at least for large bit widths. For Actel, the architecture is based on multiplexers [16]. This means that in order to achieve an efficient physical synthesis, the design should also be based on multiplexers. One way of trading multipliers for multiplexers with resource sharing can be seen in figure 3.5. Note that in this design, timing is more critical than in the design from figure 3.4 due to the fact that a logic block will have to monitor and enforce sequentiality in the shared logic. Additionally, more registers are added to store the data before the final adder. However, these registers acts as pipelining on the critical path, shortening it by one adder. This will in turn increase the performance of the design, as discussed in section 3.3.1.

Figure 3.4: Resource Sharing Illustration

<sup>&</sup>lt;sup>1</sup>In odd-order symmetrical FIR filters, the center coefficient is used only once.

Figure 3.5: Resource Sharing, Continued

#### 3.3.3 Constant Input Multipliers

In a FIR-filter, all of the multipliers are based on the fact that one input is constant. Since the possible outputs from one multiplier with one constant input port is based on the range of the second input, the output values can be predicted when compiling, using either logic or memory. This is usually done in the synthesis process, and the designer does not need to handle it. The number of operations needed in the multiplier depends on the number of "ones" in the multiplicand. The reason for this is because the product of two *N*-bit numbers can be expressed as [3]

$$P = A \cdot X = \sum_{k=0}^{N-1} a_k 2^k X \tag{3.3.2}$$

where  $A = [a_0, \dots, a_{N-1}]$ . Equation 3.3.2 suggests that if A is constant for all values of X, and the number of non-zero elements in A is reduced, the complexity of the multiplication will also be reduced. For example if A is "11101",  $a_k$  will be non-zero for four instances of the summation, which results in four additions. Using two's complement number representation, A would here be -3. If the sign of A is inverted, A would be 3, or 00011 in two's complement. A would then only need two additions to complete the summation in equation 3.3.2. However, the product would now be -P rather than P.

One feature of the FIR filter structure is that a multiplication is always followed by an addition. This can be seen in the following pseudo code from a symmetric FIR filter:

```

SmallAdder <= X[N] + X[L-N];

Multiplier <= SmallAdder * Coefficient;</pre>

```

```

LargeAdder[N] <= LargeAdder[N-1] + Multiplier;</pre>

```

A trait of using two's complement number representation is that addition is equally computational complex for both positive and negative numbers [3]. Therefore, one can use the product -P instead of the original product P from the multiplier, and replace the adder with a subtracter. This can be achieved by introducing an inverter at one of the inputs of the adder. For numbers represented by many bits, this extra logic will be compensated by the reduction in multiplier logic.

To utilize the optimization described above, one can invert the constant FIR filter coefficient, given that this inversion leaves a coefficient where the majority of bits are zero. The filter behavior can now be described with the following pseudo code:

```

SmallAdder <= X[N] + X[L-N];

Multiplier <= SmallAdder * (-Coefficient);

LargeAdder[N] <= LargeAdder[N-1] - Multiplier;</pre>

```

# **Chapter 4**

# **Existing Analog Filter**

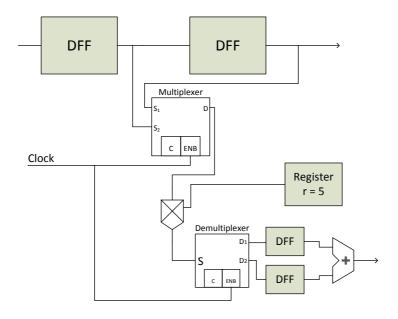

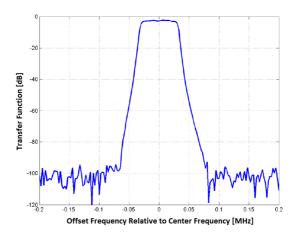

The current analog filter, which the proposed digital filter will replicate has the frequency response shown in figure 4.1. The filter is currently used in the Galileo Satellite Search and Rescue Transponder (SART). The purpose of the filter is to remove unwanted frequency components, such as noise and mixing products from the signal. The frequency modulated signal inside the passband of the filter can be located in one of several bands, defined by the specification for COSPAS-SARSAT 406 MHz distress beacons [17]. The signal information is irrelevant for this thesis, and it will therefore be treated as an isolated signal with a bandwidth of 100 kHz.

Figure 4.1: Current Filter Response

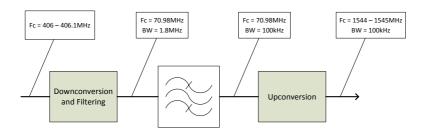

As previously mentioned, the filter is placed within the satellite SART unit. The basic functionality of the filter chain can be seen in figure 4.2. The actual input frequency of the SART, centered at 406 MHz - 406.1 MHz is mixed down to 70.98 MHz before it is received by this analog filter. The output of the SART is a bandpass filtered signal centered at around 1544 to 1545 MHz, in the *L-Band* [18], [19].

The expected frequency components of the filter from figure 4.1 can be seen in fig-

Figure 4.2: SART Converter Chain

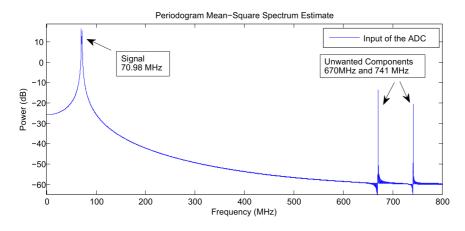

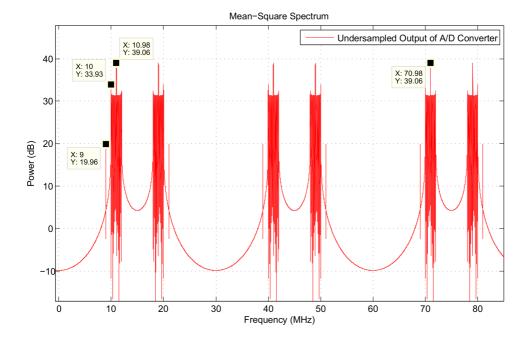

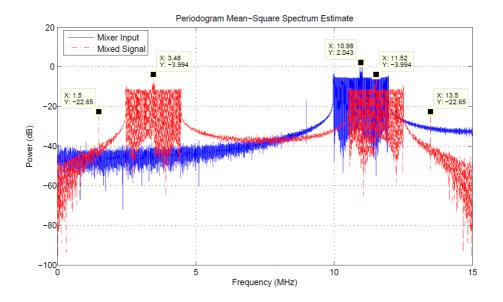

ure 4.3. As one can observe, there are three signal components in the input signal. The strongest component is the signal at 70.98 MHz, which is the passband of the signal filtered at the front end SAW filter of the receiver. This SAW filter has a bandwidth of approximately 1.8 MHz, while the relevant signal has a total bandwidth of 100 kHz. The frequency components in the signal are unwanted. These components are the result of a mixing process, where the IF signal, which is placed at 406 MHz is mixed with a local oscillator of 335 MHz. From the problem description in section 1.2 it was given that undesired frequency components were to be expected at 741 MHz and 670 MHz, with a bandwidth of 1.8 MHz.

Furthermore, the input signal noise outside the 1.8 MHz bandwidth is assumed to be wide band and uniformly distributed, and one can assume that the stopband of the preceding SAW filter is sufficiently attenuated.

Figure 4.3: Expected Input Frequency Placement

# Chapter 5

# **Methods and Tools**

To understand the signal processing techniques, and to efficiently design the filter coefficients, *MathWorks Matlab R2012a* was used. Matlab-scripts were created to simulate the DSP-components in detail, for increased insight in functionality and testability. The HDL version of the filters were designed with *Aldec Active-HDL Student Edition version 9.1*. Two *C++* based programs were created to ease the design of the symmetric FIR filters. The first program, called *prototypefilter.cpp* creates a rough version of a FIR filter, where all components are declared explicitly. This filter makes it easier to perform optimizations at the lowest level. The second program is more interactive, and the generated filters can be customized from a terminal window without recompiling. This program is called *generatefilter.cpp*. This script uses more efficient *generate* statements for component declarations. However, the program still unwraps the generate statements which creates the large adders, as these will be altered for area-optimizations in section 7.2.2. Both programs requires the filter coefficients being present in a separate file, called *coeff.txt*.

C++ was also used to create a script which generates testbenches for the VHDL Filters. Separate scripts were created for testing the individual filters, the filters with reusable logic described in section 7.2.1, the complete filter system and for the complete filter system with extra wires for probing.

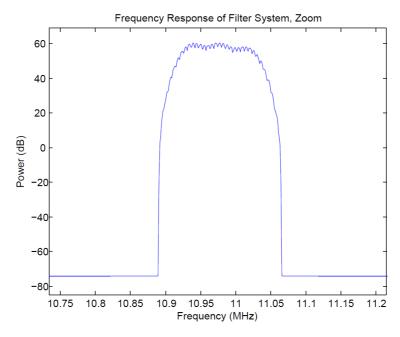

Digital simulations of the filters were performed in Active-HDL and *Mentor Modelsim SE-64 10.2. Synplify Premier with Design Planer E-2011.03-SP1* was used for HDL synthesis, to estimate and make sure that the design would satisfy the requirements in performance and area for the given FPGA. For FPGA-testing *Quartus II 30-bit 12.0 Web Edition* was used. This Quartus II installation used *SignalTap II Logic Analyzer* for communication with the FPGA. The FPGA was mounted on an Altera DE2-70 development board, and a *Terasic THDB-ADA* high speed ADC and *Digital to Analog Converter* (DAC) daughter card was mounted to the FPGA's *General Purpose Input/Output* (GPIO) interface.

All VHDL, Matlab and C++ code can be found in the enclosed zip-file.

# **Chapter 6**

# **Proposed Digital Filter**

As explained in section 2.2.1, a bandpass, linear phase FIR filter with transition bands of 50 kHz at each side, centered at 70.98 MHz would be infeasible to implement directly in any space qualified FPGA. When generating a symmetric FIR bandpass filter which fulfills the requirements from section 1.2 using Matlabs filter design software, the result is a filter consisting of 1685 stages. When synthesizing this filter in VHDL, using Synplify Premier, the specifications in table 6.1 are estimated. These results clearly states that this filter would not be possible to implement directly in the space qualified FPGAs discussed in section 3.2.3. Note that the no estimations were completed for the Virtex 4QV FPGA, as the Synplify Premier routing and fitting process failed as a result of the design size. The passband ripple of this filter was estimated to 1.8 dB.

| FPGA       | Combinatorial Cells | Register Cells | Clock Frequency |

|------------|---------------------|----------------|-----------------|

| RTAX2000S  | 587%                | 220%           | 27.3 MHz        |

| RTAX4000S  | 313%                | 117%           | 27.3 MHz        |

| Virtex 4QV | N/A                 | N/A            | N/A             |

Table 6.1: Direct Design of the Filter

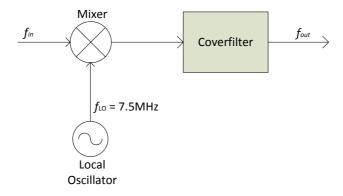

However, as explained in chapter 4, the input of the filter is a bandpass signal with a bandwidth of 1.8 MHz, and it could be assumed that the stopband is sufficiently attenuated by a preceding SAW filter. This suggests that the sampling techniques described in chapter 2 would be well suited for this application. To be safe, it is assumed that the input signal has a bandwidth of 2 MHz, and not 1.8 MHz. Hence, guard bands of 100 kHz are added to each side of the signal so that the digital filter will be more robust against imperfections in the preceding filter chain.

## 6.1 Initial Sampling, Mixer and Filter

Since the filtering will occur inside an FPGA, the analog signal would need to be sampled and quantized with an ADC. As specified in the problem description, the target FPGA for this filter should be space qualified, preferably an Actel RTAX2000S. This FPGA does not have any DSP blocks, meaning that all arithmetic components will be implemented as

logic, and no dedicated hardware will be used. This FPGA also has a limited performance, and the sampling frequency should be chosen accordingly. The sampling process should also move the center frequency towards dc.

The proposed ADC for this design should have an analog bandwidth above the highest frequency component of the signal, at 70.98 MHz + 1 MHz, but it should preferably also be lower than the mixing components at 670 MHz and 741 MHz. The output of the ADC should be able to handle a sufficient amount of bits so that the quantization noise discussed in chapter 2.1.2 will be kept to a minimum. An ADC which fulfills these requirements is the Texas Instruments ADS5463-SP, which is a space qualified 12-bit ADC with an analog bandwidth of 500 MHz [20]. The input voltage range of the ADC is  $2.2\,V_{pp}$ . It should be noted that there are several suitable alternatives to this ADC. According to equation 2.1.1, the step sizes of this ADC would be

$$\Delta = \frac{2.2 \,\text{V}}{2^{12} - 1} = 0.537 \,\text{mV} \tag{6.1.1}$$

and the quantization noise, according to equation 2.1.6

$$P_{n,rms} = \frac{0.537 \cdot 10^{-3}}{\sqrt{12}} = 1.55 \cdot 10^{-4} \,\text{W}$$

(6.1.2)

Using equation 2.1.11, the estimated SNR of the ADC output for a given rail to rail tone would be

$$SNR = 12 \cdot 6.02 \, dB + 1.76 \, dB = 74 \, dB$$

(6.1.3)

Note that the result from equation 6.1.3 is for ideal operation, with a perfect rail to rail tone. The datasheet for the ADC states an SNR of 65.3 dB relative to full scale (dBFS) [20].