## Efficient Ray Tracing of Sparse Voxel Octrees on an FPGA

Audun Wilhelmsen

Master of Science in Electronics Submission date: June 2012 Supervisor: Per Gunnar Kjeldsberg, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Statement**

Ray tracing is a method of generating images of 3D models. It involves tracing light rays in reverse, from a camera to light sources in the scene. Sparse Voxel Octrees (SVO) is a tree-based data structure used to store volumetric pixels. This structure can be used for 3D models and can be traversed efficiently, which makes it suitable for ray tracing. Recently there has been efforts to perform ray tracing of SVOs for the purpose of rendering real-time graphics. There exists pure software implementations and solutions based on general purpose graphics processing units.

Review the existing solution that implement this technique. Outline a design for a system that can accelerate this technique in dedicated hardware. Implement a unit that can traverse SVOs, a control unit which can schedule multiple traversal units and a cache and memory management that is optimized for the memory access pattern of the traversal units. Find and implement optimizations that can speed up rendering. Finally, explain how this system could be integrated with traditional graphics processing units in order to render images using both the proposed technique, and the traditional rendering technique. Discuss the possible challenges that will be encountered.

## Abstract

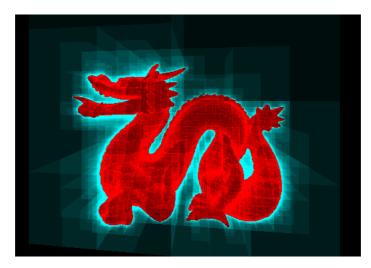

Ray tracing of sparse voxel octrees is a method of rendering images of 3D models, which could soon become practical for use in real time applications. This is desirable as ray tracing can produce very realistic visualizations, while voxel models can represent models with very fine geometric detail. For these reason the method has attracted significant attention in recent years, but no hardware solution has been published yet. This thesis presents a design of ray tracing of sparse voxel octrees in hardware. The objective is to show if it is sensible to implement the method in hardware, and if it could be integrated on modern GPUs alongside rasterization. To this end, the techniques used in existing software implementations of this method is reviewed, and an algorithm suitable for hardware implementation is presented. The problems of integrating the method with rasterization is explored, and the algorithm is analyzed and optimized to improve efficiency in hardware. A software implementation is presented, which supports the development of a hardware design. This design is implemented using the Verilog hardware description language, and it has been simulated and synthesized for an FPGA prototype. Multiple versions of the design has been synthesized and tested, and to evaluate the impact of design parameters the test results from these designs is presented. The thesis provides a comprehensive evaluation of the proposed design, and the results indicate that the algorithm is well suited for hardware implementation. Although real-time performance was not achieved, there are indications that further optimizations should allow real-time performance on the same platform, and that a full scale implementation on a modern GPU could probably allow ray tracing with a quality which is competitive with rasterization.

# Sammendrag

Ray tracing av sparse voxel octrees er en metode for å tegne bilder av 3D modeller, som snart kan bli praktisk for bruk i sanntidsapplikasjoner. Dette er ønskelig fordi rav tracing kan produsere veldig realistiske visualiseringer, mens voxel modeller kan representere modeller med veldig mye geometriske detaljer. Av disse årsakene har metoden fått betydelig oppmerksomhet de siste årene, men ingen hardwareløsning har vært publisert enda. Denne oppgaven presenterer et design for ray tracing av sparse voxel octrees. Hensikten er å vise om det er fornuftig å implementere metoden i hardware, og om den kan integreres ved siden av rasterisering på en GPU. Derfor blir teknikkene som har vært brukt i eksisterende softwareløsninger gjennomgått, og en algoritme som er passelig for å implementeres i hardware presenteres. Problemene med å integrere metoden med rasterisering har blitt undersøkt, og algoritmen analyseres og optimaliseres for å forbedre ytelsen i hardware. En software implementering presenteres, som underbygger utviklingen at et hardwaredesign. Dette designet implementeres i hardware språket Verilog, og har blitt simulate og syntetisert for en FPGA prototype. Flere versjoner av designet har blitt syntentisert og testet, og for å evaluere påvirkningen av designparametere blir disse resultatene presentert. Oppgaven gir en omfattende evaluering av det foreslåtte designet, og resultatene indikerer at algoritmen er egnet for implementering i hardware. Selv om sanntidsytelse ikke ble oppnådd, er det indikasjoner på at videre optimaliseringen vil kunne føre til sanntidsytelse på samme platform, og at en fullstending implementering på en moderne GPU sannsynligvis vil tillate ray tracing med kvalitet som er konkurransedyktig med rasterisering.

# Preface

Computer graphics has always fascinated me, and I have found it highly motivating to work with. A couple of years ago I stumbled over an interview with the co-found and technical director of id Software, John Carmack. In it he commented, "there is a very strong possibility, as we move towards next generation technologies, for a ray tracing architecture that [...] involves ray tracing into a sparse voxel octree". Ray tracing is a very enticing form of rendering, because it closely mimics the nature of light. It can be fun to work with because it is easy to get realistic results, but it is hard to make it fast. In April 2010 I e-mailed him asking whether implementing this on an FPGA would be a good idea. To my surprise he replied: "I have actually thought specifically about this – much of the work would be very amenable to an FPGA implementation in a far more efficient manner than when implemented on general purpose hardware.". This has served as a huge source of motivation while working on this thesis.

This project is a testament to the value and maturity of the open source hardware design community. I am confident that open source hardware will become increasingly influential in the coming years.

I am grateful to everyone who has contributed to the ORPSoC project, which has been an invaluable platform in this thesis. I am in particular very grateful for the work done by Stefan Kristiansson who ported ORPSoC to the Atlys prototype board I have been using in this thesis. Without it I would surely have spent a lot of time on work that is not directly relevant to the problems I wanted to explore. It is also amazing the extent of support I received through the members of the ORPSoC IRC chat channel.

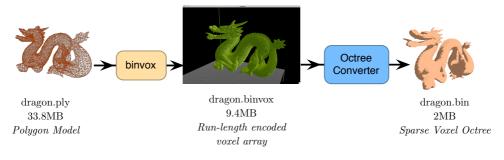

Chris McClelland's "FPGALink" project was also an important tool in simplifying the development process. It enabled me to write software which could communicate directly with the FPGA over a USB link. He was also extremely helpful in ironing out issues related to the use of this software. Other tools which have contributed to this thesis are "binvox" by Patrick Min and the "vmath" vector library by Jan Bartipan

My supervisor has been Per Gunnar Kjeldsberg (Department of Electronics and Telecommunications, NTNU, Trondheim). He has given me some absolutely essential advice on being focused and making the right decisions with regards to the scope of the thesis. More importantly, he has given precious encouragement by showing genuine enthusiasm for the value of my work.

I would also like to thank my friends in Trondheim who made the time I've spent in this

city the best years of my life, and helped me maintain a healthy balance between work and play.

This thesis is dedicated to my grandparents, Arthur and Irene Saunes, who let me stay with them during the last stretch of the thesis. They gave me the perfect environment to concentrate on my work which gave me some very productive weeks while I was there.

# Contents

| Pı           | roblem Statement               | i         |

|--------------|--------------------------------|-----------|

| $\mathbf{A}$ | bstract                        | iii       |

| Sa           | nmendrag                       | v         |

| Pı           | reface                         | vii       |

| Co           | ontents                        | x         |

| 1            | Introduction                   | 1         |

| 2            | Background                     | 3         |

|              | 2.1 Models                     | 3         |

|              | 2.2 Transforms                 | 4         |

|              | 2.3 Perspective Projection     | 5         |

|              | 2.4 Rasterization              | 5         |

|              | 2.5 Z-buffer                   | 6         |

|              | 2.6 Ray tracing                | 6         |

|              | 2.7 Space Partitioning         | 8         |

|              | 2.8 Sparse Voxel Octree        | 8         |

|              | 2.9 Traversal of Voxel Octrees | 9         |

|              | 2.10 Representation of Numbers | 10        |

|              | 2.11 Data Cache                | 12        |

|              | 2.12 FPGA                      | 13        |

|              | 2.13 ORPSoC                    | 13        |

|              | 2.14 Digilent Atlys            | 14        |

| 3            | Previous Work                  | 17        |

|              | 3.1 Software Implementations   | 17        |

|              | 3.2 GPU Implementations        | 17        |

|              | 3.3 Ray Tracing in Hardware    | 18        |

|              | 3.4 Data Structures            | 19        |

| 4            | An Algorithm for SVO Traversal | <b>21</b> |

|              | 4.1 Overview                   | 21        |

|              | 4.2 Parameters                 | 22        |

|              | <ul> <li>4.3 Child Nodes</li></ul>                        | 25        |  |  |  |  |

|--------------|-----------------------------------------------------------|-----------|--|--|--|--|

| 5            | A Ray Tracer Geometry Stage<br>5.1 Normalizing the Octree | 29        |  |  |  |  |

|              | 5.2 Generating Primary Rays                               | 30        |  |  |  |  |

|              | 5.3 Inverse Perspective Projection                        | 31        |  |  |  |  |

|              | 5.4 Normalizing Ray Length                                |           |  |  |  |  |

|              | 5.5 Z-Buffering With Ray Tracing                          |           |  |  |  |  |

| 6            | Hardware Optimizations                                    | 33        |  |  |  |  |

|              | 6.1 Floating Point vs Fixed Point                         |           |  |  |  |  |

|              | 6.2 The Decimal Point                                     |           |  |  |  |  |

|              | 6.3 Stack                                                 |           |  |  |  |  |

|              | 6.4 Restarting                                            |           |  |  |  |  |

|              | 6.5 Hardware Optimized Algorithm                          | 37        |  |  |  |  |

| 7            | Software Implementation                                   | 41        |  |  |  |  |

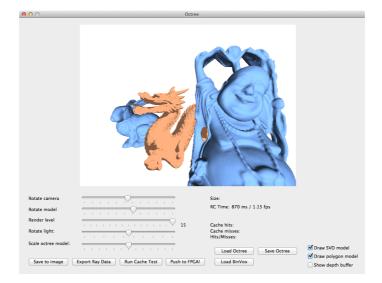

|              | 7.1 SVO Data Structure                                    |           |  |  |  |  |

|              | 7.2 Generating Sparse Voxel Octrees                       |           |  |  |  |  |

|              | 7.3 Software Ray Tracer                                   |           |  |  |  |  |

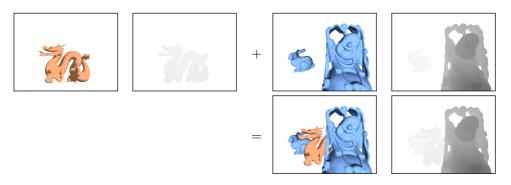

|              | 7.4 Merging Ray Tracing and Rasterization                 |           |  |  |  |  |

|              | 7.5 Cache Profiling                                       |           |  |  |  |  |

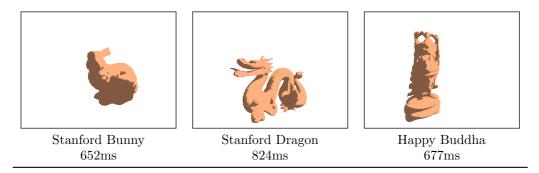

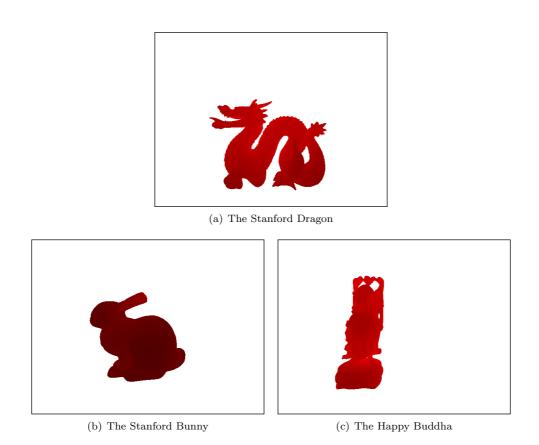

|              | 7.6 Results                                               | 46        |  |  |  |  |

|              | 7.7 Discussion                                            | 47        |  |  |  |  |

| 8            | Hardware Implementation                                   | 49        |  |  |  |  |

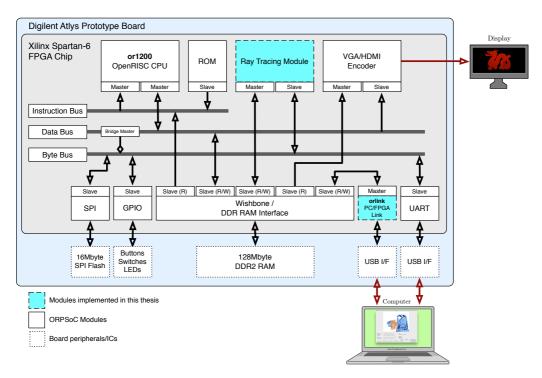

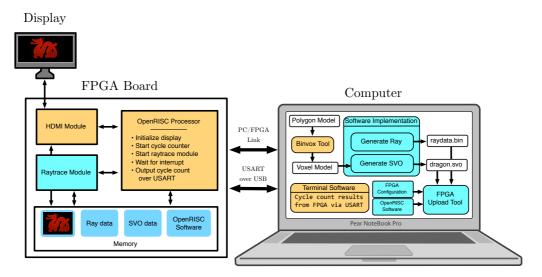

|              | 8.1 Hardware Platform                                     | 49        |  |  |  |  |

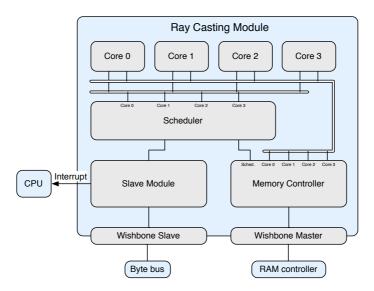

|              | 8.2 Ray Casting Module                                    | 51        |  |  |  |  |

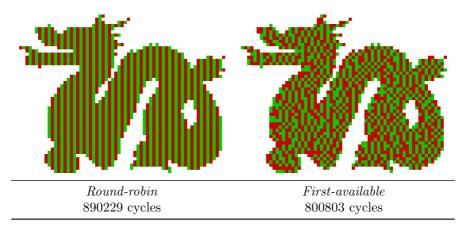

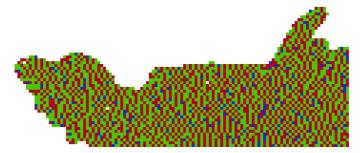

|              | 8.3 Scheduler                                             |           |  |  |  |  |

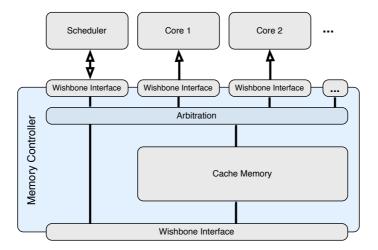

|              | 8.4 Memory Controller                                     |           |  |  |  |  |

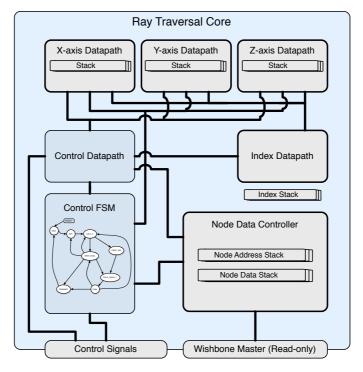

|              | 8.5 Ray Traversal Core                                    |           |  |  |  |  |

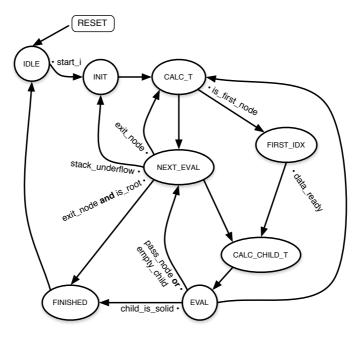

|              | 8.6 Core State Machine                                    |           |  |  |  |  |

|              |                                                           |           |  |  |  |  |

|              | 8.7 Testing                                               |           |  |  |  |  |

|              | 8.8 Results                                               |           |  |  |  |  |

|              | 8.9 Discussion                                            | 64        |  |  |  |  |

| 9            | Conclusions                                               | 67        |  |  |  |  |

|              | 9.1 Future Work                                           | 68        |  |  |  |  |

| Bi           | bliography                                                | <b>74</b> |  |  |  |  |

| $\mathbf{A}$ | Attached Files 75                                         |           |  |  |  |  |

| в            | B The Software Ray Tracing Core Functions 76              |           |  |  |  |  |

| $\mathbf{C}$ | C The Ray Tracing Core Module 82                          |           |  |  |  |  |

## Chapter 1

# Introduction

Ray tracing of sparse voxel octrees (SVO) is a method for rendering images of three dimensional models. It has a wide range of potential applications; medical imaging[31], visualization of scientific data[23], video production[9, 6] and real-time graphics[29, 10, 56]. This thesis will outline a practical design for ray tracing of SVOs in hardware.

This method has had some attention in recent years, and there are currently several implementations of real-time ray tracing of SVO in software[29, 10, 42, 56]. There are also a few implementations of a somewhat similar technique, ray tracing of polygon models, in hardware[43, 64]. Although some algorithms for ray tracing of SVOs seem to be particularly suited for hardware implementation, there seems to have been no such attempt yet.

Making hardware optimized for a specific domain, such as medical imaging, can be prohibitively expensive. Technology is often developed and popularized within a consumer market before being adopted in another domain. Consider the massively parallel general purpose graphics processor units (GPGPUs). These are now being used to process e.g., scientific and medical data[22], and NVIDIA is producing versions of their GPGPUs specifically for this market[62, 34]. However, these processors grew out graphics cards for the consumer gaming industry.

Similarly, this thesis will present a hardware implementation which could conceivably be integrated in a graphics processing units (GPUs) for consumer games, with the understanding that this might be the most practical path for developing hardware that can be used within other domains as well. It should be noted that one can not expect this method to supplant the established method of rendering graphics for consumer games: rasterization. There is a large investment in rasterization in terms of toolchains, rendering engines and knowledge. For ray tracing of sparse voxel octrees to gain popularity within games, it must be implemented alongside rasterization, and it should be possible to use it within the same rendering pipeline. This way the method can initially be used for special effects, and over time gain more uses as the capabilities of the hardware grows and the mind share of the method increases. Consequently, a practical architecture for raytracing of SVOs should be as compatible with rasterization as possible. Using sparse voxel octrees to represent 3D models is a logical evolution of virtual texturing techniques which have been developed recenty[57, 19, 18]. They can allow full freedom to define the shape and texture of the models, in addition to being a potentially more efficient way to store the color and geometry data[47]. More importantly, these structures can be ray traced efficiently[29, 10]. Although ray tracing is generally slower than rasterization, ray tracing is a much more accurate model of how light behaves, and can enable effects like accurate reflections, detailed shadows and ambient occlusion[9]. There is also a benefit to developers as expression visual effects with rays of light is more natural and easy to deal with than the tricks that rasterization employ[48]. As hardware becomes faster, as demand for more realistic graphics grows, and as algorithms for ray tracing become more developed, there may soon come a time when using ray tracing for real-time computer games is feasible. This is effectively demonstrated by Schmittler and Pohls work of converting existing games to use ray tracing[44].

Field-programmable gate arrays (FPGAs) allow designs for digital integrated circuit hardware to be prototyped and tested at a price which is several orders of magnitude cheaper than making application-specific integrated circuits (ASICs). This thesis uses an FPGA prototype platform with the intention of presenting a design that could later be integrated on an ASIC. Although there are additional challenges to putting a design on an ASIC, an FPGA prototype should solve many of the initial problems.

In this thesis an algorithm for ray tracing of SVOs has been chosen and analyzed. A software implementation has been made to produce reference renderings and behavioral simulations, which provide data relevant to a hardware implementation. The software has also been used to evaluate techniques to combine rasterization and ray tracing based rendering. A hardware module which implements the algorithm has been described in the hardware description language Verilog. This module has been simulated, integrated in a system-on-chip solution for an FPGA, and several variations of the design has been synthesized, tested and benchmarked. This has provided useful data on the impact of various design parameters.

Chapter 2 presents the background material for the thesis. Topics related to rasterization, ray tracing, sparse voxel octrees, caching techniques and FPGAs are covered. Chapter 3 presents previous work which is related to the thesis, and these have been categorized into work related to software-based ray tracing of SVOs, other forms of ray tracing in hardware and work on sparse voxel octree data structures. Chapter 4 presents and explains an existing algorithm for ray tracing of SVOs, which serves as a good basis for a hardware implementation. Chapter 5 discusses some challenges related to integrating ray tracing and rasterization and presents some solutions which should lead to an architecture that makes it easier to combine the two techniques. Chapter 6 presents analysis of aspects of the algorithm which is significant to a hardware implementation, and modifications to the algorithm that make it feasible to implement it in hardware. Chapter 7 describes the software implementation of the hardware optimized algorithm and discusses the results this produced. Chapter 8 describes a hardware implementation, the methodology for testing the resulting design and discusses the results from these tests. Chapter 9 discusses the conclusions drawn from this thesis and future work necessary to reach a comprehensive and practical design for ray tracing of SVOs in hardware.

## Chapter 2

## Background

### 2.1 Models

In 3D computer graphics, we usually want to visualize real world objects. These objects must necessarily be represented in the computer by some kind of *model*. We use a data structure or a mathematical model to represent these objects. A common way to model objects is using *polygon models*. These are constructed from sheets of polygons. The polygons themselves are usually subdvided into triangles, which can be represented by three points. A normal vector is often also included, which is useful to indicate which side of the triangle is facing outwards, and how light should behave on it.

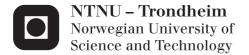

Figure 2.1: A triangle based (left) and a voxel based (right) model.

Another way to represent models is through voxels. Voxels are to 3D models what pixels are to 2D images. You represent the space as a uniform collection of points, and you store parameters for each of these points. The parameters can be a color value and normal vector of the voxel. Voxels can be drawn as points, circles or more commonly cubes. Although the cubes result in aliased hard edges, these can be softened through adaptive blurring techniques[29].

Given a type of model (polygons or voxels), there can be many different ways to render that model to a 2D image. Rendering algorithms are usually optimized for one type of model. Rasterization is optimized for polygon models, and the algorithm presented in this thesis is optimized for voxel models.

## 2.2 Transforms

Transforms are essential tools in computer graphics[3]. It takes an entity and moves, rotates, scales or performs any other kind of geometrical conversion. They are useful for positioning objects in the scene, moving cameras and lights, etc. The most useful transforms are linear transforms. These can be represented as a matrix. In computer graphics points, vectors and colors are usually represented as a 4-component vector. For points and vectors these represent the x, y and z-axis, with the fourth component (w) usually being set to 1. The w-component is useful if a transform needs to add a constant to a component. Any combination of linear transforms can then be applied using a 4x4 matrix.

**Model transform** Models are defined within their own coordinate systems. But to model a scene with several different models in it, the models must be positioned in a common coordinate system, the *world space*. A model of a teapot could be centered in the origo of its coordinate system, and the nose could point along the z-direction. The model transform for the tea-pot could then for instance rotate it around the y-axis to point at an angle  $\theta$  and position it at the coordinate (10,0,20). The matrix for this example is illustrated below, with **p** and **q** being a vector before and after transformation.

$$M = \begin{bmatrix} \cos\theta & 0 & \sin\theta & 0\\ 0 & 1 & 0 & 0\\ -\sin\theta & 0 & \cos\theta & 0\\ 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 10\\ 0 & 1 & 0 & 0\\ 0 & 0 & 1 & 20\\ 0 & 0 & 0 & 1 \end{bmatrix}$$

(2.1)

$$\mathbf{q} = M\mathbf{p} \tag{2.2}$$

**View transform** The coordinate system of the world space is usually defined in an intuitively useful manner. The ground could for instance be defined to be parallel to the X-Z plane. A virtual camera could be positioned freely in this space. For rendering algorithms however, it is useful to have the camera positioned in the origo of the coordinate system with the camera looking along the z-axis. The view transform transforms the scene from the world space to the camera space (or eye space). The model and view transform can be combined in a single model-view matrix.

**Projection transform** A projection transform maps the visible parts of the scene to some *canonical view volume*, a simple axis aligned cube with corners at e.g., (-1, -1, -1) and (1, 1, 1). The nearest visible objects are mapped to the *near plane* (z = -1). The furthest visible objects are mapped to the *far plane* (z = 1). Similarly there is a top, bottom, left and right plane[3]. Anything outside these planes is outside the view of the camera, and should be ignored.

## 2.3 Perspective Projection

A perspective projection is a projection which closely match how we perceive the world: objects gets smaller as they get further away, and larger when they come closer. Consequently in scene space, the *far plane* is larger than the *near plane*, while in the canonical view volume they are equally big. This projection is represented by the following transform matrix[3] (for the OpenGL API), where position of the near, far, left, right, bottom and top planes are denoted respectively n, f, l, r, b and t:

$$\mathbf{P}_{p} = \begin{pmatrix} \frac{2n}{r-l} & 0 & \frac{r+l}{r-l} & 0\\ 0 & \frac{2n}{t-b} & \frac{t+b}{t-b} & 0\\ 0 & 0 & -\frac{f+n}{f-n} & -\frac{2fn}{f-n}\\ 0 & 0 & -1 & 0 \end{pmatrix}$$

(2.3)

After this matrix is applied, the resulting vector must be divided by its *w*-component to complete the perspective transform. The *w*-component has in other words been used to temporarily store a value which is a linear function of the other components, and all components will be divided by this value. I.e., to get from a view space point  $\mathbf{q}$  to a canonical view space point  $\mathbf{v}$ :

$$\mathbf{v}' = \mathbf{P}_p \mathbf{q}$$

$$\mathbf{v} = \mathbf{v}' / \mathbf{v}'_w \tag{2.4}$$

## 2.4 Rasterization

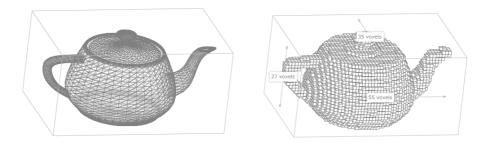

The most popular form of 3D rendering today is rasterization of polygon models, or just rasterization for short[59]. It is the technique used by virtually all commercial GPUs. The process of rasterization can be divided into a pipeline. The three conceptual stages of the pipeline is the *application, geometry and rasterizer stages*[3]. The application stage is defined by the developer and runs on the CPU, it runs simulations and provides the models, textures, data and other parameters for the following stages in the pipeline. The task of the geometry stage is to apply transforms and effects that work on the geometry of the models, and eventually ending up with triangles mapped to a surface that represents the screen. The triangles are passed on to the rasterizer stage. This stage iterates through all the given triangles, and generates *fragments* for every pixel the triangle covers. These fragments can be further processed by a *pixel shader*, a small program that applies perpixel visual effects. Finally the fragments for each pixel is merged, producing a single color-value for that pixel.

Figure 2.3 illustrates in further detail how the geometry stage works. The model transforms positions different models in a common coordinate system. The view transform positions the camera in the origo, and points it along the z-axis. The perspective transform maps the part of the world which is visible to the camera to a canonical view volume. Anything that is outside this volume is discarded. The geometry is then passed on to the rasterizer which is responsible for drawing each triangle.

Figure 2.2: A typical GPU pipeline[3]

Figure 2.3: The geometry stage in action

## 2.5 Z-buffer

When drawing a fragment, it must be possible to determine whether the fragment should be drawn in front of or behind those that were drawn before. This is usually accomplished using a Z-buffer (or depth buffer)[3]. When drawing a fragment of a triangle to a pixel in the image, the z-coordinate (in the canonical view volume) of the fragment is stored in the Z-buffer. If the z-coordinate of the fragment is larger than the one in the buffer, we know that the fragment is behind those that were drawn before, and should not be drawn to the image.

One thing which is important to note about the Z-buffer, is that when using a perspective transform, the value stored in the buffer is not proportional to the distance of the camera to the fragment. The z-coordinate in the canonical view volume is derived from Equation 2.4. It can be shown that this implies that the z-coordinate in the canonical view volume is a function of  $1/z_c$ , where  $z_c$  is the z-coordinate in the camera space.

## 2.6 Ray tracing

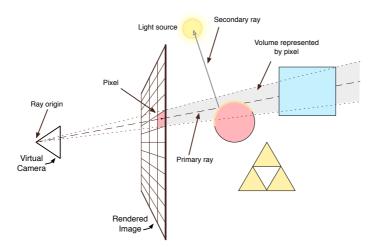

Ray tracing is a method which generates 3D images by tracing the path of a ray of light in reverse. A virtual camera is defined, with a location and direction. From this camera, rays are traced in to a scene (a collection of objects we want to render). These rays

Figure 2.4: An image of the Stanford bunny and a buddha statue, and its Z-buffer. Whiter intensity implies further distance from camera. The background has been colored green to allow the bunny to stand out.

represent the pixels on the resulting image. Ideally, a pixel represents a volume in the space as seen in Figure 2.5. Accurately rendering this would be too expensive, but the pixel can be approximated by a ray instead. This will result in anti-aliasing issues, so it is common to average the colors of several rays to find the color of a pixel[14].

Figure 2.5: Ray tracing

The rays going from the camera to the objects in the scene are called *primary rays*. After a primary ray hits an object, additional rays can be sent out. These can be used to find whether the point is in a shadow or not, by tracing a ray to the light sources in the scene. They can also be used to calculate reflections and refractions on the object, allowing us to draw accurate transparent objects such as glass or water. These rays are often called secondary rays.

Any geometrical construct for which a ray-object intersection test can be formulated, can be rendered using ray tracing. The ray can fundamentally be described using Equation 2.5. The ray has an origin **o** and a direction vector **d**. t can be considered a virtual time parameter, and **p** a position along the ray at different times. In these terms ray tracing is the problem of finding the values t where the ray intersect objects.

$$\mathbf{p}(t) = \mathbf{o} + t \cdot \mathbf{d} \tag{2.5}$$

This equation can for instance be solved for the equation of a perfect sphere, which is commonly used to demonstrate simple ray tracers. Equation 2.5 can also be solved for a triangle[14], making it possible to ray trace polygon models. A naive implementation of this would do an intersection test on every triangle in the model for every pixel in the screen, making the algorithm very slow. To optimize ray tracing, a space partitioning data structure is often used. Instead of testing every primitive, one performs a search of this data structure instead to find a set of primitives the ray could intersect. Therefore, ray tracing is cited as having the advantage over rasterization in that performance depends logarithmically, not linearly, on geometric complexity[25]. Although it should be mentioned that level-of-detail (LOD) based techniques to achieve similar performance scaling exists for rasterization[20].

### 2.7 Space Partitioning

Space partitioning is a method where a given space is divided into smaller non-overlapping spaces. These sub-spaces can be arranged in a hierarchical tree, where each sub-space can be divided into further partitions. This results in a nonuniform spatial subdivision[14]. Space partitioning data structures is often used in computer games to accelerate certain operations. In rasterization, it can used to exclude regions of polygons that will not be rendered (occlusing culling[7]), or to sort objects by depth, which is important for certain visual effects[3]. For these purposes, the BSP/kd-tree structures have been found to be better than octrees[55]. Although kd-trees have been used for ray tracing voxel data[52], sparse voxel octrees seem particularly suited for this purpose because they can be traced by a remarkably simple algorithm which will be presented in a later chapter.

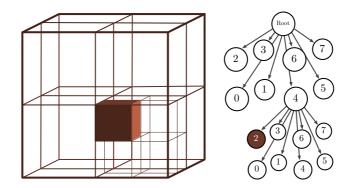

## 2.8 Sparse Voxel Octree

An octree is a hierarchical space-partitioning data structure [41] where a space is divided in eight equal sub-regions, or *octants*, and where each octant that contains objects is further divided until the resulting tree reaches a desired height. A voxel is a volumetric pixel, in other words, an axis-aligned rectangular prism [14]. A sparse voxel octree is a data structure used to store a voxel model when most of the voxels are empty (the space is "sparse"). In visualization of real-world objects, this would be the case, as all the voxels exists on the surface of objects.

Often, when using a space-partitioning data structure, a list of objects is stored in the leaf nodes. In a sparse voxel octree the leaf node is a voxel, either an empty space or a solid cube. A solid voxel may have a color value. For an inner node, we can take the

Figure 2.6: An octree with 2 levels and a single solid voxel

average color of all the child nodes, and attach it to this node. Doing so means the scene represented by the tree can be rendered at varying resolutions, depending on how deep we traverse. This is desirable because it is a waste to render objects that are far away with high detail. Furthermore, we can even avoid loading into memory those parts of the tree that represent high detail in far away parts of the scene, and stream them into memory as the camera moves towards those areas[10].

## 2.9 Traversal of Voxel Octrees

A variety of algorithms to traverse space partitions have been described in the literature. They have different complexities, and they can have very different performance on a given computer architecture. A significant attribute of the algorithms are whether they use a stack or not. A stack is useful for keeping track of the path taken as the tree is traversed, but can be detrimental on certain architectures. The following are descriptions of a few of the most common methods.

**Restart** The simplest methods are those based on the kd-restart algorithm. This is a stack-less algorithm: A starting point, the ray origin, is chosen. The tree is traversed until the voxel representing this point is found. If the voxel represented by the node is empty, the point is moved to where the ray exits the voxel. The algorithm then restarts from the new point. In other words, the algorithm traverses one octant at a time, and has to descend the tree from the root node down every iteration. This is repeated until a collision is found, or the ray exits the voxel represented by the root node.

**Backtrack** Backtracking algorithms (or *push-down optimization* [21]) are similar to kdrestart. But it exploits the fact that we can keep track of the last node which must be parent to all the nodes traversed by the ray. It is a simple optimization than can provide a performance boost. But the parent node might be close to the root, which can make the gain minimal in some iterations. It only eliminates traversal steps near the top of the tree, which are the ones that are most shared by neighboring primary rays [21].

#### Chapter 2 Background

**Full stack** A tree traversal algorithm can use a stack to keep track of the nodes visited as the algorithm descends the tree. The algorithms utilizing a stack is similar to the restarting algorithms when descending the tree, but will push the traversal state to a stack for each node. If an empty space is found, the stack is unwounded until it finds the next node the ray intersects. The descent can continue as usual from that point. In this thesis the algorithms using a stack as deep as the tree the algorithm was designed for is referred to as *full stack* algorithms, to distinguish them from *short stack* algorithms.

**Short stack** Sometimes a full stack can be too expensive to implement. In GPGPU implementations, the processing cores are often not optimized for the memory access pattern required by the stack. An alternative is to keep the state for the last  $N_s$  nodes traversed. If the stack is exhausted (a stack underflow), the algorithm can perform a restart.

The restarting algorithms can be considered a special case of a short stack with  $N_s = 0$ . Similarly, a full stack can be considered a special case with  $N_s = N_t$  where  $N_t$  is the depth of the octree. Even if an algorithm is designed with a full stack, it could be wise to support restarts, as it will allow the algorithm to support octrees deeper than it was originally designed for.

**Bottom up methods** Revelles et al. [41] describes bottom-up methods as those starting at the first terminal node intersected by the ray. The algorithm must then find the neighboring nodes by some method. Some algorithms use neighbor pointers in the octree[15], which are pointers stored in the leaf nodes, pointing to the neighboring nodes at each face of its voxel. This enables the algorithm to jump between nodes without ascending the tree. It can improve traversal speed, but at a significant memory cost, as the additional pointers have to be stored in the octree.

### 2.10 Representation of Numbers

There are several ways to represent numbers. For performing calculations, the two most popular schemes are probably fixed point and floating point representations. They both have strength and weaknesses.

**Fixed point numbers** The *fixed point* format is named so because the decimal point is fixed in one place. Equation 2.6 shows the number 5.625 represented in binary fixed-point, with three bits for the integer and fractional part, or a total of six bits.

$$101.101 1 \cdot 2^{2} + 0 \cdot 2^{1} + 1 \cdot 2^{0} + 1 \cdot 2^{-1} + 0 \cdot 2^{-2} + 1 \cdot 2^{-3}$$

(2.6)

The position of the decimal point must be chosen carefully. It will determine what range of numbers can be represented, and how accurately they can be represented. Given N

number of integer bits, and a two's complement representation, the range of integers is  $-2^{N-1}$  to  $2^{N-1} - 1$ . Given M number of fractional bits, the smallest fraction that can be represented is  $2^{-M}$ .

Fixed point numbers are relatively cheap to implement in hardware. Table 2.1 shows the resource use of a 32 bit adder/subtract unit and a 32 bit multiplier unit, as estimated by the Xilinx Core Generator tool[67, 65].

| FPGA      | Operation         | LUTs | $\mathbf{FF}$ | Latency | DSPs                                       | Max Clock Freq. |

|-----------|-------------------|------|---------------|---------|--------------------------------------------|-----------------|

| Virtex-5  | Add/Subtract      | 70   | 91            | 3       | $\begin{array}{c} 0 \\ 0 \\ 4 \end{array}$ | 410Mhz          |

| Virtex-5  | Add/Subtract      | 32   | 32            | 0       |                                            | 388Mhz          |

| Spartan-6 | Multiplier(35x35) | 58   | 107           | 8       |                                            | 250Mhz          |

Table 2.1: Resource use of fixed point operations [67, 65]

Floating point numbers Floating point numbers are similar to scientific notation; it represents numbers of the form  $m \cdot 2^{e-b}$ . A standard for floating point representation called IEEE 754[1] is now used almost exclusively in digital computing platforms[24]. The numbers are stored as a mantissa, m, and an exponent, e. The exponent is offset by a constant bias, b. A sign bit, S, indicates whether the number is positive or negative. Floating point numbers provide a much larger dynamic range than fixed point numbers given the same amount of bits. That is, it is possible to represent both very large and very small numbers in the same representational system. This has several benefits over fixed point numbers, one being that the programmer or hardware designer does not have to worry as much about overflowing the boundaries of the representation. Floating point numbers are essential in modern GPUs, and a modern high-end GPU can perform over 1000 billion floating point operations per second[60]. Table 2.2 shows the estimated resource use for single precision (32 bit) floating point numbers[66]. Comparing to Table 2.1, we see that floating point numbers are significantly more expensive to implement.

| 31           | 30 | 23       | 22 0     |   |

|--------------|----|----------|----------|---|

| $\mathbf{S}$ |    | Exponent | Mantissa | ] |

Figure 2.7: Bit organization of single precision (32 bit) IEEE 754 floating point representation[1].

| FPGA      | Operation    | LUTs | $\mathbf{FF}$ | Latency | DSPs | Max Clock Freq.    |

|-----------|--------------|------|---------------|---------|------|--------------------|

| Virtex-5  | Add/Subtract | 432  | 558           | 12      | 0    | 420Mhz             |

| Virtex-5  | Add/Subtract | 388  | 76            | 2       | 0    | 110 Mhz            |

| Spartan-6 | Multiplier   | 140  | 187           | 8       | 0    | $150 \mathrm{Mhz}$ |

Table 2.2: Resource use of floating point operations[66]

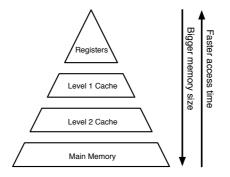

## 2.11 Data Cache

Processors can perform operations on its internal registers significantly faster than it can access its main memory. For modern systems the cost of accessing main memory can be about 120 times as much as accessing a register [39]. It has long been known that using a cache can improve the practical cost of accessing main memory. A cache is a fast memory which can hold some of the content of the main memory, and which is inserted between the processor and main memory, sometimes with multiple levels of increasingly faster and smaller caches.

Figure 2.8: A cache hierarchy

A cache exploits two features inherent in the way many algorithms access memory: *temporal locality* and *spatial locality*. Temporal locality refers to cases where the algorithm accesses the the same content several times in a small amount of time. Spatial locality is where the algorithm accesses memory that is located nearby the last address it accessed. When the processor attempts to access main memory, the cache will be checked to see if it contains the relevant word. If it did (a *cache hit*) the cache will return the data. If it did not (a *cache miss*) the cache will fetch the data from main memory, usually in a block (or "line") of several words at a time. The ratio of cache misses over the number of accesses is called the *miss rate*, and can be used as a simple indicator of the performance of the cache [17].

The cache can be considered to have a set of slots in which the blocks can be inserted. Each slot will have an associated *tag* which indicates the address of the block which is stored there. There are different ways of determining the position of a block in the cache [39]:

**Direct mapped** : Each block is mapped to a single slot. This implies that when a new block is fetched, the old block occupying its slot *must* be evicted.

**N-way set associative** : Each block is mapped to one of N slots. When fetching a new block a replacement policy determines which of the old slots are chosen. A common policy is *least recently used* (LRU). The policy tracks the usage of blocks and the block that was used least recently will be evicted in favor of the new one.

**Fully associative** : A block can be inserted into any slot. This implies that we must compare the tags of all the slots in the cache to determine if a word is present or not.

These approaches have various pros and cons. A direct mapped cache is cheap to implement, but will have a lower hit rate. An N-way set associative cache requires more logic, and higher N implies a higher cost. The cost is also dependent on the replacement policy. LRU is cheap to implement in a 2-way set associative cache, requiring only a single bit to track which block was used last. For 4 and 8-way set associative cache, using a LRU policy can become prohibitively expensive and some implementations opt for a *pseudo-LRU* policy [53, 13].

## 2.12 FPGA

A field-programmable gate array (FPGA) is a type of integrated circuit which can be programmed (or configured) to perform the function of almost any kind of digital circuit or system[28]. The FPGAs is an array of logic blocks, memory and a routing fabric which connects these together. The logic blocks, or look-up tables (LUTs), can be configured to perform arbitrary combinatorial functions on a number of inputs. FPGAs can also contain some specialized blocks. The FPGA used in this thesis contains for example digital signal processing and memory controller blocks[68]. These specialized blocks implement commonly used functions and using these is more efficient than implementing the same functions in the general logic blocks.

Although FPGAs are use more area, consume more power and are slower than applicationspecific integrated circuits (ASICs), they are still very useful due to significantly smaller investment costs in terms of both time and money[28]. It is therefore beneficial for projects with low volume productions or short development time, or for prototyping and testing.

## 2.13 ORPSoC

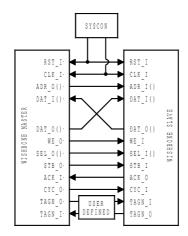

OpenRISC Reference Platform SoC ("ORPSoC") is a project aimed at creating an opensource platform for OpenRISC development. The current version of ORPSoC uses the OpenRISC processor *OR1200* and integrates it in a system with several other modules and interfaces. The system includes modules for JTAG, Ethernet MAC, on-chip RAM/ROM, SPI, UART, I2C and USB. Every module in the system is connected through the Wishbone bus. There are derivate configurations available for a few different FPGA boards, both based on Actel and on Xilinx.

Wishbone [35] is an open-source hardware bus standard, and specifies the interface between components in an ASIC or FPGA design. It is an effort by the OpenCores community to develop a common interface between open-source hardware components, and it's used by many of the modules available on the OpenCores website. The standard only specifies the digital signals and their protocol. Analog effects or bus topology is intentionally left ambiguous.

Data is transferred during an interval called a bus cycle. During a bus cycle the master will

request a read or write operation on a slave and the relevant data will be transferred. Of particular interest in this thesis is *burst cycles*, which is an optional feature of Wishbone. In a 32-bit Wishbone bus, a single 32-bit word is the most that can be transferred in a single clock cycle. By using burst cycles the master can negotiate the transfer of multiple consecutive words during a single bus cycle. This provides two benefits: it avoids having to set up a new bus cycle for each word and it allows the slave to know up front the next address that should be transferred. This can potentially allow it to service the following requests with less delay. When negotiating a burst cycle, the master provides the first address that should be transferred and indicates how the next addresses should be calculated. There are four ways the addresses can be incremented: *linear*, wrap-4, wrap-8 and wrap-16. With the linear mode the address is incremented linearly for each transfer, while with wrap-4, wrap-8 and wrap-16, the address is looped around a 4, 8 or 16 word block boundary. This feature is useful for reading cache lines for the cache of a processor. The word that the processor requested can be fetched first and sent directly to the processor, allowing it to continue executing, while the rest of the words in the cache line can be transferred subsequently.

Figure 2.9: Wishbone signal lines[35]

OpenRISC is an effort to develop a series of general purpose, open-source RISC CPU designs. There is currently one OpenRISC architecture, called OpenRISC 1000. The first implementation is OpenRISC 1200 ("OR1200"). The OR1200 is a 32-bit scalar RISC with Harvard micro-architecture (separate data and instruction interface), 5 stage integer pipeline, IEEE 754 compliant single precision FPU, virtual memory support (MMU) and basic DSP capabilities[36]. It includes an 8KB data cache and an 8KB instruction cache by default. The data and instruction interfaces is implemented as a Wishbone interface.

### 2.14 Digilent Atlys

Atlys is an FPGA prototype board made by Digilent. It uses a Spartan-6 XC6SLX45 FPGA chip. The FPGA chip has 43,661 logic cells (27,288 6-input LUTs), 54,576 flip-

2.14 Digilent Atlys

flops and 116 18Kbit Block RAM blocks (total 2,088Kbit)[68]. The Atlys prototype board includes 128Mbyte DDR2 RAM, an Ethernet port, two HDMI inputs, two HDMI outputs, an AC-97 codec, a 16Mbyte SPI Flash, USB Keyboard/Mouse input, 8 LEDs, 8 switches, 5 push buttons, a 100MHz clock and two expansion ports[11]. The FPGA is programmed through a Cypress CY7C68013A-56 USB microcontroller. This microcontroller is has communication lines connected to the FPGA which can be used to communicate with the configured FPGA from a personal computer.

#### Chapter 2 Background

## Chapter 3

## **Previous Work**

No hardware implementations of ray tracing of SVOs was found in the literature. The work this project builds on can be divided in four categories: implementations of ray tracing of SVOs in software, implementations in GPUs, implementations of other forms of ray tracing in hardware and work related to data structures for SVOs.

### **3.1** Software Implementations

These works are all in software on CPUs, which is typical for papers from the 90s, as GPGPUs were not available yet. The first descriptions found of octree traversal was as a volume rendering technique by Levoy [31]. It illustrates that introducing the hierarchical octree structure improves voxel traversal speed. The next works are the SMART algorithm by Spackman and Willis [49] and an algorithm by Stolte and Caubet [51]. They are both based on a 3D DDA (Digital Differential Analyzer) as described by Sung [54], which works by stepping through the space by adding a delta value to a vector. Revelles et al. [41] presents an algorithm based on keeping track ray parameters (t from Equation 2.5) for the voxels during traversal. It appears to be the first work that constructs an algorithm which is specifically optimized for traversing octrees. The algorithm is compared to three previous bottom-up algorithms, and one top-down algorithm, and it was found to have improved performance over existing algorithms. A paper by Whang et al. [58] was also reviewed. It presents a variation of octrees where the middle planes could be shifted. This made it possible to balance the tree depending on the content of the scene. However, it was not intended for rendering voxels, as the resulting voxels would not be equilateral.

## 3.2 GPU Implementations

The arrival of GPGPUs allowed new rendering techniques to be implemented. Gobbetti et al. [15] implemented one of the first techniques for ray casting octrees on the GPU.

#### Chapter 3 Previous Work

Their algorithm is based on an extension of an efficient ray traversal algorithm for kdtrees. Crassin et al. [10] presents a full ray tracing architecture for GPUs, which is capable of streaming parts of the octree to the GPU on demand. Their work is similar to that of Gobbetti et al. [15], but provides better quality and performance. Their algorithm is based on *kd-restart*, and avoids the use of a stack which is potentially inefficient on a GPU. The solution is geared towards rendering large volumetric data sets, e.g., medical 3D images.

Laine and Karras [29] created an implementation that utilizes a stack, and the algorithm appears nearly identical to that of Revelles et al. [41]. It is not clear why they chose to use a stack, but considering it was research by NVIDIA, who makes GPGPUs, it is probably an informed choice. Another difference from Crassin et al. [10] is that the implementation is made more suitable for rendering surfaces than volumetric data, which they claim is more relevant for most real-world content.

A master thesis by Römisch [42] presented three implementations: one using a bottom-up method utilizing neighbor pointers, the second using a kd-restart based method, and the third using a short stack. Neighbor pointers was found to be fastest, but at the cost of some flexibility. Between kd-restart and short stack, kd-restart was fastest. It's hypothesized that it's because of the limited performance of GPU processors when complex control-flow statements are used.

Römisch [42] and Laine and Karras [29] both explored short stacks on GPGPUs but came to differing conclusions. Römisch and Møller-Nielsen found that using a stack, even a short one, resulted in worse performance. While Laine found that a full stack was better than a short stack. This could possibly be due to different GPGPU architectures, or that the specifics of the implementations are different. In a hardware implementation, this issue is also particularly interesting, as the stack will require registers that consume area. This area could be used for other logic that could improve performance. Another important consideration is memory bandwidth. A short stack or restart algorithm will require more node lookups, causing more traffic on the data bus.

## 3.3 Ray Tracing in Hardware

The only hardware designed for ray tracing found in the literature are two prototypes by Woop and Schmittler from the computer graphics laboratory at Saarland University[43, 64]. They render polygon data, and use a kd-tree as an space partition structure to accelerate ray tracing. The first prototype is a fixed function ray tracer called SaarCOR. The second is a programmable ray processing unit (RPU), which allows for higher quality in the rendered image at the cost of area or performance. Presumably the kd-tree traversal unit described in these papers bears some similarity to the octree traversal unit in this thesis. Unfortunately the papers do not go into detail regarding the traversal unit, except to mention that it uses a stack and requires 4 adders, 4 dividers, 13 comparators and 44.5KB of internal memory.

3.4 Data Structures

## **3.4 Data Structures**

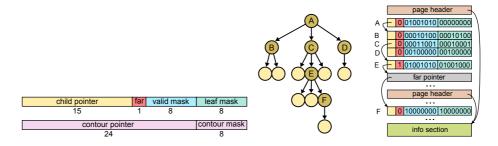

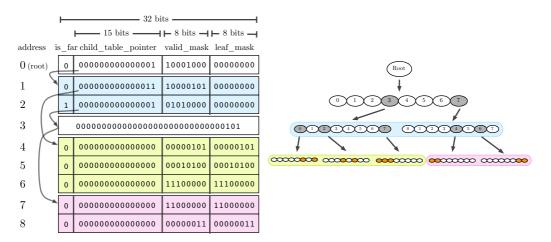

There are many ways to encode an octree. The main considerations is to compress the size of the encoded octree as much as possible without making decoding of the structure too expensive. A naive implementation would have 8 child pointers for each inner node, which would either point to another innor node, or leaf data. One optimization to this scheme is to store data about child nodes within the inner nodes as a set of flags[6, 29]. Each node can be either an empty octant, an inner node, or a solid voxel. Using 2 bits to represent these three states for each child results in 16 bits of data. Instead of having a pointer to each child node, a single pointer can point to an array of node data. The size of this pointer depends on the potential size of the octree file. Laine and Karras [29] showed that if we use a relative pointer and organize the data in a depth-first order, 15 bits is enough for most child pointers. For the few cases where the pointer falls outside the 15-bit range, an additional bit indicates that the pointer is a *far pointer*, which points to a 32-bit pointer instead. The contour pointer and page header/info section shown in Figure 3.1 is used to refine the shape of the voxels and attach additional data to them.

Octree-based geometry compression is introduced by Botsch et al. [8] and Peng et al. [38]. Schnabel and Klein [45] builds on this work and presents a method for compression of point-sampled models. The general idea is that it is possible to predict the configuration of a child node as you descend the tree, and that this can be exploited by storing this configuration using variable-length encoding. These techniques obviously add complexity to the encoding and decoding of the octree, but the size of the encoded octree is smaller.

Figure 3.1: Data structure organization from Laine and Karras [29].

Chapter 3 Previous Work

## Chapter 4

# An Algorithm for SVO Traversal

Out of the various algorithms reviewed, the one described by Revelles et al. [41] appeared to be most suited for this thesis. It was written with the intention of CPU implementation, and it is a recursive top-down algorithm using a stack. However, it can easily be modified to support restarting and short stacks. The algorithm is thoroughly described, which makes it easy to implement. Furthermore, the operations performed in the kernel of the algorithm is well suited for implementation using fixed point numbers; additions, comparisons and simple bit manipulation. And as a very similar algorithm was used by Laine and Karras [29], it appears the algorithm is still competitive. However, the addition of contour data that they presented was not used in this thesis, as it would add too much complexity to the hardware implementation. The algorithm described by Gobbetti et al. [15], uses several multiplications which would increase the cost of a hardware implementation, and it is uncertain if the algorithm is faster. Bottom-up methods were also discarded. Although they were found to be a little faster than restart based and short stack algorithms in one GPGPU implementation [42], the stack in this implementation made the algorithm slower due to the architecture of the GPGPU. It is expected that a stack will have a large performance benefit in a hardware implementation, without the drawbacks of larger memory consumption and less flexibility that the bottomup method had.

This chapter describes the algorithm presented by Revelles et al. [41], with some minor modifications and differences in notation. Finally, an illustration has been created that demonstrates in detail how the algorithm works.

### 4.1 Overview

The algorithm takes each face of the octants in the tree, and extends them to planes. It then finds the *t*-value at which the ray intersects these planes, as per Equation 2.5. First

it calculates these values for the root voxel. The ray could in some applications start outside the root, meaning the actual octree we want to traverse might just be part of the scene being rendered. We must therefore check that the ray hits the root voxel at all. If it does, the algorithm enters the recursive part. It takes the *t*-values of the voxel, and uses these to determine which child node the ray enters. If the child node is not a leaf, it calculates the *t*-values for the child, and recurses on it. It moves through each child the ray intersects, until it exits the current voxel, at which point the function returns.

For now we assume that the ray traverses in a positive direction along each axis. I.e., the components of  $\mathbf{d}$  are all positive. According to Revelles et al. [41] this assumption makes it more efficient to describe and implement the algorithm, while it is easy to modify it to support negative directions.

### 4.2 Parameters

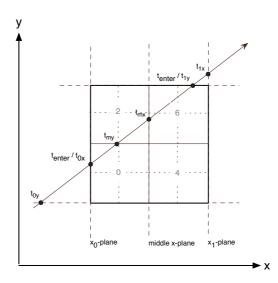

Figure 4.1: Parameters in the octree traversal algorithm[41].

The octree consists of axis-aligned cubes. Each face of the cube is extended to a plane. Unless the ray is running parallell to this plane, there will be a time, t, at which the ray intersects the plane. The *entry planes* are the ones where the ray potentially enters the octant. The *exit planes* are the ones where the ray exits the octant. The fundamental parameters of the algorithm are the t-values for the three entry planes,  $\mathbf{t_0}$  or  $t_{0x}$ ,  $t_{0y}$ ,  $t_{0z}$ , and for the three exit planes  $\mathbf{t_1}$  or  $t_{1x}$ ,  $t_{1y}$ ,  $t_{1z}$ . At every step in the algorithm, it must keep track of  $\mathbf{t_0}$  and  $\mathbf{t_1}$  for the current octant.

Assuming that the components of the direction vector are positive, the *t*-values can be found using Equation 4.1, where  $x_0$  and  $x_1$  are the *x*-coordinate of the two faces of the

octant that are normal to the x-axis.

$$t_{0x} = (min(x_0, x_1) - o_x)/d_x$$

$$t_{1x} = (max(x_0, x_1) - o_x)/d_x$$

(4.1)

The ray will not enter an octant unless it has crossed all the entry planes. Consequently, the t at which the ray enters the octant is the t of the last entry plane it crosses. Since t is strictly increasing as we travel along the ray, the t at which we enter the octant,  $t_{enter}$ , is the largest of t-values of the three entry planes. By the same reasoning, the time at which we exit the octant is the smallest of the t-values of the three exit planes.

$$t_{enter} = max(t_{0x}, t_{0y}, t_{0z}) t_{exit} = min(t_{1x}, t_{1y}, t_{1z})$$

(4.2)

### 4.3 Child Nodes

Assuming that the ray intersects an octant, and given the *t*-values for that octant, the *t*-values for the child nodes can be easily derived. As each child nodes shares either the entry plane or exit plane for each side, one set of *t*-values can be copied from the parent node. The other set can be found by finding the *t*-values for the middle planes of the node ( $\mathbf{t_m}$  or  $t_{mx}$ ,  $t_{my}$ ,  $t_{mz}$ ):

$$\mathbf{t_m} = (\mathbf{t_0} + \mathbf{t_1})/2 \tag{4.3}$$

The t-values for the child node can now be found. Equation 4.4 shows an example for the x-values, and can be extended to the other components.

$$t_{0x-\text{child}} = t_{0x} t_{1x-\text{child}} = t_{mx}$$

If child-node is on the low side of the middle plane (4.4a)

$$t_{0x-\text{child}} = t_{mx} t_{1x-\text{child}} = t_{1x}$$

If child-node is on the high side of the middle plane (4.4b)

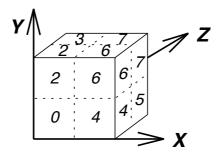

For instance, child 0 in Figure 4.1 is on the left (lower) side of the middle x-plane, and thus its  $t_{0x}$  and  $t_{1x}$  is the parents  $t_{0x}$  and  $t_{mx}$ . Determining which side of the middle plane a given child node is on is made easy by carefully selecting the indices of the child nodes. There are 8 child nodes, which can be represented by a 3-bit integer. The child nodes are numbered so that each of the 3 bits determine which side of the middle plane the nodes are on. Bit 2, 1 and 0 represent respectively X, Y and Z. I.e., if bit 2 is set, the child node is on the lower end of the X-axis. This results in the numbering shown in Figure 4.2. The hidden node is node #1.

Figure 4.2: Indexing of child nodes[41].

**Finding child indices** When processing a node, the child-nodes have to be traversed in the right order. The first child node the ray enters have to be found, and if a collision is not found there, there are one or two more child nodes the ray can intersect. The first child node is determined by looking at which side of the various middle planes the ray enters. This is best illustrated by Algorithm 1.

#### Algorithm 1 FIRSTINDEX $(t_{enter}, \mathbf{t_m})$

```

1: idx \leftarrow 0b000 (3-bit integer)

2: if t_{enter} > t_{mx} then

3: idx[2] \leftarrow 1

4: end if

5: if t_{enter} > t_{my} then

6: idx[1] \leftarrow 1

7: end if

8: if t_{enter} > t_{mz} then

9: idx[0] \leftarrow 1

10: end if

11: return idx

```

After traversing a child node, finding the index of the next child node is a function of the previous index and the exit plane of the child. This function is illustrated in Algorithm 2. It states that if the ray exits the child through the YZ-plane, which is equivalent to  $t_{1x}$  being the smallest of  $\mathbf{t}_1$ , then the ray should step to the next child along the x-axis. If the child is already on the high side of the x-axis, it means the ray exited the parent voxel.

Algorithm 1 and Algorithm 2 has here been transformed from the tabular form found in Revelles et al. [41] to a functional form closer to the form which we will use in the hardware implementation in later chapters.

```

Algorithm 2 NEXTINDEX(idx_{prev}, t_{exit-child})

```

```

1: idx \leftarrow idx_{prev}

(3-bit integer)

2: exit-node \Leftarrow false

3: if t_{1x-\text{child}} = t_{\text{exit-child}} then

if idx[2] = 1 then

4:

exit-node \Leftarrow true

5:

end if

6:

idx[2] \Leftarrow 1

7:

8: else if t_{1y-\text{child}} = t_{\text{exit-child}} then

if idx[1] = 1 then

9:

exit-node \Leftarrow true

10:

end if

11:

idx[1] \Leftarrow 1

12:

13: else

if idx[0] = 1 then

14:

15:

exit-node \Leftarrow true

end if

16:

idx[0] \Leftarrow 1

17:

18: end if

19: return idx, exit-node

```

#### 4.4 Negative Directions and Parallel Rays

**Negative Directions** It was mentioned that we have assumed that the components of the direction vector are all positive. This is obviously not the case for real rays (i.e., a ray can point in any direction in the space), and so the algorithm must be modified slightly to handle this case. If one of the components of the direction vector is negative, the ray is mirrored about the corresponding middle plane of the octree. Furthermore, a bit mask is set to recall this fact, labeled *dir-mask* in Algorithm 3. The bit mask is only used when we retrieve a child node. The corresponding bits in the child node index is then flipped (implemented using **xor** in Algorithm 3), and the the algorithm will consequently descend into the correct child node. Why this works is explained more thoroughly by Revelles et al. [41].

**Parallel Rays** If a ray runs parallel to an axis,  $t_0$  and  $t_1$  can not be found (or will be infinite). There are two ways to deal with this. Revelles et al. [41] suggests setting  $t_0/t_1$  to  $+\infty$  or  $-\infty$  depending on conditions, and taking this into account in all calculations that involve the parameters. A different solution is to check if the components of the ray direction vector **d** is zero, and if so, set them to a tiny non-zero value[30]. This is slightly less accurate, but makes the algorithm easier to implement.

#### 4.5 The Tracing Kernel

```

Algorithm 3 TRACEKERNEL(node, t<sub>0</sub>, t<sub>1</sub>)

```

```

1: if t_{1x} < 0 or t_{1y} < 0 or t_{1z} < 0 then

return false

2:

3: end if

4: t_{enter} \Leftarrow max(t_{0x}, t_{0y}, t_{0z})

5: if CHILDISLEAF(node) then

PROCESSLEAF(node, t_{enter})

6:

return true

7:

8: end if

9: \mathbf{t_m} \leftarrow (\mathbf{t_0} + \mathbf{t_1})/2

10: child - idx \leftarrow FIRSTINDEX(t_{enter}, \mathbf{t_0})

11: repeat

child-node \leftarrow GETCHILDNODE(node, child-idx \oplus dir-mask)

12:

\mathbf{t_{0-child}}, \mathbf{t_{1-child}} \leftarrow \text{SELECTCHILDT}(child-idx, \mathbf{t_0}, \mathbf{t_m}, \mathbf{t_1})

13:

if IsVALID(child-node) then

14:

found-leaf \leftarrow TRACEKERNEL(child-node, \mathbf{t_{0-child}}, \mathbf{t_{1-child}})

15:

if found-leaf then

16:

return true

17:

18:

end if

19:

child-node, exit-node \leftarrow NEXTINDEX(child-idx, \mathbf{t_{1-child}})

end if

20:

21: until exit-node

22: return false

```

The kernel of the tracing algorithm can now be defined, and is listed in Algorithm 3. It is formulated as a recursive function for clarity. The kernel can be called with the parameters calculated for the root node. It will traverse the octree until a leaf node is found, or the ray exits the octree. The first lines will skip all nodes it encounters before the start of the ray (t = 0). It then checks if the current node is a leaf node. If not, it finds the first child node index, and starts to iterate over each child node the ray intersects. If a valid node is found it recurses on that node, if not it calculates the next child index and iterates until the ray exits the current node.

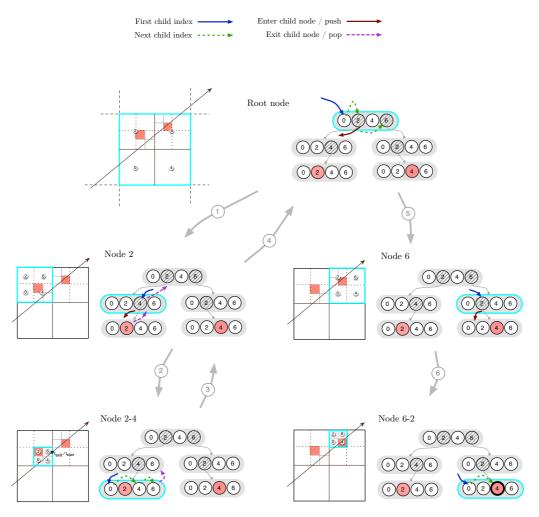

To illustrate how the algorithm works in practice, Figure 4.3 shows the algorithm running on a small three-level octree with two solid voxels. The ray will pass close to the first voxel and hit the second one.

**Initialization** The *t*-values are calculated for the root, and we check if the ray hits the octree. Since it does, the trace kernel is called for the root node.

**Root node** The first child index is found (node 0). The child is empty. The next child index is found (node 2). The child is an inner node. The algorithm recurses on node 2. ①

Figure 4.3: Illustration of the octree tracing algorithm.

**Node 2** The first child index is found (node 4). The child is an inner node. The algorithm recurses on node 2-4. ②

**Node 2-4** The first child index is found (node 0). The child is empty. The next child index is found (node 4). The child is empty. The next child index is found (node 6). The child is empty. The ray exits the current node and the algorithm goes up a level. If we used a restarting algorithm, we would use  $t_{\text{exit-child}}$  to set a parameter  $t_{start}$ , and restart from the root. Then, when evaluating a node, we would pass it if  $t_{enter} < t_{start}$ . (3)

**Node 2** We re-enter node 2 from child index 4. The ray exits the current node and the algorithm goes up a level. ④

**Root node** We re-enter the root node from child index 2. The next child index is found (node 6). The child is an inner node. The algorithm recurses on node 6. (5)

**Node 6** The first child index is found (node 2). The child is an inner node. We recurse on node 6-2. (6)

**Node 6-2** The first child index is found (node 0). The child is empty. The next child index is found (4). The child is a solid voxel. The algorithm terminates.

# Chapter 5

# A Ray Tracer Geometry Stage

With traditional rasterization, the model-view matrix and the perspective projection matrix is the main data which dictates the size and position of the models relative to the camera, and how they should be projected to a 2D image. If ray tracing of SVOs is to be implemented alongside rasterization, it would be very benificial to use the same data in the ray tracer. This chapter outlines a geometry stage for a ray tracer which mirrors the one used in rasterization. Although it is probable that these techniques have been developed previously, for instance in commercial ray tracing systems, it was not described in any of the literature covered in this thesis. Therefore, these techniques were developed independently.

#### 5.1 Normalizing the Octree

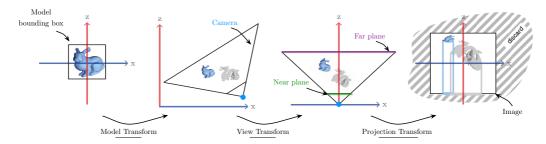

In rasterization, the world is transformed so the camera occupies a fixed position and orientation, and the volume that should be rendered occupies a fixed space. With ray tracing of sparse voxel octree, it is the octree that must occupy a fixed position. As mentioned, the algorithm requires an axis-aligned octree. The algorithm can in principle work with an octree of any size. However, to simplify analysis and implementation, we choose to normalize the octree so that it occupies the volume defined that by the points (-1,-1,-1) to (1,1,1). I.e., the length of the sides of the octree is always 2, and the center of the octree is in the origo of the coordinate system. Instead of defining the size and the position of the model by the corners of the octree, we can use a model transform matrix. This has two benefits: the core of the algorithm can make simplifying assumptions, and the same techniques used to transform polygon model can be used to transform the octree, which should simplify and ease programming.

#### 5.2 Generating Primary Rays

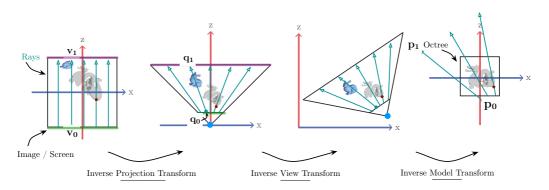

In a ray tracer, it is the position and direction of the primary rays which dictates how the model end up looking on the screen. We can easily define these rays in the canonical view volume. Each ray starts at z = -1 and ends at z = 1, and they are evenly spaced along the X/Y axis. The distance between each ray along the X and Y axis is defined by the width and height of the image. Now consider the transforms discussed in Chapter 2.2. If we follow these in reverse, we get the position and direction of the rays in the coordinate system where the octree is axis aligned and normalized. In essence, the idea of the ray tracer geometry stage is to perform the same operations as in the rasterization geometry stage (Figure 2.3), and perform them in reverse on the ray data rather than the model data. This is illustrated in Figure 5.1. Fortunately, the model and view transform can be reversed simply by taking the inverse of the model/view matrix, but the perspective projection transform requires some elaboration.

Figure 5.1: A ray tracer geometry stage in action

Equation 5.1 shows the equations for the ray tracer geometry stage, where x and y are the x and y coordinates of the pixel in the image, w and h is the width and height of the image,  $v_0$  and  $v_1$  are the starting and end point of the ray in the canonical view space,  $q_0$ ,  $q_1$ ,  $p_0$  and  $p_1$  are the same points in the camera space and the normalized octree space. These points are also illustrated in Figure 5.1.  $\mathbf{P}_i$  is the inverse perspective projection and  $\mathbf{M}_{mv}$  is the model-view tranform matrix.

$$\mathbf{v}_{0} = (x/w, y/h, -1, 1)$$

$$\mathbf{v}_{1} = (x/w, y/h, 1, 1)$$

$$\mathbf{q}_{0}' = \mathbf{P}_{i} \mathbf{v}_{0}$$

$$\mathbf{q}_{1}' = \mathbf{P}_{i} \mathbf{v}_{1}$$

$$\mathbf{q}_{0} = \mathbf{q}_{0}'/\mathbf{q}_{0w}$$

$$\mathbf{q}_{1} = \mathbf{q}_{1}'/\mathbf{q}_{1w}'$$

$$\mathbf{p}_{0} = \mathbf{M}_{mv}^{-1}\mathbf{q}_{0}$$

$$\mathbf{p}_{1} = \mathbf{M}_{mv}^{-1}\mathbf{q}_{1}$$

(5.1)

The ray origin  $\mathbf{o}$  and direction vector  $\mathbf{d}$  for the ray traversal algorithm (see Equation 4.1) may be found as such:

$$\mathbf{o} = \mathbf{p}_0 \tag{5.2}$$

$$\mathbf{d} = \mathbf{p}_1 - \mathbf{p}_0$$

#### 5.3 Inverse Perspective Projection

The model/view matrix can be inverted using standard matrix inversion algorithms such as Gauss-Jordan elimination. The perspective projection however, can not be inverted by simply inverting the perspective projection matrix, because the result is divided by the w-component(Equation 2.4). Using simple linear algebra, we can find a similar equation to go from a canonical view space point  $\mathbf{v}$  to a camera space point  $\mathbf{q}$ .

Solving for  $\mathbf{P}_i$  results in the following matrix:

$$\mathbf{P}_{i} = \begin{pmatrix} -\frac{f(r-l)}{f-n} & 0 & 0 & -\frac{f(r+l)}{f-n} \\ 0 & -\frac{f(t-b)}{f-n} & 0 & -\frac{f(t+b)}{f-n} \\ 0 & 0 & 0 & \frac{2fn}{f-n} \\ 0 & 0 & 1 & -\frac{f+n}{f-n} \end{pmatrix}$$

(5.3)

### 5.4 Normalizing Ray Length

A ray has a starting point and a direction. The direction is often defined as a normalized vector with a length of 1. However, the output of the proposed geometry stage is a starting point and an end point. The starting point is positioned at the near plane and the end point is positioned at the far plane. Although a far plane is strictly speaking not necessary in a stand-alone ray tracer, when combining with rasterization it can be be useful to have the option of terminating the ray tracing at the far plane. Following equation 2.5, the near plane is placed at t = 0 and the far plane at t = 1. If we standardize on this, our algorithm can be designed to optionally terminate at t = 1. This functionality should be useful when calculating light/shadow rays as well. In this case we also have a starting point (the point at which the primary ray hits an object) and an end point (the light source), and we are only interested in finding if the line between these points intersects some object. I.e., we should terminate the ray tracing at t = 1. Another useful feature of having the start and end point be at the near and far plane, is that the resulting t-value can be used to calculate a value for the Z-buffer.

#### 5.5 Z-Buffering With Ray Tracing

In rasterization, the Z-buffer ensures that the geometry appears appears in the correct order from front to back. If we wish to merge the result of the ray traced image with a rasterized image, and have everything appear in the correct order, we need to be able to generate the correct values for the Z-buffer.

When a primary ray hits a voxel, the algorithm returns a t-value  $(t_{out})$  which represent how far along the ray the voxel is. Because we placed the start and end of the ray at the near and far plane, this t-value also represents the position of the voxel between the near and the far plane. This is illustrated by the red dot in Figure 5.1, which can be followed in reverse from its position in the octree on the right, to its position in the canonical view volume on the left.

However, this can not be directly used as a Z-value. The  $t_{out}$  is linear with regards to distance in the camera space. In rasterization the Z-value is linear with regards to distance in the canonical view volume. If we use perspective projection, this Z-value is not linear with regards to camera space. If we look at Equation 2.4, we can see that the Z-value in the canonical view volume,  $v_z$ , is divided by  $v'_w$ . This implies that  $v_z$  is a function of  $1/q_z$  where  $q_z$  is the Z-value in the camera space.

To solve this problem, we can first find the collision point in the camera space, given the t-value at the collision point  $t_{out}$ :

$$\mathbf{q_c} = \mathbf{q_0} + (\mathbf{q_1} - \mathbf{q_0}) \cdot t_{out} \tag{5.4}$$

Using the perspective projection matrix  $\mathbf{P}_{\mathbf{p}}$  defined in Equation 2.3, we can transform this coordinate in to the canonical view volume:

$$\mathbf{v_c} = \mathbf{P_p}\mathbf{q_c} \tag{5.5}$$

Taking the z-coordinate from this vector will give us a Z-value which is compatible with the Z-buffer generated by the rasterizer.

# Chapter 6

# Hardware Optimizations

In order to optimize the ray traversal algorithm for hardware implementation, various considerations were made, and the algorithm was transformed to a form which is feasible to implement in a hardware description language. This chapter will present the rationale for using fixed point numbers, we will analyze the use of a stack in hardware, and the final hardware optimized version of the algorithm will be presented.

#### 6.1 Floating Point vs Fixed Point