# Integration of a Fractal Generator with Mali GPU

Per Kristian Kjøll

Master of Science in ElectronicsSubmission date:June 2012Supervisor:Per Gunnar Kjeldsberg, IETCo-supervisor:Øystein Gjermundnes, ARM Norway AS

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Description**

Candidate name: Per Kristian Kjøll

Assignment title: Integration of a Fractal Generator with Mali-GPU

## Assignment Text

This proposal describes a possible subject for a project thesis for students with background in microelectronics and computer graphics. The description given here is meant for an autumn project only. A possible extension of the content into a master thesis in the spring may be discussed with the supervisors as the work proceeds.

#### Abstract

In a recent master thesis Per Christian Corneliussen successfully developed a fractal generator. The purpose of this project thesis is to take this fractal generator, design AXI and APB interfaces to the fractal generator and integrate it into a system with a Mali-400 GPU and finally run a OpenGL demo that uses data structures generated by the fractal generator. A demo has already been implemented by Per Christian, but the student is encouraged to extend it in order to give it a personal touch. The fractal generator will be realized in an FPGA. When the fractal generator is successfully integrated in the system, the student may participate in one of the regular demo competitions at ARM Norway.

#### Introduction

A fractal is "a rough or fragmented geometric shape that can be split into parts, each of which is (at least approximately) a reduced-size copy of the whole," [4] a property called self-similarity. A mathematical fractal is based on an equation that undergoes iteration, a form of feedback based on recursion [9].

One such mathematical fractal is the fractal defined by the Mandelbrot set. The Mandelbrot set is a mathematical set of points in the complex plane, the boundary of which forms a fractal [7]. The point c belongs to the Mandelbrot set if and only if |Zn| = 2, for all n = 0, where  $Zn + 1 = Zn^2 + c$  and  $Z_0 = 0$

An image can be created from the Mandelbrot set by mapping the (x,y) coordinates of the pixels in the image to the real and imaginary parts of a complex number. For each pixel it is computed how many iterations that is necessary of Eq. 1 before the absolute value of the complex number Zn exceeds 2. The number of iterations is then used as an index into a colour palette which finally determines the colour of the pixel.

A globe is made by wrapping a map around a sphere. This process is known as texture mapping in the field of computer graphics, and is used for drawing or wrapping an image on to a 3D object. Textures are in many cases generated in advance to running a computer game, but they could also be generated on the fly.

#### Thesis statement

The master thesis by Per Christian Corneliussen describes a fractal generator for use with a Mali GPU. Moreover it describes a demo program that creates an animated 3D landscape where the height and the colour of the landscape at any given point is determined by the z-coordinate of vertices generated by the fractal generator.

In the first part of this thesis the student should present the Mandelbrot set and give an overview of the fractal generator.

The core of the fractal generator is complete, but it is necessary to also implement a AXI and a APB interface in order to integrate it into a system with Mali-400. This will be the main task in this project. The RTL code must be written in Verilog.

In order to run the demo it will also be necessary to do some minor changes to the software driver in order to configure the fractal generator prior to each frame. The demo itself could also be reworked in order to give the student the possibility of adding a personal touch to the demo.

Finally the system must be synthesized for FPGA, set the fractal generator up to feed the OpenGLES application with datastructures and participate in a demo competition held at ARM Norway.

Co-supervisor:Øystein Gjerdmundnes, ARM Norway AS

Supervisor:Per Gunnar Kjeldsberg, NTNU

# Abstract

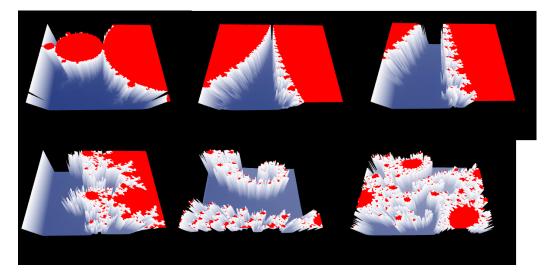

The Mandelbrot set is a well-known fractal with mathematical properties that can be exploited to create 3D-landscapes. The operations required to calculate a heightmap using the Mandelbrot set are highly parallelizable and is thus suitable for a hardware implementation. Generation of 3Dlandscapes,on-the-fly, using the Mandelbrot set is desirable since the Mandelbrot set is infinitely complex[4] and deterministic. This makes possible the creation of many different landscapes with complex patters in, for example, computer games.

A previous master thesis[4] presents a vertex array generator(VAG) that generates the vertices of a 3D-landscape based on an area of the Mandelbrot set. This thesis explores different architectures that connect this vertex array generator with the Mali-400 graphics processing unit(GPU). The result is that the VAG in its current state is not suitable for integration, mostly since it does not support random access to vertices. Thus, a new fractal generator architecture is presented, reusing parts of the VAG.

The new fractal generator is implemented in Verilog and its functionality is verified using the Universal Verification Methodology(UVM). Then, the fractal generator is integrated with the Mali-400 GPU in an FPGA framework and synthesized on FPGA. Tests are also performed at each step of integration.

An OpenGL for Embedded Systems 2.0 demo is written to showcase the functionality of the fractal generator. Changes have been made to the Mali-400 drivers to automatically configure and set-up the fractal generator while the demo is running.

The fractal generator is shown to be working as intended with a scalable performance based on a number of internal cores. Using 64 cores the fractal generator has a worst-case frame time of 51.1 ms at 400Mhz which equals a frame rate of 450 frames pr second, vastly outperforming a software implementation.

The fractal generator is currently limited to creating landscapes of  $128 \cdot 128$  points, the intention was to use the demo and driver to increase the resolution but this has not been solved.

Increasing the resolution and optimizing the cache size of the fractal generator has been left for future work.

# Sammendrag

Mandelbrot-settet er en velkjent fraktal med matematiske egenskaper som kan brukes for å tegne 3D-landskaper. De matematiske utregningene man trenger for å regne ut høydene til et landskap er svært paralleliserbare og egner seg for implementasjon i hardware. Generering av landskap basert på Mandelbrot-settet er ønskelig siden settet er uendelig komplekst og deterministisk, slik at mange forskjellige landskaper kan bli laget fra settet.

En tidligere masteroppgave beskrev en fraktalgenerator(VAG) som genererte punktene til et 3D-landskap basert på et område av Mandelbrot settet. Denne masteroppgaven utforsker forskjellige hardware-arkitekturen som kan koble VAG til Mali-400 GPU. VAG viser seg å være uegnet for integrasjon med Mali og det blir bestemt at en ny fraktalgenerator skal lages som kan gjenbruke deler av VAG.

Den nye fraktalgeneratoren er implementert i Verilog og dens funksjonalitet er testet med Universal Verification Methodology(UVM). Deretter blir fraktalgeneratoren integrert med Mali-400 og syntetisert på FPGA.

En OpenGL for Embedded Systems 2.0 demo har blitt skrevet for å vise funksjonaliteten til fraktalgeneratoren. Endringer har blitt utførst på Mali-400 driveren for å automatisk konfigurere og sette-opp fraktalgeneratoren mens demoen kjører.

Fraktalgeneratoren fungerer som planlagt med skalerbar ytelse basert på et antall indre kjerner. Ved bruk av 64 kjerner har fraktalgeneratoren i verste fall en frame tid på 51.1 ms ved 400Mhz, noe som utgjør en hastighet på 450 bilder i sekundet. Fraktalgeneratoren viser seg å være mye raskere enn en software implementasjon av fraktalgeneratoren.

Fraktalgeneratoren er begrenset til å lage landskaper med en oppløsning på  $128 \cdot 128$  punkter. Intensjonen var å bruke demoen og driveren for å øke oppløsningen men dette fungerte ikke som planlagt.

Å øke oppløsningen og å optimalisere cache-størrelsen på fraktalgeneratoren har blitt satt til framtidig arbeid.

# Preface

The problem description for this thesis was originally given for a term project and asked for two interfaces to an existing fractal generator. The existing fractal generator was designed in a previous master thesis given by ARM. During the term project it was decided that the existing fractal generator was not suited for integration with Mali-400 and a new fractal generator should be designed.

The term project began on the work presented in this thesis, specifically it explored different architectures and begun on the fractal generator design. Some of this work is recapped in this thesis to gather the whole fractal generator design process in one place.

The Vertex Array Generator presented in Section 3 was designed by Per Christian Corneliussen in a previous master thesis. The architecture exploration and discussion in Chapter 4 was done in the term project.

The rest of the chapters present the work done for this thesis.

To keep the thesis brief, the chapters does not cover low level implementation details. Some exceptions are made when the details are important to understand the discussions and choices made. If more details are needed, see the appendices for source code.

In addition to this, descriptions of the Mali-400 and its drivers has been limited in some cases due to NDA. The driver source code has been left out for this reason as well.

Thanks to Per Gunnar Kjeldsberg(NTNU) and Øystein Gjerdmundnes(ARM Norway AS) for help throughout the semester.

# Contents

| 1        | $\mathbf{Intr}$ | oduction                                                      | 1  |

|----------|-----------------|---------------------------------------------------------------|----|

|          | 1.1             | Thesis Objectives                                             | 1  |

|          | 1.2             | Thesis Outline                                                | 2  |

| <b>2</b> | Bac             | kground Theory                                                | 4  |

|          | 2.1             | The Mandelbrot Set                                            | 4  |

|          | 2.2             | OpenGL ES 2.0                                                 | 6  |

|          | 2.3             | The Mali-400 GPU                                              | 7  |

|          | 2.4             | The AMBA AXI Protocol                                         | 8  |

|          | 2.5             | The AMBA APB Protocol                                         | 8  |

|          | 2.6             | The PL301                                                     | 9  |

|          | 2.7             | Hardware Verification                                         | 9  |

| 3        | The             | Vertex Array Generator                                        | 11 |

| 4        | Arc             | hitecture Exploration                                         | 14 |

|          | 4.1             | The Vertex Array Generator as an AXI Slave                    | 14 |

|          | 4.2             | The Vertex Array Generator with DMA                           | 15 |

|          | 4.3             | Fractal Generator With Cache                                  | 16 |

| <b>5</b> | Frac            | ctal Generator Design                                         | 19 |

|          | 5.1             | Configuration Parameters and Data Types                       | 19 |

|          | 5.2             | Relationship Between AXI address and Coordinates of a Fractal | 21 |

|          |                 | 5.2.1 Discussion                                              | 22 |

|          | 5.3             | The APB Interface                                             | 23 |

|          |                 | 5.3.1 Verilog Implementation                                  | 23 |

|          |                 | 5.3.2 Discussion                                              | 24 |

|   | 5.4         | The A                                                                                  | XI Interface                                                                                                                                                         | 24                                                                                             |

|---|-------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   |             | 5.4.1                                                                                  | Verilog Implementation                                                                                                                                               | 24                                                                                             |

|   |             | 5.4.2                                                                                  | Discussion                                                                                                                                                           | 25                                                                                             |

|   | 5.5         | The A:                                                                                 | rbiter                                                                                                                                                               | 25                                                                                             |

|   |             | 5.5.1                                                                                  | Verilog Implementation                                                                                                                                               | 26                                                                                             |

|   |             | 5.5.2                                                                                  | Discussion                                                                                                                                                           | 27                                                                                             |

|   | 5.6         | The Co                                                                                 | oordinate Cache                                                                                                                                                      | 28                                                                                             |

|   |             | 5.6.1                                                                                  | Verilog Implementation                                                                                                                                               | 28                                                                                             |

|   |             | 5.6.2                                                                                  | Discussion                                                                                                                                                           | 29                                                                                             |

|   | 5.7         | Fractal                                                                                | Generator Verification                                                                                                                                               | 33                                                                                             |

|   |             | 5.7.1                                                                                  | The Verification Framework                                                                                                                                           | 33                                                                                             |

|   |             | 5.7.2                                                                                  | The Verification Plan                                                                                                                                                | 34                                                                                             |

|   |             | 5.7.3                                                                                  | Results and Discussion                                                                                                                                               | 35                                                                                             |

|   |             |                                                                                        |                                                                                                                                                                      |                                                                                                |

| 6 | Inte        | gratio                                                                                 | n of the Fractal Generator                                                                                                                                           | 38                                                                                             |

| 6 | Inte<br>6.1 | 0                                                                                      | n of the Fractal Generator                                                                                                                                           | <b>38</b><br>40                                                                                |

| 6 |             | 0                                                                                      |                                                                                                                                                                      |                                                                                                |

| 6 |             | Connee                                                                                 | cting Mali and the fractal generator                                                                                                                                 | 40                                                                                             |

| 6 |             | Connec<br>6.1.1<br>6.1.2                                                               | cting Mali and the fractal generator                                                                                                                                 | 40<br>41                                                                                       |

| 6 | 6.1         | Connec<br>6.1.1<br>6.1.2                                                               | cting Mali and the fractal generator                                                                                                                                 | 40<br>41<br>41                                                                                 |

| 6 | 6.1         | Connec<br>6.1.1<br>6.1.2<br>FPGA                                                       | cting Mali and the fractal generator                                                                                                                                 | 40<br>41<br>41<br>42                                                                           |

| 6 | 6.1         | Connee<br>6.1.1<br>6.1.2<br>FPGA<br>6.2.1<br>6.2.2                                     | cting Mali and the fractal generator                                                                                                                                 | 40<br>41<br>41<br>42<br>42                                                                     |

| 6 | 6.1         | Connee<br>6.1.1<br>6.1.2<br>FPGA<br>6.2.1<br>6.2.2                                     | cting Mali and the fractal generatorTest ResultsIntegration Discussion and ConclusionIntegration and TestPlatform and Framework DescriptionTesting the FPGA Framwork | 40<br>41<br>41<br>42<br>42<br>43                                                               |

| 6 | 6.1         | Connec<br>6.1.1<br>6.1.2<br>FPGA<br>6.2.1<br>6.2.2<br>6.2.3                            | cting Mali and the fractal generator                                                                                                                                 | <ol> <li>40</li> <li>41</li> <li>41</li> <li>42</li> <li>42</li> <li>43</li> <li>43</li> </ol> |

| 6 | 6.1         | Connee<br>6.1.1<br>6.1.2<br>FPGA<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5          | cting Mali and the fractal generator                                                                                                                                 | <ol> <li>40</li> <li>41</li> <li>42</li> <li>42</li> <li>43</li> <li>43</li> <li>43</li> </ol> |

|   | 6.1         | Connec<br>6.1.1<br>6.1.2<br>FPGA<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>Open0 | cting Mali and the fractal generator                                                                                                                                 | <ol> <li>40</li> <li>41</li> <li>42</li> <li>42</li> <li>43</li> <li>43</li> <li>44</li> </ol> |

|              |       | 7.1.2   | The Rendering Phase                                  |     | 47  |

|--------------|-------|---------|------------------------------------------------------|-----|-----|

|              |       | 7.1.3   | Configuring the Fractal Generator                    |     | 47  |

|              |       | 7.1.4   | The Vertex Shader                                    |     | 48  |

|              |       | 7.1.5   | The Fragment Shader                                  |     | 48  |

|              |       | 7.1.6   | Software Fractal Generator                           |     | 49  |

|              | 7.2   | The C   | penGL ES 2.0 Driver                                  |     | 50  |

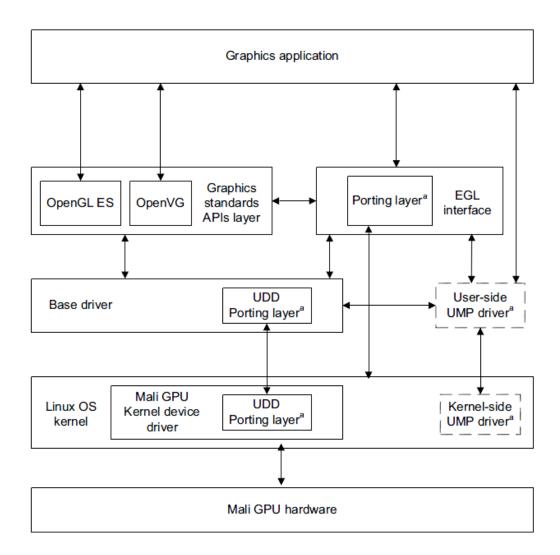

|              |       | 7.2.1   | The Mali GPU Open GL ES Driver Architecture          |     | 50  |

|              |       | 7.2.2   | Controlling the fractal generator using the Mali dri | ver | 52  |

|              | 7.3   | Result  | ts and Discussion                                    |     | 56  |

|              |       | 7.3.1   | The Fractal Resolution                               |     | 57  |

| 8            | Pro   | filing  |                                                      |     | 59  |

| 9            | Cor   | nclusio | n                                                    |     | 61  |

|              | 9.1   | Futur   | e Work                                               |     | 61  |

| 10           | ) Арј | pendic  | es                                                   |     | Ι   |

| $\mathbf{A}$ | Sou   | rce Co  | ode for the Fractal Generator                        |     | Ι   |

| в            | Sou   | rce Co  | ode for UVM Verification Framework                   | XX  | IV  |

| $\mathbf{C}$ | Sou   | rce Co  | ode for the Fractal Demo                             | ХL  | TIT |

# List of Figures

| 1  | An example system with Mali and the fractal generator. Pro-<br>duced from [13]                                                                                        | 2  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | The Mandelbrot set[4]                                                                                                                                                 | 4  |

| 3  | The Mandelbrot Set with color and zoom[9]                                                                                                                             | 5  |

| 4  | Two images of the mandelbrot set with different iteration lim-<br>its.Left = $160$ iterations, right = $80$ iterations. Points that hit<br>the limit are colored red. | 5  |

| 5  | The OpenGL ES 2.0 Graphics Pipeline [6]                                                                                                                               | 6  |

| 6  | The Architecture of the VAG. Taken from [4]                                                                                                                           | 12 |

| 7  | The Vertex Array Generator as an AXI slave                                                                                                                            | 14 |

| 8  | The Vertex Array Generator as an AXI master(DMA)                                                                                                                      | 15 |

| 9  | Structure of the Fractal Generator and how it draws a frame                                                                                                           | 18 |

| 10 | Internal and external AXI address mapping of the vertices in<br>a 3x3 fractal.                                                                                        | 22 |

| 11 | The internal components of the Arbiter and their state de-<br>scriptions                                                                                              | 31 |

| 12 | The structure of the Coordinate Cache                                                                                                                                 | 32 |

| 13 | The verification framework.                                                                                                                                           | 35 |

| 14 | Coverage metrics logged by VCS while running the verification framework                                                                                               | 36 |

| 15 | Left:Fractal landscape using a blue to white gradient. Right:<br>The Odroid-A tablet                                                                                  | 39 |

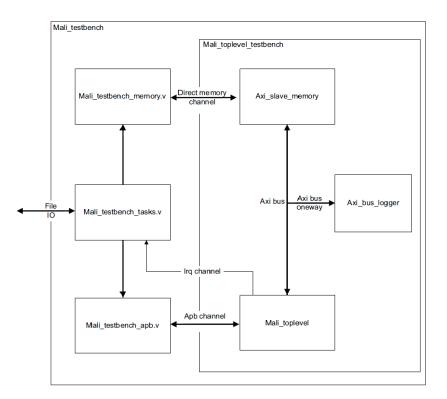

| 16 | ARM Test Bench for Mali [15].                                                                                                                                         | 40 |

| 17 | Connecting Mali and the fractal generator                                                                                                                             | 41 |

| 18 | 1. Motherboard Express $\mu$ ATX. 2-3. Virtex6 FPGAs. 4.Coretile-<br>Express. 5.The A9 CPU                                                                            | 42 |

| 19 | Hardware and software components of the Mali graphics system architecture(Linux). [18, p. 1.4]                                                                        | 51 |

| 20 | The fractal demo zooming in on a point.                                                                                                                               | 56 |

# List of Tables

| 1 | Synthesis results for the fractal generator with 8 FPGs on a                                                                                                                      |    |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | Xilinx Virtex-6x FPGA                                                                                                                                                             | 44 |

| 2 | Average frame time performance over 500 frames of the demo.                                                                                                                       | 60 |

| 3 | Average geometry processor frame time, vertex shader time,<br>and Polygon List Builder Unit time during 30 frames of the<br>worst-case scenario. All results estimated at 400 Mhz | 60 |

# 1 Introduction

Today, more than half of the world population has a mobile phone. In 2011, 17% of mobile phones were smartphones and the percentage is increasing rapidly[8].

One factor leading to the increased adoption of smartphones has been the improvement in display and graphics technologies[3]. The phone has gone from being just a phone to an entertainment platform with music, video, games and the internet.

Since, among other tasks, 3D-rendering for games can always be done more efficiently on special-purpose hardware than on a general-purpose CPU[3], the increased demand for powerful 3D-rendering in smartphones require new phones to have dedicated graphics processing units(GPU). An example of such a GPU is ARM's Mali-400(Mali), which is for example available on the smartphone Samsung S3.

In computer games and other graphical visualizations it is common to provide a 3D-landscape or terrain for the user to navigate. The height coordinates of a 3D-landscape can be calculated by exploiting the mathematical properties of the Mandelbrot set, a well-known geometric fractal. The computations involved are computationally expensive but highly parallelizable, each point can be processed independently of the others, so the calculations are suited for hardware implementation.

In this thesis, a fractal generator is a component that calculates the height coordinates as explained above. The main motivation for designing a fractal generator in hardware is 3D-landscape generation. A fractal generator can generate landscapes on-the-fly, requiring little or no memory between frames. Since the Mandelbrot set is infinitely complex[4] and deterministic, the generator can be used to draw a large amount of different landscapes. Another usage of a fractal generator is to draw aesthetically pleasing 2D images.

## 1.1 Thesis Objectives

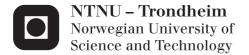

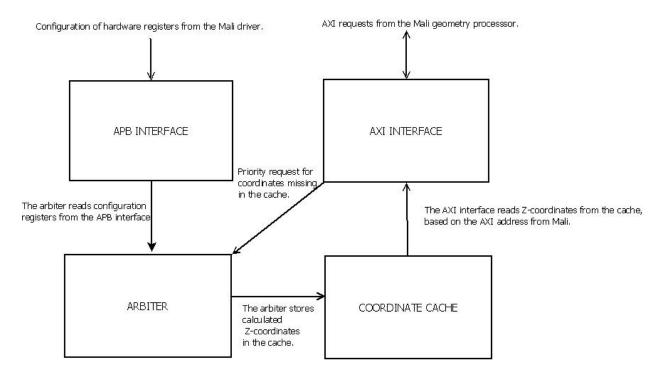

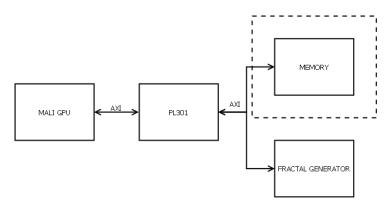

The main objective in this thesis is to design a fractal generator and integrate it with Mali on an FPGA. The fractal generator shall be able to accelerate the generation of a 3D-landscape, where the 3D-landscape is based on the Mandelbrot set and animated using OpenGL ES. The fractal generator must be implemented in Verilog and shall communicate with Mali using the ARM APB and AXI bus communication protocols. Figure 1 illustrates how a fractal generator could be connected to a Mali system.

Figure 1: An example system with Mali and the fractal generator. Produced from [13].

The secondary objective in the project is to alter the Mali drivers, such that control of the fractal generator is performed automatically by the driver, based on input from the OpenGL ES demo.

## 1.2 Thesis Outline

The thesis starts with background theory and previous work.

Chapter 2 will explain the concepts, terms and components needed to understand the later chapters of the thesis.

Chapter 3 describes the task of the fractal generator in detail and presents a previous fractal generator implementation.

Chapter 4 explores different hardware architectures that integrate a fractal generator with Mali, discusses advantages and disadvantages, and ultimately selects an architecture to implement in Verilog.

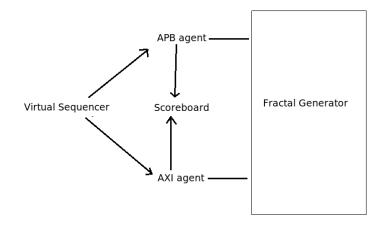

Chapter 5 presents the chosen fractal generator design and all its modules in detail. Alternative choices are also discussed briefly for each module. Section 5.7 verifies the behavior of the fractal generator hardware using the Universal Verification Methodology(UVM).

To avoid difficult debugging, it is necessary to ensure working hardware on FPGA before starting on the driver.

Chapter 6 describes the methodology used to achieve this. It connects the fractal generator to Mali, integrates the whole system with an FPGA framework and synthesizes it. Tests are performed at each step.

Chapter 7 presents the OpenGL ES demo, written to showcase the functionality of the fractal generator, and how it communicates with the driver to control and set-up the fractal generator prior to each frame. Furthermore it presents the Mali driver architecture and the changes made to enable software control of the fractal generator.

Chapter 8 is the profiling chapter, it examines the performance of the fractal generator and compares the hardware accelerated version with other solutions.

Chapter 9 concludes the thesis, it discusses if using the fractal generator increased performance, and if the fractal generator is useful for any practical purposes.

## 2 Background Theory

This chapter explains the terms and theory needed to understand the concepts, descriptions and discussions used in the rest of the thesis.

#### 2.1 The Mandelbrot Set

The Mandelbrot set is a fractal set of complex numbers c. The set is formally defined by the iterative equation

$$Z_{n+1} = Z_n^2 + c, \quad c, Z \in C \tag{1}$$

where the number c is part of the Mandelbrot set if the equation remains bounded when  $n - > \infty$ . It can be shown that if  $(|Z_{re}| > 2) || (|Z_{im}| > 2)$ , the equation will diverge [2, p. 81]. Thus, to examine if a point is in the Mandelbrot set or not, one has to iterate the equation until either the real or imaginary part of Z exceeds two.

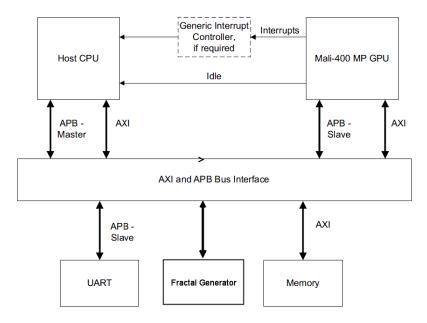

The Mandelbrot set is named after Benoit B.Mandelbrot and is infinitely complex[5, p. 197] and connected[10]. If the Mandelbrot set is plotted in a two-dimensional coordinate system as in Figure 2, using the real and imaginary part of c as its x- and y-coordinates, it shows a boundary with a distinctive and easily recognizable two-dimensional fractal shape.

Figure 2: The Mandelbrot set[4].

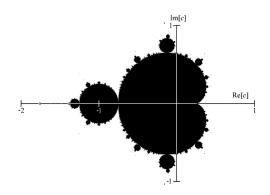

By coloring points in the aforementioned 2D coordinate system with a gradient, based on the number of iterations required to determine if the point is in the Mandelbrot set or not, the Mandelbrot set reveals a complex and aesthetically pleasing structure. Zooming in on specific areas of the set shows self-similarity and high detail as in shown in Figure 3.

Figure 3: The Mandelbrot Set with color and zoom[9].

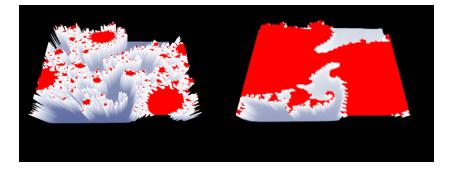

Since many points require an infinite number of the above iterations, it is necessary to set an iteration limit when drawing the Mandelbrot set in practice. This limit will affect the detail of the resulting image(Figure 4).

Figure 4: Two images of the mandelbrot set with different iteration limits.Left = 160 iterations, right = 80 iterations. Points that hit the limit are colored red.

The Mandelbrot set can be used to create 3D landscapes: Instead of, or in addition to, using the number of iterations to color each point, as explained above, the number is used as a third coordinate z. The z-coordinate represents the height of the landscape at that point. For example, the point  $C_1$  in Listing1 would get a z-coordinate of 80(the iteration limit). Since zooming in on the Mandelbrot constantly reveals new patterns and more complexity, the set can be used to generate a large number of unique landscapes.

```

\begin{array}{c} {}^{1} MAX\_ITERATIONS=80 \\ C_{1}=(0,0)=0+i0 \\ 3 Z_{0}=0 \\ Z_{1}=Z_{0}^{2}+c=0 \\ 5 \dots \\ Z_{80}=0 \\ 7 Z \text{ is still bounded when the algorithm reaches the iteration} \\ 1 \text{ limit , so } (0,0) \text{ is part of the Mandelbrot Set.} \end{array}

```

Listing 1: Example of iteration

#### 2.2 **OpenGL ES 2.0**

OpenGL ES is an Application Programming Interface(API) for 3D graphics in embedded systems(ES). It is based on the widespread desktop-API OpenGL, and aims to be smaller and optimized for constrained devices such as mobile phones[6]. In short, the API is a portable and fast software interface to graphics hardware[7]. This thesis will use OpenGL ES 2.0 when coding a demo(Section 7.1) for use with the fractal generator.

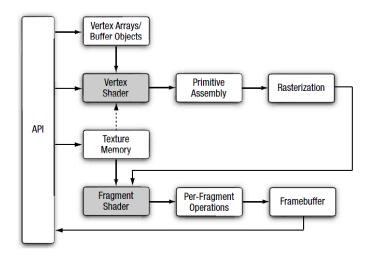

Figure 5: The OpenGL ES 2.0 Graphics Pipeline [6].

OpenGL ES 2.0 implements the graphics pipeline in Figure 5. The basic function of the API, or pipeline, is to project vertices represented in threedimensional virtual space onto a two-dimensional screen. In addition to this, the API facilitates vertex transformation prior to the projection. For example, the **vertex shader** can transform the vertex positions, compute the lighting at each point and more. Since many of these transformations are done using expensive matrix operations, special hardware(GPUs) is used to accelerate the API calls.

When using OpenGL ES functions in an application, a call is made to the OpenGL ES driver. The driver passes information, data structures and hard-ware control register settings, to the GPU(if there is one) [19] [16]. Section 2.3 explains how the Mali GPU uses this information to draw frames.

#### A brief explanation of some OpenGL ES concepts:

#### **Primitives:**

When OpenGL ES draws an object it constructs it by combining groups of vertices into primitives[7]. The most common primitive is the triangle, and there are several drawing modes that uses the triangle as a primitive[4]. If an array contains three vertices, i.e. nine coordinates  $((x,y,z)^*3)$ , and it is drawn with the GL\_TRIANGLES mode, it will be drawn as a single triangle. Adding three more vertices will add another triangle.

#### Triangle Strip:

When drawing a second triangle primitive; instead of drawing a new triangle by adding three vertices as above, a new triangle can be drawn by only adding one more vertex and draw lines to it from the first triangle. The GL\_TRIANGLE\_STRIP mode exploits this fact and avoids drawing all the vertices shared between triangles multiple times[6][7]. However, to keep the concept of primitives, some must still be drawn twice.

#### Vertex buffer object(VBO):

Vertex buffer objects allow OpenGL ES applications to allocate and cache vertex data in high performance graphics memory[6]. There are two types of buffer objects; array buffer objects contains vertex data(the coordinates), and element buffer objects describes the order in which to connect the vertices to create an object. Element buffer objects are also called index arrays, which are used throughout this thesis. All OpenGL ES vertices in this thesis are stored in VBOs.

## 2.3 The Mali-400 GPU

The Mali-400 MP GPU(Mali) is a hardware accelerator for 2D and 3D graphics systems. The GPU implements a graphics pipeline supporting the OpenGL ES and OpenVG APIs[16]. The main processing units in the GPU are the geometry processor(GP) and pixel processors(PP). The pipeline is divided into two main jobs, a GP job and a PP job. Each job performs specific parts of the pipeline, with the GP job doing the vertex shading and the PP job doing the fragment shading.

Below is a brief explanation how the Mali-400 GPU reads and process vertex data to draw geometry.

As described in the above section the OpenGL ES driver create data structures in memory for Mali and configures the hardware prior to each scene(frame). Following this step, the Mali geometry processor transforms each vertex with the instructions in a vertex shader program[16]. This vertex shader program is written by the user and loaded in the OpenGL ES application. The OpenGL ES driver compiles the program into a command list for the Mali vertex shader.

The Mali vertex shader can have several input streams of vertex data where each stream is read from memory by the vertex loader component.Vertices from each stream can be transformed, moved or combined in the 3D space. The shader can also add lightning or change the perspective of the vertices.

After the vertex shader there are several more steps in the graphics pipeline. However, they are not relevant for this thesis and will not be explained here. See [16] for more information about each stage. See[6] or [7] for a more thorough explanation of the shader language.

## 2.4 The AMBA AXI Protocol

The Advanced Extensible Interface(AXI) protocol is a part of the Advanced Micro controller Bus Architecture(AMBA) family. The AXI protocol is a communication protocol suitable for high-performance, high-frequency system designs[17].

The AXI protocol uses separate address/control and data phases. The protocol supports unaligned transfers, burst transactions, multiple outstanding addresses and out-of-order transactions[17]. Figure 1 shows the bus structure of an example system using the AXI and APB protocols.

The vertex loader component in Mali uses the AXI protocol. It reads vertex data in transactions of 32bytes. The external AXI bus width from Mali is 128 bits. This means that the AXI requests from the vertex loader will result in incremental bursts with two 16-byte(128bit) transfers in each burst. The vertex loader is used to read data from the fractal generator.

## 2.5 The AMBA APB Protocol

The APB protocol is a communication protocol optimized for low power consumption and reduced interface complexity. The APB protocol can either be used with low-bandwidth peripherals that require less performance than the AXI protocol, or, it can be used to program control registers of peripheral devices[14].

In Mali, the APB protocol is used to configure internal control registers. Note

that there is no common external APB bus on the GPU, each APB interface is instead given a range of addresses on the AXI bus. Reads or writes to this range are converted to 32-bit APB signals ahead of the APB interfaces<sup>1</sup>.

#### 2.6 The PL301

When connecting several AXI slaves and one AXI master to the same AXI bus there needs to be a way to determine the intended target of an AXI request. This can be done by giving each slave a range of AXI addresses. ARM has a component called PL301 that can be inserted onto the bus and perform this type of address management. The address mapping in the PL301 can be configured using the ARM software AMBA-designer. The software outputs the complete Verilog code of the configured component.

#### 2.7 Hardware Verification

This section will explain the terms and techniques that will be used to verify the functionality of the fractal generator in Section 5.7.

Simulation-Based Verification is the most commonly used verification approach [12]. Simulation-based verification uses a test bench to apply input stimuli to, and record output from, a design. The output from the design is then compared to a reference output. Thus, simulation-based verification is a form of verification by redundancy [12].

Directed testing: Using the directed test approach, a list of tests that each concentrate on a set of specific features are obtained from the hardware specification. The list of tests is then used as a verification plan[22]. Test bench stimuli vectors are written manually to exercise this test, and examine the specific features, in the device-under-test(DUT). Once the test works, it is marked as successful in the verification plan, and the procedure is repeated for the next test[22].

Constrained random testing: In a complex design, the directed testing approach consumes a lot of time and resources. When the complexity doubles, it takes twice as long, or twice as many people to complete[22]. A faster methodology is needed in order to obtain a high amount of coverage.

$<sup>^1{\</sup>rm For}$  example, AXI requests in address range 0x0000-0x1000 could be routed to the APB interface on the geometry processor.

Constrained random testing(CRT) can help eliminate much of the manual nature of directed testing[1]. The CRT approach adds a component to the test bench which automatically generates random stimuli and applies it to the DUT. The stimuli can be constrained to emphasize certain aspects of the DUT, and to avoid illegal inputs to the design[12].

Coverage: When a test bench using CRT is is randomly testing the design states of a DUT, two important questions are: What have been tested by this stimuli? Have the test bench verified enough? [12][22] When using either CRT or directed testing, the answer to these questions, the verification progress, can be gauged using coverage.

Functional coverage is a measure of which design features have been exercised by the tests [22], it measures the implementational completeness and correctness of the functions obtained from the design specification[12]. It is closely tied to the design intent and is sometimes called specification coverage.

Code coverage provides insight into how thoroughly the code of a design is simulated by a test bench[12], it is the easiest way to measure verification progress [22] and can be measured automatically by simulator tools.

The Universal Verification Methodology The Universal Verification Methodology(UVM) is a complete methodology that codifies the best practices for efficient and exhaustive verification[21]. The UVM is implemented as a System Verilog class library, and consists of several object-oriented, reusable, UVM verification components(UVC).

The UVM and libraries provide:

- Infrastructure to partition the verification environment into specific, hierarchical and reusable components. The infrastructure also streamlines the creation of test bench environments.

- Built-in functions to perform common activities like printing, comparing and packing items.

- Module- and system level stimulus generation, where data can be randomized and configured according to the system state.

- Incorporating functional coverage and data checks using best-known practices.

# 3 The Vertex Array Generator

The background theory states that objects drawn in OpenGL ES are passed to the vertex shader as a stream of vertices. The vertex shader can then perform transformations on the stream. Thus, in order for Mali to do transformations on the landscape created by the fractal generator, the landscape vertices has to be provided to the vertex shader. The actual job of the fractal generator(in hardware) can be now be more precisely formulated. It has to do two specific tasks:

- 1. Calculate the number of iterations of each point in a given landscape with the Mandelbrot set equation.

- 2. Provide the landscape to the Mali GP as a stream of vertices.

This chapter presents a hardware fractal generator from a previous master thesis [4] and explains how it generates a stream of vertices. To avoid confusion with the fractal generator design in later chapters, the fractal generator in this chapter is from now on referred to as the vertex array generator(VAG). The discussions in Chapter 4 will use the VAG as a reference point  $^2$ .

**The Vertex Array Generator** The vertex array generator(VAG) implements the following algorithm to calculate the Mandelbrot set.

- 1. Take as input an area of the Mandelbrot set.

- 2. Calculate the height (using equation 1) of all vertices in a single row of the area, starting with the bottom row.

- 3. Store the row as a triangle strip of vertices (as explained in Chapter 2).

- 4. Triangle strip is ready, signal Mali for retrieval.

- 5. Transmit strip and go back to step two, calculating all the rows from bottom to top until the entire area is calculated and transmitted as triangle strips.

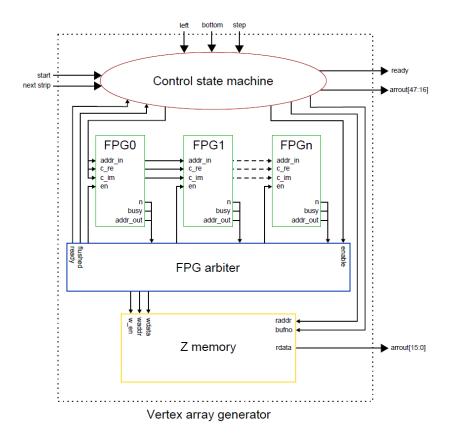

The VAG is implemented in hardware by several components as shown in Figure 6, each component and their roles in the algorithm is described below.

<sup>&</sup>lt;sup>2</sup>Chapter 4 explores different architectures that integrates a fractal generator with Mali.

Figure 6: The Architecture of the VAG. Taken from [4]

The control state machine(CSM) controls the execution of the algorithm. It takes as input three values, left, bottom and step size. These values, together with *NUMPOINTS* described below, define which area of the Mandelbrot set to draw. Left and bottom is the coordinates to the bottom left point in the area, step size is the distance between points. After receiving the area, the CSM calculates the xy- coordinates of each vertex point in the current strip of the area, these coordinates are then fed to the fractal point generators(FPGs).

The fractal point generator(FPG) does the calculations for each vertex at step two in the algorithm. It takes as input the x- and y- coordinates of a pixel, use the coordinates as the real and imaginary values of the point c in equation 1, and returns the z-coordinate; i.e., how many iterations it takes to determine if the pixel is in the Mandelbrot set or not. The VAG can contain several FPGs to calculate z-coordinates in parallel.

The FPG arbiter decides which of the FPGs that get to do calculations on a xy-coordinate from the CSM, it keeps track of which FPGs are busy and free. The FPG arbiter is also responsible for storing results from the FPGs into the Z-memory.

All the vertices of the current triangle strip is stored in the Z memory. The Z memory consists of two buffers with space to contain NUMPOINTS vertex coordinates(x,y,z). NUMPOINTS is a constant parameter set ahead of runtime, where the entire fractal has a resolution of  $NUMPOINTS \cdot NUMPOINTS$ . The CSM keeps track of which buffer to store coordinates in and avoids recalculating z-coordinates that was calculated the previous triangle strip.

All coordinates in the VAG are represented by 16bit GL float values. This datatype was chosen instead of the 32bit equivalent to save bandwith when transferring the vertices to Mali.

## 4 Architecture Exploration

This chapter will examine different architectures that integrate the fractal generator and Mali. The chapter will discuss the advantages and disadvantages of each architecture, and ultimately use the discussion to choose a fractal generator design for Verilog implementation.

#### 4.1 The Vertex Array Generator as an AXI Slave

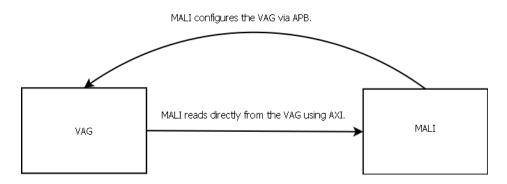

As described in the previous chapter, the vertex array generator(VAG) outputs its vertex data using triangle strips. Drawing a frame is done strip by strip from bottom to top. One possible way to integrate the vertex array generator with Mali is to connect the VAG as a slave to the AXI bus from the Mali L2 cache(Figure 7). Mali can then request strips one at the time from the VAG with, slightly modified, AXI requests. The area of the Mandelbrot set to draw from could be specified by extending the VAG with an APB slave. This architecture is a very memory efficient design since the all

Figure 7: The Vertex Array Generator as an AXI slave.

the coordinates (x, y and z) are transferred directly, i.e., not being stored in memory ahead of Mali (Mali will store data later though). There are however many disadvantages to this integration.

The main disadvantage with this architecture is that Mali has no say in which order the vertices are incoming, the AXI address does nothing, Mali has to read strip by strip. This is unacceptable, since the AXI bus from the L2 cache does not always request data in the same order. Mali would have to buffer all the vertexes internally and wait for the correct vertex before continuing. Thus, the design needs to support random access to the z-coordinates. Another disadvantage is that Mali would have to check for a new strip very often, and be ready to receive data constantly, otherwise the VAG would stop when the Z memory got full. Polling like this would consume time from the L2, and the VAG would be a bottleneck for the overall performance of the system. An improvement would be to transfer data from the VAG to a buffer connected to the bus, like a cache, and then transfer data in bursts. Unfortunately, the vertex shader could still end up waiting really long for a coordinate, if it was not included in the previous burst.

#### 4.2 The Vertex Array Generator with DMA

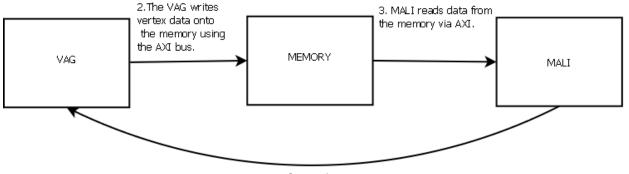

Another way to integrate by using the vertex array generator is to make it a master on the AXI bus and transfer data to the system RAM instead of Mali(Figure 8). With this solution Mali can ask for data from the RAM when it chooses, and random access would be supported, when the VAG is finished with a frame.

1.MALI configures the VAG via APB

Figure 8: The Vertex Array Generator as an AXI master(DMA).

However, the arrays would still come in order and, if a Mali requests a vertex not yet in the RAM, it could take a long time before the vertex is ready. In addition this would require double traffic on the RAM bus, since data would be transferred to the RAM from the VAG, and then to Mali from the RAM. Bus traffic is already a bottleneck in the Mali system(source) so this is a large deterrent.

Another big disadvantage to using the VAG, in both the previous methods, is that the VAG transfers all the coordinates of a vertex(x,y and z) via the triangle strips. This is unnecessary since the xy-coordinates of the Mandelbrot set are not needed to draw the landscape, they are only needed to calculate the height at each point. Instead, a flat landscape with static xy-coordinates, stored in memory, can be used as a frame for all the fractal landscapes. When drawing the landscape, the z-coordinates are read from the fractal generator and the xy-coordinates are read from the static landscape. As long as the total number of points are the same, and the z-coordinates are placed in the correct order, the landscape will be correct.

Using static xy-coordinates is a big advantage since it greatly reduces the traffic between the fractal generator and Mali. Thus, the xy-coordinates that are transferred to Mali from the fractal generator should rather be stored by using vertex buffer objects in OpenGL ES. In theory, this would enable Mali to store the entire static landscape in cache. In addition to this, the saved bandwidth from the static xy-coordinates can be used to change the representation of the coordinates from 16 to 32bits. This will allow the fractal generator to zoom in further on the Mandelbrot set before losing detail from rounding of the decimal numbers.

One last disadvantage for the VAG is that the VAG forces Mali to use the GL\_TRIANGLE\_STRIP method when drawing the landscape with OpenGL ES. This is mostly a theoretical disadvantage, since triangle strips are good for landscapes and one would rarely wish to use another drawing method.

#### 4.3 Fractal Generator With Cache

As discussed in the above sections, there are several disadvantages when connecting the vertex array generator with Mali. This section will present a new fractal generator that does not use the VAG. The new fractal generator will use the discussions above as a basis. It will reuse the good elements of the VAG and redesign the bad.

The new design will use the fractal point generators from the VAG to calculate the z-coordinates. No disadvantages have been connected to this component. It will also use the same method as the VAG to describe an area of the Mandelbrot set, except that it will use the xy-coordinates of the top-left corner and step size between points. This is instead of the bottom-left corner and seems a more intuitive way to define an area, mostly personal preference. The initial xy-coordinates will be referred to as x0 and y0 throughout the thesis. The rest of the fractal generator design is new and is made to avoid the disadvantages discussed above.

The new fractal generator is connected to the Mali AXI bus as an AXI slave.

The fractal generator consists of four main components described below. The components are connected, and draw a frame, as described in Figure 9.

- The APB interface: This interface allows an APB master to configure hardware registers inside the fractal generator. The registers decide which area of the Mandelbrot set the z-coordinates will be calculated from.

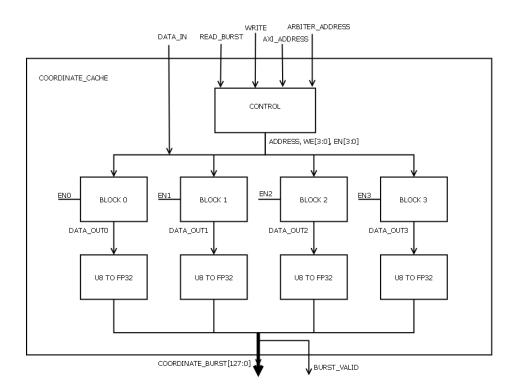

- The coordinate cache: A cache where the z-coordinates are stored as they are calculated, the cache is built up by several RAMs pasted together.

- The AXI interface: This component is responsible for answering AXI requests. Based on the address of a request, the AXI interface tries to read the corresponding z-coordinates from the coordinate cache. If the coordinates are not there, the AXI interface signals the arbiter to calculate them. After reading the coordinates they are transmitted on the AXI bus.

- The arbiter: This module uses the values of the APB registers to calculate the x- and y-coordinates of all the vertices in the chosen area of the Mandelbrot set. These coordinates are then *arbitrated* to a parameterized number of fractal point generators[4]. The FPGs calculate the number of iterations for each point and the resulting z-coordinates are stored in the coordinate cache.

The landscapes that the fractal generator generate consist of a static number of vertices. The number is set by a parameter, NUMPOINTS, and is equal to  $NUMPOINTS^2$ . Another parameterized value in the design is the number of FPG units inside the arbiter, this value decides how many z-coordinates that can be calculated in parallel. These parameters are the same as used in the VAG [4] and are presented further in Section 5.1.

This architecture has several advantages when compared to the ones using the VAG. Most importantly it supports random access of vertices by AXI addressing. Furthermore, continually calculating coordinates and using a cache means that Mali can request coordinates when it wants to, without affecting the performance of the fractal generator. No polling is required. In addition to this, the architecture saves bandwidth since it only transfers zcoordinates, and since it doesn't use hardware triangle strips it is not limited to using GL\_TRIANGLE\_STRIP in OpenGL ES.

Figure 9: Structure of the Fractal Generator and how it draws a frame.

This architecture combats all of the disadvantages seen when using the VAG. It has been selected for implementation in Verilog. A detailed description of the design is presented in the next chapter.

# 5 Fractal Generator Design

The previous chapter chose a hardware architecture for the fractal generator and explained its general functionality (Section 4.3). This chapter describes the functionality of the fractal generator in detail by presenting the fractal generator's submodules. In addition to this, the chapter discusses some alternative implementations of each module and explains why the chosen implementation has been selected.

Section 5.1 presents the configuration parameters of the fractal generator and the data types used to represent coordinates used by the fractal generator.

Section 4.3 states that the AXI interface tries to read z-coordinates from the cache based on the received AXI address. This requires a predefined relationship between AXI addresses and each vertex(x,y,z) in the fractal landscape. A predefined relationship enables Mali to request the z-coordinates of specific xy-pairs by setting the current AXI address to the address that is mapped to the wanted coordinate.

Section 5.2 explains how the fractal generator maps the vertices internally and how to translate from an AXI address to a given vertex, the actual translation is done by the AXI interface.

The following sections explain the functionality and Verilog implementation of each submodule of the fractal generator (Figure 9).

### 5.1 Configuration Parameters and Data Types

This section describes the three configurable parameters in the fractal generator. It also describes the data types used by the fractal generator.

**NUMPOINTS** This parameter sets the amount of total points in the fractal made by the fractal generator. The fractal generator creates a square fractal of  $NUMPOINTS \cdot NUMPOINTS$  z-coordinates. This parameter together with the APB configuration registers decide which area of the Mandelbrot set to cover with the fractal. The NUMPOINTS parameter is limited to be a power of two, this is done to reduce calculations with the parameter to bit-shift operations.

The current OpenGL ES demo uses one index array to describe a fractal. Since the index array is limited by the data type unsigned short, the maximum value of NUMPOINTS with this implementation is  $128.^3$  Unless drawing very small landscapes, 128 is recommended as the standard value for this parameter. The resolution of the final landscape is further discussed in Section 7.3.1.

- **NUMUNITS** This is the number of FPGs in the system. The parameter configures the amount of z-coordinates that can be calculated in parallel. Increasing this parameter will increase the performance of the fractal generator at the cost of area. Chapter 8 examines the performance of the fractal generator with varying NUMUNITS.

- MAX\_ITERATIONS This is the iteration limit the FPGs use when determining if a point is in the Mandelbrot set or not. If the iterations reach this limit, the point is defined as part of the Mandelbrot set.

Lowering this number will increase the performance of the fractal generator, since each point will be finished faster by the FPGs. However, it will also reduce the detail of the produced image, since the maximum height is limited. The points that would've gotten higher iterations will all have the same height and color. Chapter 8 will show an example of this.

**Data Types** As mentioned in Section 4.2, the amount of bits used to represent coordinates in the Mandelbrot set affect the maximum zoom level before losing detail. This loss of detail is caused by rounding decimal numbers when they reach the limits of their data types. Increasing the size of the data types, e.g. from 16bit to 32bit floating point(fp32) values, increases the details of the landscape at the cost of bandwidth and storage<sup>4</sup>. Since many interesting aspects of the Mandelbrot set appear at large levels of zoom, it was decided to use fp32 values when calculating on the Mandelbrot set internally.

This means that the inputs to the APB interface are 32 bits for the initial coordinate(x0,y0) and step size. In addition to this, the internal calculations on the fractal landscape are done with fp32 operations. Since fp32 calculations are done in one cycle, the internal performance is not affected by choosing this data type, but storing the temporary coordinates take more space. See Section 5.5 for more information about the calculations.

The output of the fractal generator are the z-coordinates of the landscape.

<sup>&</sup>lt;sup>3</sup>Since the vertex array with NUMPOINTS = 256 would have indexes above the range of unsigned short

<sup>&</sup>lt;sup>4</sup>The thesis uses the IEEE754 binary32 standard to represent numbers in fp32.

Since the z-coordinates are the number of iterations in the Mandelbrot set equation, they can be represented as integers without loss of detail. Thus, the z-coordinates are stored as integers internally.

However, the programming language used to write the vertex-shader and fragment-shader (Section 7.1), does not allow a stream of integers as input [11, p. 31]. It only allows floating point numbers. Thus, the z-coordinates are converted to fp32 on the output of the cache. It would be better to convert the coordinates to fp16, but since the limitation by the shader language was discovered late in the design, and ARM had finished unsigned integer to fp32 converters, fp32 it was chosen instead. This causes a bit of performance loss since reading data requires twice as many bursts. Since it does not affect the internal performance, and the internal performance of the fractal generator will be the bottleneck in the system<sup>5</sup>, converting to fp16 is left as future work.

## 5.2 Relationship Between AXI address and Coordinates of a Fractal

As explained above there needs to be a predetermined method of translation between an AXI address and a given fractal vertex, this section explains how the translation is performed.

Internally, the fractal generator maps the z-coordinates to the address range 0 to  $NUMPOINTS^2 - 1$  (Figure 10). The first row of the fractal is given addresses 0 to NUMPOINTS - 1, with increasing address from left to right. There is a total of NUMPOINTS rows where each row is divided into addresses like the first. Thus, the address range of row n is given by the below equation.

$row \ n \ address \ range = [n * NUMPOINTS (n * NUMPOINTS) + NUMPOINTS - 1)$   $where \ 0 <= n <= NUMPOINTS - 1$ (2)

This address setup enables easy translation from an address to a specific fractal vertex: The row of the vertex is found by address/NUMPOINTS and the column is found by address mod NUMPOINTS. Using the parameters set via the APB interface, the column and row can be used to calculate the exact x- and y-coordinates (Section 5.5), which then can be used to calculate the z-coordinates with the Mandelbrot equation (1. To ensure fast address translation in hardware, NUMPOINTS is limited to be a power of

<sup>&</sup>lt;sup>5</sup>Mali only has to read data while the fractal generator is calculating.

| 0                                                                                  | 1 | 2 |  | 00 | 04 | 08 |

|------------------------------------------------------------------------------------|---|---|--|----|----|----|

| 3                                                                                  | 4 | 5 |  | ос | 10 | 14 |

| 6                                                                                  | 7 | 8 |  | 18 | 1C | 20 |

| Internal addresses.<br>External addresses.<br>Note that all the external addresses |   |   |  |    |    |    |

Figure 10: Internal and external AXI address mapping of the vertices in a 3x3 fractal.

are prefixed with 0x1000 00

two, which reduces the calculations of x and y to shift operations. See the arbiter source code for implementation, and see Section 5.1 for setting the NUMPOINTS parameter.

Externally, the AXI bus uses byte addressing and the fractal generator is mapped to a specific address range on the bus. Otherwise the mapping is the same as the internal; coordinates are address mapped in row major order(Figure 10)<sup>6</sup>.

The AXI Interface is the only module that sees the external requests from Mali, and it has to convert the addresses to the internal format before communicating with the other modules. The conversion is done by simply ignoring the left most bits of the AXI address, and dividing the resulting number by four(by shift). The leftmost bits can be removed since they are used to select components on the AXI bus, and this selection is performed ahead of the AXI Interface. Since each coordinate is four bytes, the internal address can then be found by dividing by four.

#### 5.2.1 Discussion

Why not use the external mapping internally and remove the conversion? Using the external mapping as the internal mapping and removing the conversion would simplify the AXI interface. However, this would complicate

<sup>&</sup>lt;sup>6</sup>The mappings are not equal by coincidence, the external mapping is set by the index array in the OpenGL ES demo.

several of the internal calculations in the fractal generator. For instance, the arbiter uses the address to calculate the row and column of the xy-coordinate in the Mandelbrot set(Equation 1 on page 4). To calculate this with the external mapping, one would have to both remove the leftmost bits and divide by four(to find the column). This operation is identical to the address translation so nothing is saved.

Another example is in the coordinate cache, the cache use the address to determine which rams to read and write from. To properly determine the ram column, the address would have to be converted in this component as well. Thus, it was chosen to separate the internal and external mappings.

No other internal mappings have been considered since no drawbacks have been connected to the current one. One could switch to column major addressing in both hardware and the demo, but the performance would be the same.

## 5.3 The APB Interface

The APB interface enables an APB master, e.g. the Mali driver, to configure hardware registers in the fractal generator. The registers control which area of the Mandelbrot set that is used by the fractal generator when drawing a frame. Changing the contents of these registers thus change the landscape drawn by the fractal generator.

#### 5.3.1 Verilog Implementation

The APB interface is implemented in Verilog as a finite state machine. When the interface detects an incoming APB write, it stores the incoming data in one of the following registers. The destination register is determined by the APB address.

- The x0-coordinate register, which determines the x coordinate, in the Mandelbrot set, of the top left point of the fractal.

- The y0-coordinate register, which determines the y-coordinate, in the Mandelbrot set, of the top-left point of the fractal.

- The step size register, which determines the distance between each point in the chosen area of the Mandelbrot set. The step size value determines the zoom-level of the area to be drawn from.

After storing data in one of the registers, the interface signals to the APB master that data has been received and that it is ready to receive new data.

In addition to the above registers, the APB interface also provides read access to a couple of debug registers. These registers provide information from the arbiter and the AXI interface and can be read via APB. These registers are not in use during normal operation, but are useful for debugging purposes. For example, the Mali driver can read from these registers to confirm that the fractal generator has been configured properly and that it has started its calculations.

#### 5.3.2 Discussion

The APB interface is a very light-weight interface; it only uses a small subset of the APB protocol to communicate. Since it so small, does no computation, and no disadvantages have been observed, no alternative APB interfaces have been considered.

### 5.4 The AXI Interface

The AXI interface module is defined as an AXI slave device; it cannot initiate AXI transfers on the bus[17]. Its main responsibility is to wait for an AXI request from Mali and respond with the z-coordinates that correspond to the AXI address of the request. The coordinates are read from the coordinate cache described in Section 5.6 and transmitted on the bus in two bursts with four coordinates(128 bit) each burst. Note that an AXI request only provides the address of the first coordinate in the transfer; the AXI interface automatically has to read and transmit subsequent coordinates based on the initial AXI address, and the burst and transfer length signals.<sup>7</sup>

#### 5.4.1 Verilog Implementation

The AXI interface is implemented as a finite state machine. When there is an AXI request, the AXI interface checks if the first four coordinates of the transfer are in the coordinate cache. If they are ready the AXI interface checks the next four. On the other hand, if they are not, the AXI interface

<sup>&</sup>lt;sup>7</sup>The AXI interface only supports transfers with one or two bursts, which equals four or eight coordinates. The Mali vertex loader will never ask for more than two bursts, so no more is needed.

interrupts the arbiter with the address of the first missing coordinate. The arbiter will then prioritize the request from the AXI interface and calculate the missing coordinates. The AXI interface proceeds to wait for the coordinates to be ready. After all eight coordinates are ready the AXI interface examines if Mali is ready to receive the burst. If Mali is ready, the coordinates are sent in two cycles, four coordinates each cycle. After transmission, the AXI interface goes back to the waiting state and waits for a new request.

#### 5.4.2 Discussion

The AXI part of the AXI interface is optimized for communication with the vertex loader in Mali, as the APB interface it uses the bare minimum of signals to communicate. No other implementations have been considered on this part. On the other hand, several implementations have been considered on the reading of coordinates from the coordinate cache and how to check if a coordinate is valid(i.e. calculated by the arbiter and is not belonging to an old frame). Currently, all the coordinates in a burst is read four at the time, and if one of them are not ready, the address of the first one is given to the Arbiter. It would also be possible to check the coordinates one by one, and only give the address of the missing one to the arbiter, but this would require more cycles to check. Also, since the arbiter calculates coordinates sequentially, it is likely that one missing coordinate in a burst means that the other coordinates are also missing. In this case, checking one and one coordinate would waste a lot of time compared to the chosen solution, since the arbiter would have to be interrupted several times in a row. See the discussion in the coordinate cache section for details on the validity check.

## 5.5 The Arbiter

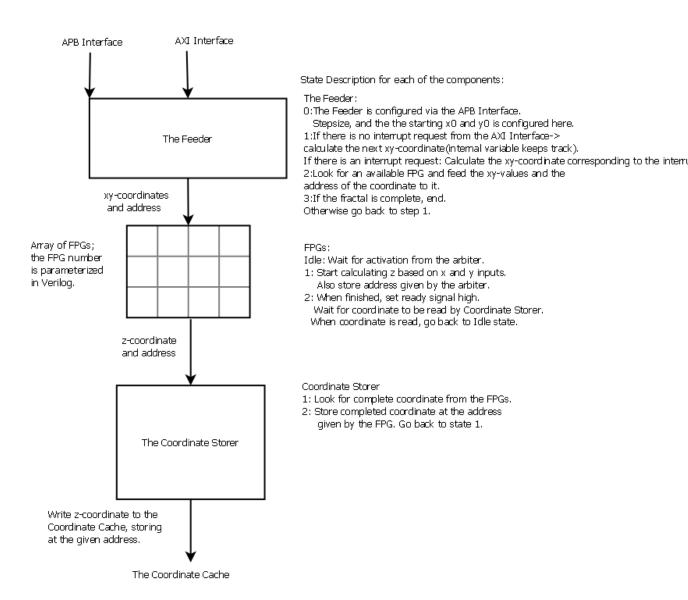

The primary function of the arbiter <sup>8</sup> is to calculate all the z-coordinate values of a fractal and store them in the coordinate cache. As displayed in Figure 11 the arbiter consists of several sub-components; a feeder, the fractal point generators (FPGs) and a coordinate storer. The number of FPGs is parameterized and determines the number of z-coordinates that can be calculated in parallel. The functionality of each component is explained below.

<sup>&</sup>lt;sup>8</sup>This is not a descriptive name, the module does more than arbitration, but good names are hard to find.

The job of the feeder is to feed x- and y-coordinates to the FPGs; the FPGs will then calculate the z-coordinate of the given vertex. The Feeder is given the initial coordinates and step size of the fractal landscape from the APB interface; once the values have been received the Feeder starts calculating the xy-coordinates of the vertices. When an xy-coordinate is ready it is fed to the first available FPG.

The feeder assumes that Mali will request the coordinates in incremental order, based on AXI addresses as specified in Section 5.2, so it calculates coordinates in row major order until the fractal is complete or there is an interrupt from the AXI interface. If there is an interrupt, the AXI interface just tried to read missing coordinates from the coordinate cache. These coordinates must be given priority since Mali is waiting for them. The feeder, after finishing the current coordinate, handles the interrupt by calculating the coordinates of the data burst that belongs to the address from the AXI <sup>9</sup>. Once the interrupt has been handled, the feeder continues to calculate from the position it was interrupted.

The FPG is taken from the work in [4] and is explained in Chapter 3. It uses Equation 1 to calculate the z-coordinate of a vertex, using the x- and y-coordinate of the vertex as input.

The coordinate storer reads finished z-coordinates from the FPGs and stores them in the coordinate cache.

#### 5.5.1 Verilog Implementation

The feeder is implemented as a state machine: At the initial state it checks for an interrupt from the AXI Interface. As explained above, the status of the interrupt decides which pair of xy-coordinates to calculate next. In the case of an interrupt, the feeder keeps track of its current position with an internal address register.

Calculation of coordinates is done according to the steps below; note that the feeder uses two memories to store finished xy-coordinates in, this is done to save calculations as the coordinates are used *NUMPOINTS* times in the calculations of a frame.

1. The coordinates of the top left vertex(x0,y0) and the step size between

<sup>&</sup>lt;sup>9</sup>The address given to the arbiter from the AXI interface is in the internal format described in Section 5.2. The arbiter converts this address into the corresponding xy-coordinate.

vertices of the fractal are read from the APB interface.

- 2. The row and column of the x,y,z vertex is found by translating the vertex address as described in Section 5.2.

- 3. The feeder checks if the xy-coordinates are in memory. If they are, they have already been calculated and is fed straight to an available FPG, skipping the next steps.

- 4. If the xy-coordinates are not in memory they are calculated:

```

y = y0 + (stepsize * rownumber)

x = x0 + (stepsize * columnnumber)

This step requires one 32bit floating-point adder and one 32bit floating-

point multiplier. In addition, it requires a 32bit fixed- to floating-

point converter to convert the row and column numbers. All these

components are provided by ARM libraries.

```

5. Finally, the coordinates are fed to an FPG and stored in memory for reuse at a later time.

The FPGs are taken straight from [4] so the implementation details are not presented here. See Chapter 3.

The coordinate storer is implemented as a state machine. It continuously checks if any of the FPGs are finished with a coordinate. When an FPG finishes, its z-coordinate is written to the z-coordinate's address in the coordinate cache.

#### 5.5.2 Discussion

The arbiter has many design options, especially regarding the calculation and storing of xy-coordinates. Currently it calculates the xy-coordinates and then stores them in a memory. Another option is to not have memories; this would save area at the cost of performance. Since performance is the most important criteria for the fractal generator, memories are used.