# Design of a Linear FMCW Radar Synthesizer with Focus on Phase Noise

Ruben Undheim

Master of Science in Electronics Submission date: February 2012 Supervisor: Egil Eide, IET

Co-supervisor: Harald Rosshaug, Kongsberg Seatex AS

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## **Problem Description**

Student: Ruben Undheim

Title: Design of a Linear FMCW Radar Synthesizer With Focus on Phase Noise

#### Text:

Phase noise is the most important performance parameter in phase locked synthesizers and local oscillators of communication equipment and radars. In this exercise, a synthesizer will be constructed which will be used in a range/bearing measurement system based on FMCW radar principles.

#### Tasks:

- Theoretical study of phase noise in phase locked loops

- Analysis of the importance of the phase noise for the performance of a FMCW based range/bearing measurement system

- A survey of alternative topologies for the synthesizer of an FMCW-based range/bearing measurement system. Possible frequency bands are: 5.46 GHz 5.64 GHz and 9.2 GHz 9.3GHz

- Construction of synthesizer based on chosen topology

External supervisor: Harald Rosshaug, Kongsberg Seatex AS

Internal supervisor: Egil Eide

### Abstract

The linear FMCW radar has become more and more popular in recent years mainly due to advances in digital signal processing and the good performance of the radar at close ranges. What puts limits to the performance is mainly phase noise. Because transmission and reception happen simultaneously, the phase noise will limit the maximum power that should be used and hence also the ability to detect weak targets. By ensuring during the design process that the phase noise is low, the radar's performance will thus get better. This thesis describes the construction of a FMCW radar frequency synthesizer where the focus is mainly on phase noise. The functionality of the circuit is shown to be successful, but there is more phase noise than what is predicted. Several causes for this are discussed. Important background theory about radars, phase noise and phase-locked loops is presented and several simulations are performed in order to get a better understanding. The conclusion of the work is that it is not very hard to build a synthesizer, but in order to tweak the phase noise performance to be as good as the linear theory tells it to be, careful attention must be paid during all stages of the design.

## **Preface**

This thesis concludes my Master Degree in Electronics Engineering at the Norwegian University of Science and Technology (NTNU). It was carried out during the Winter of 2011/2012 and submitted to NTNU, Trondheim February 20th, 2012. The focus is mainly on how a synthesizer for an FMCW radar can be built, what its performance issues may be, and then getting a thoroughly understanding of phase noise, the PLL and radar systems in general. It involves general circuit design, RF circuit design, PCB layout, microcontroller programming, simulations, soldering, measurements etc.

I would like to thank Kongsberg Seatex AS for letting me work there and for funding the project, and especially my supervisor, Harald Rosshaug, for the assistance I have received during the work with the thesis.

I would also like to thank Egil Eide at NTNU for the questions he has helped me clear out.

Trondheim, February 20th, 2012 Ruben Undheim

# Contents

| 1 | Intr | roduction                                      | 1  |

|---|------|------------------------------------------------|----|

| 2 | Rac  | lars                                           | 3  |

|   | 2.1  | Pulse Radar                                    | 4  |

|   |      | 2.1.1 Pulse-Doppler signal processing          | 7  |

|   | 2.2  | CW Radar                                       | 8  |

|   | 2.3  | FMCW Radar                                     | 8  |

|   |      | 2.3.1 Ambiguity                                | 12 |

|   |      | 2.3.2 Target ID                                | 13 |

|   | 2.4  | Frequencies                                    | 14 |

| 3 | Pha  | ase Noise                                      | 17 |

|   | 3.1  | Internally Generated Noise                     | 17 |

|   |      | 3.1.1 Thermal noise                            | 17 |

|   |      | 3.1.2 Flicker noise                            | 18 |

|   | 3.2  | External Noise                                 | 18 |

|   | 3.3  | What is Phase Noise?                           | 19 |

|   | 3.4  | Why Phase Noise?                               | 24 |

|   |      | 3.4.1 Leeson's equation                        | 24 |

|   |      | 3.4.2 LTV model                                | 26 |

|   |      | 3.4.3 Nonlinear models                         | 28 |

|   | 3.5  | Propagation in Devices                         | 29 |

|   |      | 3.5.1 Mixers                                   | 29 |

|   |      | 3.5.2 Frequency multipliers                    | 30 |

|   | 3.6  | Measurement Techniques                         | 30 |

|   |      | 3.6.1 Down-conversion and filtering of carrier | 31 |

|   |      | 3.6.2 Quadrature method                        | 31 |

|   |      | 3.6.3 Delay line discriminator                 | 32 |

|   | 3.7  | Jitter                                         | 32 |

| 4 | Pha  | ase Locked Loops                               | 35 |

|   | 4.1  | Phase Detectors                                | 37 |

|   |      | 4.1.1 PFD                                      | 37 |

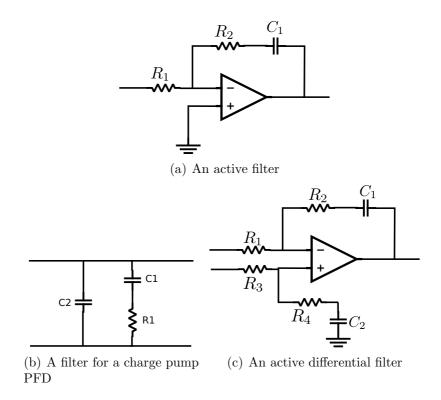

|   | 4.2  | Filter                                         | 38 |

|   | 4.3  | Full Transfer Function                         | 40 |

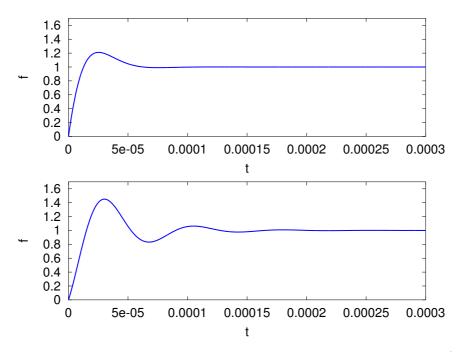

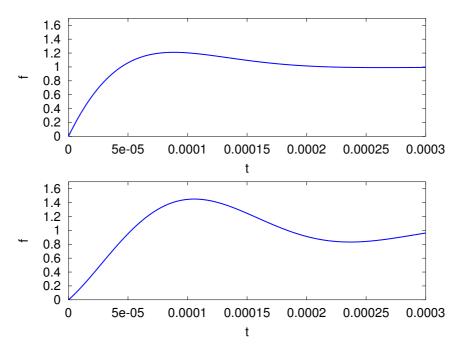

|   | 4.4  | Tracking                                       | 41 |

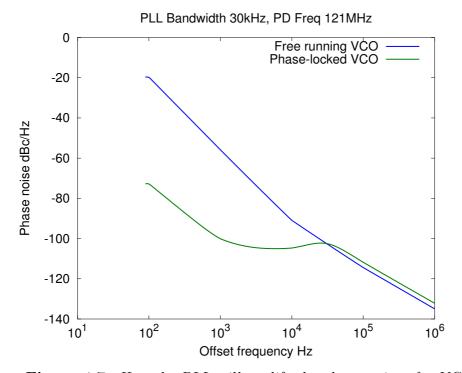

|   | 4.5  | Phase Noise in Phase Locked Loops              | 43 |

vi *CONTENTS*

| <b>5</b> | Degradation Effects in FMCW Radars |                                                                 |     |  |  |

|----------|------------------------------------|-----------------------------------------------------------------|-----|--|--|

|          | 5.1                                | Phase Noise                                                     | 45  |  |  |

|          |                                    | 5.1.1 Contribution to the unaccuracy of the distance estimation | 47  |  |  |

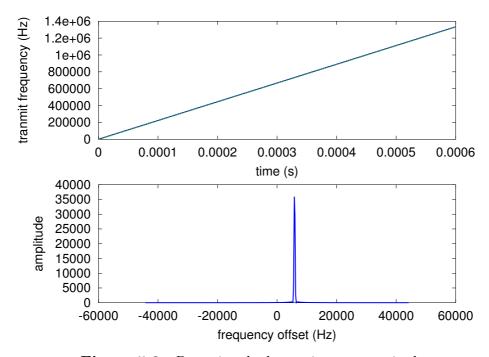

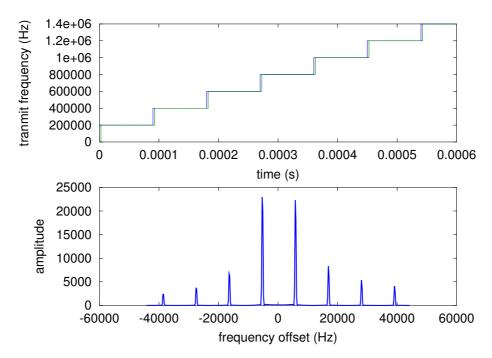

|          | 5.2                                | Linearity and Quantization of Sweep                             | 48  |  |  |

| 6        | Top                                | ology                                                           | 53  |  |  |

| Ū        | 6.1                                | Possible Solutions                                              | 53  |  |  |

|          | 0.1                                | 6.1.1 Open loop                                                 | 53  |  |  |

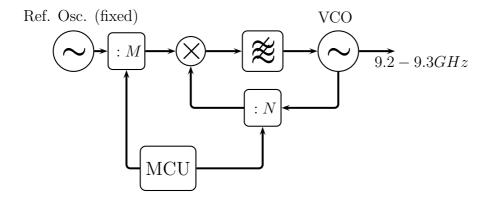

|          |                                    | 6.1.2 PLL with variable prescaler                               | 54  |  |  |

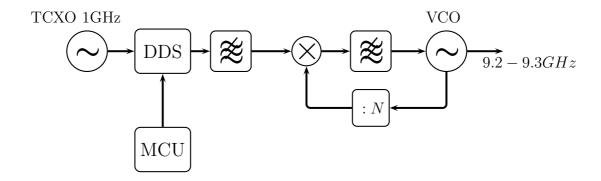

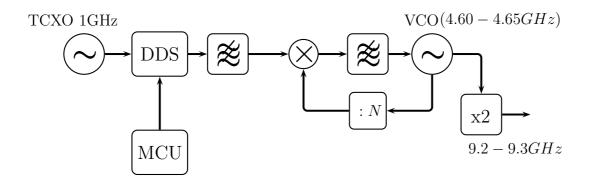

|          |                                    | 6.1.3 DDS as the reference oscillator for the PLL               | 55  |  |  |

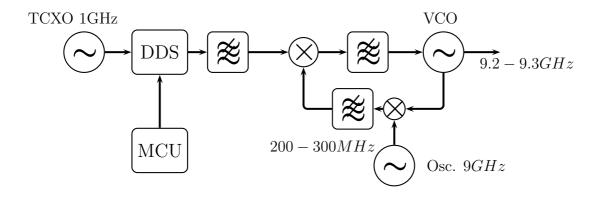

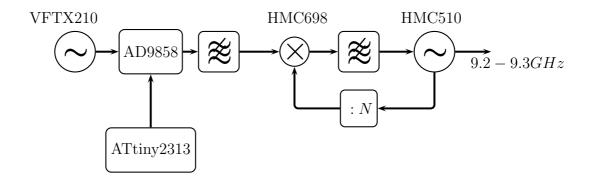

|          |                                    | 6.1.4 DDS output mixed directly with fixed oscillator           | 60  |  |  |

|          | 6.2                                | Chosen Topology                                                 | 60  |  |  |

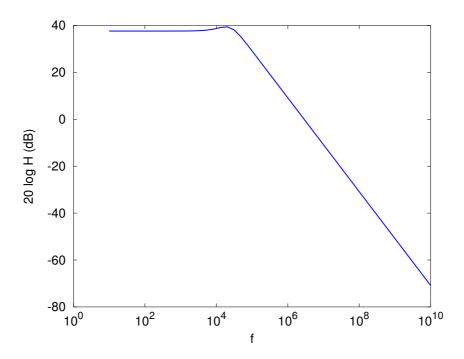

|          | ·-                                 | 6.2.1 Phase noise predictions                                   | 63  |  |  |

|          |                                    | 6.2.2 Bode diagram                                              | 65  |  |  |

| _        | ~.                                 |                                                                 |     |  |  |

| 7        |                                    | cuit Design                                                     | 67  |  |  |

|          | 7.1                                | Components                                                      | 67  |  |  |

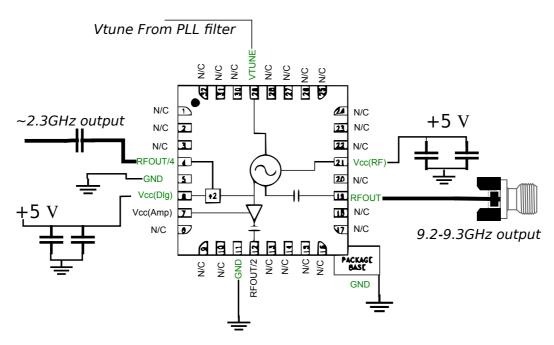

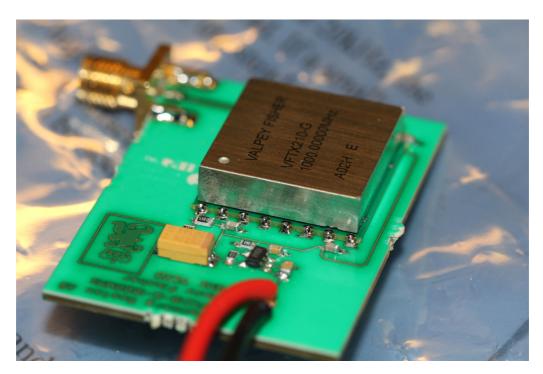

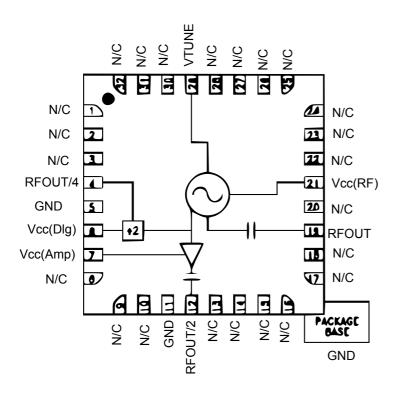

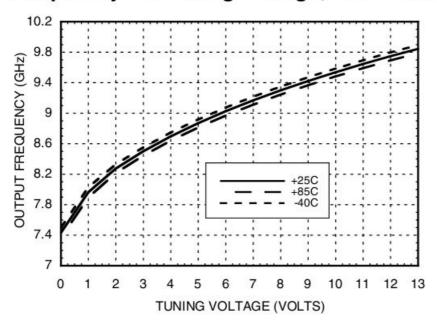

|          |                                    | 7.1.1 VCO                                                       | 67  |  |  |

|          |                                    | 7.1.2 DDS                                                       | 68  |  |  |

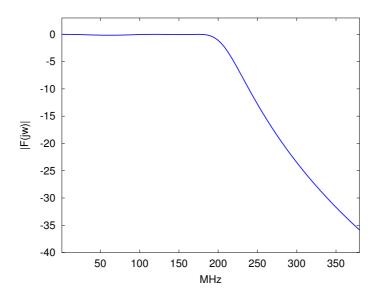

|          |                                    | 7.1.3 Low-pass filter                                           | 72  |  |  |

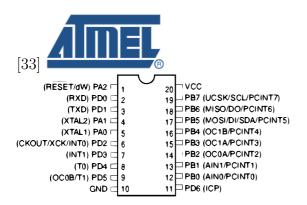

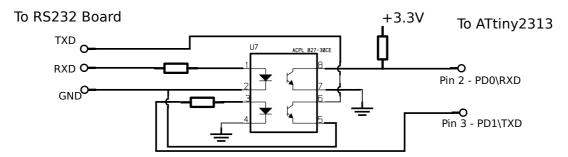

|          |                                    | 7.1.4 Microcontroller                                           | 72  |  |  |

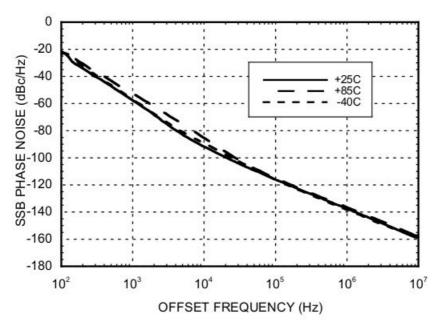

|          |                                    | 7.1.5 Phase detector                                            | 74  |  |  |

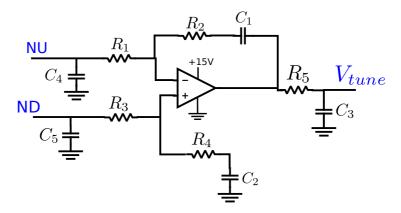

|          |                                    | 7.1.6 Loop filter                                               | 75  |  |  |

|          |                                    | 7.1.7 Frequency reference                                       | 77  |  |  |

|          | <b>7</b> 0                         | 7.1.8 Voltage regulator                                         | 78  |  |  |

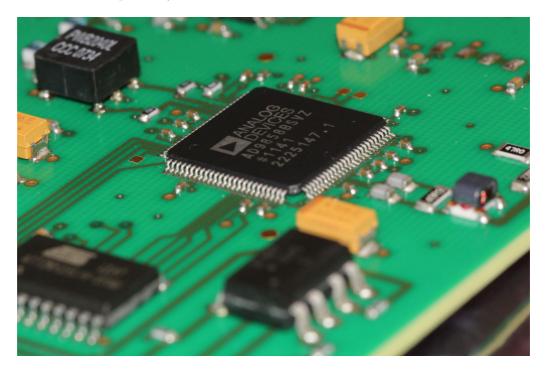

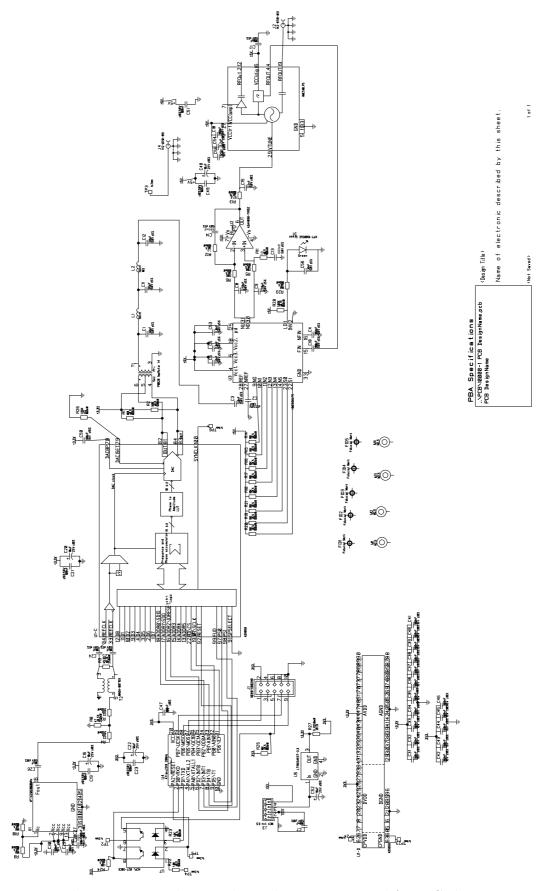

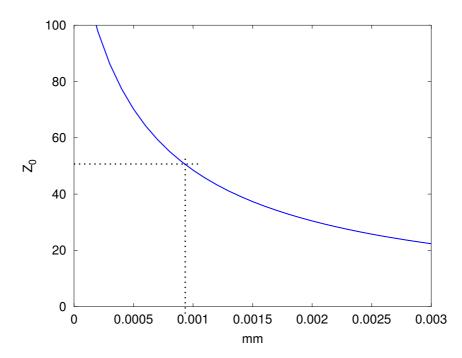

|          | 7.2                                | Schematic                                                       | 78  |  |  |

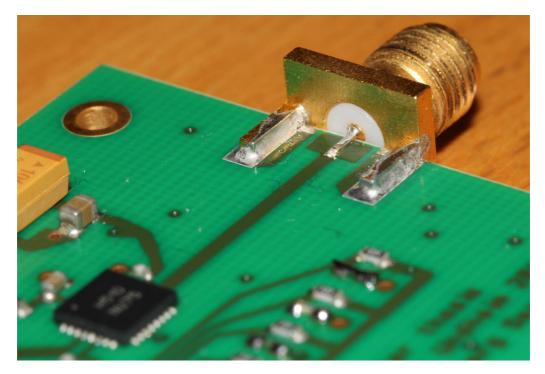

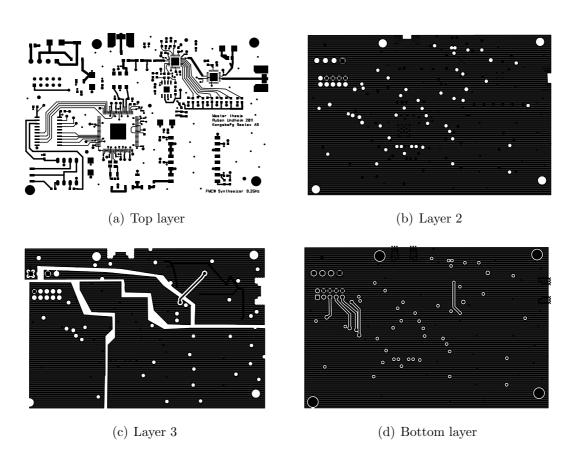

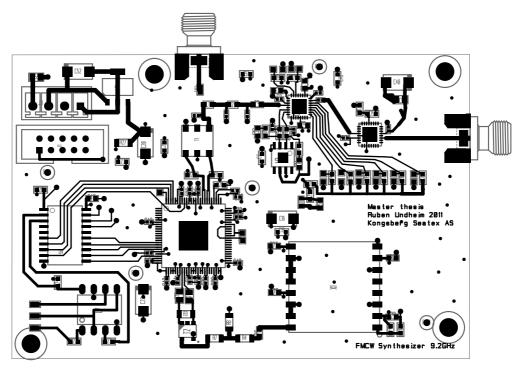

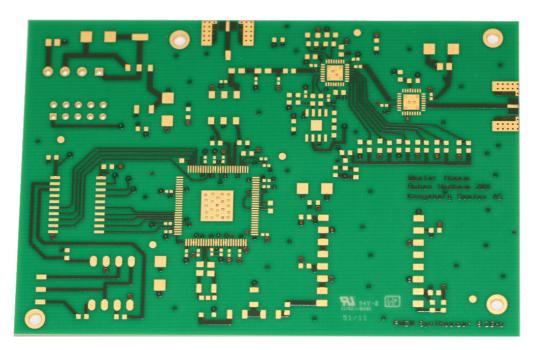

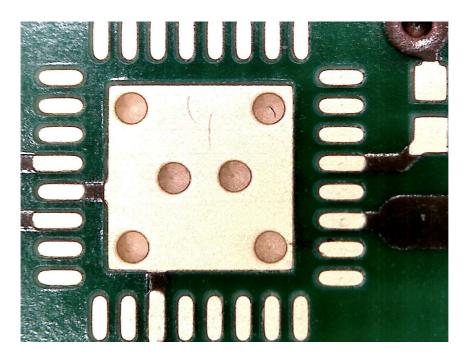

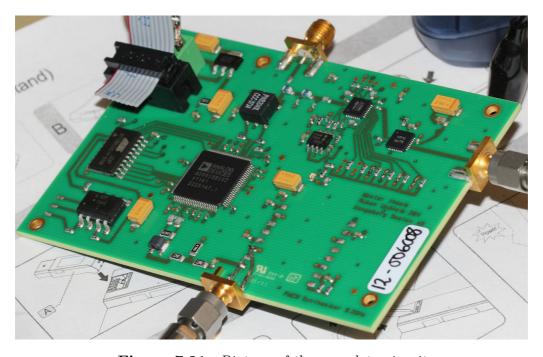

|          | 7.3                                | PCB                                                             | 78  |  |  |

|          | - 4                                | 7.3.1 Finished design                                           | 81  |  |  |

|          | 7.4                                | Verification of Board                                           | 85  |  |  |

| 8        | Mea                                | surements                                                       | 89  |  |  |

|          | 8.1                                | Equipment                                                       | 89  |  |  |

|          | 8.2                                | Procedure                                                       | 89  |  |  |

|          |                                    | 8.2.1 Phase Noise                                               | 89  |  |  |

|          |                                    | 8.2.2 Step Response                                             | 91  |  |  |

|          |                                    | 8.2.3 Sweep                                                     | 91  |  |  |

| 9        | Resi                               | ults                                                            | 93  |  |  |

| •        | 9.1                                | Phase Noise                                                     | 94  |  |  |

|          | 9.2                                | Frequency Step                                                  | 98  |  |  |

|          | 9.3                                | Sweep                                                           |     |  |  |

| 10       | Dias                               | cussion                                                         | 103 |  |  |

| τO       |                                    | Frequency Step Measurements                                     |     |  |  |

|          |                                    | Phase Noise Measurements                                        |     |  |  |

|          |                                    | Frequency Sweep Measurements                                    |     |  |  |

|          |                                    | - · · · -                                                       | 110 |  |  |

CONTENTS vii

| 11           | Conclusion                         | 113 |

|--------------|------------------------------------|-----|

|              | 11.1 Future Work                   | 113 |

| $\mathbf{A}$ | Source Code ATtiny2313             | 123 |

|              | A.1 ad9858control.h                | 123 |

|              | A.2 ad9858control.c                | 124 |

|              | A.3 main-fixedfrequency.c          | 127 |

|              | A.4 main-switchfreq.c              | 128 |

|              | A.5 main-sweeper.c                 | 128 |

|              | A.6 main-symsweeper.c              | 129 |

| В            | In-System Programming (ISP) of AVR | 131 |

| $\mathbf{C}$ | Source Code Octave                 | 133 |

|              | C.1 phasenoise-doall.m             | 133 |

|              | C.2 phasenoise1.m                  | 135 |

|              | C.3 phasenoise2.m                  | 137 |

|              | C.4 sweep.m                        | 138 |

|              | C.5 tracking-step.m                | 139 |

|              | C.6 cancellation.m                 | 142 |

| D            | Direct Digital Synthesis (DDS)     | 145 |

| ${f E}$      | Datasheets                         | 147 |

|              | E.1 HMC510LP5                      | 147 |

|              | E.2 HMC698LP5                      | 149 |

|              | E.3 AD9858                         | 152 |

|              | E.4 VFTX210                        | 155 |

|              | E.5 ATtiny2313                     | 156 |

viii CONTENTS

## Glossary

**AM:** Amplitude Modulation

CW: Continuous Wave

**DAC:** Digital to Analogue Converter

**DDS:** Direct Digital Synthesis

**DUT:** Device Under Test

**FFT:** Fast Fourier Transform

FM: Frequency Modulation

FMCW: Frequency Modulated Continuous Wave

**IF:** Intermediate Frequency

**ISF:** Impulse Sensitivity Function

LO: Local Oscillator

LTV: Linear, Time-Variant

MCU: Microcontroller Unit

OCXO: Oven-Controlled Crystal Oscillator

PCB: Printed Circuit Board

**PD:** Phase Detector

**PFD:** Phase/Frequency Detector

**PI:** Proportional-Integral (A regulator)

**PLL:** Phase Locked Loop

**PRF:** Pulse Repetition Frequency

**PRI:** Pulse Repetition Interval

**RBW:** Resolution Bandwidth

**RPC:** Reflected Power Canceller

SFDR: Spurious-free Dynamic Range

**SMA:** SubMiniature version A (coaxial connector)

SSB: Single Sideband

STC: Sensitivity Time Control

TCXO: Temperature-Compensated Crystal Oscillator

VBW: Video Bandwidth

VCO: Voltage Controlled Oscillator

# Chapter 1

## Introduction

In recent years, there has been a growing interest in the linear FMCW radar [1]. It has some properties that are not seen with the traditional pulse radar or its variety, the pulse-Doppler radar - the main advantage being higher performance at close ranges. This is very useful for radio navigation systems that are used to navigate near obstacles. A typical example is marine vessels. They are often relatively big, and the captain will often struggle to keep every part of the vessel under observation when navigating in narrow areas or in bad weather.

As in other fields of electronics and signal engineering, noise is an important issue. For the FMCW radar, the main worry is more specifically phase noise. This category of noise appears in all systems which employ oscillators. Because transmission and reception happen simultaneously in an FMCW radar, the phase noise will limit the maximum power that it makes sense to use and hence also the ability to detect weak targets. The fascinating and disturbing thing with phase noise is that it is very hard to get rid of when it first has appeared. Therefore it is of high importance to ensure that the oscillators in the circuit are stable and show good phase noise performance at many offset frequencies. Phase noise is not only important in radar systems but also in communication systems. It is the major contributor to undesired phenomena such as interchannel interference, leading to increased bit error rates. In radar- and communication technology, phase noise is regarded in the frequency domain, but in other fields, like digital design, it is regarded in the time domain where it is called jitter. Even here it may be of critical importance.

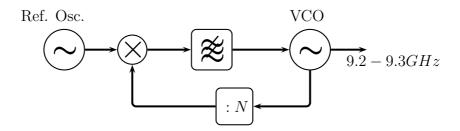

The aim of the thesis is to get an understanding of radar systems, investigate how they can be implemented and what put limits to their capability. Furthermore, a frequency synthesizer will be implemented which will be used in a linear FMCW radar in the frequency band of 9.2-9.3 GHz. It must provide a very clean sweep in this frequency range and therefore phase noise will be one main consideration. Different theories have appeared during the last decades which attempt to explain what phase noise is and how it appears [2, 3, 4]. There is still not complete agreement on these issues, and it therefore remains somewhat a mystery.

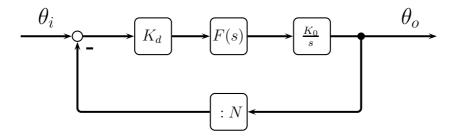

To be able to design a synthesizer for the FMCW radar, knowledge of many kinds of circuits and devices is required. Two circuits that are particularly much used

nowadays are the Phase-locked loop (PLL) and the Direct Digital Synthesizer (DDS). The PLL can be considered a linear control theory system when it is in lock, so that the analysis can be simplified. It consists of several important parts that need to be well understood. The DDS on the other hand, is mostly a digital circuit connected to the world with an on-chip DAC.

The following three chapters present radars, phase noise and phase-locked loops. Further Chapter 5 presents a discussion and some simulations of the degradation effects that appear in FMCW radars. Chapter 6 discusses different topologies that can be used for the design, while Chapter 7 presents the actual design. The thesis sums up with the measurement results of the radar synthesizer and a discussion.

# Chapter 2

# Radars

Radars use radio waves to estimate the distance, bearing and velocity of *something*. Something can either be one target, multiple targets or all targets in view as for imaging radars.

There are two main-types - the pulse radar and the continuous wave (CW) radar. They both have their advantages. In the beginning of the days of radio technology, the CW radar was the only one that was successfully made. [5] A single oscillator running at a constant frequency could be used to transmit a carrier and the reflected signal from a moving target would then result in a received Doppler shift<sup>1</sup>. This would then be proportional to the velocity of the target. It was first discovered accidentally when big ships near receivers caused changes to the received signal from a distant transmitter. This was a bistatic<sup>2</sup> radar, but later the concept was employed on purpose and the first real radar appeared. With this technology, it was not possible to measure the distance to the target, but moving targets could more or less easily be detected.

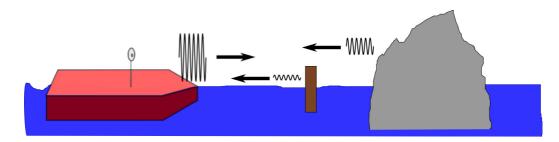

**Figure 2.1:** How marine vessels can use radars. In this case a pulse radar.

Later, when the technology allowed it, the pulse radar was made. Its principle is easy to understand, but at that time, it was not that easy to implement. It was necessary to transmit very short pulses of a clean radio signal, and then be completely silent for a while in order to receive the echo. The development of the pulse radar

<sup>&</sup>lt;sup>1</sup>This is a change in frequency  $\Delta f = 2v/\lambda$  for targets moving with a relative speed v

<sup>&</sup>lt;sup>2</sup>Bistatic means that the transmitter and the receiver are at different locations as opposed to the normal monostatic radar.

advanced rapidly when the magnetron was invented in 1940 [6]. Much of the major development happened during World War II, when the different countries realized the benefit of detecting airplanes. The pulse radar was able to measure the distance to the targets where the CW radar failed. As time went on, and electronics became more advanced, good pulse radars were developed with very high performance and the continuous wave radars were almost forgotten. With the arrival of the pulse-Doppler radar, it was possible to measure both range and velocity with one single radar.

Radars can be used for two main applications, namely target detection and imaging. Imaging radars try to make an image of the observed area, and they take all echos into consideration. A prime example of this is the Synthetic Aperture Radar. It is mainly used from space to make a mapping of the earth's surface. A target detection radar tries to find the location of a certain or several objects.

This chapter will first present the traditional pulse radar and then the simple CW Doppler radar before proceeding with the explanation of the FMCW radar which the rest of the text will be about.

#### 2.1 Pulse Radar

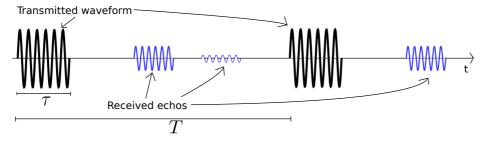

Figure 2.2: Principle of basic pulse radar

The basic pulse radar is intuitive to understand. A pulse is transmitted at regular intervals and the received echoes of this pulse define the targets. When we say a pulse, it is actually a sine-wave of very short duration, even though most texts forget to mention and illustrate this. We see that in order to detect and decide the distance to a target far away, the length between the pulses, T(also called PRI), needs to be long enough. The pulse flies at the speed of light, and it has to go back and forth, so the minimum time between each pulse in order to have no ambiguous ranges<sup>3</sup> is given by:

$$T = \frac{2R_{\text{max}}}{c} \tag{2.1}$$

<sup>&</sup>lt;sup>3</sup>Ambiguous range means that a certain reading on the radar screen can be caused by targets at two different distances quite far apart from each other.

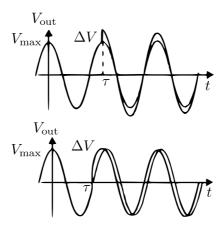

$R_{\rm max}$  is the maximum range of the radar. Note that in Figure 2.2, the length of  $\tau$  is overemphasized. In traditional pulse radars,  $\tau$  is very much smaller than T.

The inverse of T is called the pulse repetition frequency (PRF).

$$PRF = \frac{1}{T} = \frac{c}{2R_{\text{max}}} \tag{2.2}$$

Another fact that can be observed is that the length of each pulse,  $\tau$ , defines how close targets can be to each other and still distinguish them as two separate targets, and not a big one. This is known as the resolution. It is important to remember that the accuracy of a system is something else than the resolution. The accuracy can be good even though the resolution is bad. The accuracy is mainly degraded by noise. However, the resolution normally influences negatively the way noise degrades the accuracy. So indirectly, bad resolution often causes worse accuracy.

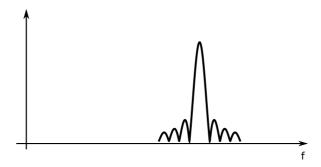

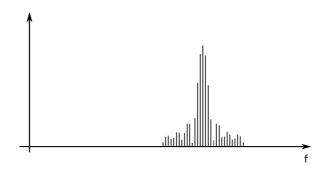

Figure 2.3: One pulse in frequency domain

In the frequency domain, a pulse of a sine wave at a certain frequency looks like a sinc-function centered at that frequency. The width of the main-lobe of the sinc-function is defined by the length of the pulse. A longer pulse will have a narrower main-lobe of the sinc-function in frequency domain and will therefore use less bandwidth. There is therefore a relationship between the bandwidth of the pulse and the resolution of the radar.

$$x_r = \frac{c}{2B} \tag{2.3}$$

The spectrum with a single sinc-function is just applicable for the ideal case when only one single pulse is sent. However, when many pulses are sent after each other at regular intervals, the frequency specter will consist of many discrete lines which have an envelope of the sinc-function of the single-pulse case (Figure 2.4). The distance between these discrete lines is given by the PRF. The higher the PRF, the longer distance between every discrete line. More advanced pulse radars, called *pulse-Doppler Radars*, take advantage of the frequency spacing between these discrete lines in order to measure the Doppler shift of the returned pulses. The Doppler shift appears when the target moves relatively to the radar. It is therefore an indicator of velocity. A moving target will shift the entire spectrum either up or down (depending

on whether the target is approaching or not) and the velocity will be measured. In order to measure the velocity it is very important that the radar signal is coherent. That basically means that only the amplifier is turned off between the pulses and not the oscillator. This is hard to do with a magnetron but easy to do with a klystron amplifier. Since the PRF defines the distance between the discrete lines, it will also define how fast targets can be detected without getting an *ambiguous velocity* reading.

Figure 2.4: Many pulses in frequency domain

We therefore have a dilemma, increasing the PRF, improves the velocity ambiguities, while decreasing the PRF, improves the range ambiguities. Because the Doppler shift gets higher if higher carrier frequencies are used, the problem also becomes bigger at higher frequencies. The pulse-Doppler Radar actually often ignores what was said above about that the distance between the pulses must be long enough to achieve no ambiguous range. It makes a compromise between ambiguous range and ambiguous velocity.

There are three different main-types of the pulse-Doppler Radar depending on how high the PRF is [7].

Low PRF: The PRF is kept so low that there will be no range ambiguities but many velocity ambiguities.

Medium PRF: The PRF is kept higher so that there will be both range ambiguities and velocity ambiguities, but not so many of each.

**High PRF:** The PRF is kept so high that there will be no velocity ambiguities. However, there will be many range ambiguities.

The exact values of the PRFs for the different types above, depend on over which region in range and velocity the radar is supposed to operate.

Many methods have been made to cope with this problem of ambiguities. One solution is to use a variable PRF, often called staggering. It is quite commonly used for high PRF-radars and will solve out the range ambiguities since they will be different for the different PRFs that are used. Normally, at least 3 different PRFs are needed in order to solve all the ambiguities.

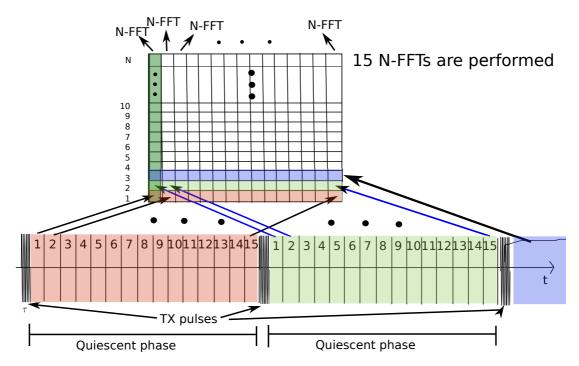

Figure 2.5: How Pulse-Doppler signal processing can be performed

## 2.1.1 Pulse-Doppler signal processing

Pulse-Doppler signal processing is nowadays used for most pulse radars. Here follows a short explanation of how it can be performed [8]. After the radar pulse has been emitted, the receiver monitors the received echoes. The received signal during the time between the pulses is called the quiescent phase. This time is divided into M equally long bins corresponding to the desired range resolution - often called range gating in the literature. The received signal is mixed down to an intermediate frequency with a local oscillator whose frequency is derived from the transmitted signal. Following some filters at the IF frequency, the signal is mixed down in quadrature to baseband. One complex sample is thereby taken for each bin and saved in a matrix in memory (see Figure 2.5). All the complex samples for the succeeding bins are saved in the same row in the matrix. When then the next pulse is emitted, the following samples are saved in a new row. After N pulses a full matrix of  $M \times N$  complex values are found. An N-FFT is taken for each column in the matrix. The result is multiple Doppler spectra. Each of them correspond to a time bin after one pulse and hence one ambiguous range. If a high PRF is used, each bin corresponds to several distances. The Doppler spectra will reveal the speed of the moving targets in each bin. Before the advent of FFT processors, the processing was performed with analogue filters and the structure was therefore slightly different.

### 2.2 CW Radar

The CW radar uses a single oscillator running at a constant frequency. By taking advantage of the Doppler shift, moving targets can be detected. The received signal is mixed with the transmitted signal and the beat signal<sup>4</sup> will contain the Doppler shifts of the targets. The processing is much simpler than for the pulse-Doppler processing. An FFT can be performed continuously for the received signal. The main problem is however that since the signal is stationary at a single frequency, the distance to targets can not be found. The radar has been used, and is still used in many different applications. A prime example is the police speed radar. Since the range is not interesting in this case, the basic CW radar does its job well.

One difficulty with the CW radar compared to the pulse radar is that it is receiving at the same time as it is transmitting. This will cause some of the transmitted signal to propagate or leak directly to the receiver. This is certainly the case if the same antenna is used. Two different antennas (quasi-bistatic) are often used but still in this case the leakage of the transmitted signal can be severe. As we will see, this problem is actually the biggest disadvantage of the CW radar, and its relative, the FMCW radar, which will be presented now.

### 2.3 FMCW Radar

The main problem of the CW radar above is that it is unable to measure the distance to the target. In many cases this is exactly what we want. To be able to determine the distance, the signal cannot be stationary. It must change somehow. It is possible to either change the amplitude or the frequency. When the signal then returns from the target the distance can be calculated since it is known how the transmitted signal looks like at all times. Changes of the amplitude are indeed very hard to measure because they are easily overloaded by the transmitted signal, and there is no way to filter out the returned signal. In addition, the amplitude of the returned signal is very variable depending on the exact angle in which the wave hits the target and so on. There are few implementations of an amplitude modulated CW radar. An example is found in [9]. On the contrary, changing the frequency of the carrier has proved to be a successfull thing to do. By frequency modulating the signal, the returned signal can more easily be filtered from the transmitted signal and the variations depending on the illumination angle are much lower. This principle is called Frequency Modulated Continuous Wave Radar (FMCW). There have been attempts to modulate the carrier with different wave forms. The first used were probably sine waves because of its simple implementation. Now, the most popular form is a linear sweep. This kind of radar is referred to as a linear FMCW radar.

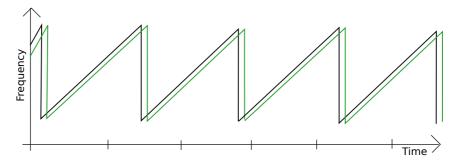

The sweep may be from lower to higher frequencies, from higher to lower frequencies or do both successively. The first two are referred to as asymmetrical linear FMCW

<sup>&</sup>lt;sup>4</sup>The beat signal is the transmitted signal mixed with the received signal. Also called the conversion product.

Figure 2.6: How an asymmetrical linear sweep FMCW radar sweeps

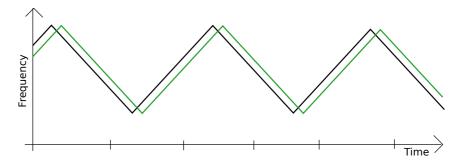

radars (Figure 2.6), while the third is called a symmetrical linear FMCW radar (Figure 2.7). It has been discovered that the linear waveform has many advantages compared to other waveforms [1]. The most obvious thing is probably that during the sweep, if the transmitted signal is mixed with the received signal, the beat signal will be a signal containing a wave with a frequency that is exactly proportional to the distance to the target. In Figure 2.6 and 2.7 the received signal is also indicated in green. It should be noticed that the frequency of the received signal differs from the transmitted signal at a certain time instant.

Figure 2.7: How a symmetrical linear sweep FMCW radar sweeps

Let us do an analysis of a single sweep - here an up-sweep. If the instantaneous frequency is given by [1]

$$f_t = f_0 + \alpha t$$

where  $\alpha$  is the sweep rate, the phase is:

$$\phi = 2\pi \int_0^t f_t dt = 2\pi \left( f_0 t + \frac{\alpha t^2}{2} \right)$$

The transmitted signal can then written

$$s(t) = A_0 \sin 2\pi \left( f_0 t + \frac{\alpha t^2}{2} \right) \tag{2.4}$$

If the signal is delayed by  $\tau$  from the target, the received signal is:

$$s_{\text{received}}(t) = B_0 \sin 2\pi \left[ f_0(t - \tau) + \frac{\alpha(t - \tau)^2}{2} \right]$$

(2.5)

Where  $B_0$  represents the loss in energy. Because of

$$2\sin x \sin y = \cos(x - y) - \cos(x + y)$$

the beat signal is:

$$c(t) = C_0 \cos 2\pi \left[ f_0 \tau + \alpha t \tau - \frac{\alpha \tau^2}{2} \right]$$

(2.6)

Here the second component at twice the transmission frequency has been removed (filtered). The delay  $\tau$  is

$$\tau = \frac{2r}{c}$$

and therefore the beat signal can be written:

$$c(t) = C_0 \cos 2\pi \left[ \frac{2f_0 r}{c} + \frac{2\alpha t r}{c} - \frac{\alpha (2r/c)^2}{2} \right]$$

(2.7)

The only time-varying term is the middle one,  $2\alpha tr/c$  (for a non-moving target), and thus the only term leading to oscillation. The main frequency component of the beat signal will hence be

$$f_{\text{conversion}} = \frac{2\alpha r}{c} \tag{2.8}$$

Compared to the pulse radar, the FMCW radar has a number of advantages and it is almost surprising that it has not been used more before. Since the FMCW radar transmits continuously, the average power (energy) will be the same as the maximum power. The pulse radar, on the other hand, outputs all its energy in a very short time period, so its average power will be low. The ability to detect targets is related to the average power, so in order to have the same detection ability, the pulse radar needs a very high maximum power. It requires typically expensive amplifiers like klystron amplifiers. An FMCW radar can use solid-state amplifiers which today are much cheaper to produce and can be highly integrated into the design of the radar. The low maximum power provides an advantage in another way too. It is harder to detect - the radar has a low probability of interception. For military use, this is very valuable, because it makes it harder for the enemy to manipulate the radar signal.

These are not the only advantages. Since the radar is receiving at all times, it does not have to wait for the pulse to be transmitted before it starts analyzing the received signal. This causes a remarkable improvement of the minimum distance that can be measured [10]. Furthermore, the range resolution is no longer dependent on how short the pulse can be made, but on the total frequency sweep range that is employed. Since the processing then does not have to sample a very short pulse which requires a high sample rate, its range resolution can easily be made considerably better.

The main issue, however, is the leakage from the transmitter to the receiver that appears from the fact that it is receiving at the same time as it is transmitting. It puts an upper limit to how strong the transmitted signal can be, and therefore also

the maximum range. Apart from this thing, it seems like the FMCW radar almost has only advantages. It is implied that the digital revolution has happened and that the more complicated processing power needed can be satisfied. First of all this concerns an efficient FFT processor, but perhaps also the DDS.

One can conclude that the FMCW radar is very good for detection at near ranges, and the industry has started to discover this by now using it in several commercial products. Some examples are collision detection radars for cars, altitude measurement and near obstacle ship navigation.

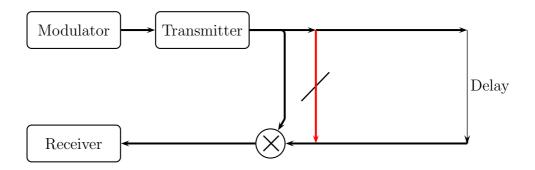

**Figure 2.8:** Conceptual diagram of an FMCW Radar. The transmitter leakage is indicated with the red line

Figure 2.8 is a simple diagram showing how an FMCW radar may be implemented. The modulator generates a sweep, which is transmitted by the transmitter. The same signal is taken to the receiver in order to mix with the reflected signal. A homodyne configuration is used. This means that the signal is mixed directly to baseband (not via an intermediate frequency). The leakage from the transmitter to the receiver is also illustrated in red. In the receiver, there can be an FFT processor which calculates the frequency spectrum of the beat signal. It is of course also possible to use a collection of filters. The receiver is in fact quite the same as for a normal CW radar.

The beat signal is sampled during the sweep. One FFT is normally calculated for each sweep. The number of samples taken during one sweep therefore decides how big the FFT must be. The sample rate defines the maximum beat signal frequency that can be detected. By increasing the sample rate, the FFT must be made bigger, but that will only make it able to represent higher frequencies. Its resolution will not get any better. If the sweep time is increased and the swept bandwidth is kept constant, the frequency sweep rate will decrease. Such a decrease causes the frequency in the beat signal to be lower. The resolution will not get any better in this case either. The only way to improve the resolution is therefore to increase the span of the sweep and it can be shown that the resolution is given by (2.3) for the FMCW radar too.

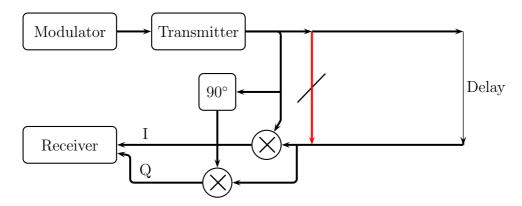

Figure 2.9 shows another structure that can be used. The difference here is that quadrature mixing is performed. This causes the receiver to be able to distinguish the frequencies above the carrier and below the carrier. This can be useful in some

Figure 2.9: Conceptual diagram of FMCW Radar with complex processing

radar systems when for example the targets have IDs which are modulated onto the carrier. In order to do the quadrature mixing, the transmitted signal must be splitted in two and one of the signals must be phase-shifted 90°.

### 2.3.1 Ambiguity

Like the pulse radar, the FMCW also has ambiguities. There are both range ambiguities and range/velocity ambiguities. First of all, the distance to a target is calculated from the received frequency shift. If the target is further away, the frequency shift will be higher. In the case when the target is moving, there will also be a frequency shift because of the Doppler effect. It is easy to imagine that this can make it hard to say if the shift is caused by the range or the velocity. However, it is observed that in the case of Doppler shift, a higher velocity causes greater frequency shift during the up-sweep and smaller frequency shift during the down-sweep. So by exploiting both the up-sweep and the down-sweep, the Doppler shift can be separated from the range-induced shift. This way, the FMCW radar is capable of both range and velocity measurements, but only when a symmetrical sweep is used<sup>5</sup>.

Let us see what happens to Equation (2.7) if r is not any more a constant but given by

$$r(t) = r_1 + vt$$

where v is the relative speed between the targets [1].

<sup>&</sup>lt;sup>5</sup>This is not always true. By doing fourier analysis of the whole signal including the return to start for the assymmetrical sweep, the beat signal will still contain an indication of what is Doppler shift and what is range-induced shift [11]. Most radars do however not take this into consideration.

$$c(t) = C_0 \cos 2\pi \left[ \frac{f_0 \cdot 2(r_1 + vt)}{c} + \frac{\alpha t \cdot 2(r_1 + vt)}{c} - \frac{\alpha(2(r_1 + vt)/c)^2}{2} \right]$$

$$= C_0 \cos 2\pi \left[ \frac{2f_0 r_1}{c} + \frac{2f_0 vt}{c} + \frac{2\alpha t r_1}{c} + \frac{2\alpha vt^2}{c} - \frac{2\alpha r_1^2}{c^2} - \frac{4\alpha r_1 vt}{c^2} - \frac{2\alpha v^2 t^2}{c^2} \right]$$

$$= C_0 \cos 2\pi \left[ \frac{2\alpha r_1 t}{c} \left( 1 - \frac{2v}{c} \right) + \frac{2f_0 vt}{c} + \frac{2\alpha vt^2}{c} \left( 1 - \frac{v}{c} \right) + \frac{2r_1}{c} \left( f_0 - \frac{\alpha r_1}{c} \right) \right]$$

Thus, the contribution from the range and the velocity can now be separated. The first term belongs to the range and the second to the velocity:

$$f_{\text{due\_to\_range}} = \frac{2\alpha r_1}{c} \left( 1 - \frac{2v}{c} \right) \tag{2.10}$$

$$f_{\text{due\_to\_velocity}} = \frac{2f_0v}{c} = \text{Doppler effect}$$

(2.11)

The third term:

$$\frac{2\alpha vt^2}{c}\left(1-\frac{v}{c}\right)$$

is also affected by the change of distance. As [1] states: It may either be interpreted as chirp on the range beat, due to the changing rate, or as chirp on the Doppler, due to the changing transmitter frequency. The last term in (2.9) is a constant phase term and will hence not influence the frequency of the beat signal.

One thing that should be noted is that the frequency offset due to the range (2.10) is no longer equal (2.8). A factor (1-2v/c) is added. It will of course not affect the result much as long as the velocity is much lower than the speed of light.

Now let us take a look at the range ambiguities. In the extreme case, the sweep may be so fast, or the target so far away, that when the reflected signal eventually returns, the radar has already started on a new sweep. The returned signal can then be mistaken for being very much closer than it really is. For most practical purposes this is however not the problem. The implementation of the sampling plays a bigger role. Because the further away the target is, the higher the frequency shift will be, the sampling frequency sets the upper limit of the range, and according to Nyquist this is  $F_s/2$ . If the low-pass filter in front of the AD converter is not good enough, there will be aliasing and targets further away than the maximum Nyquist range can be mistaken for being nearer.

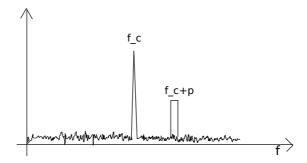

## 2.3.2 Target ID

The returned signal from non-moving targets will as we have seen be a frequency shifted  $\Delta f = 2\alpha r/c$  Hz. If there are many visible targets, it might be hard to distinguish the desired targets. When only a certain set of known targets are to be tracked, it is possible to equip them with onboard oscillators and mixers so that the returned signal will be shifted in frequency. This makes it possible to easier

recognize the known targets. Each of them may also be identified if different mixing frequencies are used. The returned signal will contain two carriers, one on both sides of the original returned signal at a frequency offset equal to the local oscillator of the targets. If the radar signal is given by:

$$s_0(t) = \sin 2\pi \left( f_0 t + \frac{1}{2} \alpha t^2 \right)$$

And the local oscillator at a target j is given by:

$$s_j(t) = \sin(2\pi f_j t)$$

The returned signal will be:

$$s(t) = s_0(t) \cdot s_j(t)$$

$$= \sin 2\pi \left( f_0(t - \tau) - \frac{1}{2}\alpha(t - \tau)^2 \right) \cdot \sin(2\pi f_j t)$$

$$= \frac{1}{2}\cos 2\pi \left( (f_0 - f_j)t - f_0\tau + \frac{1}{2}\alpha(t - \tau)^2 \right)$$

$$- \frac{1}{2}\cos 2\pi \left( (f_0 + f_j)t - f_0\tau + \frac{1}{2}\alpha(t - \tau)^2 \right)$$

(2.13)

Thus, two carriers shifted with a frequency  $f_i$ .

One other advantage of having such an oscillator at the targets, is that the returned signal will be shifted away from the worst phase noise of the transmitted signal. Hence, the sensitivity can be made better. Letting the targets have such an ID is one additional thing that makes the FMCW radar attractive compared to a pulse radar.

## 2.4 Frequencies

For radars, a general rule is that the range resolution obtained is given by the band-width used by the transmitted signal. This attracts the use of high frequencies, because at these frequencies, a high bandwidth is not high proportional to the operating frequency, and the components of the radar won't show big variations over the band. Furthermore, there are more available bands at higher frequencies. A third reason is that the waves do not propagate further than the horizon at these frequencies but more in a straight line. At last, the resolution in bearing can be made better.

There are reasons for using lower frequencies too. First of all, the components used at low frequencies are cheaper and easier to produce. Secondly, the higher frequency used, the greater the Doppler shift will be and the sampling in Doppler domain needs to be higher which implies a higher pulse repetition frequency (PRF) in the

case of a pulse radar. This reduces the maximum unambiguous range. For FMCW radars, this last argument is not applicable. At low frequencies, it is also easier to achieve low phase noise. In this thesis, a synthesizer at 9.2-9.3 GHz is built. This is part of the X-band which is defined as being from 8.0 to 12 GHz. It is a rather high frequency band, but it is chosen because it is among other things reserved for maritime radionavigation [12].

# Chapter 3

## Phase Noise

Noise is often considered a problem in the design of electronic circuits. It is normally desired to achieve the minimum amount of noise possible. However, one often tends to forget that it is actually the noise that makes it possible to communicate at a location without disturbances from the other side of the globe. Since most noise is gaussian random and often also has a white spectrum, it can be averaged out in many cases. The noise also makes it possible to do remote sensing of objects because of their thermal radiation. In this text, however, noise will be regarded as a problem just as in nearly all texts. In particular it will focus on phase noise, which can be very tricky and most likely never has been considered a positive thing. In order to understand phase noise, a short summary of the types of noise that lead to phase noise is appropriate.

## 3.1 Internally Generated Noise

#### 3.1.1 Thermal noise

The best known type of noise is thermal noise. It is radiated by all material that has a temperature above 0K, and it is therefore hard to prevent. For the frequencies employed by radio, the thermal noise power is given by:

$$P_n = kTB (3.1)$$

where k is the Boltzmanns' constant. This noise depends only on the temperature and the bandwidth so that in order to reduce it, either of them can be reduced. For many applications, however, it is not possible to reduce the temperature, and we are left with the bandwidth as the only way to reduce the noise.

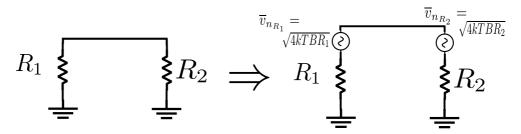

The noise voltage variance provided by a certain resistor R, is given by:

$$\overline{v}_n = \sqrt{4kTBR} \tag{3.2}$$

Thermal noise often sets the lower limit of the performance of a radio system.

Figure 3.1: Thermal noise of resistors

#### 3.1.2 Flicker noise

While thermal noise is generated in all components containing an electrical resistance, the flicker noise appears in all semiconductor based components. The exact physics to explain why it is there, still remains unclear today, but we know that it is there, and it must be taken into consideration. Flicker noise is unalike thermal noise since its spectrum is not white (at radio frequencies). It is however pink. This means that its energy is higher at low frequencies. It is actually proportional to 1/f. Because of this, it actually dominates at low frequencies while at higher frequencies it is overshadowed by the thermal noise. In oscillators, the flicker noise is often modulated up and therefore stays close to the carrier, where it plays one major role in the contribution to the phase noise (see Section 3.4.1 and 3.4.2).

$$S(f) \propto 1/f \tag{3.3}$$

For FMCW Radars, which are normally designed as homodynes, the flicker noise can play a role by itself by degrading the beat signal. For heterodynes with high IF-frequency and amplication there where the flicker noise is dominated by thermal noise, it does not play that big role.

### 3.2 External Noise

Thermal noise and flicker noise are types of internally generated noise. There are also sources of noise that can come from the outside. This can for instance be radiation that hits the circuit from outside. At places where there are strong transmitters nearby, this can be a problem. In addition, the 50 Hz (or 60 Hz) AC frequency can jump from the walls and into the circuit. It is however more common that this AC frequency enters through the power supply (as long as it is not battery powered equipment). It is necessary to design the power supply well in order to suppress noise. This is accomplished with good capacitors of different sizes after the rectifier and maybe also an inductor to form a good filter. There might also be active circuits involved in order to get rid of the noise. Some types of power supplies do actually generate much noise themselves. These are the switching mode power supplies. For them it is even more important to design good noise reduction filters in front of the circuits if they at all should be used.

Besides bypassing capacitors in the power supply, it is important to have bypass capacitors on the circuit board also preferably very close to the power supply pins of IC's when such are used.

### 3.3 What is Phase Noise?

The output of an ideal oscillator is given by:

$$s(t) = A_0 \sin(2\pi f t) \tag{3.4}$$

In the real world, however, this is an impossible signal. A more correct representation of the output of a real oscillator is given by:

$$s(t) = A_0(1 + \varepsilon(t))\sin(2\pi f t + \phi(t)) \tag{3.5}$$

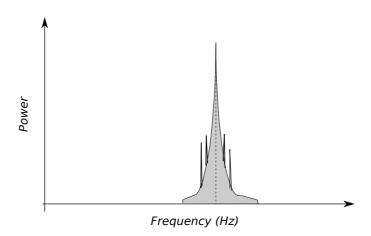

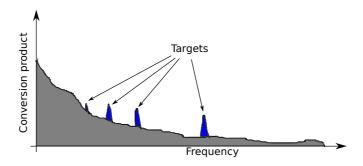

**Figure 3.2:** Simple illustration of phase noise in the frequency plane. The peaks illustrate spurious signals

Here we see two things that were not present in 3.4,  $\varepsilon(t)$  and  $\phi(t)$ . The first is the amplitude noise, while the latter is the phase noise. The amplitude noise is the disturbance of the amplitude of the signal, while phase noise is the disturbance of the phase of the signal. It is also possible to consider the phase noise as frequency noise, since a variation in phase always will be accompagnied by a variation in frequency.<sup>1</sup>

A typical spectrum of the output of a real oscillator is given in Figure 3.2. On both sides of the carrier, there is a skirt of noise. In addition to this, there are some peaks caused by spurs. The noise that we see, is actually composed of both the phase noise and the amplitude noise. In a normal situation with additive noise, the phase noise will be equal to the amplitude noise in magnitude. This is given by the equiparition theorem of thermodynamics [14, p.65]. However, the two categories of noise react to changes in different ways. An imporant example is in a signal limiter. A perfect limiter will remove the amplitude noise completely, but not influence the phase noise

If the phase noise is given by  $S_{\phi}(f)$ , the frequency noise is given by  $S_y(f) = f^2/f_0 \cdot S_{\phi}(f)$  [13].

at all. In many circuits, there is unvoluntarily a limiting-effect and we are then left with the phase noise. For instance a frequency multiplier will amplify phase noise, but keep the amplitude noise unchanged or even remove it. Also, an oscillator itself will have a limiting effect and remove the amplitude noise so that the output of an oscillator is dominated by the phase noise. Because of this, we do in most cases only care about the phase noise. The amplitude noise is simply already taken care of. The expression for s(t) then looks like:

$$s(t) = A_0 \sin(2\pi f t + \phi(t)) \tag{3.6}$$

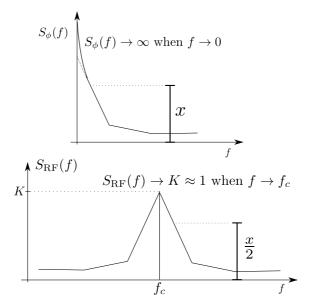

Often it is believed that the skirt around the carrier in Figure 3.2 is the phase noise itself. However, the phase noise is formally defined by IEEE as one half of the spectrum of  $\phi(t)$  [13].

$$\mathcal{L}(f) = \frac{S_{\phi}(f)}{2} \tag{3.7}$$

$\mathcal{L}(f)$  is often given in dBc/Hz. This spectrum will not be equal to what we see in Figure 3.2, but it is possible to find a relation between the two for frequencies a bit away from the carrier. In the phase spectrum, the power of the noise will approach  $\infty$  as the frequency goes towards 0. In the signal spectrum, on the other hand, the power will approach the magnitude of the carrier as we approach 0 offset frequency.

It might be confusing to read about phase noise since it can be defined in two ways. The power of the noise in a 1 Hz bandwidth at a certain offset frequency in the signal spectrum divided by the power of the entire signal is one definition. It is measured in dBc/Hz and here the symbol  $S_{\rm RF}(\Delta f)$  is used for it. The c in dBc means that it is relative to the carrier. This was actually the former official definition by IEEE for phase noise before it was changed to the definition above (3.7) in 1997 [13].

$$S_{\rm RF}(\Delta f) = \frac{\text{power density in one phase noise modulation sideband per Hz}}{\text{total signal power}}$$

(3.8)

The power density of  $\phi$  for a certain frequency offset is measured in rad<sup>2</sup>/Hz, and normally referred to 1 rad<sup>2</sup>/Hz. Its symbol is  $S_{\phi}(f)$ . It can be shown that for offset frequencies not too close to the carrier, the value of  $S_{\phi}(f)$  is two times the value of  $S_{\rm RF}(\Delta f)$ . This is the reason for that the definition above (3.7) contains a division of 2. When the formal definition was changed they wanted it to remain as similar as before. For all cases when we have no amplitude noise and the frequency offset is not too small, the value of  $\mathcal{L}(f)$  might be found just by observing the signal spectrum.  $\mathcal{L}$  is in the literature usually referred to as the *Single Sideband* (SSB) phase noise.

To show the relation between the two definitions, we take advantage of Bessel functions. Let's consider  $\phi(t)$  given as a sine with angular frequency p. This is the same

**Figure 3.3:** How the signal spectrum is related to the phase spectrum for the case with no amplitude noise.<sup>a</sup>

as saying that the carrier is phase-modulated. The oscillator output of a carrier with the amplitude equal to 1 can then be written [15, p.10].

$$s(t) = \sin\left(2\pi f t + \theta \sin p t\right) \tag{3.9}$$

This may also be written:

$$s(t) = \sin(2\pi ft)\cos(\theta\sin pt) + \cos(2\pi ft)\sin(\theta\sin pt)$$

(3.10)

There are two Bessel function properties [16]:

$$e^{jx\sin\phi} = \sum_{n=-\infty}^{\infty} J_n(x)e^{jn\phi}$$

(3.11)

$$J_{-n}(z) = (-1)^n J_n(z)$$

(3.12)

Using these, we find two expressions:

$$\cos(x\sin\phi) = J_0(x) + 2[J_2(x)\cos 2\phi + J_4(x)\cos 4\phi\cdots]$$

(3.13)

$$\sin(x\sin\phi) = 2[J_1(x)\sin\phi + J_3(x)\sin3\phi + \cdots]$$

(3.14)

With them, we can get a new expression for s(t):

<sup>&</sup>lt;sup>a</sup>That K is equal to 1 is not exactly true, but it is what is observed with spectrum analyzers. In theory, it is the entier integrated spectral density that is equal to 1. The exact value of K is only known for some specific cases like in Equation (3.23)

$$s(t) = \sin(2\pi f t) [J_0(\theta) + 2J_2(\theta)\cos(2pt) + 2J_4(\theta)\cos(4pt) + \cdots]$$

$$+ \cos(2\pi f t) [2J_1(\theta)\sin(pt) + 2J_3(\theta)\sin(3pt) + \cdots]$$

(3.15)

Simplifying this and we get:

$$s(t) = J_0(\theta)\sin(2\pi f t) + J_1(\theta)\sin((2\pi f + p)t) - J_1(\theta)\sin((2\pi f - p)t)$$

$$+J_2(\theta)\sin((2\pi f + 2p)t) + J_2(\theta)\sin((2\pi f - 2p)t) + \cdots$$

(3.16)

The  $J_{\alpha}(\theta)$ -values are given by:

$$J_{\alpha}(\theta) = \sum_{m=0}^{\infty} \frac{(-1)^m}{m!\Gamma(m+\alpha+1)} \left(\frac{1}{2}\theta\right)^{2m+\alpha}$$

(3.17)

When  $\theta$  is very small which is normally the case for random noise (at least at greater offsets), this can be simplified to:

$$J_0(\theta) \simeq 1$$

$$J_1(\theta) \simeq \frac{\theta}{2}$$

$$J_2(\theta) \simeq J_3(\theta) \simeq J_4(\theta) \cdots \simeq 0$$

(3.18)

Now (3.16) can be written

$$s(t) \simeq J_0(\theta) \sin(2\pi f t) + J_1(\theta) \sin((2\pi f + p)t) - J_1(\theta) \sin((2\pi f - p)t)$$

$$\simeq \sin(2\pi f t) + \frac{\theta}{2} \sin((2\pi f + p)t) - \frac{\theta}{2} \sin((2\pi f - p)t)$$

(3.19)

For real noise, we get an infinite number of such sine waves next to each other. If the total phase deviation is small enough, it can be shown based on this that the noise density has the following relationship:

$$S_{\rm RF}(\Delta f) \approx \frac{S_{\phi}(f)}{2} = \mathcal{L}(f)$$

(3.21)

for big enough  $\Delta f$ .

What we can recognize above is that the phase noise causes sidebands of equal magnitude at each side of the carrier. Their sign differ however. The spectrum will always be antisymmetrical around the carrier as long as there is only phase noise. For amplitude noise it can be shown that the spectrum always will be symmetrical

Figure 3.4: Carrier with added noise in a 1 Hz bandwidth

around the carrier. So in the case when there is noise only at one of the sides, we know that there must be a combination of phase noise and amplitude noise.

Consider Figure 3.4. There is noise only at one side of the carrier. This implies that there is both amplitude noise and phase noise. One can say that the amplitude noise cancels the phase noise at the lower side. Let's say that we then let the signal go through a limiter so that the amplitude noise disappears. What will happen is that we suddenly get noise on both sides of the carrier. So by introducing additive noise at one of the sidebands, we have suddenly created noise on both sides of the carrier by putting it through a limiter [15, p.20-24].

At small frequency offsets, the approximation shown earlier (3.21) does not hold. This is caused by the fact that  $S_{\phi}(f)$  gets very big as the offset gets smaller (in fact it approaches infinity in a normal oscillator). It has been shown [4] that if  $\mathcal{L}(f) = h_2/f^2$ , the relation is the following:

$$\mathcal{L}(f) = \frac{S_{\phi}(f)}{2} = \frac{h_2}{f^2} \Rightarrow$$

$$S_{RF}(f) = \frac{h_2}{(\pi h_2)^2 + \Delta f^2}$$

(3.22)

This is the Lorentzian shape - the shape of the squared magnitude of a one-pole lowpass filter. It ensures that the carrier does not get infinite power even though the phase noise at 0 frequency offset in the phase spectrum is infinite. It has a value of

$$S_{RF}(0) = \frac{1}{h_2 \pi^2} \tag{3.23}$$

at zero offset. Some other properties of this shape is that the total power of  $S_{RF}$  is equal to 1 and that it approaches (3.21) as the frequency offset gets big.

#### Typical phase noise of an oscillator

An oscillator will typically have a phase noise spectrum that consists of several terms:

$$\mathcal{L}(f) \approx \frac{h_4}{f^4} + \frac{h_3}{f^3} + \frac{h_2}{f^2} + \frac{h_1}{f} + h_0 \tag{3.24}$$

The most important is the  $h_2/f^2$  term. Nearly all oscillators will have such a slope at some important offsets, and many approximations of the phase noise are calculated based on an "ideal" oscillator with such a phase noise spectrum. The  $h_4/f^4$  term is often ignored. It appears mainly in the spectra of precision frequency standards at very low frequencies (below 1 Hz) [17].

When plotting dB-values, the terms in equation 3.24 are correspondingly slopes of -40 dB/decade, -30 dB/decade, -20 dB/decade, -10 dB/decade and constant.

## 3.4 Why Phase Noise?

Phase noise is the consequence of the contribution from all the different noise components in the oscillator. The resistors generate thermal noise, the transistors both thermal noise and flicker noise, the power supply provides ripple. These can all contribute noise which will be transformed into phase noise at the output.

At first we will look into how phase noise appears in a simple LC oscillator. Leeson was one of the first that tried to make a theory about this in 1966 [2]. His theory has been referred to a lot in the literature afterwards. However, as we will see, the theory has its limitations, and therefore during the last decades there have been attempts to make even better foundation theories for understanding the phase noise in simple oscillators.

## 3.4.1 Leeson's equation

Leesons's equation is an expression which can be used to estimate the phase noise of an LC oscillator. [14, p.64-67]

Consider an LC tank in parallel with a resistor and a perfect noiseless energy restoring element. The resistor will provide a noise current density of

$$\frac{\overline{i_n^2}}{\Delta f} = 4kTG = \frac{4kT}{R} \tag{3.25}$$

If this current is multiplied with the impedance, the voltage is given. The perfect noiseless energy restoring element will cancel the resistance in the resistor, and hence the impedance is just the impedance of the LC tank. At a small offset frequency  $\Delta\omega$ , from the center frequency,  $\omega_0$ , the impedance may be approximated by

$$Z(\omega_0 + \Delta\omega) \approx j \frac{\omega_0 L}{2\frac{\Delta\omega}{\omega_0}}$$

(3.26)

The Q factor is given by

$$Q = \frac{R}{\omega_0 L}$$

and hence the impedance may be written:

$$|Z(\omega_0 + \Delta\omega)| \approx R \frac{\omega_0}{2Q|\Delta\omega|}$$

(3.27)

The squared mean noise voltage density is therefore given by:

$$\frac{\overline{v_n^2}}{\Delta f} = \frac{\overline{i_n^2}}{\Delta f} |Z|^2 = 4kTR \left(\frac{\omega_0}{2Q\Delta\omega}\right)^2 \tag{3.28}$$

The estimated phase noise in dB is hence given by

$$\mathcal{L}(\Delta\omega) = 10\log\left(\frac{\overline{v_n^2}}{2P_{\text{sig}}R\Delta f}\right) = 10\log\left[\frac{2kT}{P_{\text{sig}}}\left(\frac{\omega_0}{2Q\Delta\omega}\right)^2\right]$$

(3.29)

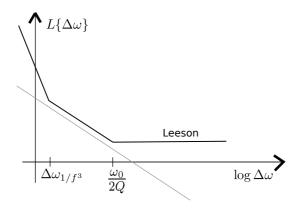

It basically says that in order to minimize the phase noise, the Q factor and the total signal power should be increased. Expression (3.29) does not show the whole truth. In reality, the region proportional to  $1/(\Delta\omega)^2$  is larger than predicted by it. There is also an unavoidable noise floor at sufficiently high offsets. At very small offsets there is typically also a region proportional to  $1/(\Delta\omega)^3$ . To take all these extra considerations into account, the full Leeson's equation is given by:

$$\mathcal{L}(\Delta\omega) = 10 \log \left[ \frac{2FkT}{P_{\text{sig}}} \left\{ 1 + \left( \frac{\omega_0}{2Q\Delta\omega} \right)^2 \right\} \left( 1 + \frac{\Delta\omega_{1/f^3}}{|\Delta\omega|} \right) \right]$$

(3.30)

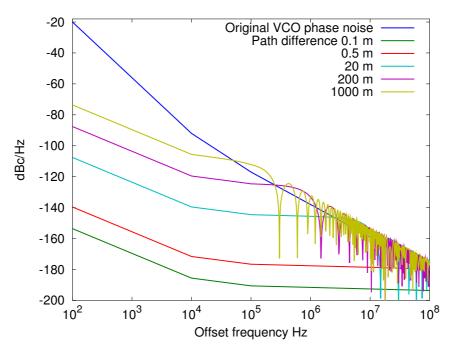

Figure 3.5 shows the difference between what Equation (3.29) (grey) and (3.30)

Figure 3.5: Leeson's equation

(black) represent. A factor F has been introduced together with a lower noise floor and a  $1/f^3$  factor. One of the main problems is that this method does not provide any way to actually calculate the factor F and the value of  $\Delta\omega_{1/f^3}$ .

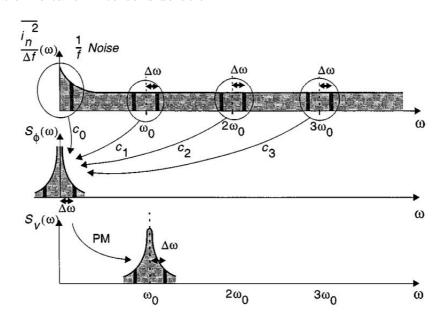

#### 3.4.2 LTV model

Since Leeson's model contains empirical parameters without showing where they come from, Lee and Hajmiri developed a new model in 1998 [3]. It considers an oscillator as a time-varying system, and by doing this, much higher insight is achieved into how the phase noise appears. Earlier texts claimed that to explain different effects of the phase noise development in oscillators, it was necessary to consider the system as nonlinear and they therefore normally skipped any explanation since it would become quite complicated. This new model, however, shows that it is not strictly necessary to consider it as a nonlinear system. The time-variant model, goes far in showing that up-mixing of flicker noise to near-carrier phase noise and that down-mixing of near-harmonics noise contributes to the  $1/f^2$  phase noise, is fully possible even when the oscillator is considered a linear system as long as the time-variation is taken into consideration.

**Figure 3.6:** Evolution of circuit noise into phase noise (Borrowed from [18, p.331])

Figure 3.6 shows how noise from different frequency bands adds to the phase noise. The flicker-noise (upper Figure to the left) becomes  $1/f^3$  phase noise in the phase spectrum. The noise near every harmonic of the carrier frequency moves near the carrier and adds to the  $1/f^2$  noise. How can it be explained that the noise shifts frequency if nonlinearity is not taken into consideration?

The key to understanding this can be found in Figure 3.7. This is the response of a current impulse in an LC tank that is already oscillating. What can be observed is that the response of the impulse is different depending on where in the cycle it appears. If it appears when the amplitude is maximum (upper), it will not influence the phase anything. However, when it appears at the same time as the sine is at the zero-crossing (lower), the phase will be shifted. This basically says that the system is time variant and theories not including time-invariance will fail to explain much

(like Leeson). It means that in order to minimize the phase noise, it will be good to add the lost energy (in the oscillator) when the amplitude is at its maximum.

Figure 3.7: Impulse response of LC tank [18, p.329]

The impulse response to the phase of one such pulse can be written:

$$h_{\phi}(t,\tau) = \frac{\Gamma(\omega_0 \tau)}{q_{\text{max}}} u(t-\tau)$$

(3.31)

(3.32)

so that the phase response is equal too:

$$\phi(t) = \int_{-\infty}^{\infty} h_{\phi}(t,\tau)i(\tau)d\tau \tag{3.33}$$

We see that  $h_{\phi}$  has two arguments. The  $\tau$  actually means at what time the pulse is inserted and takes care of the time-invariance. The  $\Gamma$  is a function that will define when the impulse makes the biggest influence to the phase. It is called the impulse sensitivity function (ISF). It will be periodic. Since it is periodic it can be expressed as a Fourier series:

$$\Gamma(\omega_0 \tau) = \frac{c_0}{2} + \sum_{n=1}^{\infty} c_n \cos(n\omega_0 \tau + \theta_n)$$

(3.34)

Setting in for (3.33), we get:

$$\phi(t) = \int_{-\infty}^{\infty} h_{\phi}(t,\tau)i(\tau)d\tau = \frac{1}{q_{\text{max}}} \int_{-\infty}^{t} \Gamma(\omega_{0}\tau)i(\tau)d\tau$$

$$= \frac{1}{q_{\text{max}}} \left[ \frac{c_{0}}{2} \int_{-\infty}^{t} i(\tau)d\tau + \sum_{n=1}^{\infty} c_{n} \int_{-\infty}^{t} i(\tau)\cos(n\omega_{0}\tau)d\tau \right]$$

(3.35)

If then a sinusoidal current is added which is near an integer multiple m of the oscillation frequency,

$$i(t) = I_m \cos[(m\omega_0 + \Delta\omega)t]$$

(3.36)

it is found that only the terms where n=m contribute considerably and (3.35) can be written

$$\phi(t) \approx \frac{I_m c_m \sin(\Delta \omega t)}{2q_{\text{max}} \Delta \omega} \tag{3.37}$$

This is interesting because it says that injected noise at frequencies near harmonics of the oscillator frequency,  $\omega_0$ , also contribute to the near-carrier phase noise. This was earlier claimed to be because of nonlinearities, but we see that the time invariance can cause this behaviour. We see that the influence is scaled by the  $c_m$  factor. The m is the number of the harmonic, so that if we know all the  $c_m$  factors for  $2 \leq m < \infty$ , we will be able to say how much each of the near-harmonics noise bands influence the phase spectrum. Another quite interesting thing is that  $c_0$  actually says how much of the near-0Hz noise that will be upmixed, and this is mainly the flicker noise. At last the  $c_1$  says how much of the near carrier noise that will be added to the carrier phase noise. Figure 3.6 shows how the noise becomes phase noise. Just one problem remains, how do we find the  $c_m$  values - or in other words, how do we find the ISF  $(\Gamma(\omega_0\tau))$ . In [3] some methods are explained. It is possible to measure the ISF by injecting pulses and see the response or one may calculate it. It is referred to [3] for details.

#### 3.4.3 Nonlinear models

Even though the LTV method is able to explain how the noise from different frequencies adds the phase noise, it is a matter of fact that the oscillator behaviour is nonlinear by nature. So it can be expected that the results obtained will not take everything into account and hence not be completely correct. Some approximations employed in the LTV method has been shown to be false [19], but still may provide good design intuition. There have been several attempts to analyze the phase noise in a nonlinear system too, and perhaps the most acknowledged of these is presented by Demir, Mehrotra and Roychowdhury in [4].

The noise is in their work modelled rather differently. If the periodic response of an unperturbed oscillator is given by  $x_s(t)$ , the signal with noise (both amplitude and phase) is described as:

$$x_s(t + \alpha(t)) + y(t) \tag{3.38}$$

$\alpha(t)$  contains the time shift (phase shift) experienced after time t. It was stated above that  $S_{\phi}(f)$  approaches  $\infty$  as  $f \to 0$ . That implies that after a certain time, most likely (in practice always) the signal will have a constant phase shift relative to the beginning. This means that  $\alpha(t)$  will in general keep increasing with time. y(t) will on the other hand always remain small because it represents the orbital deviation. Nonlinear differential equations are solved and some important results are derived. One of them is that the spectrum is Lorentzian near the carrier as

given in (3.22). Another thing is that the oscillator behaviour with noise is shown to be stationary despite being intuitively hard to understand. It also points out that what is done in the LTV method is in general false.

The article only considers noise appearing from white noise sources, hence only phase noise with a  $1/f^2$  characteristic, and it is therefore not straightforward to use their result in practical desisgn. It mainly attemps to establish a foundation theory for the description of phase noise in nonlinear systems, which has been lacking earlier. Based on the huge number of newer articles citing their work, it may be concluded that they have kind of succeeded with the last thing.

# 3.5 Propagation in Devices

#### 3.5.1 Mixers

The mixer will preserve the phase noise. It will be added or subtracted depending on which mixing product that is wanted.

Two perturbed carriers are given by:

$$s_1(t) = \sin(2\pi f_1 t + \phi_1(t))$$

$$s_2(t) = \sin(2\pi f_2 t + \phi_2(t))$$

Their product is:

$$s(t) = s_{1}(t) \cdot s_{2}(t)$$

$$= \sin(2\pi f_{1}t + \phi_{1}(t)) \cdot \sin(2\pi f_{2}t + \phi_{2}(t))$$

$$= \frac{1}{2}\cos[2\pi f_{1}t + \phi_{1}(t) - 2\pi f_{2}t - \phi_{2}(t)]$$

$$- \frac{1}{2}\cos[2\pi f_{1}t + \phi_{1}(t) + 2\pi f_{2}t + \phi_{2}(t)]$$

$$s(t) = \frac{1}{2}\cos[2\pi (f_{1} - f_{2})t + \phi_{\text{difference}}(t)]$$

$$- \frac{1}{2}\cos[2\pi (f_{1} + f_{2})t + \phi_{\text{sum}}(t)]$$

(3.39)

One of these two terms is then typically selected by a filter since they are at completely different frequencies. For the sum frequency, the phase noise is given by:

$$\phi_{\text{sum}}(t) = \phi_1(t) + \phi_2(t)$$

(3.40)

For the difference frequency:

$$\phi_{\text{difference}}(t) = \phi_1(t) - \phi_2(t) \tag{3.41}$$

In FMCW radars, the interest is almost always in the difference frequency, because it is how the beat signal is made. The phase noise will therefore be given by  $\phi_1(t) - \phi_2(t)$  and as we will see in Chapter 5, this can be made an advantage.

#### 3.5.2 Frequency multipliers

The effect of frequency multiplication is also considered [15, p.76]. If a perturbed carrier is given as:

$$s_1(t) = \sin(2\pi f_1 t + \theta \sin pt) \tag{3.42}$$

the phase and the instantaneous frequency of the signal is

$$\theta_{\rm sig} = 2\pi f_1 t + \theta \sin pt \tag{3.43}$$

$$f_1(t) = \frac{1}{2\pi} \frac{d\theta_{\text{sig}}}{dt} = f_1 + \frac{1}{2\pi} (p\theta \cos pt)$$

(3.44)

If the frequency is multiplied by n

$$f_2(t) = nf_1(t) = nf_1 + \frac{1}{2\pi}(np\theta\cos pt)$$

$$= f_2 + \frac{1}{2\pi}(np\theta\cos pt)$$

(3.45)

The phase of this is:

$$\theta_{\text{sig}} = \int 2\pi \left( f_2 + \frac{np\theta}{2\pi} \cos pt \right) dt$$

$$= (2\pi f_2 t + n\theta \sin pt) + C \tag{3.46}$$

Neglecting the constant C and the new signal is given by:

$$s_2(t) = \sin(2\pi f_2 t + n\theta \sin pt) \tag{3.47}$$

Hence, the phase noise has been scaled by the frequency multiplication factor n.

$$\phi_2 = n\phi_1 \tag{3.48}$$

In dB, the relation is

$$\mathcal{L}_{\text{out}}(f) = \mathcal{L}_{\text{in}}(f) + 20\log n = \mathcal{L}_{\text{in}}(f) + 20\log\frac{f_{\text{out}}}{f_{\text{in}}}$$

(3.49)

- an expression which may be very useful.

# 3.6 Measurement Techniques

The most obvious way to measure phase noise is to use a spectrum analyzer directly on the signal. The noise observed will have to be scaled according to the bandwidth used when measuring with the formula:

Phase noise in 1 Hz = Noise in RBW

$$- 10 \log RBW$$

(3.50)

where RBW is the resolution bandwidth used while measuring. In addition, a correction factor which takes into account the implementation of the RBW, the logarithmic display mode and the detector characteristic should be added [20]. Many spectrum analyzers are capable of doing this scaling automatically. The noise will then be given in noise power per Hz. By dividing this by the total carrier power, an estimate of  $\mathcal{L}(f)$  is found. This corresponds to the old definition,  $S_{\rm RF}$ , in Equation (3.8) which is measured in dBc/Hz.

However, using a spectrum analyzer directly on the signal has its limitations. First of all, as stated above, the skirt around the carrier is composed of both the phase noise and the amplitude noise. We therefore need to make sure that the amplitude noise is eliminated. In some cases it can also be assumed that the phase noise and amplitude noise are equally strong and half of the observed power can be attributed to each of them. Another problem is that if the phase noise is low, the spectrum analyzer needs a very high dynamic range in order to see the phase noise. This is caused by the fact that the carrier itself is observed at the same time. The carrier furthermore makes it harder to measure near-carrier phase noise. Because of all this, it is natural that other methods have been developed in order to measure the phase noise [21].

#### 3.6.1 Down-conversion and filtering of carrier

One possibility is to down-convert the signal to an IF and pass it through a sharp IF filter which removes the carrier while keeping the noise around it. The signal can then be measured with a spectrum analyzer with the carrier removed and the constraints on the dynamic range are reduced a lot. Also the noise introduced by the mixing with the spectrum analyzer's local oscillator is reduced. The quality of the oscillator used for the down-conversion must of course be very good, preferably better than the oscillator under test (DUT).

One drawback is that because of the IF filter, it is hard to measure noise closer to the carrier than 10 kHz. Compared to the previous method it is also slightly harder to calibrate the measurement. This is because the carrier has been removed. At first, the down-conversion oscillator (LO) must be tuned to a frequency so that the carrier falls into the passband of the filter and then measure the level of it. Afterwards, the LO must be tuned so that the carrier is removed and then the noise can be measured.

# 3.6.2 Quadrature method

A different method can measure  $S_{\phi}(f)$  directly. In order to do this, another stable oscillator with exactly the same frequency is needed. If the two oscillators are mixed, the result after a low-pass filter will be the phase spectrum. It is compulsary that the two oscillators are in quadrature - 90° degrees phase shifted to each other. It might be quite hard to achieve this, and in cases with a drifting oscillator it is practically impossible. However, if the two oscillators are very stable and controlled

by a synthesizer, it is possible to adjust them exactly to get them in quadrature. In other cases it is possible to use a Phase-locked loop in order to lock the phase of the second oscillator to the first.

This method can measure phase noise really well. It is therefore used to measure high performance oscillators, like for instance crystal oscillators. One problem with this method is that it requires a more complicated calibration than the previous methods.

#### 3.6.3 Delay line discriminator

A third method measures the frequency noise. It is performed by splitting the oscillator signal in two and then delay one of them 90° and mix them together. After a low-pass filter we have frequency demodulated the signal. It is only possible to measure noise up to a certain offset frequency, because the discriminator has a bandwidth of  $\operatorname{sinc}(\pi T f_m)$  where the T is the delay of the delay line. This method works well for drifting oscillators and it eliminates the amplitude noise just like the quadrature method. However it is not so useful for high-offset noise and for noise very close to the carrier.

It is also possible to design such an FM detector at an IF frequency. Then the discriminator can be made better since it is designed for only one frequency. The signal must first be mixed down to the IF frequency.

## 3.7 Jitter

The jitter is the perturbation of the phase seen in time domain. There are several definitions of jitter, but the most common are absolute jitter and period jitter [17].

The absolute jitter is defined as the total time deviation from where a clock transition were supposed to be without jitter after time  $nT_0$  where  $T_0$  is the nominal period  $T_0 = 1/f_0$ . The standard deviation of the absolute jitter is:

$$\sigma_{j\_abs}(T_0) \approx \frac{1}{2\pi f_0} \sqrt{\int_0^\infty S_\phi(f) df} = \frac{1}{\pi f_0} \sqrt{\frac{1}{2} \int_0^\infty \mathcal{L}(f) df}$$

(3.51)

The period jitter is the time difference of a single clock period and the ideal clock period. It is often more useful than absolute jitter - at least in digital circuits with high clock speeds. The period jitter is often also referred to as cycle jitter. The standard deviation of the period jitter is:

$$\sigma_j(T_0) \approx \frac{1}{\pi f_0} \sqrt{\int_0^\infty 2\sin^2(\pi f T_0) \mathcal{L}(f) df}$$

(3.52)

In most cases it does not converge. Then other integration limits can be set,  $f_1$  and  $f_2$ . The lower limit  $f_1$  is often given as 10 Hz because everything below 10 Hz is

regarded as wandering, and everything above is considered jitter. The upper limit must be chosen depending on the application and actual phase spectrum. In some cases when  $f_1$  is chosen as 10 Hz and  $f_2$  kept at  $\infty$ , it converges.

A special case is when the phase noise displays a -20 dBc/Hz slope (it is proportional to  $1/f^2$ ). Then the period jitter can be related to the phase noise by:

$$\sigma_j = \sqrt{\frac{f^2 \mathcal{L}(f)}{f_0^3}} \tag{3.53}$$

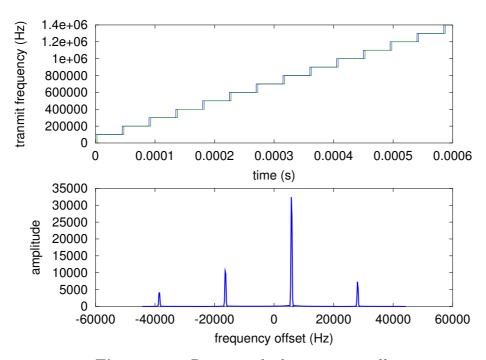

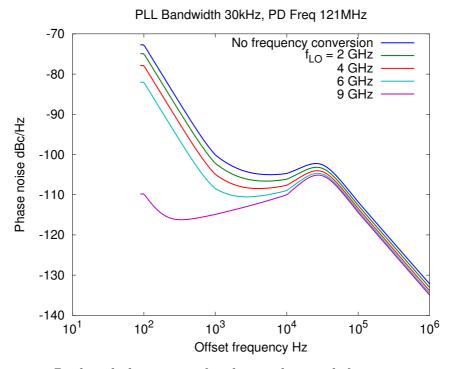

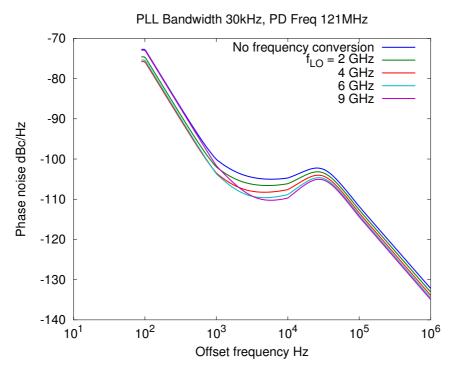

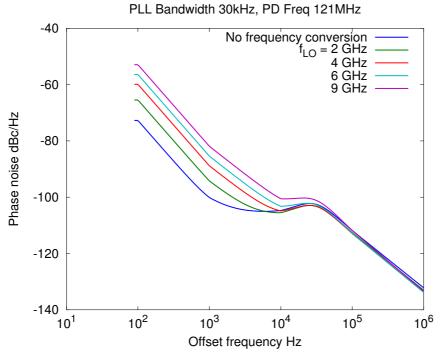

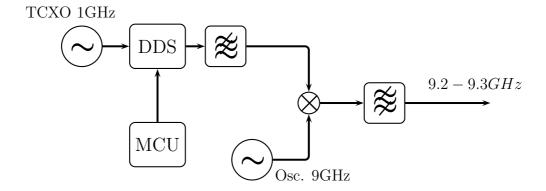

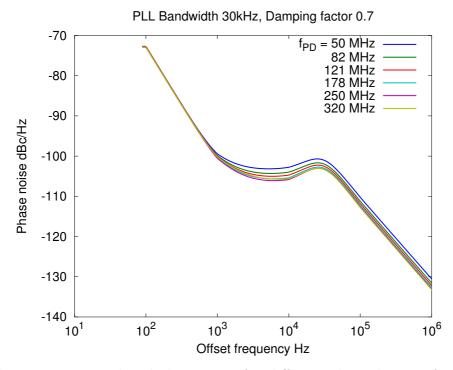

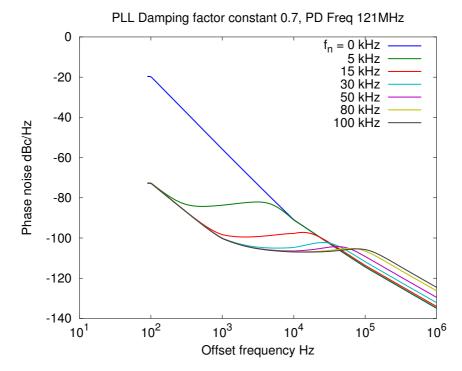

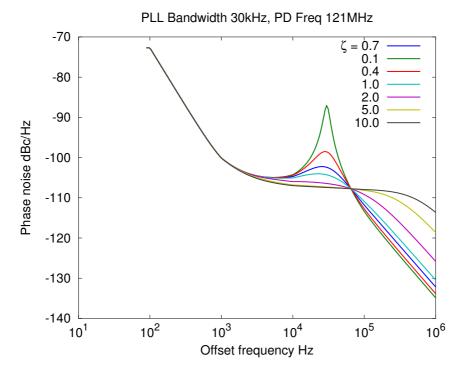

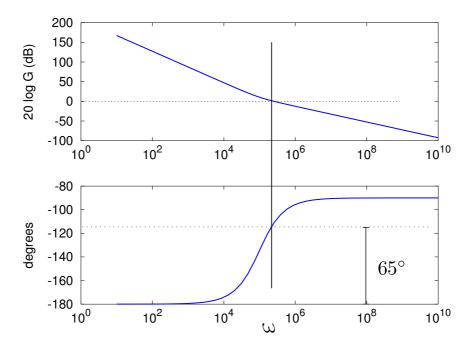

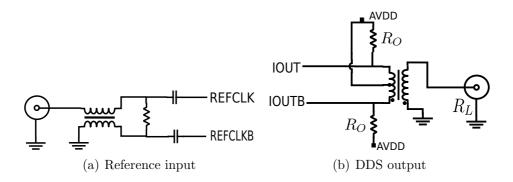

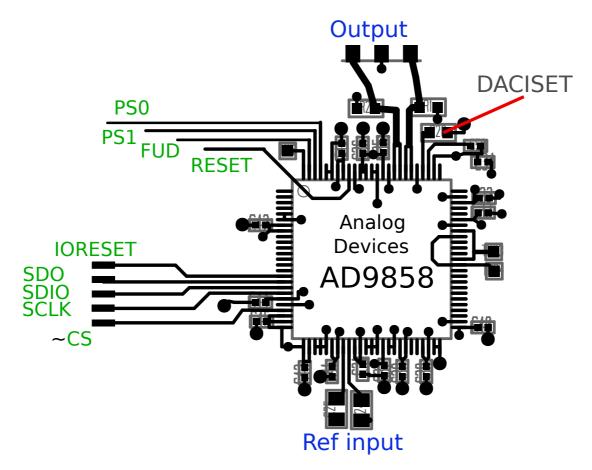

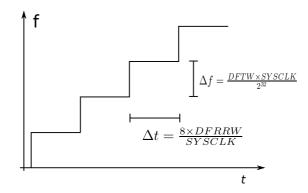

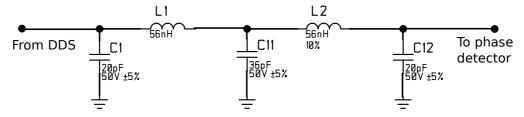

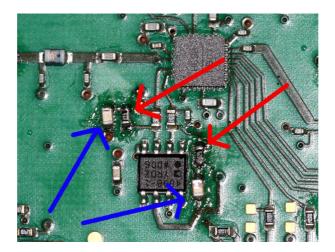

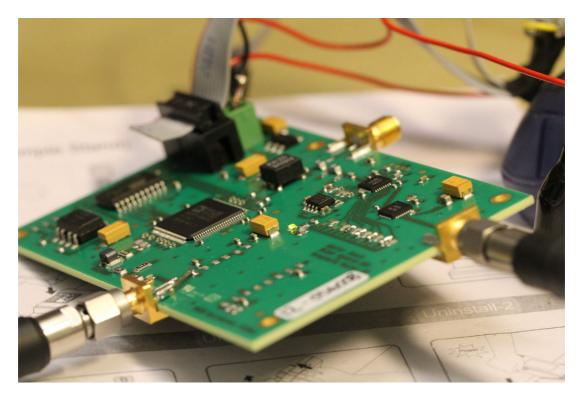

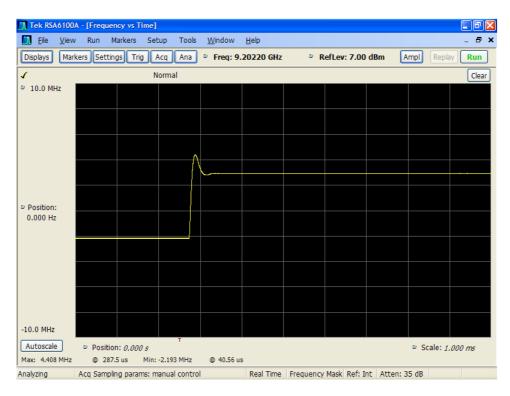

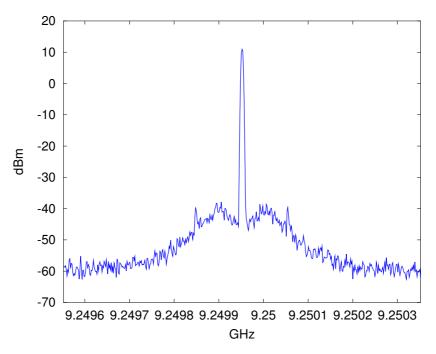

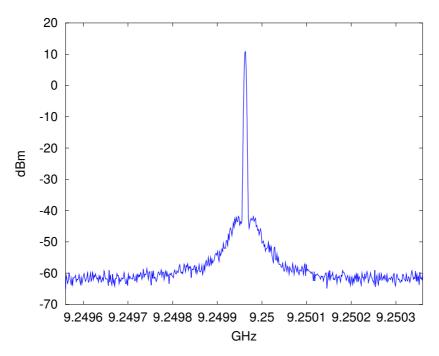

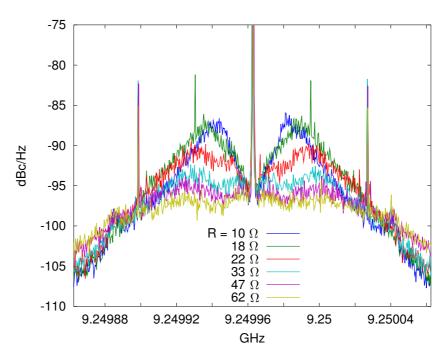

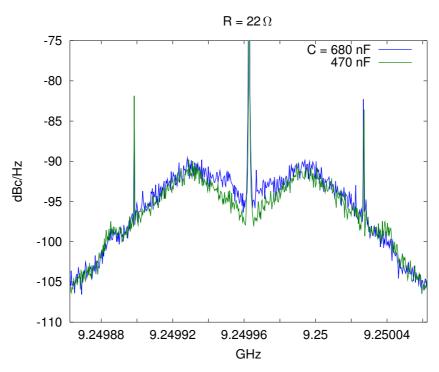

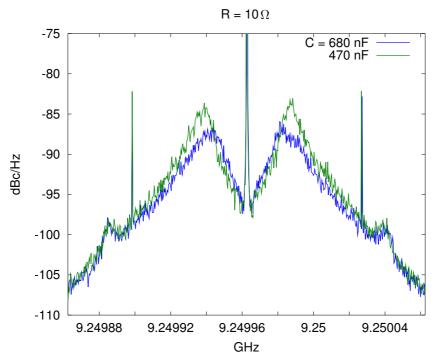

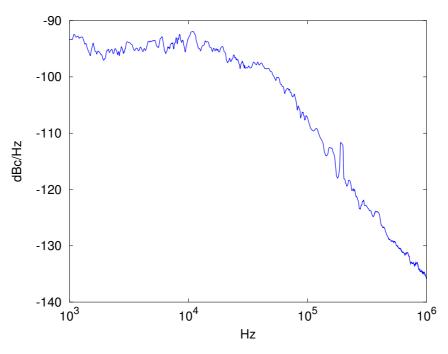

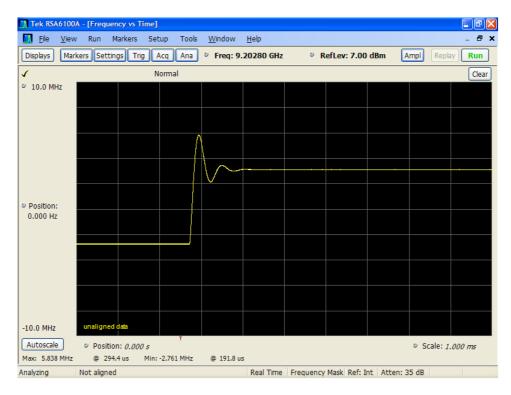

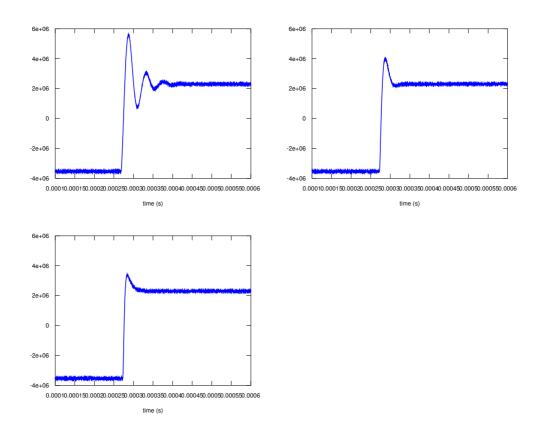

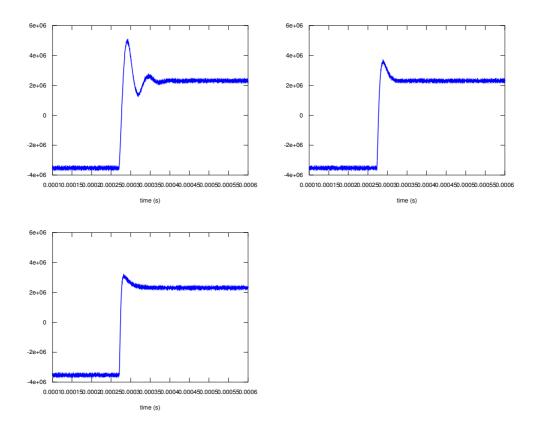

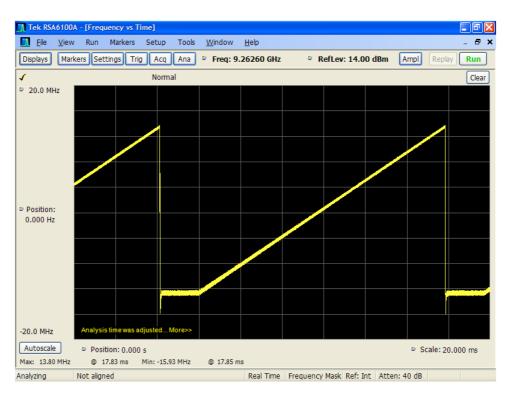

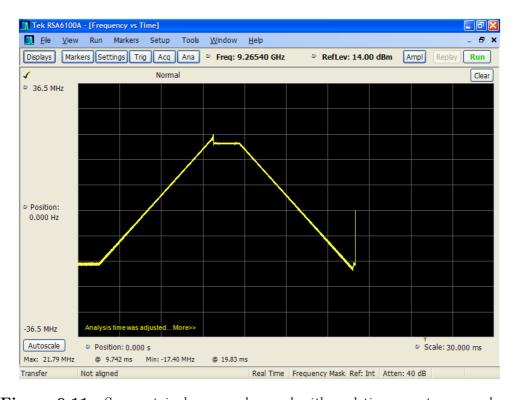

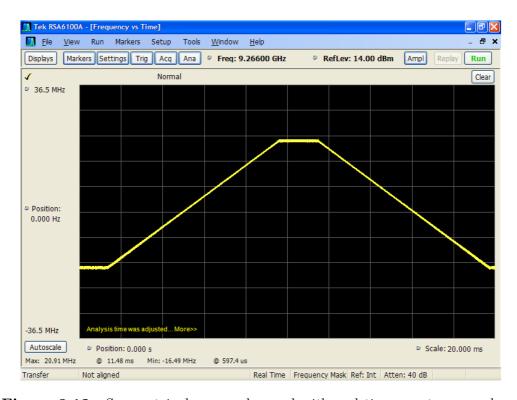

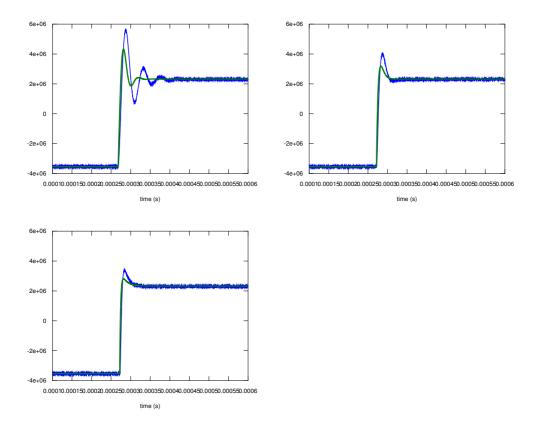

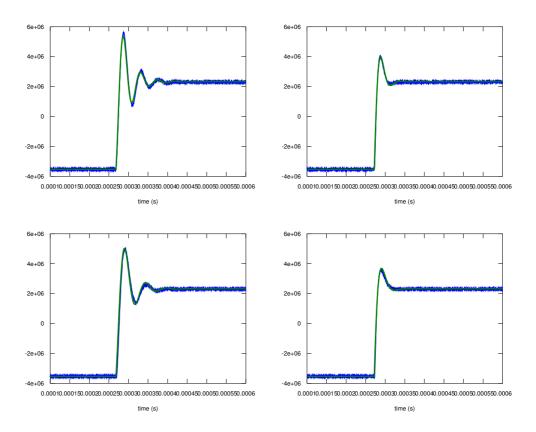

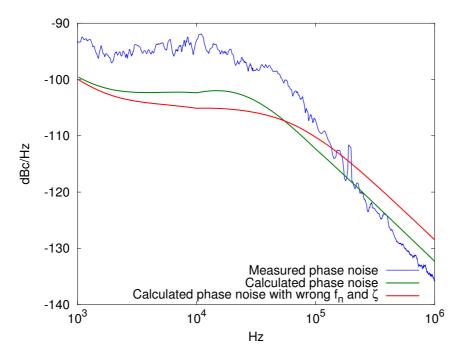

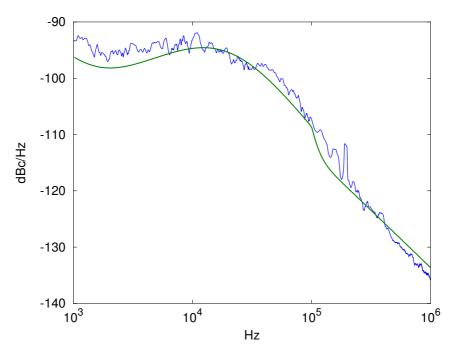

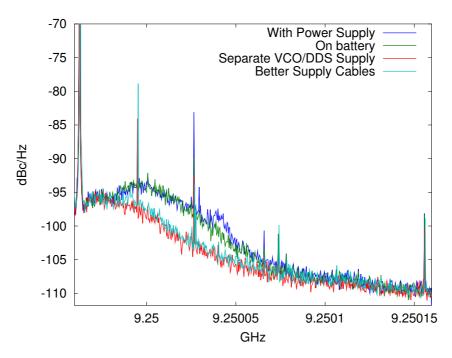

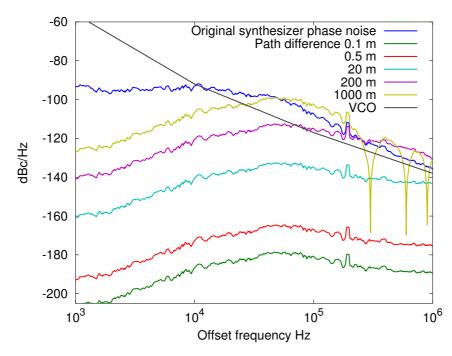

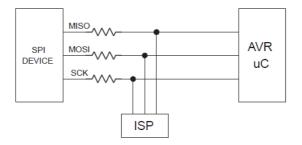

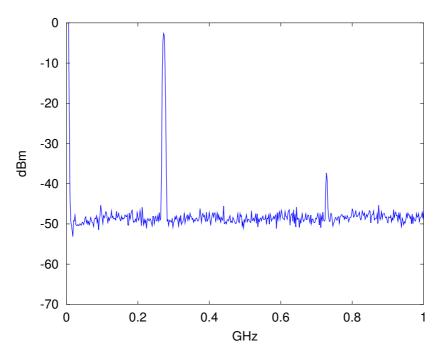

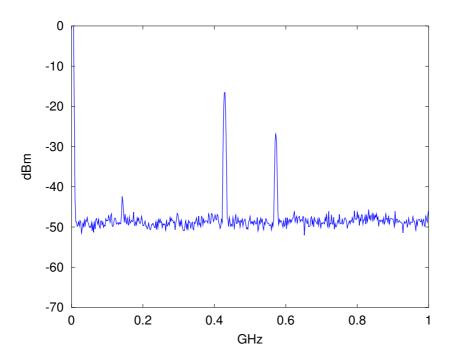

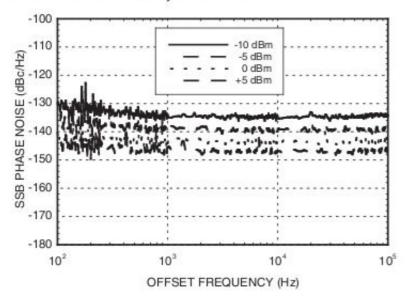

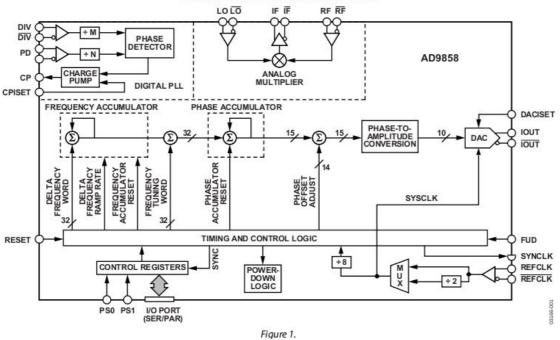

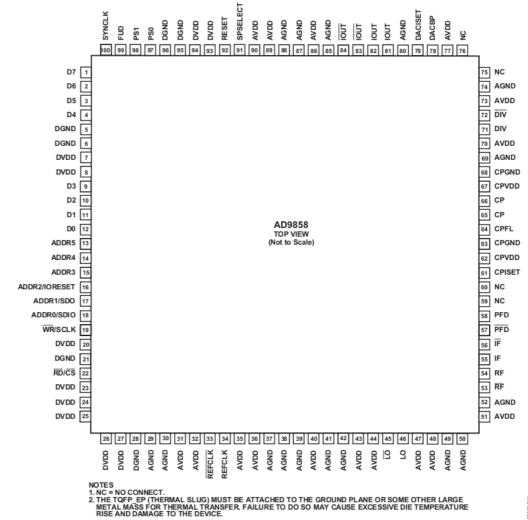

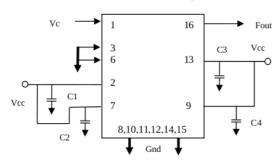

If  $\mathcal{L}(f) = h_2/f^2$ , this is the same as: