# Application of asynchronous design to microcontroller startup logic

Svein Rypdal Henninen

Master of Science in Electronics

Submission date: August 2011

Supervisor: Bjørn B. Larsen, IET

# **Problem Description**

A particular challenge in microcontroller system is designing the logic involved in the startup sequence, i.e. when power is initially applied to the system. Advanced microcontrollers rely on a complicated interaction between several digital and analog modules, often outside of the regular operating range of the system.

Analog modules are inherently asynchronous and using asynchronous logic to control them could have several advantages:

- No oscillator or clock system required

- Operation in near-threshold/sub-threshold region is possible, while traditional synchronous operation breaks down

- Direct integration with analog cells that support built-in handshaking capability (enable/ready signals)

#### The student should:

- Implement a synchronous Verilog RTL model of the startup logic to be used as a reference for further work

- Study literature and available tools (e.g. Teak/Balsa) and propose an equivalent implementation using asynchronous techniques, such as 4-phase dual-rail.

- Propose a protocol for analog cell interfaces to make the cells usable in an asynchronous design

- Synthesize both the synchronous and asynchronous implementations and simulate them with Verilog and Spice simulators

A secondary objective is to extend the startup logic with ultra-low power features, such as real-time clock, voltage monitoring, or external event detection.

#### Abstract

Digital circuits designed today are almost exclusively clocked. As designs grow in size it becomes harder to effectively distribute the various clock signals over the circuit. The clock is also a big contribution to the power consumption of a circuit. Some work is being done to provide alternatives to standard synchronous design. One of these alternatives is the Balsa system.

Several versions of an asynchronous module for controlling the startup process of a microcontroller was made in Balsa and compared to a standard synchronous implementation. Area estimates for the best asynchronous implementation gives a number that is a factor of over four larger than for the synchronous implementation. The asynchronous implementation has other advantages though. It has no dynamic power consumption when it is in a stable state. Additionally it can operate closer to the sub-threshold area.

The asynchronous implementations have been tested and found working in active HDL. Balsa generated verilog netlists in a  $350 \ nm$  library from the balsa language description. Design Compiler from Synopsys was used to get the area estimates. The asynchronous implementations shows potential, especially with regards to reduced power consumption.

# Contents

| N  | omer                        | ıclatur | re x                            | ζi |

|----|-----------------------------|---------|---------------------------------|----|

| Li | st of                       | Figure  | es xi                           | ii |

| Li | st of                       | Tables  | s x                             | V  |

| 1  | Intr                        | oducti  | ion                             | 1  |

| 2  | $\operatorname{Th}\epsilon$ | eory    |                                 | 3  |

|    | 2.1                         | Introd  | luction to Asynchronous         | 3  |

|    |                             | 2.1.1   | Potential drawbacks and gain    | 4  |

|    |                             | 2.1.2   | Protocols                       | 6  |

|    |                             | 2.1.3   | Special cells                   | 2  |

|    | 2.2                         | Power   | consumption                     | 4  |

|    |                             | 2.2.1   | Dynamic power dissipation       | 4  |

|    |                             | 2.2.2   | Short circuit power dissipation | 5  |

|    |                             | 2.2.3   | Leakage power dissipation       | 5  |

|   | 2.3  | Metastability                        | 16 |

|---|------|--------------------------------------|----|

| 3 | Bals | sa 1                                 | L7 |

|   | 3.1  | Introduction to balsa                | 17 |

|   | 3.2  | Balsa system                         | 18 |

|   | 3.3  | Balsa language                       | 20 |

|   |      | 3.3.1 Language constructs            | 20 |

| 4 | Star | rtup logic specification 2           | 23 |

|   | 4.1  | Startup system                       | 23 |

|   | 4.2  | Analog Cells                         | 24 |

|   |      | 4.2.1 Power-on-Reset (POR) generator | 24 |

|   |      | 4.2.2 Voltage Monitor                | 24 |

|   |      | 4.2.3 Voltage Regulator              | 26 |

|   |      | 4.2.4 Voltage Reference              | 27 |

|   | 4.3  | Startup logic Controller             | 28 |

|   | 4.4  | Asynchronous specification           | 29 |

| 5 | Des  | ign 3                                | 31 |

|   | 5.1  | Synchronous implementation           | 31 |

|   |      | 5.1.1 Design Considerations          | 31 |

|   |      | 5.1.2 Implementation                 | 32 |

| 7 | Con | clusio  | n                                           | 61 |

|---|-----|---------|---------------------------------------------|----|

|   | 6.3 | Discus  | ssion                                       | 58 |

|   | 6.2 | Synthe  | esis                                        | 56 |

|   |     | 6.1.3   | Testing of the asynchronous implementations | 53 |

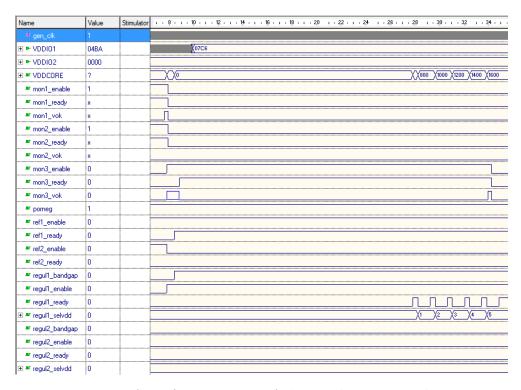

|   |     | 6.1.2   | Testing of the synchronous implementation   | 52 |

|   |     | 6.1.1   | Test cases                                  | 51 |

|   | 6.1 | Testin  | g                                           | 51 |

| 6 | Eva | luation | n and results                               | 51 |

|   |     | 5.3.5   | Active PUSH Interface                       | 49 |

|   |     | 5.3.4   | Passive PULL Interface                      | 48 |

|   |     | 5.3.3   | Passive PUSH Interface                      | 47 |

|   |     | 5.3.2   | Sync interface                              | 45 |

|   |     | 5.3.1   | Choice of interface                         | 44 |

|   | 5.3 | Interfa | ace                                         | 44 |

|   |     | 5.2.4   | Optimized implementation                    | 39 |

|   |     | 5.2.3   | State machine implementation                | 36 |

|   |     | 5.2.2   | Design Considerations                       | 35 |

|   |     | 5.2.1   | Description                                 | 35 |

|   | 5.2 | Async   | hronous Implementation                      | 35 |

| A | Bals | sa Cod | e e                            | 65 |

|---|------|--------|--------------------------------|----|

|   | A.1  | State  | machine implementations        | 65 |

|   |      | A.1.1  | State machine implementation 1 | 65 |

|   |      | A.1.2  | State machine implementation 2 | 68 |

|   |      | A.1.3  | State machine implementation 3 | 71 |

|   | A.2  | Optim  | nized implementations          | 74 |

|   |      | A.2.1  | Optimized implementation 1     | 74 |

|   |      | A.2.2  | Optimized implementation 2     | 76 |

|   |      | A.2.3  | Optimized implementation 3     | 78 |

| В | Syn  | chrono | ous startup logic              | 81 |

# Nomenclature

2PSR 2-phase single-rail 4PSR 4-phase single-rail 2PDR 2-phase dual-rail 4PDR 4-phase dual-rail

EDA Electronic Design Automation

HDL Hardware Description Language

LEDR Level-Encoded 2-phase Dual-Rail

LSB Least Significant Bit(s)

MSB Most Significant Bit(s)

NCL Null Convention Logic

RTZ Return-To-Zero

VLSI Very-Large-Scale-Integration

DUT Device under test

# List of Figures

| 2.1 | Comparison between synchronous and asynchronous pipelines      | 4  |

|-----|----------------------------------------------------------------|----|

| 2.2 | Single-rail scheme                                             | 7  |

| 2.3 | 4-phase Single-rail                                            | 8  |

| 2.4 | 2-phase Single-rail                                            | 9  |

| 2.5 | Dual-rail scheme                                               | 10 |

| 2.6 | communication over 4-phase dualrail protocol                   | 10 |

| 2.7 | 2-phase dual-rail transaction                                  | 11 |

| 2.8 | Muller C-element                                               | 13 |

| 3.1 | balsa design flow                                              | 19 |

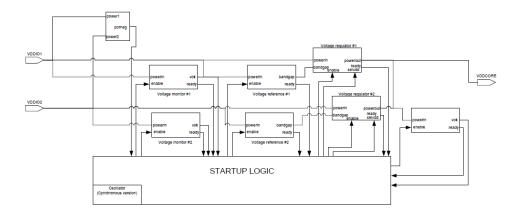

| 4.1 | Startup system with controller and analog cells                | 23 |

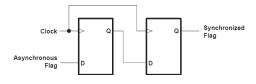

| 5.1 | Two stage synchronizer                                         | 32 |

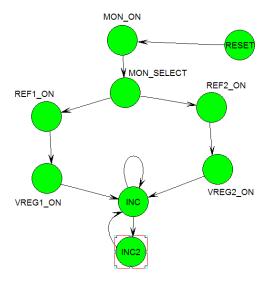

| 5.2 | Simplified state Diagram of the Synchronous implementation $.$ | 33 |

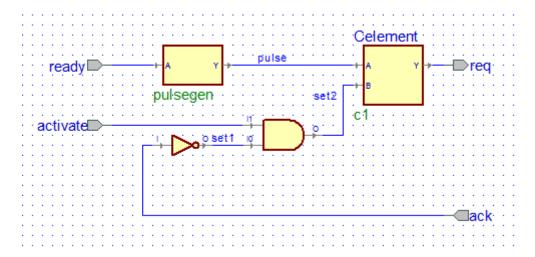

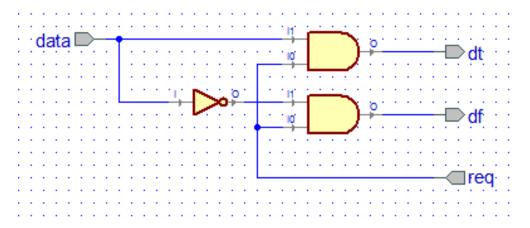

| 5.3 | Sync interface                                                 | 45 |

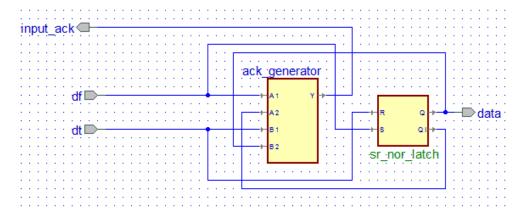

| 5.4 | Passive PUSH interface                                         | 47 |

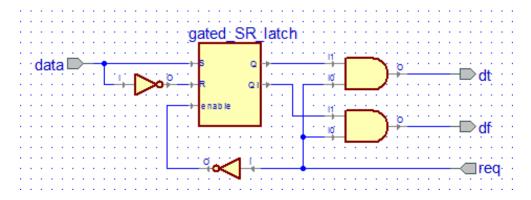

| 5.5 | Passive PULL interface                                            | 48 |

|-----|-------------------------------------------------------------------|----|

| 5.6 | Modified passive PULL interface                                   | 49 |

| 5.7 | Active PUSH interface                                             | 50 |

| 6.1 | Waveform from the test of the synchronous implementation          | 53 |

| 6.2 | Simulation output in execution window                             | 54 |

| 6.3 | Waveform from the test of one of the asynchronous implementations | 55 |

# List of Tables

| 2.1 | Truth table for a Muller C-element      | 13 |

|-----|-----------------------------------------|----|

| 3.1 | Balsa commands                          | 21 |

| 4.1 | Pin Description for the POR             | 24 |

| 4.2 | Parameter list for POR                  | 24 |

| 4.3 | Pin Description for a voltage monitor   | 25 |

| 4.4 | Parameter list for a voltage monitor    | 25 |

| 4.5 | Pin Description for a voltage regulator | 26 |

| 4.6 | Parameter list for voltage regulator    | 26 |

| 4.7 | Selvdd table for a voltage regulator    | 27 |

| 4.8 | Pin Description for a voltage reference | 27 |

| 4.9 | Parameter list for a voltage reference  | 28 |

| 5.1 | Signals used to change the state        | 34 |

| 6.1 | Area estimates for startup logic        | 57 |

| 6.2 | Area estimates | for the | interfaces |  |  |  |  |  |  |  |  | 5' | 7 |

|-----|----------------|---------|------------|--|--|--|--|--|--|--|--|----|---|

|     |                |         |            |  |  |  |  |  |  |  |  |    |   |

# Chapter 1

# Introduction

In this thesis the design and implementation of clock-less, or asynchronous, digital circuits is explored. More specifically, the circuit being made is a module controlling the startup process of a microcontroller. The unit controls several analog cell used in the startup process to provide a correct power up sequence for the microcontroller. The asynchronous startup logic is compared to a synchronous version to better see the benefits and drawbacks of the asynchronous implementation. To design the circuit the Balsa system is used, since ordinary hardware descriptive languages are geared towards synchronous design.

Chapter 2 goes through the basics of asynchronous circuits to give a better understanding of some of the concepts presented later in the thesis. This includes differences between asynchronous and synchronous systems, advantages and disadvantages, protocols and signaling schemes and some special cells. It also gives an overview of power consumption and metastability.

The balsa system and hardware descriptive language (HDL) is presented in chapter 3, to provide the base knowledge necessary to understand the balsa code presented later in this thesis.

Chapter 4 presents the specifications given for the startup system. This includes specifications for the various analog cells and behavioral specifications given for the startup logic controller.

The design process for the startup logic controller is described in chapter 5.

A synchronous design is first presented, and then the various asynchronous implementations. The interfaces used to enable communication between the asynchronous implementations and the analog cells, are presented last.

In chapter 6 the test and synthesis process is presented and the results are discussed. Comparison is made between the synchronous implementation and the asynchronous ones.

Chapter 7 presents the conclusions drawn from the work in this thesis.

The balsa code description of the startup circuit is included in the appendix A and the verilog code for the synchronous startup logic is included in appendix B. The generated verilog code has not been included as it is implemented with a Atmel technology, and therefor not testable without the technology package.

# Chapter 2

# Theory

## 2.1 Introduction to Asynchronous

Almost all digital circuits made today are almost without exception synchronous circuits. This is mainly because of the many tools which make design, simulation, verification and testing of large and complex circuits a relatively easy task. Additionally, the fact that all signals are binary and that all components share a common clock which defines a discrete time when all signals should be valid [1]. The discrete time lets designers focus their attention on functionality in stead of timing. Asynchronous circuits also require binary signals, but the components do not share a common and discrete time. Instead they use handshaking to sequence operations, communicate and synchronize events. This makes timing a bigger issue, but also gives asynchronous circuits other potential benefits.

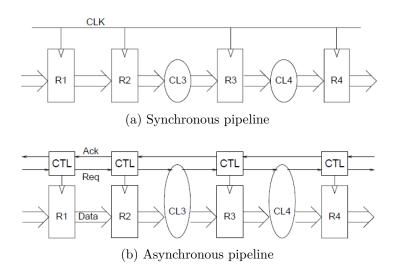

Figure 2.1 illustrates the difference between asynchronous and synchronous circuits. In the synchronous version the clock drives the communication, and in the asynchronous version the communication is controlled by handshakes between components. The CTL blocks in 2.1b signify control logic blocks that communicate with each other through handshake signals. The control signals have to be delayed to make sure that the data passing through the combinational logic, CL, is valid before being stored in the registers. In the synchronous pipeline, the clock switches at a frequency that guarantees that data through the combinational logic is valid before it is stored in the regis-

Figure 2.1: Comparison between synchronous and asynchronous pipelines

ters.

#### 2.1.1 Potential drawbacks and gain

Asynchronous circuits have certain benefits that make them attractive, like lower power consumption and robustness to variations in power supply and temperature, but they are also associated with certain problems. These problems include area overhead due to handshaking circuitry and the lack of electronic design automation (EDA) tools. A selected set of drawbacks are discussed below:

#### Lack of tools:

There are few EDA tools available for a designer who wishes to design asynchronous circuits, and many of the successful circuits which have been designed so far have more or less been designed manually. The few tools that are available lack the maturity needed to make designers confident about using them and their use widespread.

#### **Unfamiliarity:**

Few electronic engineers are offered courses in asynchronous design, and are for the most part only familiar with synchronous design. Companies are as a result less willing to start asynchronous projects since it involves extra training for the designers involved.

#### Area overhead:

Because of the extra handshaking circuitry involved in asynchronous circuits, there may in some cases be a significant area overhead compared to a synchronous version. Every circuit component needs circuitry to control request and acknowledge signals, and this overhead increases not only the area, but can also lead to extra switching. This can result in reduced speed and increased power consumption compared.

#### Complex designs:

The overhead does not only decrease quality compared to the ideal case; it could also lead to more complex designs. The added complexity, in addition to the lack of mature tools can make asynchronous design even harder compared to synchronous design.

#### Testing and debugging:

Scannable flip-flops and automated test-pattern generation has made testing of synchronous circuits efficient and reliable. Many asynchronous design styles introduce loops which make observability, controllability and test-pattern generation challenging. Debugging failures can also be difficult because of the lack of a clock. Asynchronous circuits operate at maximum possible speed at all times, and the clock frequency can not be lowered to potentially reveal the location of errors.

Event though there are many problems associated with asynchronous circuits there are some potential benefits. For some applications these benefits may outweigh the drawbacks, making an asynchronous implementation beneficial. The potential benefits of asynchronous design are presented below.

#### Lower power consumption:

The activity of the global clock in a synchronous circuit makes the circuit consume power even when it is not processing data. Some synchronous designs reduce this problem with clock gating, but the clock driver still has to constantly provide a powerful clock to always be able to reach all parts of the circuit. In asynchronous circuits, the switching activity is local and parts of the circuit not involved in the current operation are inactive.

#### Less electromagnetic noise:

A global clock makes sure that most transitions in the circuit are triggered by the positive edge of the clock and come in intervals determined by the clock frequency. This results in peak currents that are much higher than the average power, causing electromagnetic noise. In asynchronous systems, the transitions are spread out more evenly over time, mostly consuming an average amount of power. This greatly reduces the noise.

#### No clock skew:

Clock skew refers to the clock arriving at different times to different parts of the circuit. Because of clock skew, the clock speed sometimes has to be reduced to ensure correct operation. Because of the local handshaking, this is not an issue in asynchronous design.

#### Robustness:

Asynchronous systems have no timing constraints, and can in theory wait for a logic value to settle before continuing with the operation, thus avoiding metastability. Asynchronous systems, in addition, are robust against physical variations like temperature, supply voltage and fabrication parameters. This is because the critical paths can use as long as they have to before completing, without causing trouble for the rest of the circuit. If temperature or supply voltage variations increase delays in the circuit, the operation will be slower, but it will not halt.

#### Speed:

The critical path in synchronous designs determines the clock speed of the entire circuit, and thus limiting the circuits overall performance by reducing the speed of all paths. Because there is no clock limiting potential speed, asynchronous systems will over time operate at average-case performance.

For more in depth information about the drawbacks and benefits of asynchronous design [1] and [2] is recomended.

#### 2.1.2 Protocols

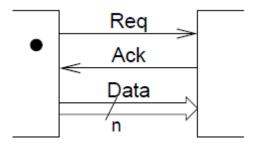

Communication between different components in an asynchronous system happens over a channel in the form of handshakes. These handshakes consists of some sort of request and acknowledge signals in addition to eventual data being transfered. The handshake has an active part which issues the request and a passive part which responds with an acknowledge. If data is being transfered the active side may either send or request data, also known as PUSHing and PULLing. A channel where data is being actively sent is called a PUSH channel, while a channel where the data is requested by the active side is called a PULL channel. It is called PUSHing because the active side

can be described as "pushing" data to the passive side. Similarly, The other kind of transaction would be a PULL, as the data could be seen as "pulled" from the passive side to the active side. Dataless channels also exist and is mostly used for synchronization between different parts of the circuit. These channels are known as sync channels.

The way components communicate with each other in an asynchronous circuit is defined in a protocol. Several different protocols for asynchronous communication have been proposed and developed. The two most common signaling schemes, single-rail and dual-rail, with their variations of 2- and 4-phase protocols are discussed here in some detail, while other protocols are briefly mentioned at the end. The different protocols have benefits compared to the others for different types of circuits.

#### Single-rail protocols

In single-rail protocols, each bit of data is transferred over a single line, with the request and acknowledge signals on separate lines. The single-rail protocols are often called bundled-data protocols, as the request and acknowledge signals are bundled together with the data signal(s). The single-rail scheme can be in the form of a 2-phase or 4-phase protocol, which differs in how many transition events are needed to complete a data transfer.

Figure 2.2: Single-rail scheme

In figure 2.2, the black dot represents the active side of the transaction. A request, along with the guarantee of valid data, is issued from the active to the passive side of the channel. An acknowledgment from the passive side means that the data is received. This transaction is a PUSH. If the data lines had been reversed, the request would have been a request for data from

the right. The acknowledgment would then mean that the data is valid and ready. This other kind of transaction would be a PULL.

Single-rail control circuits are said to be speed-independent, while the data path circuits are self-timed. These concepts are explained later. Data representation is not affected by what single-rail protocol (2-phase or 4-phase) is used since it is separated from the controlling wires, as opposed to the dual-rail protocols discussed later on.

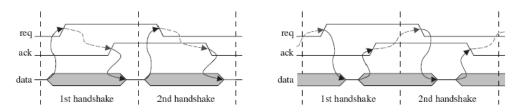

#### 4-phase single-rail (4PSR)

As mentioned, 4-phase means that four events, are needed to complete a data transfer. This can be illustrated as in figure 2.3. The active side of the transaction sets request high, followed by the passive side setting acknowledge high when data either has been received or is ready and valid, depending on whether the transfer is a PUSH or PULL, respectively. The active part then responds by setting request low, followed by the passive part setting acknowledge low. The active part can then start a new transaction. This is true for both push and pull transactions. 4-phase uses twice as many signaling edges as 2-phase, but the control circuits in 4-phase are often easier to implement. When driving storage elements, for instance, level-controlled latches can be driven directly from the signaling lines. The RTZ (return-to-zero) property of the protocol also means that the control lines maintain the same logical level after performing a transaction as they were before.

Figure 2.3: 4-phase Single-rail

#### 2-phase single-rail (2PSR)

The 2-phase single-rail protocol interprets all transitions on the controlling wires as a signaling event. The level of the signal (binary 0 or 1) is not

important - just the transition - with a rising edge being equivalent to a falling edge. Figure 2.4 illustrates this. The active side transitions the request line, followed by the passive side transitioning the acknowledge line when the data either has been received or is ready and valid, depending on whether the transfer is a PUSH or PULL, respectively. Then, the active part is cleared to initiate a new transfer.

Figure 2.4: 2-phase Single-rail

Two transitions would in theory be faster than four transitions, but as mentioned, the control circuits for 2-phase protocols tend to be more complex, resulting in area overhead and possible speed degradation. The choice between 2-phase and 4-phase will depend on the function or system to be implemented, and one will not be better than the other for all applications.

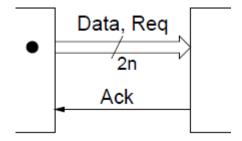

#### Dual-rail protocols

Dual-rail signaling uses two wires for each data bit being transferred, where the request is implicit in the signal wires. It is common to represent the data bit d with the wires dt and df, where the t and f stands for true and false. The true wire indicates a logical 1 and the false wire indicates a logical 0. Only one acknowledge line is needed between components. This is illustrated in figure 2.5. The dual-rail signaling scheme uses two wires for each bit, along with one acknowledge line, resulting in 2N+1 wires for each data channel, as opposed to the N+2 wires needed for each data channel in the single-rail protocol. As for single-rail, dual-rail comes in the form of 2-phase and 4-phase protocols, pointing to the number of transition events needed to complete a data transfer.

Figure 2.5: Dual-rail scheme

#### 4-phase dual-rail (4PDR)

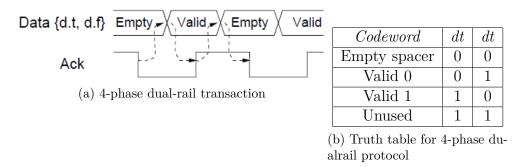

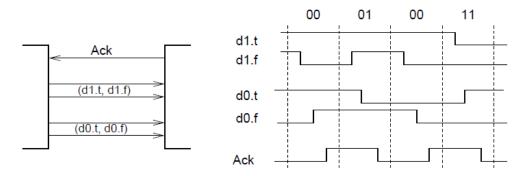

In the 4-phase dual-rail protocol, it is common to use one-hot encoding, where a valid 1 sets the true wire high, and a valid 0 sets the false wire high. Setting both wires to logical 0 represents an empty value, which is used as a spacer. The code words for this type of encoding is shown in table 2.6b, while a typical transaction is shown in figure 2.6a.

Figure 2.6: communication over 4-phase dualrail protocol

A data transfer is initiated with the data wires being set to a valid value. The other party acknowledges this by setting the acknowledge line high. The data wires are then returned to the empty value, which the other party responds to by setting the acknowledge line low. After this, a new transaction can be started. Because the data is inherent in the request and all the data bits need to be valid before an acknowledge, the protocol is said to be delay-insensitive [1]. This can make the protocol very attractive for some implementations. The obvious drawback with this protocol is the number of wires needed, increasing the area and switching activity.

#### 2-phase dual-rail (2PDR)

Like the 4PDR protocol, the 2-phase dual-rail protocol also uses two wires per bit. Though instead of using the levels of the wires, it uses the transitions to encode information. The 2-phase protocol does not rely on the spacer; in stead, a new codeword is received when exactly one wire of each bit has made a transition. This is illustrated for a 2-bit channel in figure 2.7.

Figure 2.7: 2-phase dual-rail transaction

The true and false wires represent whether or not a logical 1 or 0 is being transmitted and both bits has to have a transaction on exactly one wire for data to be valid. In the figure, the transaction of the data word 00 is initiated with a transition on the false wires of both bits, which the receiver acknowledges by transitioning the acknowledge line. The next transaction is of the data word 01, which is represented with the false wire of the MSB and the true wire of the LSB having transitions, which again is acknowledged by a transition on the acknowledge line, and so on. The 2-phase dual-rail protocol has the advantage of decreased switching activity over the 4-phase version, but has the same amount of wires.

#### Other protocols

One-hot encoding and N-of-M encoding are other types protocols that are used, and the dual-rail protocols can be seen as subsets of these. One-hot circuits represent n bits with 2<sup>n</sup> wires. Each line can then represent n bits of information. The Null Convention Logic (NCL) uses a 4-phase protocol where each wire represents either DATA or NULL [3]. In theory, an arbitrary number of wires can be used (for instance representing 10 possible values

with 10 wires), but typically only two wires are used, in the same way as for dual-rail, representing true or false.

N-of-M encoding uses groups of M wires to encode data values, and considers data to be valid as soon as N wires are activated. 1-of-2 encoding would be the dual-rail encoding. N-of-M codes are as mentioned for the dual-rail encoding said to be delay-insensitive [4].

Another delay-insensitive protocol, is the Phased Logic [5] which uses the Level-Encoded 2-phase Dual-Rail (LEDR) encoding scheme. Without going into detail, this encoding scheme uses two wires, where one wire transmits the logical value, and the other transmits phase information.

#### 2.1.3 Special cells

Although comprised of the same basic components, there are some basic concepts which set synchronous and asynchronous circuits apart even at the lowest level. Some cells that are rarely seen in synchronous circuits are very important to asynchronous circuits, and the missing discrete time in asynchronous circuits mean that special timing considerations must be taken. These aspects are discussed below.

Asynchronous circuits can usually be constructed from the same components as synchronous circuits. This means that they can be implemented using standard cells like AND, NAND, OR and so on from VLSI(Very-Large-Scale-Integration) libraries and there is no need to design completely new cells. However, some standard cells are usually essential to the design of asynchronous circuits. Two of them are presented in the following sub sections, namely the event synchronizing C-element and the arbitrating Mutex (mutual exclusion unit).

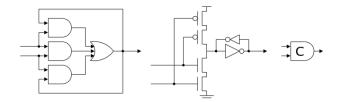

#### Muller C-element

The Muller C-element is very common in asynchronous designs, and was originally defined by David E. Muller as a way of synchronizing events [1]. Figure 2.8 shows a gate level and transistor implementation of a C-element, in addition to the symbol.

Figure 2.8: Muller C-element

There are several ways of implementing the C-element. Designing it from scratch as a new cell will give the best performance, but it can also be constructed from AND and OR gates. Regardless, it has to adhere to the truth table given in table 2.1. Here we see that the output only transitions if both inputs have the same value. It behaves like an OR-port when the output is high and like an AND-port when the output is low. The special behavior of the C-element makes it well suited for synchronizing signals.

| input a | input b | output y         |

|---------|---------|------------------|

| 0       | 0       | 0                |

| 0       | 1       | previous y value |

| 1       | 0       | previous y value |

| 1       | 1       | 1                |

Table 2.1: Truth table for a Muller C-element

#### Mutex

A mutex is employed in arbitration between circuit components trying to access the same resource at approximately the same time. This is crucial in an asynchronous circuit, because sometimes it is difficult to completely determine the order in which events happen. Latches and other bi-stable devices may become metastable if two signals try to change the state of the device at the same time. A common 4-phase implementation involves cross-coupled NAND gates, and has the following behavior:

The mutex has two request inputs and two corresponding grant outputs. If both requests arrive at approximately the same time, grant 1 will be triggered. Grant 2 will not be triggered until request 1 is set low. The Mutex prevents both outputs becoming active at the same time and prevents a potentially metastable state. If the requests arrive close to one another, the Mutex may use a long time to decide [6].

## 2.2 Power consumption

The power consumption in CMOS technology can be split into three main components [7]; dynamic, leakage and short-circuit. This is shown in the following equation:

$$P_{total} = P_{dynamic} + P_{short-circuit} + P_{leakage}$$

(2.1)

The first term represents the dynamic component of power, which is determined by the switching activity in the circuit. The second term is due to the direct-path short circuit current,  $I_{sc}$ , which arises when both the NMOS and PMOS transistors are simultaneously active, conducting current directly from supply to ground. The last term is the leakage component,  $P_{leakage}$ , which is primarily determined by fabrication technology considerations.

### 2.2.1 Dynamic power dissipation

In a CMOS circuit, each node have an associated capacitance, C, consisting of a load capacitance and parasitic capacitances. During operation, C is charged when the node switches value from logical zero to logical one and each time an amount of power is dissipated. The amount of power dissipated, also known as the dynamic power component, is given in equation 2.2:

$$P_{dynamic} = \alpha C V_{dd}^2 f_{clk} \tag{2.2}$$

$V_{dd}$  is the supply voltage,  $f_{clk}$  is the clock frequency and  $\alpha$  is the average number of  $0 \to 1$  transitions per clock cycle. Equation 2.2 assumes that a logical one refers to the voltage  $V_{dd}$ , the power dissipated each transition is then  $CV_{dd}^2$ . The number of transitions is given as  $\alpha$  times  $f_{clk}$ .

#### 2.2.2 Short circuit power dissipation

In static CMOS, when the input to a logic gate changes value, there will be a short period of time when both the N- and P-network are partially conducting while the input voltage  $V_{in}$  changes value. This results in short circuit power dissipation due to the current flowing from  $V_{dd}$  directly to ground. Both N- and P-networks are (partially) on when  $V_{thn} < V_{in} < (V_{dd} - |V_{thp}|)$  [8]. Here the voltages  $V_{thn}$  and  $V_{thp}$  are the threshold voltages of the NMOS and PMOS transistors in the logic gate. [8] states that with careful design, this power consumption source can be kept to be less than 15 % of the dynamic power.

### 2.2.3 Leakage power dissipation

Leakage power is power consumption due to unintended leakage currents flowing though transistors. The leakage current can be split into three main components [8]: reverse-bias diode leakage on the transistor drains, tunneling current through gate oxide, and sub-threshold leakage through the channel of a transistor turned off. The diode leakage occurs when a transistor is turned off and the drain/source is reverse-biased by another device. The leakage current through the gate oxide happens if the oxide is sufficiently thin, though the probability of leakage current drops off exponentially with oxide thickness. The sub-threshold leakage current occurs due to carrier diffusion between the source and the drain nodes when the gate-source voltage,  $V_{gs}$ , has exceeded the weak inversion point, but is still below the threshold voltage  $V_{th}$ . According to [9] the power consumption due to leakage increases with shrinking transistor technologies and is set to exceeding total dynamic power consumption as technology drops below the 65nm feature size.

## 2.3 Metastability

Flip-flops have certain constraints with regards to the setup and hold time of their input. Violations of these constraints make the flip-flop enter a state where its output is unpredictable, this state is known as metastable state. When a flip-flop is in a metastable state, its output oscillate between a logic 0 and 1. Metastability typically occurs in these cases:

- When the input signal is an asynchronous signal.

- When the clock skew/slew is too much (rise and fall time are more than the tolerable values).

- When interfacing two domains operating at two different frequencies or at the same frequency but with different phase.

- When the combinatorial delay is such that flip-flop data input changes in the critical window (setup + hold window)

A common way to measure metastability is by the mean time between failure. A simplified way of calculating the MTBF is shown in equation 2.3 [10]. The formula uses the worst case way of representing the settling time of the flip-flop. A more accurate formula would contain an exponent on the form  $e^T$  where T depends on the settling time of the flip-flop in the case of metastability and the difference in time between the clock period and the propagation delay of the flip-flop.

$$MTBF = \frac{1}{f_{clk}f_{in}t_{pd}} \tag{2.3}$$

Where the  $f_{clk}$  is the frequency of the clock the flip-slop uses,  $f_{in}$  is the frequency of the input and  $t_{pd}$  is the propagation delay through the flip-flop. A more precise formula is presented in [11].

# Chapter 3

# Balsa

### 3.1 Introduction to balsa

This chapter introduces Balsa and some of its concepts to provide the basis necessary to understand the asynchronous design and netlist generation done in this thesis. A more thorough description of the Balsa system and language is given in the Balsa manual [12]. Balsa is freely distributed on the University of Manchester's home page [13].

Balsa is the name of both a framework for synthesizing asynchronous systems and a hardware descriptive language (HDL) used to describe such systems. It has been developed over several years by the ATP group (Advanced Processor Technologies) of the School of Computer Science, University of Manchester, and is based on the Tangram system made by Philips [12]. Balsa provides a higher abstraction level than gate level design of asynchronous circuits by introducing handshake components. More specifically Balsa provides a one-to-one mapping between the language constructs used to describe a circuit and the handshake circuit generated. While Balsa will not necessarily give the solution with the highest performance or smallest area, it makes it easier for the user to see the architecture of the generated circuit and make predictable changes to the implementation when changing the code. Balsa is most of all an attempt at building a tool capable of synthesizing large asynchronous systems while still keeping the compilation transparent and understandable.

A circuit described in Balsa is compiled into handshake components connected together by communication channels. Communication between the components takes place as handshakes defined by a protocol like the ones described in subsection 2.1.2. The handshakes may transfer data between the components or act as a control signal. If an asynchronous handshake circuit is designed in a common HDL like verilog or VHDL the choice of communication protocol between handshake modules has to be made at an early stage, as every component and module in the design have to follow the protocol. A lot of effort has to be focused on making the implementation fit the protocol during the design, rather than focusing it on functionality and optimization of the circuit. An eventual change of protocol at a late stage would necessitate a major rewrite of the circuit, though this is not the case with Balsa. With Balsa the focus of the design is on functionality and the protocol used is only determined when the a netlist is generated. This makes it possible to compare the different protocols in terms of area and performance to get the most suited implementation.

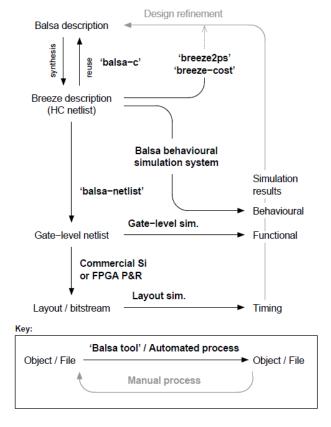

## 3.2 Balsa system

The balsa system consists of several tools [12], and some of the most important ones are listed below.

- balsa-c: the compiler for the Balsa language. The output of the compiler is an intermediate language breeze.

- balsa-netlist: produces a netlist appropriate to the target technology/CAD framework from a Breeze description.

- **breeze2ps:** a tool which produces a postscript file of the handshake circuit graph.

- breeze-cost: a tool which gives an area cost estimate of the circuit.

- balsa-md: a tool for generating makefiles

- balsa-mgr: a graphical front-end to balsa-md with project management facilities.

- balsa-make-test: automatically generates test harness for a Balsa description.

• **breeze-sim-control:** a graphical front-end to the simulation and visualization environment

Balsa-c interprets code written in the Balsa HDL into a handshake-component network into the intermediate breeze format. From this format cost estimations, behavioral simulations and network visualizations can be performed to improve the design. The design can also be compiled into a Verilog netlist via balsa-netlist, which is usable for other tools. Figure 3.1 provides a summary of the Balsa design flow.

Figure 3.1: balsa design flow

The current Balsa version supports three different protocols; 4PSR, 4PDR and a 1-of-4 encoding scheme. Balsa also provides a few technologies for netlist production as extension packages. Some kind of technology has to be installed to make netlist production possible. In this design a technology provided by Atmel used for netlist generation.

## 3.3 Balsa language

This is a short introduction to the balsa language to provide the background necessary to understand the code presented in section 5.2. For a more thorough and in depth description of the balsa HDL, the balsa manual is recommended [12].

As mentioned in section 3.1, the balsa HDL is closely related to the handshake components making up the circuit implementation.

#### 3.3.1 Language constructs

Table 3.1 present the different commands available in the balsa HDL.

**Sync** is a dataless handshake. The code initiates a handshake and halts the circuit until handshake is completed.

The two operators <- and -> are used to assign data to and from channels. <- is used to assign a value to an output channel, while -> is used to assign a value from an input channel to either an output channel or a variable. The := operator is used to assign the result of an expression to a variable.

The ; operator is used to denote sequentiality between statements. If two statements are separated by ;, the first statement is performed before the other. On the other hand the || operator denotes concurrency. Two statements separated by || are executed at the same time.

**continue** is effectively a null command. It has no effect, but may be required for syntactic correctness in some instances. The **halt** command causes a process thread to deadlock.

The **loop** command can cause an infinite repetition of a block of code, or it can be finite if a **while** construct is added. The **for** loop construct is used for iteratively laying out repetitive structures, not for behavioral description as many are used to.

Balsa has **if** and **case** constructs to achieve conditional execution. While **case** statements only have one guard expression, while **if** statements can

| Command              | Description                                   |

|----------------------|-----------------------------------------------|

| sync                 | dataless handshake for control                |

| <-                   | handshake data transfer from an expression to |

|                      | an output port                                |

| ->                   | handshake data transfer to a variable from an |

|                      | input port                                    |

| :=                   | assigns a value to a variable                 |

| ;                    | sequential operator                           |

|                      | parallel operator                             |

| continue             | null command                                  |

| halt                 | causes deadlock                               |

| loop end             | loop forever                                  |

| loop while then also | conditional loop with optional initial com-   |

| end                  | mand                                          |

| for in then end      | iteration used for repeating structures       |

| if then else end     | conditional execution, may have multiple      |

|                      | guarded commands                              |

| case of end          | conditional execution based on constant ex-   |

|                      | pressions                                     |

| select end           | non-arbitrated choice operator                |

| arbitrate end        | arbitrated choice operator                    |

| -> then end          | handshake enclosure                           |

Table 3.1: Balsa commands

have several.

The select **statement** chooses between the two input channels by waiting for data on either channel to arrive. The code enclosed between the select statement and the **end** is executed. If there is a possibility that the inputs arrive at the same time, the **arbitrate** statement must be used instead to ensure correct operation.

Normally handshakes are points of synchronization for assignments between channels or assignments between channels and variables. A transfer is requested and when all parties to the transaction are ready, the transfer completes. After completion of the handshake, the data provider is free to remove the data. If the data on a channel is required more than once, it must be stored in a variable. Balsa has two language constructs that allow the handshake on a channel to be held open whilst a sequence of actions completes. The handshake is said to enclose the other commands. Handshake enclosure can be achieved by use of the **select** or **arbitrate** command or by assigning channels into a command using the syntax: *<channels> -> then <commands> end*

Common operators (such as and, or, +, -, =, > and <) that you find in almost every language are also found in the Balsa language.

# Chapter 4

# Startup logic specification

# 4.1 Startup system

In this project a system for ensuring the correct startup sequence for a microcontroller is designed. The system is shown in figure 4.1.

Figure 4.1: Startup system with controller and analog cells

The startup system consists of a controller labeled startup logic and several analog cells which it is meant to interface with. The specifications for the analog cells was given as follows.

## 4.2 Analog Cells

## 4.2.1 Power-on-Reset (POR) generator

A generator is a microcontroller peripheral that generates an active low reset signal, porneg, when power is applied to the device. This is to ensure that the device is powered up in a known state. In this design the POR cell monitors the voltage from two power supplies. When both voltages are below the given threshold, its output is a logic zero. When one of the power inputs rises above the threshold, its output stays zero for a predefined time, Tpor, before it then goes to a logic one.

| Pin name | Direction | Size             | Comment                   |

|----------|-----------|------------------|---------------------------|

| power1   | input     | AVR32 POWER BITS | Power supply 1 monitored  |

|          |           |                  | by the POR                |

| power2   | input     | AVR32 POWER BITS | Power supply 2 monitored  |

|          |           |                  | by the POR                |

| porneg   | output    | 1                | Power-On Reset output - 0 |

|          |           |                  | : reset, 1 : not reset    |

Table 4.1: Pin Description for the POR

| Parameter Name | Default Value | Used for                  |

|----------------|---------------|---------------------------|

| Threshold      | 1000 mV       | POR threshold             |

| Tpor           | 100 ns        | minimum duration of reset |

Table 4.2: Parameter list for POR

## 4.2.2 Voltage Monitor

A voltage monitor is a microcontroller peripheral used to monitor a power supply voltage, and signal whether the voltage is above or below a given threshold voltage, VThreshold. The vok signal indicates a voltage above the threshold with a logic one, and a zero if the voltage is below the threshold. When the cell is enabled it requires a certain amount of time, TReady, to properly turn itself on, and the signal vok signal is not valid before that. The voltage monitor uses the ready to indicate whether it has been turned on, a logic one indicated that it is on. If the supply voltage is changed there is a given delay, TMeasure, before the vok signal is updated.

| Pin name | Direction | Size             | Comment                                          |  |  |

|----------|-----------|------------------|--------------------------------------------------|--|--|

| power    | input     | AVR32 POWER BITS | Power supply monitored by                        |  |  |

|          |           |                  | the voltage monitor                              |  |  |

| enable   | input     | 1                | Enable signal: 1: enabled,                       |  |  |

|          |           |                  | 0 : disabled                                     |  |  |

| ready    | output    | 1                | Signals that the voltage                         |  |  |

|          |           |                  | monitor is ready (after en-                      |  |  |

|          |           |                  | able 0->1)                                       |  |  |

| vok      | output    | 1                | output - 0 :                                     |  |  |

|          |           |                  | power <threshold, 1="" :<="" td=""></threshold,> |  |  |

|          |           |                  | power>threshold                                  |  |  |

Table 4.3: Pin Description for a voltage monitor

| Parameter Name | Default Value | Used for                  |

|----------------|---------------|---------------------------|

| VThreshold     | 1000 mV       | Voltage monitor threshold |

| TReady         | 1000 ns       | enable->ready time        |

| TMeasure       | 100 ns        | time needed to update     |

|                |               | vmon after a change in    |

|                |               | power                     |

Table 4.4: Parameter list for a voltage monitor

## 4.2.3 Voltage Regulator

A voltage regulator is a device that is used to automatically maintain a constant voltage level. This voltage regulator can supply several different output voltages determined by the logic value of the selvdd input given in table 4.7. The bandgap input is a reference voltage used to generate the correct output voltage. When enabled, the voltage reference needs some time to properly turn itself on. Correct operation is indicated by the ready signal outputting a logic one. If the selvdd input is changed, the ready signal goes low until the output voltage has been updated.

| Pin name | Direction   Size   Comment |                   | Comment                     |

|----------|----------------------------|-------------------|-----------------------------|

| powerin  | input                      | AVR32 POWER BITS  | input from power supply     |

| powerout | output                     | AVR32 POWER BITS  | output power                |

| enable   | input                      | 1                 | Enable signal: 1: enabled,  |

|          |                            |                   | 0 : disabled                |

| bandgap  | input                      | 1                 | Bandgap reference voltage   |

| selvdd   | input                      | AVR32 VREG SELVDD | see next table              |

|          |                            | BITS              |                             |

| ready    | output                     | 1                 | Signals that the voltage    |

|          |                            |                   | monitor is ready (after en- |

|          |                            |                   | able 0->1)                  |

Table 4.5: Pin Description for a voltage regulator

| Parameter Name | Default Value | Used for                    |

|----------------|---------------|-----------------------------|

| TStart         | 20000ns       | Time needed by the regula-  |

|                |               | tor to reach target voltage |

|                |               | after enable 0->1           |

| TChange        | 1000 ns       | time needed to update       |

|                |               | powerout after a change in  |

|                |               | selvdd                      |

Table 4.6: Parameter list for voltage regulator

| Selvdd | bandgap | powerout(mV) |

|--------|---------|--------------|

| XXX    | 0       | 0            |

| 000    | 1       | 600          |

| 001    | 1       | 800          |

| 010    | 1       | 1000         |

| 011    | 1       | 1200         |

| 100    | 1       | 1400         |

| 101    | 1       | 1600         |

| 110    | 1       | 1800         |

| 111    | 1       | 2000         |

Table 4.7: Selvdd table for a voltage regulator

# 4.2.4 Voltage Reference

A voltage reference is a device that outputs a constant voltage regardless of the load on the device, power supply variations, temperature changes, and the passage of time. This specific voltage reference is modeled after a bandgap reference voltage and is used to provide a stable voltage to the voltage regulator. When enabled, the voltage reference needs some time to properly turn itself on. Correct operation is indicated by the *ready* signal outputting a logic one. The *bandgap* voltage is a voltage, but is modeled in this project as a logic signal for the sake of simplicity. A logic one indicates the correct bandgap voltage.

| Pin name | Direction | Size                         | Comment                     |  |  |

|----------|-----------|------------------------------|-----------------------------|--|--|

| powerin  | input     | AVR32 POWER BITS             | input from power supply     |  |  |

| enable   | input     | 1 Enable signal : 1 : enable |                             |  |  |

|          |           |                              | 0 : disabled                |  |  |

| bandgap  | output    | 1                            | Bandgap reference voltage   |  |  |

| ready    | output    | 1                            | Signals that the voltage    |  |  |

|          |           |                              | monitor is ready (after en- |  |  |

|          |           |                              | able 0->1)                  |  |  |

Table 4.8: Pin Description for a voltage reference

| Parameter Name | Default Value | Used for           |

|----------------|---------------|--------------------|

| TReady         | 2000 ns       | enable->ready time |

Table 4.9: Parameter list for a voltage reference

## 4.3 Startup logic Controller

The following specification was given for the startup system

Two power supply inputs VDDIO1 and VDDIO2 may rise from 0v to 3.3V (for VDDIO1) or 5V (VDDIO2). When VDDIO1 or VDDIO2 rise above 1.0V the POR cell releases its reset, porneg. As long as the reset is active the startup logic is kept in a RESET state and every analog peripheral should be disabled. When the reset is released the startup logic will then do the following operations:

- Turn-on Voltage monitor #1 and check if *VDDIO*1>1.6V (*VDDIO*1 is "good").

- Turn-on Voltage monitor #2 and check if VDDIO2>3.3V (VDDIO2 is "good").

- if VDDIO1 is good and VDDIO2 is "bad": Turn-on voltage reference #1, wait for it to be ready and then turn-on voltage regulator #1 (selvdd = 600mv).

- if VDDIO1 is bad and VDDIO2 is good: Turn-on voltage reference #2, wait for it to be ready and then turn-on voltage regulator #2 (selvdd = 600 mV).

- if VDDIO1 and VDDIO2 are good: Turn-on voltage reference #2, wait for it to be ready and then turn-on voltage regulator #2 (selvdd = 600mV).

- if *VDDIO*1 and *VDDIO*2 are bad, wait for one of them to be good.

- When one of the voltage regulators has been turned on (with *selvdd* set to 600mV initially), the startup logic must increase the output voltage until the third voltage monitor says "voltage OK" (Threshold = 1.6V).

# 4.4 Asynchronous specification

The asynchronous implementation needs to follow the specification given in section 4.3, other than that only one specification was given; that the 4-phase dual-rail protocol should be used for communication.

# Chapter 5

# Design

## 5.1 Synchronous implementation

## 5.1.1 Design Considerations

The synchronous startup logic interacts and controls several analog cells. As the signals from the analog peripherals are asynchronous there is a definite chance that the will be metastability problems on the inputs.

By using formula 2.3 in section 2.3 the MTBF can be calculated. The available clock in the implementation technology was given as 20MHz and the given propagation delay of the flip-flops was between 0.5 ns and 1 ns depending on load, temperature and other conditions. Looking at the ready input from one of the voltage regulators where the update time TChange is 1000 ns, this gives a MTBF between  $0.5\mu s$  and  $1\mu s$ , which is a clearly an unacceptable number, and this is without considering the other any other ports as well.

A simple way of improving the MTBF is by using a slower clock, though that will impact performance. Which could be somewhat feasible considering that the startup logic spends a lot of time waiting for inputs from the analog cells, however since the MTBF is very bad the improvement isn't likely to be good enough. The most common way of improving the MTBF is by adding successive flipflops to improve synchronization on the input [11]. This gives any metastability problems more time to settle with each successive flip-flop, with the downside of added latency on the input and added area due to the extra flip-flops. A two-stage synchronizer is shown below in figure 5.1, though a three-stage synchronizer was used in the design.

Figure 5.1: Two stage synchronizer

### 5.1.2 Implementation

The startup logic controller was implemented as a straight forward Mealy state machine, meaning that the next stage is dependent on both the current state and by the values of its inputs. The specified behavior of the system is mostly sequential with the exception when the startup logic increments the output voltage of one of the system by incrementing the *selvdd* signal to one of the voltage regulators. A simplified state diagram is shown in figure 5.2.

The system starts in the RESET state waiting for the reset signal from the POR cell. None of the analog cells are enabled in this state. When the reset is released it moves on to the next state MON ON.

In the  $MON\_ON$  stage the two voltage monitors monitoring the power supply inputs are enabled. When both of the monitors have signaled that they are ready, the startup logic moves on to their next state  $MON\_SELECT$ .

In the  $MON\_SELECT$  state the next state is determined by the vok signals from the two voltage monitors. If the vok signal from monitor 2 is high, the next state is  $REF2\_ON$ . If the vok signal from monitor two is low and the vok signal from monitor 1 is high, the next state is  $REF1\_ON$ . If both signals are low the state machine stays in the  $MON\_SELECT$  state until one of the signals goes high, and then sets the corresponding next state.

Figure 5.2: Simplified state Diagram of the Synchronous implementation

Both  $REF1\_ON$  and  $REF2\_ON$  are equal in behavior, though they control different voltage references. In both states the matching voltage reference is enabled and the state machine loops in that state until the ready signal from the voltage reference is set high. Then the next state is set to  $VREG1\_ON$  or  $VREG2\_ON$ , depending on which state the state machine is currently in.

In the VREG states voltage monitor 3 and the appropriate voltage regulator is enabled and the initial selvdd value set. The state machine loops in the state until voltage monitor 3 signals that it is ready and then the next state is set to INC.

The state INC and INC2 controls the incrementation of the output voltage VDDCORE by incrementing the selvdd signal to the enabled voltage regulator, until the vok signal from voltage monitor 3 goes high. Selvdd is incremented whenever the voltage regulator signals that it is ready, as long as the vok signal from voltage monitor 3 is low and selvdd haven't been incremented too much. By too much it is meant that the counter used to assign selvdd its value hasn't reached the binary value 111. Incrementing further would make the counter over wrap and get the binary value 000. The state machine loops from the INC state to INC2 and back again. All the incrementation behavior is done in the INC state, the only purpose of the INC2 state is to give voltage monitor 3 time to update its vok signal.

Without the INC2 state the startup logic increments selvdd event though the output voltage from the voltage regulator was over the defined threshold. This is because there is a delay between the time when VDDCORE reaches its threshold value and the time when voltage monitor 3 detects this. When the vok signal is set high the state machine loops in the INC state, though nothing is done until the state machine is reset by the reset signal from POR going low.

Table 5.1 shows which signals and which value they need to have for the state machine to move from the current state to the next state.

| Current state | Inputs values changing state           | Next state |

|---------------|----------------------------------------|------------|

| RESET         | POR reset = 1                          | MON_ON     |

| MON_ON        | $mon1\_ready, mon2\_ready = 1$         | MON_SELECT |

| MON_SELECT    | $mon2\_vok = 1$                        | REF2_ON    |

| MON_SELECT    | $mon2\_vok = 0, mon1\_ready = 1$       | REF1_ON    |

| REF2_ON       | $ref2\_ready = 1$                      | VREG2_ON   |

| REF1_ON       | $ref1\_ready = 1$                      | VREG1_ON   |

| VREG2_ON      | mon3_ready                             | INC        |

| VREG1_ON      | mon3_ready                             | INC        |

| INC           | $mon3\_vok = 0, mon3\_ready,$          | INC2       |

|               | $  (vreg1\_ready    vreg2\_ready) =  $ |            |

|               | 1                                      |            |

| INC2          |                                        | INC        |

Table 5.1: Signals used to change the state

## 5.2 Asynchronous Implementation

### 5.2.1 Description

For the asynchronous implementation two different kinds of solutions was made, one modeled as a state machine like the synchronous implementation, and the other written to make an optimized implementation without regard for the readability of the code. The analog cells which the startup logic interacts with are the same, with the exception that interfaces has been added to enable communication in the specified 4-phase dual rail protocol.

Three different versions was made for both the state machine and optimized implementations. The difference between them is the interface used to connect to voltage monitor 1 and 2, meaning that the majority of the circuit is still the same between the different versions. The corresponding state machine and optimized implementations uses the same interfaces, meaning that state machine implementation 1 uses the same interfaces as the first optimized implementation, and so on.

## 5.2.2 Design Considerations

Balsa doesn't support passive pull ports. All data ports are either passive PUSH, active PUSH or active PULL ports. The recommended replacement is an active PUSH port enclosed by a sync select. The active PULL port on the receiving end of the channel functions as usual. An alternative solution is an active PULL port and an active PUSH port as earlier, but without the using the sync channel enclosure. In this case balsa generates a so called passivator between the two ports. A passivator is a "unit" with a passive PUSH port connected to the active PUSH port, and a passive PULL port connected to the active PULL port. The passivator functions as memory, storing the data from the PUSH channel until the PULL channel requests it, or waiting until the PUSH before acknowledging (sending the data) the PULL. To make this work properly there need to be a matching number of PULLs and PUSHes. If not, the procedures (threads) may end up waiting for a PUSH that never comes, or try PULLing data that won't be sent. This will make the threads controlling the port lock, possibly halting the entire module/procedure.

### 5.2.3 State machine implementation

#### State machine implementation 1 and overall behavior

The set state procedure consists of balsa case-statements similar to verilog case-statements. The states themselves are also like the verilog cases used in the synchronous startup logic, modeling the same behavior for all the states, except the INC states and RESET state. In addition there is a final state, DONE, where the stop variable is set to halt the main loop, stopping the circuit. To illustrate, the code of the first two states is given below.

Listing 5.1: First two states

```

1

case state_r of

2

MON ON then

3

mon1 enable <-1

4

mon2 enable \leftarrow 1

5

select mon1 ready then

6

continue

7

end ||

8

select mon2 ready then

9

continue

10

end;

nextstate := MON\_SELECT

11

12

13

MON SELECT then

14

vok1 \rightarrow vok1_t \mid

15

vok2 \rightarrow vok2_t;

16

if vok2 t = 1 then

17

nextstate := REF2 ON

vok1_t = 1 then

18

19

nextstate := REF1_ON

20

21

nextstate := MON\_SELECT

22

end

```

As with the synchronous implementation the analog cells are enabled and the ready and vok signals from the cells are then used to determine the next state. The big difference here is the  $MON\_ON$  state where the state machine doesn't loop in the state, checking the input signals every iteration, instead the circuit waits for both the ready signals before moving on to the next state. The  $MON\_SELECT$  state loops like in the synchronous implementation, Pulling the vok signal from the interface to the analog cells every iteration.

Like the  $MON\_ON$  stage, the  $REF1\_ON$  and  $REF2\_ON$  stages enable their corresponding voltage reference and wait for a ready response. When the ready signal arrives the next state is set to  $VREG1\_ON$  or  $VREG2\_ON$  depending on current state. In the VREG states voltage monitor 3 is turned on, as well as the voltage regulator associated with the state and the initial binary selvdd value of 000 is sent to the voltage regulator. When the ready signals from both the voltage monitor and the enabled voltage regulator arrives, the state machine PULLs the vok value from voltage monitor 3. After that then next state is set to INC and the current state is saved in a variable called prevstate. The prevstate variable is used in the INC state.

The *INC* state models controls the output, *VDDCORE*, by incrementing the *selvdd* value to the voltage regulator until the voltage is over a given threshold. In the *INC* state first test the vok3\_t variable which is used to store the *vok* value PULLed from the voltage monitor monitoring *VDDCORE*. If the *vok* value stored in the variable is a logic 1 the state machine sets the *nextstate* variable to *DONE*, but if it is 0 the *selvdd* value sent to the voltage regulator is incremented. This is done by incrementing a count variable and PUSHing this value over the *selvdd* channel. The state then waits for a *ready* signal from the voltage regulator specified by the *prevstate* variable. Last the *vok* value is pulled and this value is tested in the next iteration of the main loop. The state machine stays in this state until the pulled *vok* value is 1.

While the INC2 state is used to give vok3 time to properly update, a sync channel has been added in the vok-loop for the asynchronous implementations. The sync channel initiates a handshake with an external delay cell. When a suitable time has passed the delay cell acknowledges the handshake and the vok-loop continues.

The additional DONE state is as mentioned used to stop the circuit. It does this by setting the stop variable controlling the main loop. The main loop is shown in the code below.

Listing 5.2: Main loop

```

begin

state_r := MON_ON;

loop while stop = 0 then

setstate();

state_r := nextstate

end

end

end

```

The final difference to the synchronous version is the lack of a RESET state. The balsa-generated circuit has an  $activate\_r$  input used to start the circuit, which is connected to the power-on-reset signal. When this input is high the circuit is active, while it is automatically resets when it goes low.

#### State machine implementation 2

An alternative to the MON\_SELECT state was also made to prevent the startup logic from looping while it waits for one or more of the the pulled vok signals to be high. This state waits for a response to be sent instead of pulling it directly. As there is a chance of both signals arriving at the same time the startup logic has to arbitrate between them. If a variable called vokmutex is zero a value is written to it depending on which signal is chosen by the arbitration. If the variable already has been written to nothing happens and the state continues with the next part of its behavior. The next part is a check on the vokmutex variable to see which signal was arbitrated and using this to set the next state. The code for the state is shown in the code below.

Listing 5.3: MON SELECT state from state machine implementation 2

```

MON SELECT then

2

arbitrate vok2 then

3

if vokmutex = 0 then

vokmutex := 2

4

6

vok1 then

7

if vokmutex = 0 then

8

vokmutex := 1

9

end

10

end:

11

if vokmutex = 1 then

12

nextstate := REF1 ON

13

vokmutex = 2 then

14

nextstate := REF2 ON

15

end

```

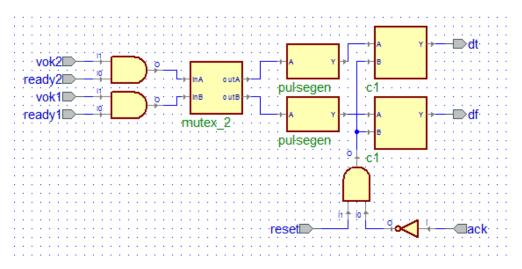

#### State machine implementation 3

According to [12] the arbitration circuit generated by balsa leads to a significant increase in area. To prevent this increase in area another implementation

was made. Instead of doing the arbitration in the startup logic this implementation will passively wait for a data signal from the interface with the arbitrated result. The interface is described in 5.3.5. In this implementation there is only one channel for the vok signal from the voltage monitors. The state waits for a handshake on the vok channel and the data sent is used to determine the next state. The code for the state is shown in listing 5.4

Listing 5.4: MON\_SELECT state from state machine implementation 3

```

MON SELECT then

1

2

vok -> then

3

case vok of

4

1 then

5

nextstate := REF2_ON

6

7

nextstate := REF1_ON

8

end

end

```

## 5.2.4 Optimized implementation

#### Optimized implementation 1 and overall behavior

This implementation takes advantage of the fact that sequential circuit behavior can easily be modeled in balsa. A lot of the code in the state machine is enabling an analog cell, and then waiting for one and more signals from the cell. This is easy to model in balsa and it isn't really necessary to use a state machine to control this behavior. The parts of the code where data values are pulled from the analog cells are a bit more complicated to model. Here a while loop is required to substitute the state machine looping in a particular state. The code in listing 5.5 models the same behavior as the  $MON\_ON$  state and part of the  $MON\_SELECT$  state in subsection 5.2.3.

Listing 5.5: code for beginning of optimized implementation 1

```

mon1\_enable <- 1

1

2

mon2 enable <-1

3

select mon1_ready then

4

continue

5

\operatorname{end}

6

select mon2 ready then

7

continue

8

end ;

9

loop while (vok1 \ t \ or \ vok2 \ t) = 0 \ then

10

vok1 \rightarrow vok1 t

11

vok2 \rightarrow vok2_t

12

end;

```

The part of the code before the while loop is exactly like the  $MON\_ON$  state, but instead of setting the nextstate variable for use in the next iteration of the state machine a single sequential operator is used to indicate that the while loop is executed afterwards. The loop PULLs the vok signal from voltage monitor 1 and 2 in each iteration and stores them in the variables  $vok1\_t$  and  $vok2\_t$ . When one or both of the variables are 1 the loop exits and the startup logic moves on to the code shown in listing 5.6.

Listing 5.6: code for selecting a voltage reference

```

if vok2 t = 1 then

1

2

ref2 enable <- 1

3

select ref2_ready then

continue

4

5

end;

6

vreg2\_enable <- 1

7

vok1 t = 1 then

8

ref1 enable <- 1 ||

9

select refl ready then

10

continue

11

end:

12

vreg1_enable <- 1

13

end;

```

This part of the code handles the selection of which of the voltage references and voltage regulators are to be turned on. Depending on the  $vok1\_t$  and  $vok2\_t$  variables either voltage reference 1 is turned on or voltage reference 2 is turned on. When the voltage reference that is turned on signals that it is ready the corresponding voltage regulator is turned on. After this voltage monitor 3 is turned turned on, while the other two voltage monitors are turned off. When voltage monitor 3 signals that it is ready the startup logic

begins the incrementation part of its behavior. This is shown in listing 5.7.

Listing 5.7: incrementation loop for optimized implementation

```

loop while vok3 t = 0 then

1

2

inc();

3

selvdd <- count ;

4

if vok2 t = 1 then

5

select vreg2 ready then

6

inc()

7

end

8

| vok1_t = 1 then

9

select vreg1_ready then

10

inc()

11

end

12

end ;

13

--sync delay ;

vok3 \rightarrow vok3_t;

14

15

end

```

Like in the state machine implementation the while-loop controlling the incrementation loops as long as the value pulled from voltage monitor 3 isn't a logic 1. First a counter is incremented and the value is sent over the *selvdd* channel to the interface. The inc-procedure used to increment a counter is shown in listing 5.8. Then an if-sentence checks whether to wait for a ready signal from voltage regulator 1 or 2. When the ready signal arrives the vok3 signal is PULLed from voltage monitor 3.

Listing 5.8: procedure for incrementation

```

shared inc is

begin

if count < 7 then

count := (count +1 as 3 bits)

end

end

```

The inc procedure is used to increment a counter used to assign the next selvdd value. The procedure has a if-guard to ensure that the counter doesn't increment when the current count value is a binary 111, so that the counter doesn't over wrap and get a new binary value of 000. When the incrementation is done the next selvdd value is sent to the voltage regulator. When the loop finishes the startup logic is done and sets its activate acknowledge output high. As long as the activate request input doesn't go low the startup logic stays static.

#### Optimized implementation 2

The optimized implementation 2 uses the same interfaces and solution as the second state machine implementation, for the same reason. Arbitration with a *vokmutex* variable is used, but instead of setting the next state, it enables the selected voltage reference. When the voltage reference signals that it is ready the corresponding voltage regulator is turned on. This code substitutes the code in listing 5.6 and the vok-loop in listing 5.5 from optimized implementation 1, but the rest of the code is the same. The changed code for this implementation is showed in listing 5.9.

Listing 5.9: Code changed in optimized implementation 2

```

1

arbitrate vok2 then

2

if vokmutex = 0 then

3

vokmutex := 2

4

5

vok1 then

6

if vokmutex = 0 then

7

vokmutex := 1

8

9

end;

10

if vokmutex = 1 then

11

ref1 enable <- 1 ||

12

select refl ready then

13

continue

14

end ;

15

vreg1\_enable <- 1

16

vokmutex = 2 then

ref2\_enable \leftarrow 1 \mid \mid

17

18

select ref2_ready then

19

continue

20

end ;

21

vreg2_enable <- 1

22

end;

```

#### Optimized implementation 3

This implementation is the optimized equivalent of state machine implementation 3. Compared to the code in optimized implementation 1 it only substitutes the vok-loop in listing 5.5, leaving the rest of the code unchanged. The changed code for this implementation is showed in listing 5.10. In state implementation 3 the next tate variable is set within the case-statement, but

in this implementation the one of the temporary variables  $vok1\_t$  or  $vok2\_t$  is set to one. The temporary vok variables are used to select which voltage reference is turned on in listing 5.6, like in optimized implementation 1.

Listing 5.10: Code changed in optimized implementation 3