# A sub-1µW, 16kHz Current-Mode SAR-ADC for Neural Spike Recording

Bård Haaheim

Master of Science in ElectronicsSubmission date: August 2011Supervisor:Trond Ytterdal, IETCo-supervisor:Timothy Constandinou, Imperial College

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## Problem description

The candidate is to develop a ultra-low-power analogue-to-digital converter (ADC) for single channel neuron spike recording using a commercially-available  $0.18\mu m$  CMOS technology. A key requirement is that the circuit occupies a compact silicon area to allow for scalability within an array. Specifically, it is envisaged that the analogue front-end will be confined to the footprint of a neural probe, which must be scalable up to 100's of channels.

For this project, the candidate must become familiar with the field of neurotechnology and specifically regarding neuron spike recording. A good understanding to the dynamics of neural signals, and challenges brought on by the electrode-electrolyte interface would give good insight into defining the ADC specifications and in revealing potential improvements.

Both the choice of topology and implementation are left to the candidate, although it is required to be Nyquist-rate to allow for an asynchronous system architecture. A successful outcome would have a performance comparable to the state-of-the-art with the design tolerant to process variation to achieve a  $3\sigma$  production yield. A full-custom layout will be submitted for fabrication in the target technology.

## Preface

In Autumn 2010 I was invited to work at Imperial College under Dr. Timothy Constandinou as a part of a research team aiming to develop an ultra low power implantable platform for the next generation neural interfaces. Recent advances in technology combined with a ground breaking concept for neural spike sorting on-chip was the foundation of this project motivated by the need of providing easy to use neuralgic tools paving the way for new treatments of conditions currently suffering from extensive clinical burdens. The project, spanning over several years, was in an initial phase emphasizing experimental design and creative thinking my participation concerned and has therefore dynamically changed while it has progressed. My work omitted the front-end analogue to digital converter started as the project of course TFE4540 at NTNU. For convenience, the main content of this project has been incorporated into this paper [22].

## Acknowledgements

I would like to direct my sincere thanks to Dr. Timothy Constandinou for all the encouragement and useful guidance through the project, but also for enabling this cooperation between colleges and letting me take part in his research team. Further I would like to thank the neural team consisting of Dr. Amir Eftekhar, Song Luan, Sivylla Paraskevopoulou and Ian Williams for the feedback, ideas and moral support. A special thanks goes to Song Luan for his many helps and discussions.

Also, I would like to thank my professor and advisor at NTNU, Trond Ytterdal for all guidance and past-on wisdom, but also for being extremely helpful and flexible, using his network to provide me a project abroad.

Last, but not least, I would like to thank my office sharers at NTNU, Daniel Aasbø, Torbjørn Løvseth Finnøy, Carolina Fiorella Inche Velezmoro, Kjetil Kvalø and Marius Lind Volstad for fun times, good discussions and moral support over the last years.

## Abstract

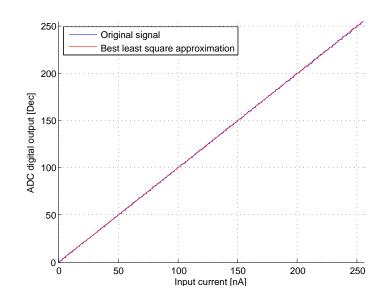

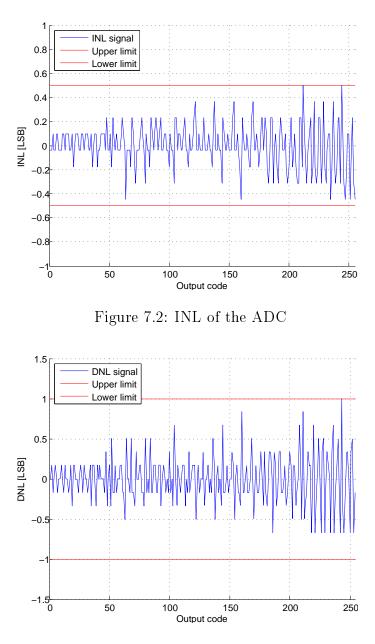

This thesis presents an ultra-low-power 8-bit asynchronous current-mode successive approximation (SAR) ADC for single channel neuron spike recording. The novel design exploits current mode operating in weak inversion for high power efficiency and is design to operate at a 1.8V supply. The ADC is running at a 16kHz sampling frequency using under  $1\mu W$  of power, though is adjustable using the featured calibration registers. A finished layout is presented, occupying less than  $0.078mm^2$ . Linear operation through mismatch and process variations is obtained using a current calibration circuit connected to both the current mode DAC and all the biases. This ensures  $INL < \pm 0.5$  and  $DNL < \pm 1$ , yielding no missing codes and a  $3\sigma$  production yield. Calibration is needed because of the relatively large mismatch caused by sub-threshold operation of the current mirrors. The design also offers a newly developed current comparator with high resolution and fast settling relative to the current level and is completable with other state-of-the-art solutions, though still feature some voltage scaling issues left for future work.

# Contents

| $\mathbf{A}$ | bstra           | ct VII                                    |

|--------------|-----------------|-------------------------------------------|

| Co           | onter           | Ats XI                                    |

| Li           | st of           | Figures XIV                               |

| Li           | st of           | TablesXV                                  |

| A            | crony           | Yms XVII                                  |

| 1            | $\mathbf{Intr}$ | oduction 1                                |

| <b>2</b>     | Neu             | ral Science and ADC requirements 3        |

|              | 2.1             | Neuron Signals                            |

|              | 2.2             | The next generation neuron interfaces     |

|              | 2.3             | Limitations                               |

|              | 2.4             | This project                              |

|              | 2.5             | ADC requirements                          |

| 3            | Bac             | kground 9                                 |

|              | 3.1             | Topology                                  |

|              | 3.2             | Current Mirror                            |

|              |                 | 3.2.1 Topologies                          |

|              |                 | 3.2.2 Noise                               |

|              |                 | 3.2.3 Frequency response                  |

|              |                 | 3.2.4 Mismatch                            |

|              |                 | 3.2.5 Absolute Accuracy and dynamic range |

|              | 3.3             | Converter Performance Characteristics     |

|              | 3.4             | Current Comparator                        |

|              |                 | 3.4.1 Implementations                     |

|              | 3.5             | Current Mode DAC                          |

|              |                 | 3.5.1 Performance Limitations             |

| 4            | Design and Methods 2                                                                                                           | 5          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|------------|

|              | 4.1 Estimations $\ldots \ldots 2$                 | 25         |

|              | 4.2 Current Mirror                                                                                                             | 26         |

|              | 4.3 Current Mode DAC                                                                                                           | 26         |

|              | 4.4 Current Comparator                                                                                                         | 29         |

|              | 4.5 Calibration $\ldots \ldots 2$                        | 29         |

|              | 4.6 Logic                                                                                                                      | 80         |

| <b>5</b>     | Implementation 3                                                                                                               | 1          |

|              | 5.1 Control Logic                                                                                                              | 31         |

|              | 5.2 Current Comparator                                                                                                         | 34         |

|              | 5.3 Current-Mode DAC                                                                                                           | 86         |

|              | 5.4 Calibration Module                                                                                                         | 87         |

|              | 5.5 Calibration register                                                                                                       | 39         |

|              | 5.6 Input current mirror                                                                                                       | 10         |

| 6            | Layout 4                                                                                                                       | 3          |

| 7            | Results 4                                                                                                                      | 7          |

|              | 7.1 ADC Core                                                                                                                   | 17         |

|              |                                                                                                                                | <u>1</u> 9 |

|              | 0                                                                                                                              | 50         |

|              |                                                                                                                                | 53         |

|              |                                                                                                                                | 53         |

|              | -                                                                                                                              | 54         |

| 8            | Analysis and Discussion 5                                                                                                      | 7          |

|              | 8.1 Topology                                                                                                                   | 58         |

|              | 8.2 Architecture                                                                                                               | 58         |

|              | 8.2.1 Current mode DAC                                                                                                         | 58         |

|              | 8.2.2 Current Comparator                                                                                                       | 59         |

|              |                                                                                                                                | 60         |

|              | 8.2.4 Calibration $\ldots \ldots 6$ | <b>51</b>  |

|              | 8.2.5 Calibration Register                                                                                                     | <b>52</b>  |

|              | 8.3 ADC core                                                                                                                   | <b>52</b>  |

|              | 8.4 Future Works                                                                                                               | 53         |

| 9            | Conclusions 6                                                                                                                  | 5          |

| $\mathbf{A}$ | Derivations 7                                                                                                                  | 3          |

|              |                                                                                                                                | 73         |

| В            | Oce            | n Scripts 75                                                                                                             |

|--------------|----------------|--------------------------------------------------------------------------------------------------------------------------|

|              | Β.1            | Current Mirror                                                                                                           |

|              | B.2            | ADC Core                                                                                                                 |

|              | B.3            | Calibration Register                                                                                                     |

|              | B.4            | $iDAC \dots \dots$ |

| $\mathbf{C}$ | Mat            | ab Code 83                                                                                                               |

|              | C.1            | iDAC                                                                                                                     |

|              | C.2            | ADC Core                                                                                                                 |

|              | C.3            | iComp input impedance                                                                                                    |

| D            | $\mathbf{Pin}$ | overview 87                                                                                                              |

| $\mathbf{E}$ | Mea            | surements 89                                                                                                             |

|              | E.1            | Current Mirror                                                                                                           |

|              |                | E.1.1 DR                                                                                                                 |

|              |                | Е.1.2 АС                                                                                                                 |

|              |                |                                                                                                                          |

|              |                | E.1.3 Noise                                                                                                              |

|              |                | E.1.3 Noise                                                                                                              |

# List of Figures

| 2.1  | Neural recording from a cat motor cortex using Utah Electrode                                                                                            |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Array and CMOS amplifier.                                                                                                                                | 4  |

| 2.2  | The 100-electrode silicon-based Utah Electrode array measur-                                                                                             | ۲  |

|      | $ \inf_{a} 4 \times 4 \times 1.5 mm^3 \dots \dots$ | 5  |

| 2.3  | System overview                                                                                                                                          | 7  |

| 3.1  | Comparison of recent published ADCs in performance of interest                                                                                           | 10 |

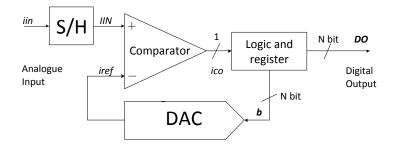

| 3.2  | General SAR ADC system overview.                                                                                                                         | 11 |

| 3.3  | SCM with compensation resistor for bandwidth enhancement .                                                                                               | 13 |

| 3.4  | Principle of current comparison                                                                                                                          | 18 |

| 3.5  | Multilevel input impedance current comparator                                                                                                            | 20 |

| 3.6  | Common implementation of a current mode DAC                                                                                                              | 22 |

| 3.7  | Current splitting technique I                                                                                                                            | 23 |

| 3.8  | Current splitting technique II                                                                                                                           | 23 |

| 4.1  | SCM Mismatch - 3D model                                                                                                                                  | 27 |

| 4.2  | SCM Mismatch - Side projection in log-scale $\hdots$                                                                                                     | 28 |

| 5.1  | System level design for the current mode SAR ADC                                                                                                         | 32 |

| 5.2  | Digital circuit used to realize the SAR algorithm and output                                                                                             |    |

|      |                                                                                                                                                          | 33 |

| 5.3  |                                                                                                                                                          | 34 |

| 5.4  |                                                                                                                                                          | 35 |

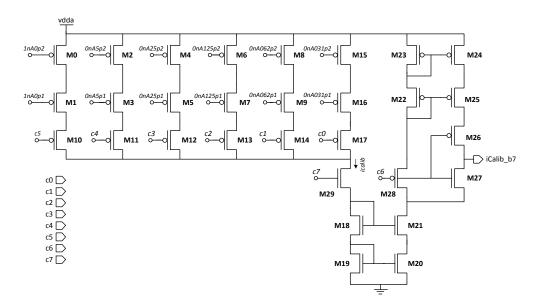

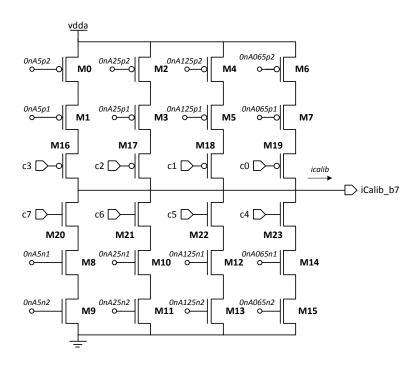

| 5.5  | -                                                                                                                                                        | 36 |

| 5.6  |                                                                                                                                                          | 37 |

| 5.7  |                                                                                                                                                          | 38 |

| 5.8  |                                                                                                                                                          | 38 |

| 5.9  | Calibration circuit for bit 2-6, though all with different bias-                                                                                         |    |

|      |                                                                                                                                                          | 39 |

| 5.10 | calibration register                                                                                                                                     | 40 |

| 5.11 | Current input/output stage                                                                                                                               | 41 |

|      | . – –                                                                                                                                                    |    |

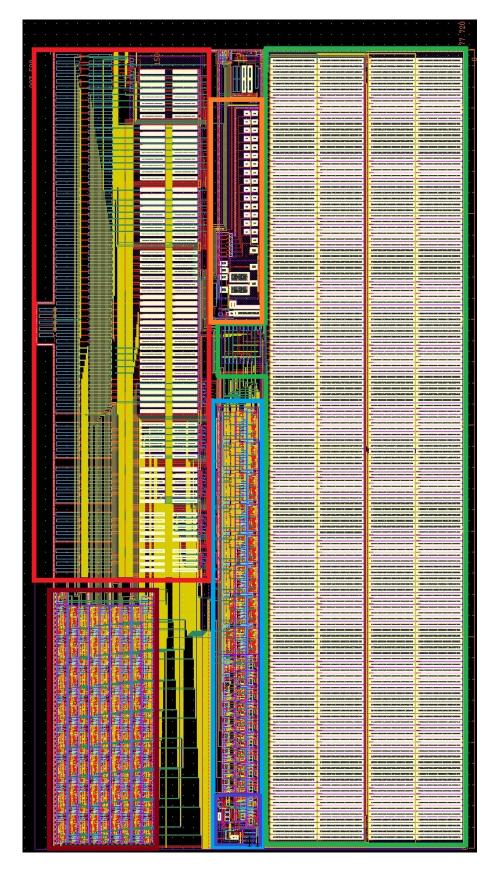

| 6.1            | Final Layout                                                | 44 |

|----------------|-------------------------------------------------------------|----|

| 7.1            | Input/output characteristics of the ADC                     | 48 |

| 7.2            | INL of the ADC                                              | 49 |

| 7.3            | DNL of the ADC                                              | 49 |

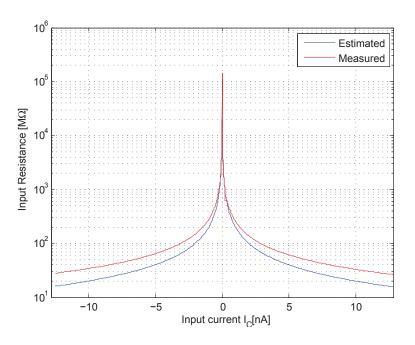

| 7.4            | Input impedance of the current comparator                   | 55 |

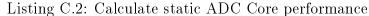

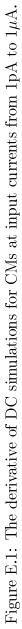

| $\mathrm{E.1}$ | The derivative of DC simulations for CMs at input currents  |    |

|                | from 1pA to $1\mu$ A                                        | 91 |

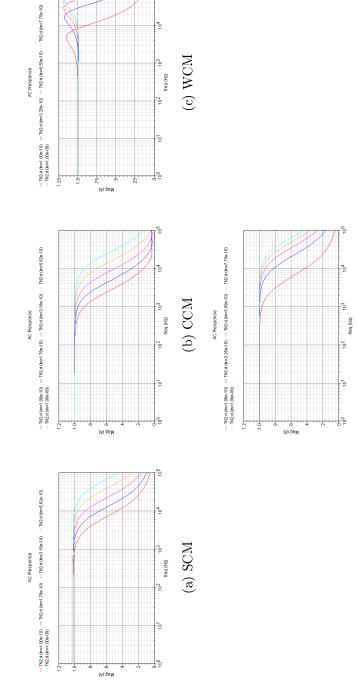

| E.2            | AC simulations of CMs for currents in range of 0.1nA to 1nA | 92 |

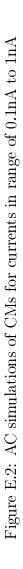

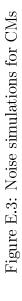

| E.3            | Noise simulations for CMs                                   | 93 |

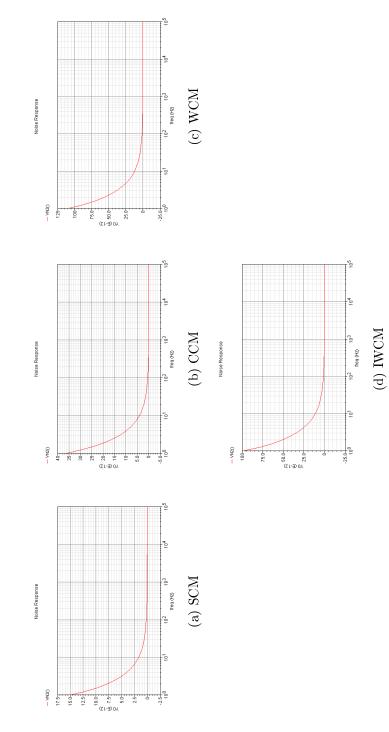

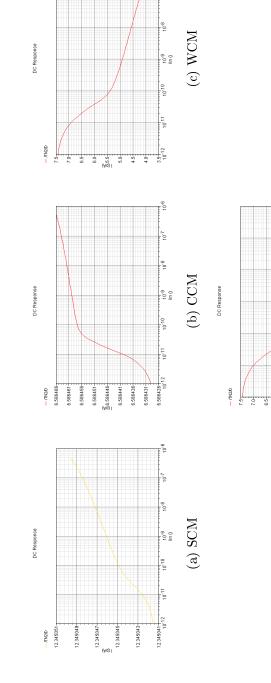

| E.4            | Leakage simulations of MCs                                  | 94 |

# List of Tables

| 2.1                                                                   | ADC system requirements                                                         | 8                                                          |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------|

| 3.1                                                                   | Output resistance of the four most common current mirrors                       | 16                                                         |

| 5.1                                                                   | Register overview                                                               | 40                                                         |

| 6.1                                                                   | Layout explanation                                                              | 45                                                         |

| $7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 7.7 \\ 7.8 \\ 7.9 \\ 7.10$ | Power Consumption                                                               | $50 \\ 50 \\ 51 \\ 52 \\ 53 \\ 54 \\ 54 \\ 54 \\ 54 \\ 55$ |

| 8.1                                                                   | Comparison of low power ADCs                                                    | 57                                                         |

| A.1                                                                   | Assigned error to each iDAC branch                                              | 73                                                         |

| D.1                                                                   | ADC pin overview                                                                | 88                                                         |

| E.1                                                                   | Summary of simulation results of the different topologies at scaling 1:1 at MSB | 95                                                         |

# Acronyms

| ADC    | analogue-to-digital converter                       |

|--------|-----------------------------------------------------|

| ССМ    | cascoded current mirror                             |

| CMOS   | complementary metal-oxide-semiconductor             |

| DAC    | digital-to-analogue converter                       |

| DNL    | differential nonlinearity                           |

| DR     | dynamic range                                       |

| DSP    | digital signal processor                            |

| ENOB   | effective number of bits                            |

| EEPROM | Electrically erasable programmable read-only memory |

| FOM    | figure of merit                                     |

| INL    | integral nonlinearity                               |

| IWCM   | Improved Wilson current mirror                      |

| KCL    | Kirchhoff's current law                             |

| LNA    | low noise amplifier                                 |

| LPF    | local field potential                               |

| MOSFET | metal-oxide-semiconductor field-effect transistor   |

| OPAMP  | Operational amplifier                               |

| ΟΤΑ    | operational transconductance amplifier              |

| PGA    | programmable gain amplifier                         |

- **PTAT** proportional to absolute temperature

- **SNR** signal-to-noise ratio

- **SAR** successive approximation

- **SCM** simple current mirror

- **TDA** threshold detecting amplifier

- **WCM** Wilson current mirror

## Chapter 1

## Introduction

With ever-advancing trends in microelectronics, researchers are now innovating analytical tools for the in-vivo measurements of neuron activity. They are developing next generation neural interfaces for totally-implantable devices that use bio-telemetries for the transmission of both power and data. Such links require digitised signals for efficient and reliable data transmission therefore introducing the need for on-chip analogue-to-digital converters (ADCs). Traditionally, such systems use single, multiplexed ADCs that are timeshared [7, 24, 41], whereas this thesis offers single-channel implementations allowing for an efficient and easily-scalable system. These solutions are also commonly using charge redistribution voltage-mode successive approximation (SAR) ADCs despite current mode converters are now demonstrating excellent characteristics and in particular, high resource efficiency (power and area) [1, 2, 17]. This thesis presents an ultra low power 8-bit asynchronous current-mode SAR ADC implemented in a commercially-available  $0.18 \mu m$ CMOS technology intended for neural spike recording. Exploiting current mode, the requirement of small area is ensured featuring 16kHz sampling frequency.

The paper is organized as follows: Chapter 2 explains the challenges and the nature of neural signal recording together with the conceptual technique of on-chip neural spike sorting. Chapter 3 covers the theory behind applied techniques and design, while chapter 4 describes the design process. Chapter 5 describes the final implementation while chapter 6 briefly presents the final layout. Chapter 7 presents all simulated data and obtained results, while chapter 8 makes an analysis and discussion of the project. Chapter 9 concludes the report, summarizing the whole project.

## Chapter 2

# Neural Science and ADC requirements

Neural spike recording is not a new scientific area, but has existed over half a century. Already conducted experiments yield profound insights into brain function and how this complex system is affected by neurological injuries and diseases while recent years research have brought systems like Deep Brain Stimulator and Cochlear Implants helping thousands of patients worldwide [37, 45]. However, despite considerable advances in electrode technologies, the ability to interface digital microelectronics with the brain at the level of individual neurons is at present severely limited. To be able to mimic complex brain functions like moving limbs or preventing seizures, individual neuron recording and stimulation in numbers of hundreds are required. This aims to make new therapeutic avenues available to neurologists battling until now untreatable conditions among Huntington's, Parkinson's and Alzheimer's disease, spinal cord injuries and epilepsy to name a few. To better understand the design challenges regarding neuron spike recording a brief presentation of signal characteristics and recording methods will be explained in the following.

### 2.1 Neuron Signals

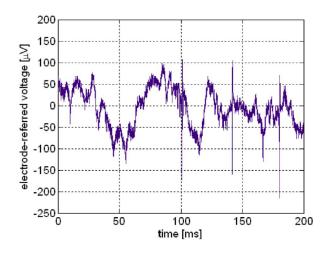

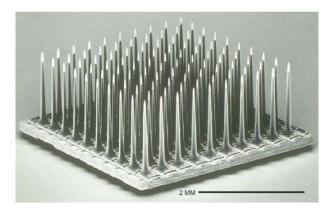

The analogue voltage potential of a neuron exhibits larger fluctuations whenever the neuron fires a signal. This manifests as a voltage pulse usually in range of  $50-200\mu V$  over a  $1-5\mu s$  period of time. Each neuron has its own signature within the 300Hz - 5kHz signal range, though the noisy background makes them hard to distinguish. A typical signal is shown in figure 2.1 and is showing three spikes at  $\sim 100\mu s$ ,  $\sim 140\mu s$  and  $\sim 180\mu s$  respectively [25]. Because the neurons are in close proximity of each other surrounded in dielectric material, the DC potential is correlated to the global brain activity resulting in unpredictable variations in frequencies below 300Hz, also known as local field potentials (LPFs). This can also be seen in the figure. Figure 2.2 on the next page is showing the recording probe array. The LPFs are easily detected by commercially available technologies and contain information of general activity in regions of the brain. Understanding and interacting with the neuron spikes on the other hand, though unclear, scientists widely believe that it will give access to complete control of the body, though still severely limited due to its complexity [19].

At the present, arrays of electronic probes inserted into the brain tissue have no guaranty to the proximity to the actual neurons, making single probes (referred to as a channel,) picking up signals from several neurons. The average is  $3.4 \pm 1.5$  per channel. This severely increases the complexity of systems intended for neuron spike detection as a single probe needs to be able to distinguish several neurons from each other to detect activity. The interval of which a neuron fires is also changing. While the average is around 50Hz, burst up at 300Hz are possible.

Figure 2.1: Neural recording from a cat motor cortex using Utah Electrode Array and CMOS amplifier.

Figure 2.2: The 100-electrode silicon-based Utah Electrode array measuring  $4 \times 4 \times 1.5 mm^3$

### 2.2 The next generation neuron interfaces

Several wired solutions for multi-channel recording and stimulation systems have been created in the past. However, the wiring limits movement, increases the risk of infections and severe complications in addition to increase tissue regeneration changing the characteristics. In all, due to the sever exposure of the system, supervision is required at all times in addition to limited and often corrupted data because of external factors interfering with the sensitive nodes. The key factor for the next generation neuron interfaces is therefore wireless telemetry for both power and signal transfer to totally isolate the system. The required number of channels are unknown, though in-vivo measurements have shown that tens to hundreds are required to monitor simple body functions like moving a limb. For future research, it is therefore important not to restrict the data acquiring, but to enable an as broad spectre as possible leaving the requirement of a highly scalable channel count. Later projects have encountered these challenges [7, 24, 41] while in-vivo measurements still have yet to be conducted, most projects in their early stages.

### 2.3 Limitations

The key challenges for the system implementation are power and area. Preliminary studies have shown that approximately 10mW of power can safely be dissipated using a system measuring  $6 \times 6 \times 2mm^3$  attached to the Utah array [25]. The main issue arising with limited power is the available bandwidth of the wireless link as the intended high channel count leads to raw data generation far higher than possible transmission rates. There exist several techniques for data reduction which exploit compression, signal redundancy and/or level of abstraction [19] though the next generation systems will need to provide high quality signals containing information about which neuron fired at a given time. The process to determine this information is complex and requires high computational force previously performed by powerful external computers.

Concerning area, the whole front-end is restricted to within the boundaries of the probing array. This will both ensure that multiple systems can be put in close proximity to each other while also minimizing invasion and unwanted side effects of electrical signals and heat in other parts of the brain. For the Utah array, 100 channels should be fitted within the  $16mm^2$  area. Other things to consider are tissue regeneration at the probes causing probe characteristics to change over time, leading to continuous calibration requirements.

#### 2.4 This project

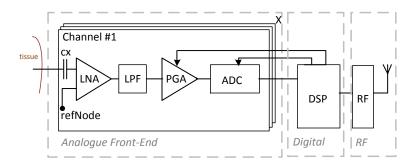

The strength of this project is the use of a digital spike sorting technique to digitize the spike events. This will reduce the requirements on the wireless link while providing high quality data and for the future support on-chip response to the brain activity, stimulating the nerves back to prevent seizures or similar if necessary. A simplified overview of the system is shown in figure 2.3 on the facing page. The capacitor  $C_x$  together with the inherent frequency response of the low noise amplifier (LNA) high-pass filters the input removing the unwanted frequency range from DC to 300Hz. The LNA is of band-pass type implementing together with the low-pass filter(LP) also a 5kHz cut-off frequency before amplified by programmable gain amplifier (PGA) adjusting the signal level to the dynamic range (DR) of the ADC. The output of each channel is input into a rolling buffer in the digital signal processor (DSP) using template matching to find spike events. The events are transmitted over the wireless link coded with the channel number and a time-stamp. The templates are created in a calibration period using a high resolution high sampling frequency ADC which data are sent to an external computer for processing. The generated templates are later uploaded to the system. When the system is running in normal mode, the deviation of matches to the

templates are determining if a new calibration if required. However, tissue regeneration is only expected to require daily or weekly adjustments.

Figure 2.3: System overview

### 2.5 ADC requirements

For this system to work, internal preliminary simulations have shown that the analogue signals need to be digitized at 16kSamples/s using 8-bit resolution for the DSP's algorithms to work with satisfactorily numbers of falsenegatives and false-positives. The power consumption is restricted to  $2\mu W$ though less should be striven as to enable more computational power and options in other parts of the system. The area should be less than  $0.1mm^2$ to accommodate 100 channels within the boundaries of the Utah array including the reset of the front-end and the input DR should be  $0.9 \pm 0.5V$ , the specifications derived in compliance with the neural team. However, the PGA's output can also be a current, removing the last output stage making it a  $g_m$ -source. The sample and hold will be done in voltage-mode after amplification. Table 2.1 on the next page summarizes the requirements.

| Table 2.1. ADO system requirements   |              |      |           |       |                      |

|--------------------------------------|--------------|------|-----------|-------|----------------------|

| PARAMETERS                           | CONDITIONS   | MIN  | TYP       | MAX   | UNIT                 |

| Power Supply                         |              |      |           |       |                      |

| Supply Voltage                       |              | 1.75 | 1.8       | 1.85  | V                    |

| Power                                |              |      |           | 2     | $\mu W$              |

| Area                                 |              |      |           |       |                      |

| Analogue front-end                   | per channel  |      |           | 0.175 | $mm^2$               |

| ADC estimate                         | per channel  |      |           | 0.1   | $mm^2$               |

| Accuracy                             |              |      |           |       |                      |

| Resolution                           |              |      | 8         |       | $\operatorname{bit}$ |

| INL                                  |              |      | $\pm 0.5$ |       | LSB                  |

| DNL                                  |              |      | $\pm 1$   |       | LSB                  |

| Offset                               |              |      | $\pm 0.5$ |       | LSB                  |

| Timing                               |              |      |           |       |                      |

| Sampling Frequency                   |              |      | 16.384    |       | kHz                  |

| Conversion Time                      |              |      |           | 60    | $\mu s$              |

| Input/Output                         |              |      |           |       |                      |

| Input Range                          | Voltage Mode | 0.4  |           | 1.4   | V                    |

|                                      | Current Mode |      | Optiona   | ]†    | Ι                    |

| Output                               | Parallel     |      | 8         |       | bit                  |

| Other                                |              |      |           |       |                      |

| ${\rm Temperature}^{\dagger\dagger}$ |              | 20   | 37        | 42    | $C^{\circ}$          |

Table 2.1: ADC system requirements

<sup>†</sup> The output of the  $g_m$ -source will be designed after the ADC-requirements

$^{\dagger\dagger}$  Includes testing environment for convenience. The actual requirement is  $37\pm5^\circ C$

## Chapter 3

## Background

In this chapter, theory and background material needed to understand this thesis will be explained. However, some basic theory will be assumed known to the reader and of such refers to general books of analogue design and ADCs [12, 26].

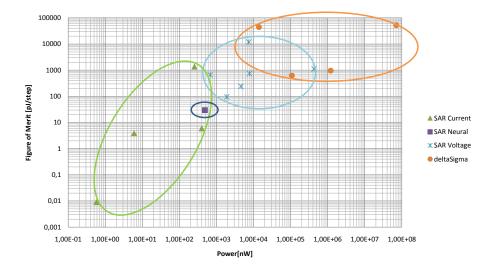

### 3.1 Topology

From previous work [22], the topology was chosen to be a current-mode SAR ADC. The choice was based on figure 3.1 on the following page showing a figure of merit (FOM) versus power plot for recent<sup>1</sup> IEEE publications [1, 2, 8, 9, 16, 17, 20, 27, 29, 32, 35, 36, 38, 42, 44] in addition to be supported by several published papers [17, 40]. The FOM is given by equation 3.1 on the next page, normalized by the term in the parenthesis for technology interdependency. The presented ADCs have resolutions around 8-bits and relatively low sampling frequencies as this is the performance of interest. The figure indicates that current mode SAR ADCs at the moment have the best performance for the given specifications. They are also small compared to their voltage mode counter parts using large capacitors for accurate matching, thus suitable for single channel implementation. For further argumentation

$<sup>^1\</sup>mathrm{As}$  of October 2010

Figure 3.1: Comparison of recent published ADCs in performance of interest

of selected topology it is referred to the term paper.

$$FOM = \frac{Power}{2^{ENOB} \cdot Fs} \cdot \left(\frac{\gamma \cdot Area}{Technology^2}\right)$$

(3.1)

The main components within a current mode SAR ADC shown in figure 3.2 on the facing page are a current comparator, a sample and hold module, a current mode digital-to-analogue converter (DAC) and some logic. The topology is based on the same fundamentals as its commonly known voltagemode counterpart (e.g. charge redistributed SAR ADC), though this only needs MOSFET devices in its implementation. This introduces the potential of: (1) reduce the area requirements, (2) reduce power consumption and (3)achieve high speed operation. The digital output is acquired by comparing the input current to a reference current in sequence, for each bit in the selected resolution, adding up to N-cycles per conversion(i.e. a binary search). The reference current is generated by a current mode DAC controlled by the digital logic and is calculated according to equation 3.2. Here,  $I_{bias}$  controls the input DR, which makes the power consumption of the DAC module directly proportional to the signal level and thus favourable for low energy signals. The current comparison feeds back to the logic which adjusts the reference current.

$$I_{DAC} = (b_n \cdot 2^n + b_{n-1} \cdot 2^{n-1} + \dots + b_1 \cdot 2 + b_0) \cdot I_{bias}$$

(3.2)

Figure 3.2: General SAR ADC system overview.

In the following, the different parts needed in an implementation of a current mode SAR ADC will be explained, starting with the current mirror as it is a fundamental building block. A note concerning all the analogue circuit parts is that the low overall power consumption results in a nano-ampere current range, yielding weak inversion operation for most devices.

### 3.2 Current Mirror

The main performance limitations of a current mirror are frequency response, absolute accuracy, noise, mismatch and DR which all are dependent on the topology, transistor size and current level. All will be explained in the following.

#### 3.2.1 Topologies

There exist many topologies for current mirrors though for low power applications, four are most common selected due to accuracy, simplicity, lowvoltage operation and widespread usage. These are (1) simple current mirror (SCM), (2) Wilson current mirror (WCM), (3) Improved Wilson current mirror (IWCM), (4) cascoded current mirror (CCM). Active current mirrors make use of amplifiers to drive compensations, feedback loops and/or regulators. This consumes extra power in respect to the data signal and is therefore to be avoided in low power applications if possible, though they have much better specifications otherwise. Other subsequent modes of the previously mentioned mirrors are the use of potential shifted sources of the transistors and extra biasing currents to set stable operation region. All techniques inherent different characteristics, thus trends and brief overviews will be given for each in the next sections.

#### 3.2.2 Noise

Noise can be a significant error source for many applications, especially when using low powered signals. However, for current mirrors considering small gain and low frequencies, the added noise is negligible, applying to all mentioned topologies. However, for small lengths and narrow bandwidths at low current levels one has to be careful as the flicker noise could prove significant. Methods to minimize noise are: (1) reduce the gain; (2) augmenting the output impedance; (3) decrease  $g_m$  by: (a) decreasing W; (b) decreasing  $I_D$ ; (c) increasing L. Moreover, it may seem to be favourable using cascaded gain stages to achieve gain requirements, though for higher values the best way is still direct conversion [4].

#### 3.2.3 Frequency response

Regarding frequency response, the behaviour of the topologies is very different. Mutual design strategies for maximizing the bandwidth are: (a) Increasing the quiescent current; (b) decrease W and/or L (L being the dominant parameter); (c) decrease the gain to move the dominant pole imposed by  $C_{gs}$  of M2, though the two first must be applied with care as decreasing the output impedance affects the accuracy. Also note that the current frequency response is often not restricted by the current mirror or the output load, but mainly due to the current to voltage(I-V) conversion performed by the load itself. This is setting strict requirements to the load for a given current. Concerning the topologies, both Wilson mirrors are performing much better than the others and are in general not as affected by larger gains because of their negative feedback compensation [3]. The CCM is the slowest of the presented topologies.

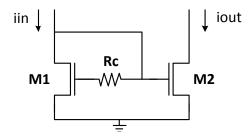

A technique of bandwidth enhancement is to add a resistor between the gates of the mirroring transistors demonstrated with a SCM in figure 3.3 on the facing page. This will effectively change the first-order low-pass filter function of the SCM given in equation 3.3 on the next page to a second-order lowpass mirror with one zero and two poles given by equation 3.4. By choosing  $R_C = 1/g_m$  and  $C_{gs1} = C_{gs2}$ , the zero is cancelled out by a pole yielding a first order system with twice bandwidth of the original circuit. However, on-chip poly-silicon resistors have rather large variations in addition to be affected by temperature and are therefore unsuitable for this purpose. Exchanging it with the  $r_{ds}$  of a small transistor biased in a manner to compensate for global process variations and temperature drift is therefore necessary[21].

Figure 3.3: SCM with compensation resistor for bandwidth enhancement

$$\omega_0 = \frac{g_m}{2C_{gs}} \tag{3.3}$$

$$\omega_0 = \sqrt{\frac{g_{m1}}{R_C C_{gs1} C_{gs2}}} \tag{3.4}$$

#### 3.2.4 Mismatch

Mismatch is a substantial part of the limitations considering all precision analogue design and is identified by the differential performance of two or more devices. For current mirrors, this is defined according to equation 3.5 and is affected by a numerous of processes. Commonly, the deviation of the output current of a current mirror is given by equation 3.6, moreover introducing the current ratio M : N results in the relative variance of the current ratio R given in equation 3.7. The error associated with edge variations is given in equation 3.8. The derivation of this is given in [12, p.75]. The later equation is stating that if the ratio is due to dimension sizes in the transistors, an additional offset is introduced and the use of equal sized parallel devices is recommended. Furthermore, the variance is widely determined by the smallest device making it important to keep ratios low so to make the minimum sized device as large as possible. It is also evident that increasing the area, preferable the length to also increase  $V^*(=V_{gs} - V_T)$  is the only way of reducing the mismatch for a given current. The foundry provides the parameters for these equations, though including extra parameters for deviation in effective channel length and width to accommodate for mismatch to the measured performance. The mismatch scales with the inverse of the current level and is known to grow exponentially in sub-threshold region.

$$\delta_I = \frac{I_{in} - I_{out}}{I_{in}} \tag{3.5}$$

$$\frac{\sigma^2(I)}{I^2} = \frac{1}{WL} \cdot \left(A_{\beta}^2 + \frac{4AV_T^2}{V_{GS} - V_T}\right)$$

(3.6)

$$\frac{\sigma^2(R)}{\overline{R^2}} = \frac{1}{WL} \cdot \left(A_\beta^2 + \frac{4AV_T^2}{V_{GS} - V_T}\right) \cdot \frac{1}{2} \left|\frac{1}{M} + \frac{1}{N}\right|$$

(3.7)

$$\varepsilon_{sys} \approx \delta W \left| \frac{1}{W_2} - \frac{1}{W_1} \right| + \delta L \left| \frac{1}{L_1} - \frac{1}{L_2} \right|$$

(3.8)

If cascoding the output of several current mirrors, the total standard deviation follows equation 3.9 though the covariance is hard to predict because the common gate voltage is affected by the mismatch of the input mirror. Other effects like channel length modulation will also affect the correlation, but to a smaller extent. To provide an approximation, equation 3.10 is given and holds via the Cauchy-Schwarz inequality [33, p.291]. It describes the maximum covariance for a finite set of variances and should be used to calculate the maximum mismatch. However, simulations will probably give better results as the system has only one of the transistors in common.

$$\sigma_{Tot} = \sqrt{var(X) + var(Y) + 2cov(X,Y)}$$

(3.9)

$$|Cov(X,Y)| \le \sqrt{Var(X) \cdot Var(Y)}$$

(3.10)

Though the foundry's models have a good correlation with the real transistors, some deviation exists. The devices reported tested are of  $W/L \ge 1$  with the deviation between model and measurements increasing with a decreasing ratio. Extensive fundamental experiments reported in [18] yield  $V_T$  mismatch not following a simplistic  $1/\sqrt{area}$  function, especially for wide/short and narrow/long devices and comments on foundries attempts to accommodate the otherwise anomalous scaling behaviour by using the effective length and width. Moreover, they claim that in higher Spice modelling, this is circumvented by creating local subsets fitting the model to the data whilst creating discontinuities in the model. This makes the accuracy of hand calculations regarding mismatch in many cases often inadequate and could lead to over design. Calculations should therefore only be used for rough estimations.

In the choice of PMOS versus NMOS for best matching properties there are in general no trends across technologies regarding voltage biased devices. However, using current bias, i.e. a diode connected transistor, the lower electron mobility of the PMOS results in a higher  $V^*$  effectively reducing the mismatch in accordance with equation 3.6/3.7. Another technique of enhancing mismatch similar to  $V^*$  incrementation, exploits changing the substrate voltage, introducing a bipolar action potential in the substrate-to-source junction for the forward biased transistor. This is well documented and works especially well in weak inversion and for small devices. However, increasing the  $V_{BS}$  voltage too much results in unpredictable effects and should be avoided [11]. The  $V_{BS}$  affects the effective threshold voltage according to equation 3.11, thus also  $V^*$ .

$$V_T = V_{T_0} + \gamma (\sqrt{2\phi_p + V_{SB}} - \sqrt{2\phi_p})$$

(3.11)

Regarding layout, symmetry is of the essence concerning mismatch and the use of dummy devices is common to avoid under or over etching in the fabrication process. Common centroid layout or at least parallel or stripe pair patterns are to be used together with current flow in the same direction for matched devices. Further, large spacing and no routing over active area of all analogue components should be employed. For an extensive overview of layout guidelines and rules, it is referred to [5, 39] in addition to the foundry's own manual (confidential).

#### 3.2.5 Absolute Accuracy and dynamic range

For the mean output current, the relative error is given by equation 3.12. Disregarding mismatch, asymmetrical properties are the sources of the deviation, either caused by an inherent asymmetry in the topology as for the WCM, or through channel length modulation caused by a non-zero differential input-output voltage which is a valid assumption in most cases. Equation

| Current mirror | DC matching error $\varepsilon$                                                                      | OVC                                  |

|----------------|------------------------------------------------------------------------------------------------------|--------------------------------------|

| SCM            | $\lambda(V_{out} - \frac{1}{2}V_{in})$                                                               | λ                                    |

| WCM            | $-\frac{\lambda V_{in}}{2(1+\lambda V_{in})} + \lambda^2 \sqrt{\frac{I_{in}}{2K}(V_{out} - V_{in})}$ | $\lambda^2 \sqrt{\frac{I_{in}}{2K}}$ |

| IWCM           | $\lambda^2 \sqrt{\frac{I_{in}}{2K}(V_{out} - V_{in})}$                                               | $\lambda^2 \sqrt{\frac{I_{in}}{2K}}$ |

| CCM            | $\lambda^2 \sqrt{\frac{I_{in}}{2K}(V_{out} - V_{in})}$                                               | $\lambda^2 \sqrt{\frac{I_{in}}{2K}}$ |

Table 3.1: Output resistance of the four most common current mirrors

3.13 provides a quality factor for this, first defined in [43].

$$\varepsilon = \frac{I_{out}}{I_{in}} - 1 = \alpha - 1 \tag{3.12}$$

$$OVC = \frac{\Delta I_{out} / I_{in}}{\Delta V_{out}} \tag{3.13}$$

The channel length modulation effect, in resemblance to the early effect of the bi-polar transistor, is caused by different bias conditions changing the position of the depletion edges. For the MOSFET, different  $V_{ds}$  voltages causes a change in the effective channel length, thus also  $r_{ds}$  leading to changing output characteristics of the current mirror. Table 3.1 summarizes the characteristics of each of the common mirrors derived from their respective output resistances [43] where  $K = \mu C_{ox} \frac{W}{L}$  being the mobility, gate oxide capacitance per unit area, transistors width and length respectively.  $\lambda$  is the channel length modulation factor and  $V_{in} = 2\sqrt{\frac{2I_{in}}{K} + V_T}$ . However, the equations are only valid for the saturation region. The literature provides little if no information about weak inversion.

From the equations it is evident that the WCM withholds an extra term independent of  $V_{out}$  compared to the other cascoded mirrors which causes an imbalance in the input-output voltage, increasing the error. From the topology of the WCM, it is evident that the output resistance is different from the input resistance, and thus a non-unity transfer function is expected for a 1-to-1 mirror. Both the SCM, CCM and IWCM withhold symmetric properties and thus provides  $i_{in} = i_{out}$  given no mismatch and  $V_{in} = V_{out}$ . However, for most systems, the output voltage will deviate from the input voltage and therefore skew this balance. The channel length modulation is dependent on region of operation, but cascoding devices are an efficient way of minimizing the effect regardless of this.

The DC-output value of a current mirror can be precisely designed for a given current level. However, if a wide range of input values are required, the mirror may change region of operation, giving non-linear behaviour.

#### **3.3** Converter Performance Characteristics

To be able to compare and determine the performance of a data converter, it is referred to the commonly used terms described in [26], chapter 11.5. In short, the offset, gain error, absolute accuracy, integral nonlinearity (INL), differential nonlinearity (DNL), monotonicity/missing codes, sampling rate and DR are defined and explained there. This is needed both for the characterization of the whole system, but also for some of the sub-modules. However, INL and DNL need some further elaboration as they can be defined in several different ways. In a current mode approach, gain error and offset are easily cancelled and a linear best-least-square approximation curve is therefore to be used. INL and DNL are then defined as the maximum difference from the fitted line.

#### **3.4** Current Comparator

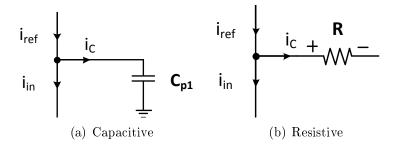

The basic principle of the current mode SAR ADC is to compare two currents to determine which is the largest. To do this, a current comparator is needed and is easily achieved by joining the currents of opposite signs and measure the output in accordance with Kirchhoff's current law (KCL) yielding  $i_c = i_{ref} - i_{in}$  given figure 3.4 on the following page. As the figure indicates, there are two approaches to measure the residual current  $i_c$ .

In the capacitive method, if the  $i_C$  current is positive, it will charge the capacitor. If it is negative, it will discharge it. The capacitor is normally not explicitly defined in the design, but makes use of the parasitics associated with the summing node as increasing the capacitor value will linearly slow down the circuit in accordance with equation 3.14 on page 19. To give a numerical example; assuming 0.2V is needed to determine the logic output, the parasitic capacitance is 15fF and the residual current is 0.1nA, the circuit

Figure 3.4: Principle of current comparison

will use  $100\mu s$  to reach the threshold corresponding to a speed of 10kHz. It is therefore evident that for small currents, care must be taken to reduce the parasitics. Because the technique exploits the time domain as a parameter to determine the output, for an infinite amount of time the theoretical resolution would be infinite. As these parameters are inverse proportional to each other, speed can be sacrificed for accuracy and is the method of choice when high resolution is required. Feedback loops could be applied to increase transition time.

The resistive topology exploits the instant voltage drop/gain over the resistor as a result of the residual current flowing through it. For an ideal circuit, the speed would be infinite, though for real implementations parasitics will introduce limitations. However, the resistive method is widely used when high speed is required. On the other side, because the voltage supply is limited and the unit measuring the voltage over the resistor has a finite resolution, the current values through the resistor are limited and thus give rise to a finite resolution. A combination of the two techniques is also possible [10, 14] and will be explained later.

It is also common to distinguish between synchronous and asynchronous design. However, synchronous methods are not applicable for this ADC as there are no accurate clock sources available on-chip, thus auto-zeroing techniques for offset attenuation or propagation delay reduction though the use of clock-controlled circuitry are not possible.

#### 3.4.1 Implementations

The easiest capacitive implementation is using an inverter which input is connected to the summing node employed by previously published works [2, 17].

However, if the residual current is small compared to the capacitor, the time where the input of the inverter is between the rails becomes significant. In this period, the current draw of the inverter is huge resulting in an energy inefficient system. Also, because the system is non-ideal, the input current sources will be affected by the summing voltage through the channel length modulation effect and will result in a finite voltage non-equal to the rail voltages. Especially if the two currents are near equal to each other, the voltage will not deviate much from common-mode, resulting in a huge power loss, also after settling. A solution to this may be to use a current starved inverter chain to control the current draw. Other methods involve using operational transconductance amplifiers (OTAs) or Operational amplifiers (OPAMPs) though requiring relative large bias currents for slew-rate requirements following the same simplistic equation in 3.14. Some existing amplifier topologies using feedback to control the output biasing, encounter this by reducing the bias when not shifting output value resulting in high slew-rate and low power operation [30, 34]. However, these techniques are often complicated and more suitable in higher power applications.

$$i_C = C \frac{dV}{dt} \Rightarrow \Delta t = \frac{C\Delta V}{i_C} \tag{3.14}$$

The resistive (low impedance) method is usually employed using an amplifier connected in a resistive feedback configuration allowing the residual current to flow to the amplifier's output node, using the amplifier to source or sink the current for equilibrium [28].

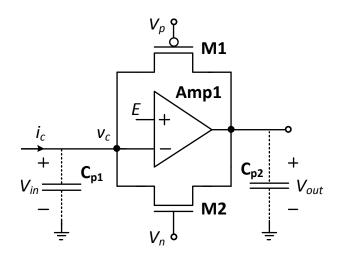

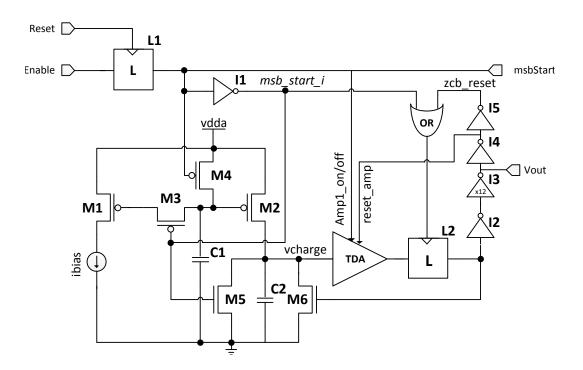

The third option is to combine the two methods and has been successfully employed yielding high accuracy at high speeds relative to the power level [10, 14]. Figure 3.5 on the following page demonstrates this functionality. The circuit has two operating modes being either positive or negative  $i_C$ where the M1 path is used for the negative currents and M2 for the positive. M1 and M2 must be biased in a manner to make the  $r_{ds}$  of the respective transistor equal to high impedance relative to the input current near common-mode output voltage levels. Considering a positive  $i_C$  charging the parasitic capacitor between the input and the output, the input voltage  $V_C$  will start deviating from the common-mode voltage E and the inverting amplifier will switch transistor M2 on as  $V_{gs_{M2}}$  increases with decreasing output voltage. Turning M2 on draws current to the input node equalizing the voltage to common-mode. Ideally this will keep the input voltage at common-mode and the amplifier's output will vary dependent on how much

Figure 3.5: Multilevel input impedance current comparator

current needed to be sourced or sink from the input node. The output voltage will also need to further be amplified to make a logical value. However, this is not a problem as the sensitivity of this node can be adjusted with the preceding amplifier Amp1. It is similar for the negative currents. There exist other similar topologies, but as the parasitic capacitance  $C_{p1}$  is important to keep as small as possible, source follower structures in the resistive path are to be avoided. This is because the capacitance  $C_{gs}$  of a transistor tends to be large and in this configuration effectively forms a capacitive coupling from input to output, much alike the Miller effect in amplifier structures slowing down the circuit.

The settling time is given by equation 3.15 where GB is the gain-bandwidth product of the amplifier and J is the input current overdrive step, assuming [-J, J] step response [14]. It is evident that to increase settling time, a high gain-bandwidth product and/or a large input current change is required. Furthermore, the biasing of transistor M1 and M2 should just meet the requirements, though a margin must be assumed allowing for process deviations. Biasing conditions is given by the equations in 3.16 on the facing page.

$$T_D = \sqrt{\frac{2C_{in}}{GB} \frac{V_p - V_n + V_{tn} + |V_{tp}|}{J}}$$

(3.15)

$$V_{in} = V_o = E$$

$$V_n \leq CM + V_{tn}$$

$$V_p \geq CM - |V_{tp}|$$

(3.16)

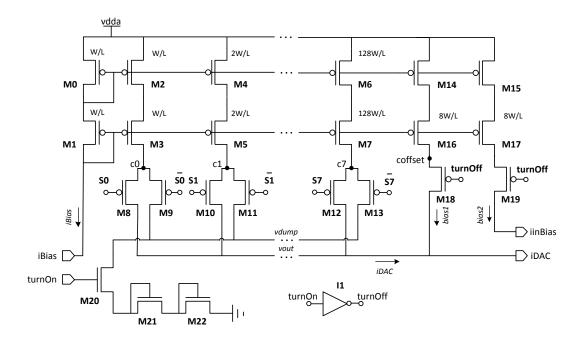

#### 3.5 Current Mode DAC

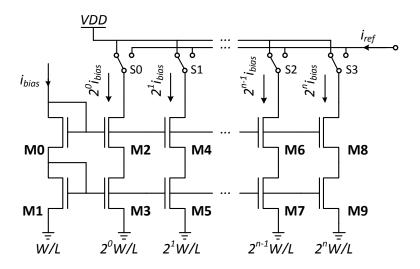

Another major part of the system is the current reference circuit. This is commonly implemented as a binary weighted current splitting array using switches to steer the current [2, 17]. Figure 3.6 on the next page is showing a typical implementation. The scaling of the transistors to create the different current paths, is with the use of multiple equal sized transistors supported by the theory in section 3.2 on page 11. This is to create accurate current levels with the lowest amount of mismatch. Because the reference current is split into several current paths, the use of feedback current mirrors such as WCM and IWCM is not possible. A downside with this current mode DAC is that the current not used for the output reference is just dumped into the power supply. Turning the mirrors dynamically on and off are normally not possible for 8bit resolution DACs given sub-threshold operation as there will be settling issues limited by the frequency response of the mirrors. The required transistor dimensions for a low production yield are by great too large for a reasonable frequency response. The technique is however demonstrated with great success in [16] also offering multiple gain stages for increased minimum sized current mirrors, though the paper says nothing about mismatch.

Other topologies are R-2R based converters, dynamically matched current source DACs and hybrids together with different coding schemes [26, p.471-484]. Though the dynamically matched current source DAC features no inherent mismatch because it uses the same transistor for both input and output current, leakage over time will affect the accuracy of the output current and will therefore require regular calibration. Though the literature suggests several techniques of improvements [12, p.381], calibration through switched circuitry is still needed and thus not suitable for this project reasoned the asynchronous chip. Coding schemes like thermometer-code are known to reduce glitches when switching between the different output values in addition to support inherent monotonicity and good DNL errors[26, p.477]. Normally, care must be taken for proper timing of the control signals to avoid glitches causing either temporary low impedance between power

Figure 3.6: Common implementation of a current mode DAC

rails or high impedance nodes which slows down the circuit. This method requires extra logic for the binary-to-thermometer code conversion though. Using only one control signal per channel is another technique to minimize this problem [26, p.478].

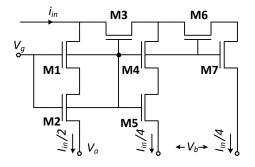

There exist several different R-2R converters. They commonly use a larger reference current and divide it into several smaller current paths to generate the binary scaled current output array. A current division technique is described in [6, 15] and repeated in figure 3.7 on the next page for convenience. This is claimed to be independent of process variations and reference current level, though still subject to output voltage dependency and mismatch. The circuit achieves 103dB DR and -80dB THD at 10kHz using  $I_{max} = 100 \mu A$ which corresponds to about 12bit operation. However, the circuit requires relative high supply voltage because of its many stacked transistors. It works as follows. Current  $i_{in}$  gets split in two equal portions because the resistance seen from the input node is equal in the two splitting branches given that  $V_a = V_b$ . The current through M3 sees an equal resistance in M4 + M5and M6 + M7 and gets further divided in two. This can go on, but terminated here in this example for simplicity. It is important that all current branches are active to balance the circuit. In [31] a slightly different scheme is implemented, re-printed for convenience in figure 3.8 on the facing page. It is reported to be able to generate currents down to pico-range with small mismatch, though the accuracy suffers due to the SCM-structure.

Figure 3.7: Current splitting technique I

Figure 3.8: Current splitting technique II

#### 3.5.1 Performance Limitations

The DR of the current mode DAC, regardless of chosen topology is easy to calibrate as it is proportional to the given reference current cf. equation 3.2. Also offset is easily removed as subtraction and addition in current mode is a matter of connecting nodes together. However, the relative accuracy between the current branches determines the obtainable resolution where absolute accuracy, mismatch and DR of the current mirrors are the determining factors.

### Chapter 4

# Design and Methods

This chapter will describe the design process and in detail give an account for the implementation decisions. The design takes basis in [16], holding the lowest reported power and area<sup>1</sup>.

#### 4.1 Estimations

A power, area and error budget was set up regarding the three main modules; the current comparator, the current mode DAC and the logic. In addition, overhead was taken into account for the S/H-circuit not included in the design. Half the power and area and one third of the error budget were reserved this part, though the design of this was left to other members of the team. The estimations take basis in [16] and an overview can be found in the result section, table 7.1 on page 50 for comparison with the final result. Given this budget, the maximum reference current, i.e. the least significant bit(LSB), was estimated to be 1nA.

The design process followed a bottom-up approach, putting the system together as the individual parts got finished.

$<sup>^1\</sup>mathrm{As}$  of October 2010

#### 4.2 Current Mirror

An extensive characterization of all mention mirrors was performed at the beginning of the project to better know the limitations. Already conducted experiments reported in the term project[22] served as the foundation, though a more complete and thorough approach was conducted for this paper. Width and length for the current interval [0.1nA, 1nA] were tested for the topologies in section 3.2.1 concerning mismatch, frequency response, DR, noise, leakage and absolute accuracy. An overview of the main results is given in appendix at page 89 with accompanying scripts from page 75. In general, the results showed a consistency with the theoretical principle, though the theory was unable to predict the absolute values within acceptable margin. This is, as section 3.2 suggests, because the common diode-equation for describing sub-threshold operation is too simplistic and requires more sophisticated modelling. The technique of bandwidth enhancement prove well functioning and should be used for the input current mirror as this is the only mirror the technique is applicable for.

#### 4.3 Current Mode DAC

The results from the current mirror simulations suggests that the dynamical approach of adjusting the power consumption of the DAC with the input signal level described in section 3.5, is far from realistic. Even using the WCM and neglecting the accuracy and DR, the settling speed of  $\sim 10kHz$  for 1nA bias is not enough to accommodate the sampling frequency requirement of 16kHz, especially considering that three such mirrors are cascaded in this implementation. The numbers are obtained when the transistors are sized to give an acceptable mismatch, though they can be much improved by downsizing. If one disregard production yield, only focusing on the typical performance, this solution is possible and enabled through the use of post-fabrication trimming of the critical transistors. However, this is time consuming and expensive and therefore not suitable from an industrial point of view.

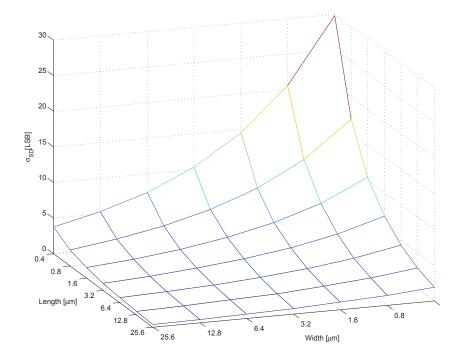

Deciding to use the common current mode DAC implementation described in 3.5, the frequency response requirement of the current mirrors disappears and arbitrary large transistors could be used to accommodate the other specifications as long as within the given area. It is decided to use PMOS current

Figure 4.1: SCM Mismatch - 3D model

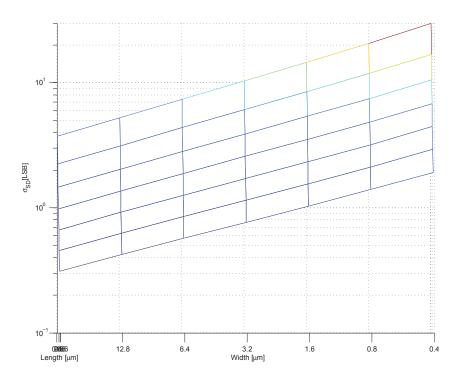

mirrors as they employ a significant reduction in standard deviation compared to the NMOS mirror. Looking into the mismatch for weak-inversion operation of the current mirrors though, it is evident that it would require impractical large transistors to give 8-bit resolution. The results presented in figure 4.1 and 4.2 on the following page are captured using a 1nA input current with a 1 : 128-ratio current mirror using unit sized devices. The size is given by the x,y- coordinates and the standard deviation is normalized to the input current. The figures show an inverse logarithmic dependency of the standard deviation to the area.

Calculating the required mismatch for each current path in the 8-bit binary scaled DAC, makes it evident that the requirements can not be met without calibration. The derivation is given in appendix at page 73. From this, it is evident that the MSB requires a standard deviation less than  $\sim \frac{1}{12}nA$ . Figure 4.2 shows that a unit area much larger than  $25.6 \times 25.6 \mu m^2$  is required to accommodate this. In fact, the area required will exceed the budget by far and therefore a calibration scheme is introduced. This will be dealt with in a later section.

Assuming that the mismatch will be calibrated within requirements, DR and

Figure 4.2: SCM Mismatch - Side projection in log-scale

accuracy are the next concern. An overview of the response from the different mirrors is attached in appendix at page 89 including frequency response, noise analysis and leakage. From this, it is shown that the CCM or IWCM is needed for the output current mirror, concerning the linearity over the DR. They also perform well in terms of accuracy which is convenient for easy transistor dimensioning. The simulations shows further that leakage is of no concern for neither of the mirrors, while the Wilson-type mirrors show significant increased noise levels. In frequency response, the Wilsontype mirrors perform best, though all mirrors for reasonable sizes are within specification. The CCM is therefore selected for all the full-range current mirrors needed. The inherent source degradation of the lower mirror in the CCM architecture also improves the mismatch, though to a small extent.

The DR and accuracy are not important for the individual current paths in the DAC as these currents will be DC and can be adjusted individually with different sizing. A SCM is therefore possible saving area compared to the others. However, this will require different sizing of all individual transistors and lead to larger mismatch because of asymmetry in the layout. Other concerns with this are the lack of robustness, in terms of being dependent on an accurate input bias for the right scaling ratio in addition to temperature dependency. It was therefore chosen to use CCM for the DAC module as well, sacrificing area for increased robustness and a more consistent layout.

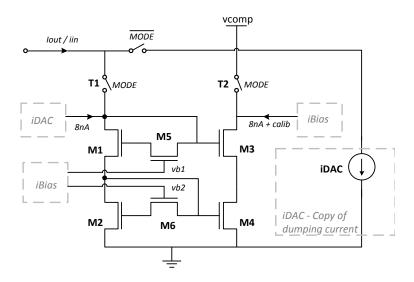

#### 4.4 Current Comparator

Given the selected bias at 1nA, the input range of the current comparator is from -128nA to 128nA. With an error budget of  $\frac{1}{3}$  of the overall budget, the comparator will need to settle to  $\frac{1}{6}nA$  accounting for the requirement of INL less than  $\pm 0.5 LSB$ . For the settling time, 50%, i.e.  $\sim 4\mu s$  was first assigned. All topologies mentioned in section 3.4 were tested. The simple inverter proved well functioning, but showed a very high average power consumption. Changing the inverter to a current starved inverter chain was briefly tested and reduced the power within budget though increased the signal path delay so that the total comparator delay became too large. The OPAMP method proved too slow because the transistor dimensions of the input stage needed to be large because of mismatch considerations, introducing a large gate capacitance coupled directly onto the comparing node. The multi-level input impedance comparator was tested using a voltage limited inverter as the amplifier introducing a  $\sim 2fF$  capacitance at the input. Estimates of the gain-bandwidth product needed by the amplifier were calculated from equation 3.15 on page 20 yielding around  $\sim 1MHzV/V$  using  $V_p = V_n, V_t n = |V_t p| = 0.35$  and were used to design the final amplifier. The multi-level input impedance comparator proved well functioning and selected for the final implementation.

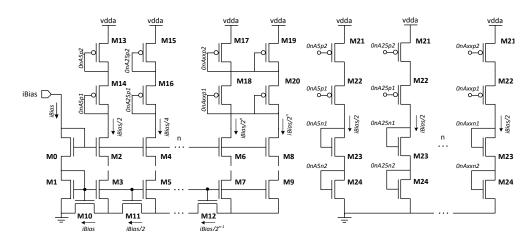

#### 4.5 Calibration

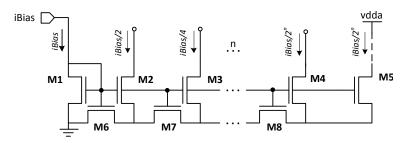

To make calibration currents, the need of creating binary scaled reference currents smaller than the supplied bias arose. For this, the second current division technique described in section 3.5 was used. The same argumentation for choosing CCM is used for this module as for the DAC. However, for this purpose it is further extended because the number of current copies made from the reference currents will vary dependent on the individual need of calibration for each chip after production. This will affect the reference current because of the sensitivity of pico-range current levels.

With reference currents for each binary division step down to 31.25pA, cur-

rent mode DACs were made for each bit in the main DAC, adjusted to accommodate the individual channel's calibration needs.

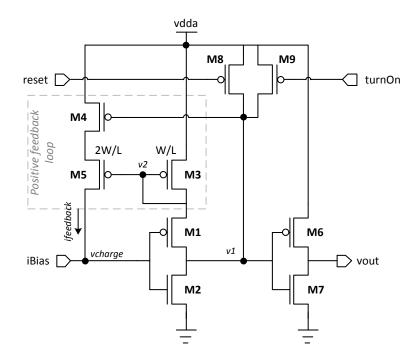

### 4.6 Logic

The digital part of [16] which served as the basis for the initial project, is when realized very power hungry and seemingly a poor design. In detail, it is the pulse generating feedback loop consisting of an inverter chain that uses the largest amount of power. Three solutions were derived to improve this: (1) Using an differential two stage amplifier with large gain in a feedback configuration, (2) a power restricted inverter chain increasing the currents in later stages for sharpening of a digital signal while ensuring limited current draw, (3) a novel threshold detecting amplifier (TDA) using the inherent signal properties to drive a positive feedback path. All three methods significantly improved the power consumption, though the last option proved to be the best.

### Chapter 5

### Implementation

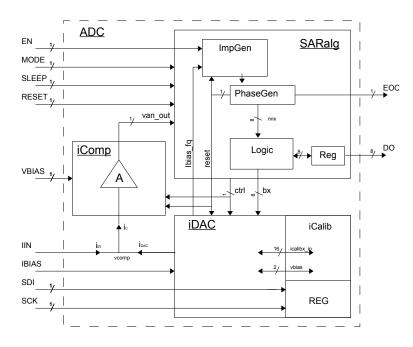

This chapter will in detail describe the final implementation of the ADC and is divided into four sections; Control Logic (SARalg), Current Comparator (iComp), Current Mode DAC (iDAC) and Calibration Module (iCalib) respectively. An overview of how all the modules are interconnected is shown in figure 5.1 on the following page. The ADC has some extra features including a sleep-mode (SLEEP) and a test-mode (MODE). The sleep-mode is used to turn off all bias currents leaving only leakage as the power consumption. This is a feature required by the neuron implementation to turn of defect channels. In test-mode, the current comparator is turned off and the DAC current is copied to the input pin making it a sourcing output pin. This enables the DAC module to be tested separate, thus allowing easier calibration and debugging if necessary. A pin overview is provided in appendix at page 87. A design overview is provided with figure 5.1 on the next page.

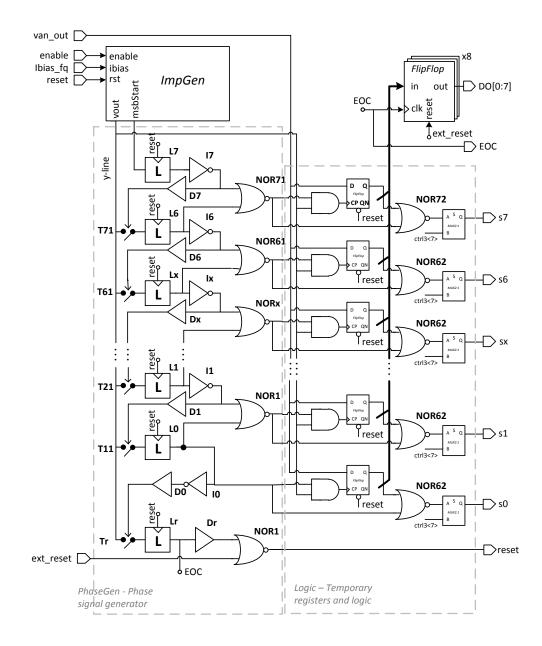

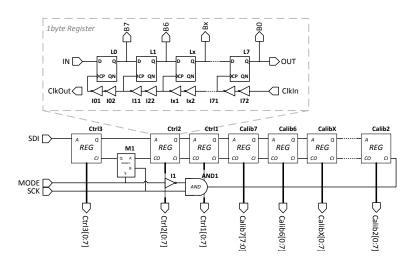

#### 5.1 Control Logic

The digital logic (SARalg) used to realize the SAR algorithm is shown in figure 5.2 on page 33. The impulse generator (ImpGen) together with the phase generator (PhaseGen) establish the connection between the comparator output and the appropriate storage register for each cycle. The  $NOR_{X2}$ gates provide the control to the current mode DAC using a combination of the non-overlapping phases and the stored values. This design is similar to [16]. However, several enhancements concerning power consumption and reliability have been applied. First, the input from the comparator module

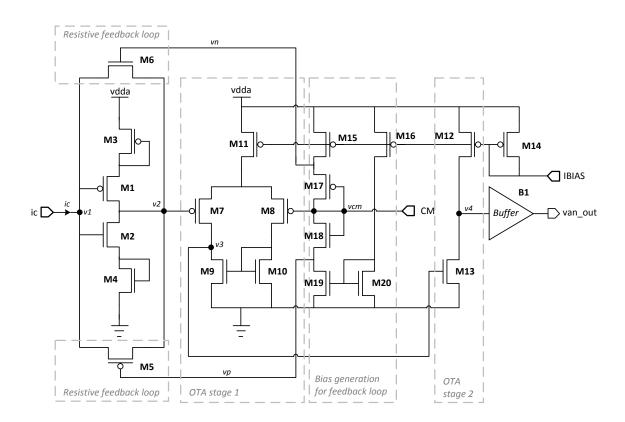

Figure 5.1: System level design for the current mode SAR ADC.

is for this application purely digital making the original storage capacitors redundant and are exchanged with digital flip-flops. This because in addition to voltage drop over time causing the consecutive stage to draw unnecessary power, the capacitors for this technology would be minimum 30fF causing heavy load for the comparator module. Instead the flip flops provided by the founder exhibiting 2fF input capacitance were used, adding up to 16fF load or the equivalent 8x driving strength for the preceding stage. It is also added output registers holding the acquired data until the next set of data is ready, avoiding accurate timing considerations and increasing the flexibility of the system. The  $L_x$  latches used in the phase generator module are also altered reducing power consumption by using positive feedback to drive logical signal fast to rail. The non-ideal logical voltages are caused by the on-resistance of switches  $T_{X1}$  in combination with parasitics leading to long turn-on time. The 2:1  $MUX_x$ s are used to explicitly control the iDAC in test mode.