## A 33 µW Sub-3 dB Noise Figure Low Noise Amplifier for Medical Ultrasound Applications

Hans Herman Hansen

Master of Science in Electronics

Submission date: July 2011

Supervisor: Trond Ytterdal, IET

## Problem Description

The main goal of this project is to design a low nose amplifier for medical ultrasound imaging using a  $180 \, \text{nm}$  design kit from Austria Microsystems. The low noise amplifier is intended to be used with a piezoelectric transducer with a center frequency of  $7 \, \text{MHz}$  and a  $100 \, \%$  relative bandwidth, i.e. from  $3.5 \, \text{MHz}$  to  $10.5 \, \text{MHz}$ .

The main focus should be on the design of the low noise amplifier, having a very low power budget and small area. The maximum power per channel is 130  $\mu$ W for both transmit and receive. Therefore, the available power for the analog–front end is limited to half of this. As a result the maximum power consumption for the low noise amplifier is 40  $\mu$ W, which only allows for a bias current of 22.2  $\mu$ A for a 1.8 V supply. The noise factor should ideally be less than 3 dB, but due to the extremely low power budget a noise factor as high as 5 dB is acceptable. It would also be of great advantage if the amplifier could perform a single–ended to differential conversion.

The given transducer element can be modeled at resonance as a capacitor of 450 fF in parallel with a 32 k $\Omega$  resistor. Due to the high impedance of this small element, the input capacitance should be as small as possible in order to cause minimum attenuation of the input signal of the amplifier, i.e. less than 100 fF. The input resistance should be much higher than 32 k $\Omega$  in order to achieve a good voltage division when using voltage sampling.

The type of output could be both current and voltage. In case of a voltage amplifier, the voltage gain should be more than 20 dB.

The main topic of this thesis is to design a low noise amplifier for ultrasound applications. Thus, the task will consist of

- 1. Be familiar with low noise amplifier fundamentals

- 2. Be familiar with ultrasound front—end electronics, including variable gain

- 3. Designing a low noise amplifier within the specifications

- 4. Verifying the design through relevant test benches

A major specification of any ultrasound front—end is the ability to handle the large dynamic range of the ultrasound signal. If time, the project could also include investigations of different methods of implementing variable gain. Finally, designing the layout and doing post layout simulations could also be done as a part of the thesis.

Assignment given: 31. August 2010. Supervisor: Trond Ytterdal, IET.

#### **Abstract**

The low noise amplifier is a critical part of most high performance ultrasound receivers, and is important for achieving high sensitivity and a wide dynamic range. By having a large gain in the low noise amplifier, the total noise of the receiver system will be dominated by that of the amplifier. For most low noise amplifier, there is a fundamental trade–off between accuracy and power consumption, which makes it difficult to design micro power front–end amplifiers with excellent noise performance. In some cases, however, lower accuracy can be tolerated if the source itself is noisy. This is the case for small, high impedance sources, where the noise level is in the region of  $18 \, \mathrm{nV}/\sqrt{\mathrm{Hz}}$ .

This thesis presents the design and simulations of a low noise amplifier in standard 180 nm CMOS suitable for use with high impedance sources. In fact, high impedance sources pose challenges on the biasing of voltage amplifiers, where maintaining high input impedance is necessary. In addition, for differential amplifiers, implementing common—mode feedback will typically result in a significant increase in power consumption and area overhead. To alleviate this problem, a switched common—mode feedback scheme is implemented, that also provide high input impedance biasing of the input transistors.

In order to cope with the large dynamic range requirement inherent in many ultrasound modalities, variable gain is often used to compress the dynamic range for the analog front—end. Methods for adding variable gain without resulting in a large increase in area and power consumption is therefore of huge interest in many ultrasound applications. Several methods of adding variable gain is investigated in this thesis, and a capacitive attenuator is proposed, which causes minimum increase in noise factor, while increasing the gain range by at least 20 dB.

Large scale integration of several thousands analog front–ends in a single ultrasound probe handle requires low power consumption and minimum area overhead for all parts of the analog front–end, including the low noise amplifier. By using a figure–of–merit based optimization technique, the designed amplifier topology achieves an low power consumption of 17.3  $\mu$ A, while maintaining a noise factor of less than 3 dB at resonance. In addition to performing a single–ended to differential conversion, this amplifier realizes a maximum voltage gain of 23.4 dB, with a 3 dB bandwidth of 21.5 MHz.

## Preface

This thesis is submitted in partial fulfillment of the requirements for the degree of master of science (MSc) at the Department of Electronics and Telecommunications, Norwegian University of Science and Technology (NTNU). The work was carried out in the period August 2010 to July 2011 as a 50 % part time study, under the supervision of Professor Trond Ytterdal, who is with the Department of Electronics and Telecommunications at NTNU

### Acknowledgment

First and foremost I would like to thank my adviser Trond Ytterdal, both for introducing me, and giving me the opportunity to work with the topic of analog circuit design. His vast, and seemingly never—ending insight within the topic, combined with his enthusiasm, have been a great source for both motivation and inspiration during this work.

I would like to thank my fellow students for valuable input during the course of writing this thesis. I would especially like to thank my friend and fellow student Dragan Mitrevski for many motivating and fruitful conversations, and for introducing me to many of the advanced typesetting techniques used throughout this thesis. I'm also grateful to the rest of my friends I've made over the years at NTNU for six unforgettable year. Especially thanks to Einar Berge Mogstad, Henning Bjørgo, Johannes Haukelidsæter, Even Heum Hennie, Anders Ellingsen Stephansen, Eirik Skogestad Næs, Rune Bergh Nilssen and Markus Løland for making all these years fly by.

Trondheim, Norway, July 2011, Hans Herman Hansen

## Contents

| 1 | Int           | roduction                                  | 1  |

|---|---------------|--------------------------------------------|----|

|   | 1             | Thesis Outline                             | 2  |

| 2 | $\mathbf{Th}$ | eoretical Background                       | 5  |

|   | 1             | Low Noise Amplifiers                       | 5  |

|   | 2             | Linearity                                  | 5  |

|   | 3             | Linearization Techniques                   | 7  |

|   | 4             | Noise in Solid–State Circuits              | 8  |

|   | 5             | Thermal noise                              | 8  |

|   | 6             | Shot Noise                                 | 9  |

|   | 7             | Flicker Noise                              | 10 |

| 3 | Ult           | trasound Front–End Electronics             | 11 |

|   | 1             | Systems Overview                           | 11 |

|   | 2             | Practical Front–End Circuit Considerations | 13 |

|   | 3             | Transducer Elements                        | 14 |

|   | 4             | Variable Gain                              | 15 |

|   | 5             | Dynamic Range                              | 15 |

|   | 6             | Power Consumption                          | 16 |

| 4 | In-           | -Probe Analog Front–End                    | 17 |

|   | 1             | Analog versus Digital Power Consumption    | 17 |

|   | 2             | Digital Beamforming ASICs                  | 18 |

|   | 3             | Front-End Architecture                     | 20 |

|   | 4             | Piezoelectric Transducers                  | 21 |

|   | 5             | Voltage Sampling                           | 22 |

|   | 6             | Single–Ended to Differential Conversion    | 23 |

| 5 | Cir           | rcuit Topology                             | 25 |

|   | 1             | Linearized Transconductor                  | 25 |

|   | 2             | Simplified Amplifier Topology              | 27 |

|   | 3             | Small–Signal Analysis                      | 28 |

|   | 4             | Source–Follower                            | 29 |

|   | 5             | Noise analysis                             | 30 |

|   | 6             | Previously Published Noise Analysis        | 30 |

|   | 7             | Simplified Noise Analysis                  | 31 |

| 6            | Methods for Adding Variable Gain            | <b>33</b>    |

|--------------|---------------------------------------------|--------------|

|              | 1 Capacitive Divider                        | 33           |

|              | 2 Variable Resistor                         | 35           |

|              | 3 Coarse Gain Steps                         | 36           |

| 7            | Design Methodology                          | 37           |

|              | 1 Figure–of–Merit for Analog Modules        | 37           |

|              | 2 Definition of Figure–of–Merit             | 37           |

|              | 3 Dynamic Range and Power Consumption       | 38           |

|              | 4 Minimum Power Consumption                 | 39           |

|              | 5 Figure-of-Merit Optimized Design          | 39           |

|              | 6 Systematic Design Approach                | 44           |

|              | 7 Common–Mode Feedback Circuitry            | 45           |

|              | 8 Feedback Biasing                          | 46           |

|              | 9 Implementing Variable Gain                | 48           |

| 8            | Simulation Results and Discussion           | 49           |

|              | 1 Simulation Setup                          | 49           |

|              | 2 Transistor Level Implementation           | 49           |

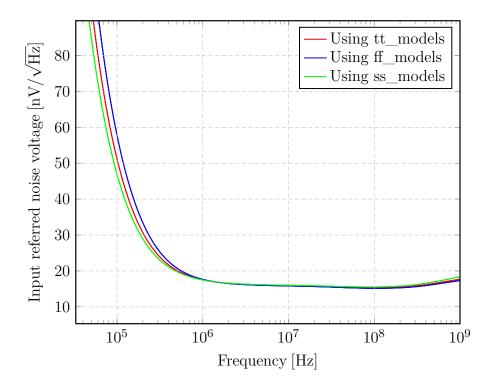

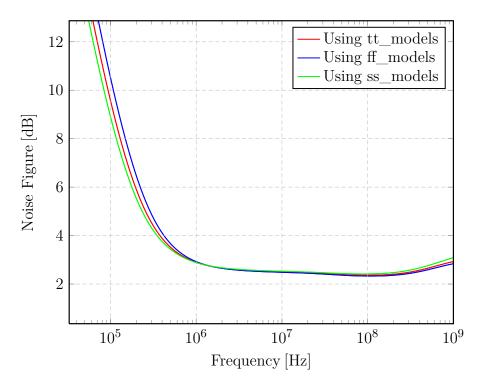

|              | 3 Noise Performance                         | 51           |

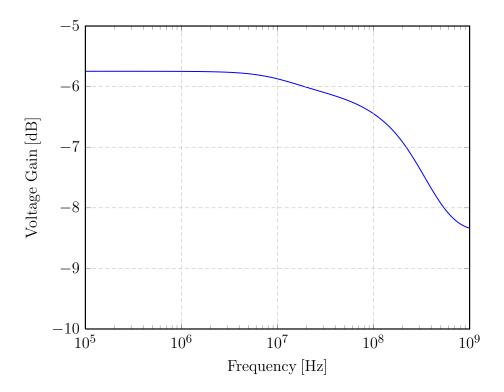

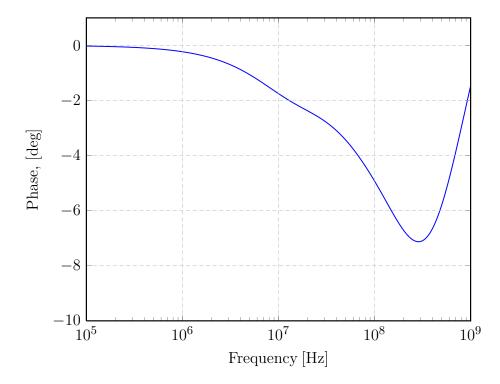

|              | 4 Frequency Response                        | 54           |

|              | 5 Small Signal Performance Summary          | 57           |

|              | 6 Large Signal Performance                  | 59           |

|              | 7 Extracting Input Resistance               | 60           |

|              | 8 Discussion                                | 61           |

| 9            | Conclusion                                  | 63           |

|              | 1 Future Work                               | 64           |

|              | 2 Main Contributions                        | 65           |

| Aı           | ppendices                                   | $\mathbf{I}$ |

| $\mathbf{A}$ | Figure-of-Merit and Noise Efficiency Factor | $\mathbf{I}$ |

| R            | Transistor Sizing                           | III          |

| ט            | 1 Sizing NMOS Transistors                   | III          |

|              | 2 Sizing PMOS Transistors                   |              |

|              |                                             | V            |

| С            | Amplifier Schematic and Netlist             | VII          |

| D            | Verifying Design Through Simulations        | XI           |

|              | 1 DC Test Bench                             | XI           |

|              | 2 AC Test Bench                             |              |

|              | 3 Transient Analysis Test Bench             | XIX          |

# List of Figures

| <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | P-channel input differential pair                                                                                                                                        | 7                                |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3.1<br>3.2<br>3.3                             | Receiver system for ultrasound diagnostics                                                                                                                               | 12<br>14<br>14                   |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5               | Analog and digital power consumption versus signal—to—noise ratio. Digital Beamforming System                                                                            | 18<br>19<br>20<br>21<br>22       |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6        | Differential pair using resistive degeneration                                                                                                                           | 25<br>26<br>27<br>28<br>28<br>31 |

| 6.1<br>6.2<br>6.3                             | Capacitive attenuator at the input of the front–end amplifier Capacitive attenuator at the input of the front–end amplifier Coarse VGA implementation                    | 33<br>35<br>36                   |

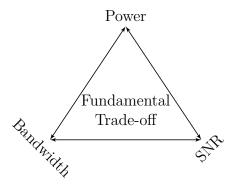

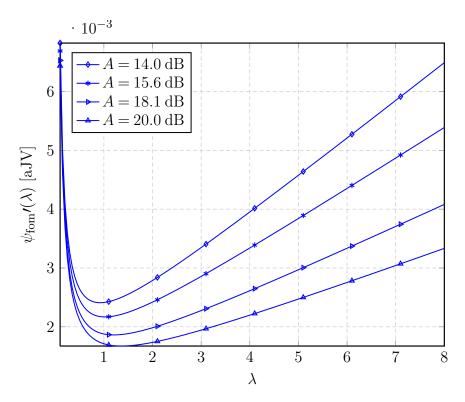

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6        | Fundamental trade–offs in analog design                                                                                                                                  | 38<br>39<br>42<br>43<br>45<br>47 |

| 8.1<br>8.2<br>8.3                             | Simplified voltage amplifier topology including biasing Input referred noise voltage spectral density for three process corners. Noise figure for three process corners. | 50<br>52<br>53                   |

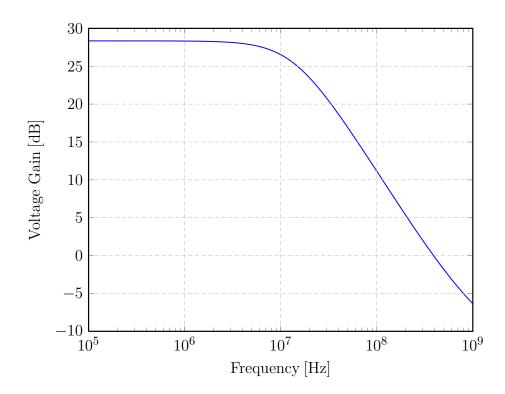

| 8.4  | Magnitude plot of the source followers buffering the input voltage    |   |

|------|-----------------------------------------------------------------------|---|

|      | across the degeneration resistor                                      | 5 |

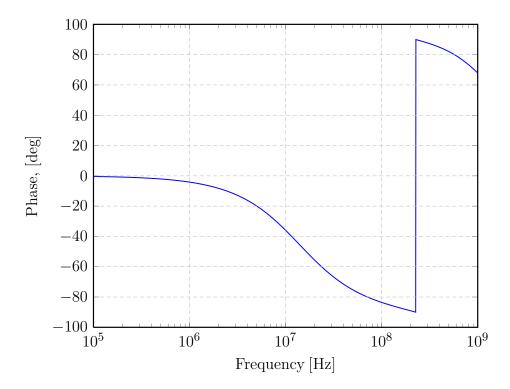

| 8.5  | Phase plot of the source followers buffering the input voltage across |   |

|      | the degeneration resistor                                             | 5 |

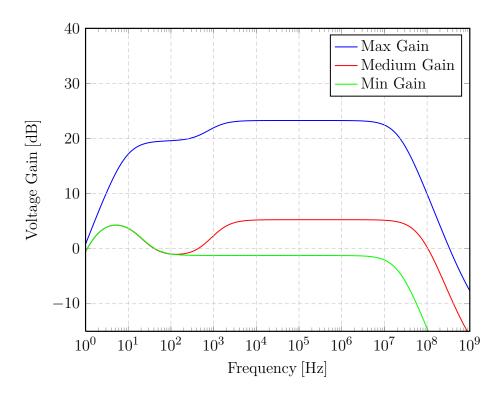

| 8.6  | Magnitude plot of the source followers buffering the input voltage    |   |

|      | across the degeneration resistor                                      | 6 |

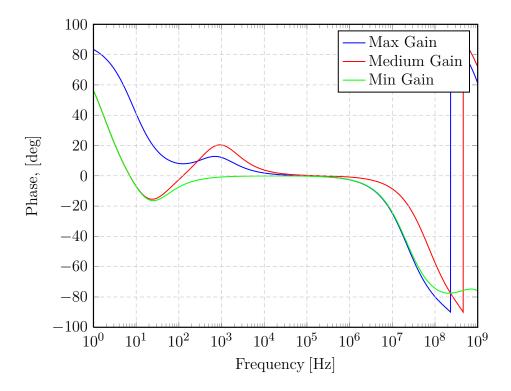

| 8.7  | Phase plot of the source followers buffering the input voltage across |   |

|      | the degeneration resistor                                             | 6 |

| 8.8  | Magnitude plot of the complete front—end amplifier                    | 8 |

| 8.9  | Phase plot of the complete front—end amplifier                        | 8 |

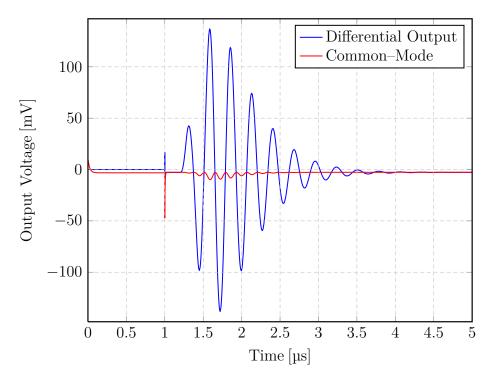

| 8.10 | Differential output voltage and common—mode level variations 5        | 9 |

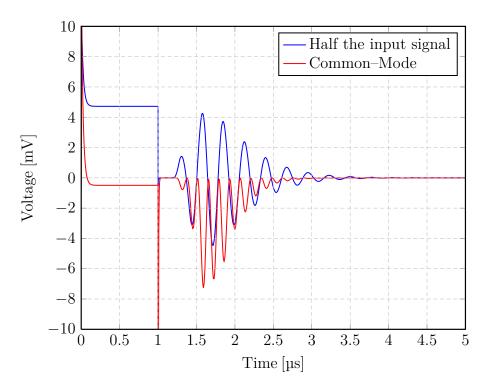

| 8.11 | Half the input signal versus common—mode variations 6                 | 0 |

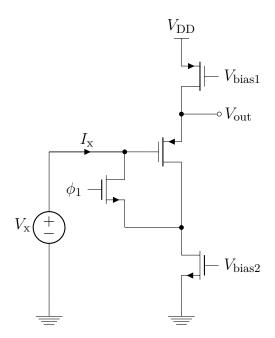

| 8.12 | Test source to extract input resistance 6                             | 1 |

| C.1  | Amplifier Schematic                                                   | Ι |

## List of Tables

| 7.1 | Important transistor parameters for the designed amplifier | 45 |

|-----|------------------------------------------------------------|----|

| 8.1 | Depicted simulations in the verification of the amplifier  | 50 |

| 8.2 | Transistor parameters for the complete amplifier           | 51 |

| 8.3 | Performance summary for the designed low noise amplifier   | 54 |

| 8.4 | Important simulation results                               | 57 |

| 8.5 | Input resistance simulation results                        | 60 |

## Chapter 1

## Introduction

Ultrasound imaging for medical and nondestructive testing purposes has made significant progress since its introduction over half a century ago [1]. In fact, much of the increase in the use of diagnostic ultrasonic imaging can be traced to improvements in image quality. In addition, digital imaging systems coming into use hold the promise of further enhancing image quality [2]. The flexibility inherent in digital imaging systems enables the possibility of using a wide range of algorithms to reconstruct, enhance, and analyze ultrasonic images. However, the usefulness of these algorithms is limited by the quality of the original data. Critical to any digital ultrasound imaging system is the analog front—end; the transducer and associated electronics which link the digital system to the medium under examination. Although imaging capabilities can be improved by digital signal processing techniques, the analog front—end normally sets the performance limits of the complete system. In particular, the signal—to—noise ratio (SNR), bandwidth, and dynamic range of the sampled data all have a strong impact on the utility of certain image processing approaches.

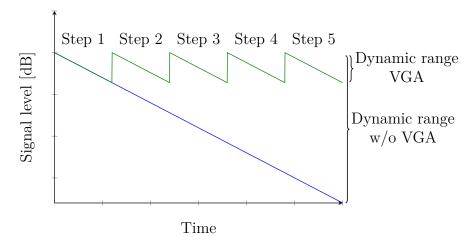

Typically, one of the bottlenecks in analog front—ends is the low noise amplifier, which must introduce as little noise and distortion as possible in order to maximize the sensitivity and dynamic range. On the other hand, the noise requirements can be relaxed if the source itself, i.e. the transducer, is less accurate. For transducers with a body resistance of several kilo ohms, the noise requirements for a 3 dB noise factor can be achieved with a relatively low power consumption. However, as the ultrasound wave propagating in tissue experiences an attenuation of 1 dB/cm/MHz the dynamic range requirements can in some applications be as high as 160 dB [3]. In order to cope with the large dynamic range associated with ultrasound imaging, variable gain is usually required in the receive amplifier.

In the pursuit of even more flexible ultrasound systems, there is an ongoing trend of integrating as much of the electronics into the transducer probe, including a low noise amplifier and analog to digital converter (ADC). Especially for 3–D ultrasound imaging this can reduce the amount of channels by employing micro beamforming in the probe handle, but also relax the amount of high quality microcoaxial cables by also integrating the ADC in the transducer. In fact, the system cable consisting of several hundred micro-coaxial cables can be one of the most expensive part of the ultrasound system. By integrating the ADC in the probe

handle, digital beamforming can be partially done in the front—end as well as in the main unit, which usually results in a better increase in signal—to—noise ratio compared to analog beamforming. Although very desirable, the area and power consumption of such an analog front—end would be extremely limited.

A front–end amplifier topology that can satisfy the requirement of high input impedance and sufficient linearity is based on the source coupled differential pair with resistive source degeneration. This amplifier topology can achieve high linearity, without sacrificing power consumption and noise performance, by boosting the transconductance,  $g_{\rm m}$ , of the input transistors using a composite device [4]. This linearized transconductor cell has received some attention in the literature [5], [6], [7], [8], [9]. For most of the applications, however, the noise performance is incompatible with medical ultrasound [5], [6], [7]. Even though [8] shows excellent linearity and variable gain, the power consumption and integrated noise is too high for this ultrasound application. Also, the low noise and distortion achieved in [9] comes at the expense of a current consumption of 40 mA, which is a few decades above the requirement in the design specifications.

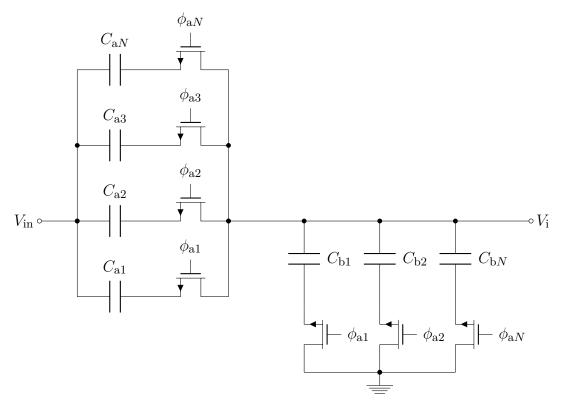

This thesis presents the design of a ultra low power, low noise amplifier using a figure-of-merit based approach [10]. By applying the figure-of-merit based technique proposed in [10], an optimized trade-off between noise and power consumption can be achieved. The designed amplifier performs a single-ended to differential conversion to match the single-ended transducer to a differential frontend. By exploiting the fact that most ultrasound systems transmit and receive pulses in time intervals, a switched common—mode feedback is proposed and implemented, that minimizes the power and area overhead typically involved with common-mode feedback circuitry, while also providing biasing of the input transistors. In contrast to many ultrasound systems, where variable gain can be implemented in a separate amplifier, the analog front-end integrated in the probe handle does not have the luxury of too much analog signal processing. However, the dynamic range must be compressed before the ADC, as dynamic range is very expensive in terms of power consumption. Therefore, a digitally controlled variable gain method is proposed that is based on a capacitive attenuator. By using a capacitive divider in front of the low noise amplifier, the input dynamic range of the micro power, front-end amplifier can be limited to avoid clipping, without sacrificing the receiver noise factor.

#### 1 Thesis Outline

This thesis is organized as follows; Chapter 2 provides a theoretical background for low noise amplifiers, with focus on noise and linearity.

In Chapter 3, ultrasound systems are described in general in order to understand the most important trade-offs in the design of front-end electronics for ultrasound. Some previous knowledge on the topic is assumed.

Chapter 4 motivates the need for in–probe electronics, and sketches the requirements for the analog front–end amplifier to be used in such a system. Some of the specifications of the amplifier have been derived using the piezoelectric transducer source, such as input referred noise level and required input resistance.

The proposed amplifier topology is described in Chapter 5, and a small–signal analysis of the circuit is provided in order to derive design equations and investigate noise performance.

Chapter 6 describes different ways of implementing variable gain for the proposed front—end, where a capacitive attenuator, that can limit the dynamic range requirement for the front-end amplifier, is proposed and described.

In Chapter 7 the figure—of—merit based approach is described and applied in the design of the front—end amplifier. In addition, the design of the variable gain attenuator and common—mode feedback circuitry is covered in this chapter. A coarse variable gain attenuator is described and simulated using a simple array, consisting of only a few capacitors and switches.

In Chapter 8 the most relevant simulation results are presented and discussed. A comparison with state of the art micro power, low noise amplifiers for biomedical applications is also shown.

Finally, the thesis is concluded in Chapter 9. The conclusion also contains suggestions for future work and a summary of the main contributions of this thesis.

Appendix A shows that the figure—of—merit (fom) used in this thesis is proportional with the more known noise efficiency factor (nef) and argues why they are essentially equivalent formulations.

Appendix B contains the test bench used in the design of the transistor dimensions.

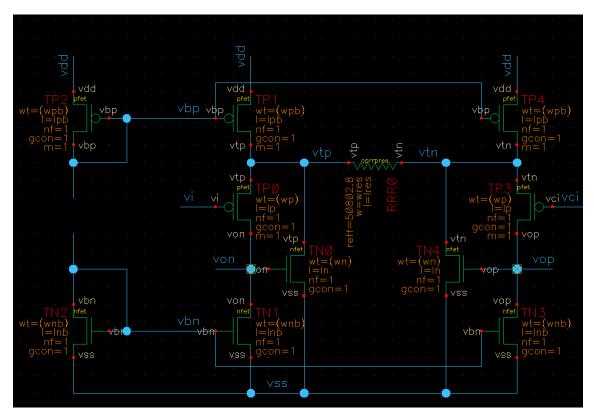

In Appendix C the schematic of the amplifier is shown with a 1:1 corresponding netlist.

Finally, Appendix D shows the different test benches used to verify the amplifier performance.

## Chapter 2

## Theoretical Background

This chapter briefly describes relevant, fundamental background theory for this thesis, with special focus on noise and linearity. Understanding these two parameters of the analog front—end is important in achieving a high dynamic range, one of the most essential specifications of any ultrasound front—end.

### 1 Low Noise Amplifiers

The low noise amplifier (LNA) is one of the key building blocks in most high performance analog front—ends, and is essential for achieving high sensitivity and a wide dynamic range. The low noise amplifier buffers the input signal such that the noise generated by the following blocks has little impact on the total signal—to—noise ratio (SNR). In a typical analog front—end, the low noise amplifier is one of the most important components, as it tends to dominate the sensitivity. In general, the amplifier design involves many trade—offs between noise figure (NF), gain, linearity and power dissipation. Given a large gain in the front—end amplifier, the total noise of the receiver system will be dominated by that of the amplifier. For this reason, it is essential that the amplifier can maintain a good signal—to—noise ratio, even at extremely low input signals, but also to be able to have a high dynamic range. This requires that all the receiver blocks, including the low noise amplifier, maintain a good SNR for both small signals and large signals. In fact, the linearity of a circuit is often one of the limiting factors to its dynamic range, and it is typically one of the major specifications for any front—end amplifier.

### 2 Linearity

Linearity is an important parameter that is determined by a circuit's ability to handle relatively large signal swings. Large signals can cause desensitization and harmonic distortion in a non–linear circuit, and in order to improve performance, linearization techniques are often used in CMOS circuits. For CMOS amplifiers with linear load at the output, the linearity is mainly determined by the input transistors. The transconductance,  $g_{\rm m}$ , of a MOSFET in saturation is given by [11]

$$g_{\rm m} = \mu_{\rm n} C_{\rm ox} \frac{W}{L} V_{\rm eff} \frac{1 + (\alpha/2) V_{\rm eff}}{(1 + \alpha V_{\rm eff})^2}, \tag{2.1}$$

where  $V_{\rm eff}$  is the overdrive voltage, and  $\alpha$  is defined as

$$\alpha = \theta + \frac{\mu_0}{2v_{\text{sat}}L}. (2.2)$$

Here,  $\mu_0$  is the mobility when the overdrive voltage is zero and  $\theta$  is a process constant. In addition, the body effect causes the threshold voltage to change with the input voltage, described by the following equation

$$V_{\rm th} = V_{\rm th0} + \gamma_{\rm th} \left( \sqrt{V_{\rm sb} + 2\phi_{\rm f}} - \sqrt{2\phi_{\rm f}} \right), \tag{2.3}$$

where  $V_{\rm th0}$  is the threshold voltage when the source-to-substrate voltage,  $V_{\rm sb}$ , is zero. The factor  $\gamma_{\rm th}$  is the well known body-effect constant and  $\phi_{\rm f}$  is the Fermi potential at the channel. This effect usually introduces additional distortion into a CMOS amplifier. Connecting source and substrate together can reduce the distortion, but increases the parasitic capacitance at the source.

In recent years, voltage—to—current converters or transconductance amplifiers has shown signs of dramatic change and find many applications in traditional analog applications. The simplest and most widely used transconductance amplifier is the differential pair. While offering excellent high frequency performance and low noise, its large signal characteristics are inherently non—linear.

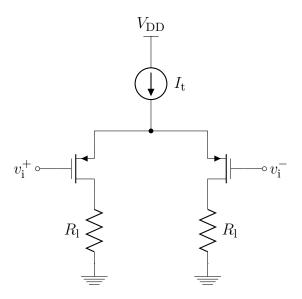

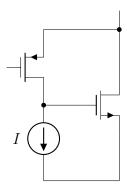

Figure 2.1: P-channel input differential pair.

Assuming perfectly quadratic i-v characteristics for the MOS transistor in the saturation region and neglecting short channel effects such as channel length modulation, the drain current can be written as

$$I_{\rm d} = \frac{\beta}{2} (V_{\rm gs} - V_{\rm t})^2,$$

(2.4)

where,  $\beta$  is the transconductance parameter and  $V_t$  is the threshold voltage of the transistor. Using this expression for the circuit in Figure 2.1 the output current is given by

$$i_{\rm o} = \sqrt{2\beta I_{\rm o}} v_{\rm i} \sqrt{1 - \frac{\beta v_{\rm i}^2}{8I_{\rm o}}} = \sqrt{2\beta I_{\rm o}} v_{\rm i} \sqrt{1 - \frac{v_{\rm i}^2}{4(V_{\rm gs} - V_{\rm t})^2}}$$

(2.5)

In general, increasing the overdrive voltage,  $V_{\rm gs}-V_{\rm t}$ , and using a longer channel device can improve linearity. Using longer devices, results in a smaller  $\alpha$ , but on the other hand, it also increases the power consumption and reduces the cut-off frequency,  $\omega_{\rm t}$ .

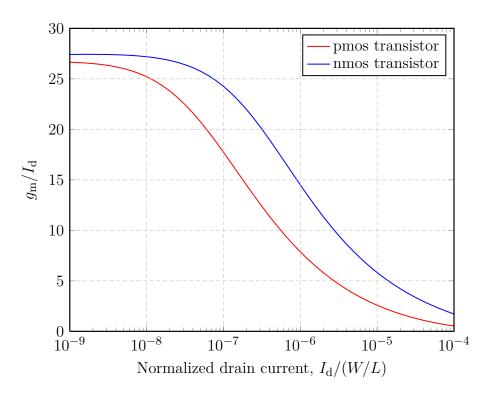

For low–voltage applications requiring a high overdrive voltage usually constitutes a major drawback. In fact, using a very high overdrive voltage usually results in a poor current efficiency,  $g_{\rm m}/I_{\rm d}$ , which may be unacceptable in power constrained designs.

### 3 Linearization Techniques

The principle idea behind linearization is to reduce the dependence of the gain upon the input signal level. Normally, this translates into making the gain less dependent of the transistor bias current. One of the simplest topologies to linearize the transfer characteristic of the MOS transconductor is by means of source degeneration using a linear resistor as depicted in Figure 2.2.

**Figure 2.2:** Differential pair using resistive degeneration.

The degeneration resistor reduces the signal swing applied between the gate and the source of the transistor by means of an internal feedback path, thus making the transfer function more linear. Neglecting the body effect, the overall transconductance of the stage can be written as

$$G_{\rm m} = \frac{g_{\rm m}}{1 + g_{\rm m}R},\tag{2.6}$$

which for large  $g_{\rm m}R$  is given by  $G_{\rm m}\approx 1/R$ , an input independent parameter. It is worth mentioning that the amount of linearization is dependent on  $g_{\rm m}R$  rather than the degeneration resistor alone. Using this technique the  $G_{\rm m}$  is relatively independent of the input and the amplifier is thus linearized.

The disadvantage of this configuration is the large resistor value needed to achieve a wide linear input range as it requires  $g_{\rm m}R\gg 1$ . Since in this case  $G_{\rm m}\approx 1/R$ , the obtained transconductance may be restricted to small values. Alternatively, using a  $g_{\rm m}\gg 1/R$  is typically not a viable option in power constrained designs.

#### 4 Noise in Solid-State Circuits

In general, there are several noise contributors in solid–state circuits. For transistors, they include thermal noise generated in the resistive channel, usually caused by the random collisions of carriers with the lattice, flicker noise generated by the surface traps between the silicon and the gate oxide and shot noise related to the junction diodes, caused by the random emission of electrons or photons, or the random passage of carriers across potential barriers [12].

Both the channel thermal noise and the junction shot noise have a white noise spectrum, in contrast to the flicker noise, which has a  $1/f^{\alpha}$  spectrum, where  $\alpha \approx 1$ . For field–effect transistors in saturation, the channel thermal noise is generally much more significant than the shot noise.

#### 5 Thermal noise

The limiting noise mechanism in field-effect transistors is in many applications thermal noise from the conducting channel. Thermal noise arises from the random thermal motion of the carriers in addition to its drift in the field. A MOSFET has an inverse resistive channel between the drain and the source, where the gate voltage forms with minority carriers in the channel. In the case when the drain source voltage  $V_{\rm ds}=0$  V, the noise corresponds to thermal noise of the drain conductance, i.e. the channel can be treated as a homogeneous resistor with associated thermal noise. The noise in the channel is then

$$i_{\rm n}^2(f) = 4kTg_0,$$

(2.7)

Here,  $g_0$  is the channel conductance at zero drain—source voltage. This expression is also valid when the transistor is operating in the linear area with resistive characteristics, by replacing  $g_0$  with the actual drain—source conductance,  $g_{\rm ds}$ . The temperature T is given in Kelvin and k is Boltzmann's constant.

For typical biasing conditions,  $V_{\rm ds}$  is not close to zero, which results in noise characteristics different from that of a homogeneous resistor. Taking the body effect into account, the thermal noise current can be found as

$$i_{\rm n}^2(f) = 4\gamma k T g_{\rm m},\tag{2.8}$$

where  $g_{\rm m}$  is the transconductance of the transistor. The factor  $\gamma$  is a complex function of transistor parameters and biasing conditions. Without taking short channel effects, such as channel length modulation and mobility degradation into account it typically has a value of between 2/3 and 1 [12], [13]. It is worth mentioning that (2.8) has limited validity and cannot be used when the transistor is operating in the triode region, which is a limitation in applications such as MOSFET-C and  $G_{\rm m}$ -C filters [14], [15].

On the other hand, using (2.7) and multiplying with  $\gamma$  results in a model that works well for long channel devices. However, it is not very accurate for short channel devices, especially in saturation, which is the usual region of operation for MOSFETs in analog integrated circuits.

A more accurate noise model is therefore required for robust simulations of high performance analog circuits. It has been shown that the noise due to thermal fluctuation in the transistor channel can be expressed as [16]

$$i_{\rm n}^2(f) = 4\gamma kT \frac{\mu_{\rm eff}}{L_{\rm eff}^2} Q_{\rm N}.$$

(2.9)

Here,  $Q_{\rm N}$  is the total channel inversion charge and  $\mu_{\rm eff}$  is included to take mobility degradation into account, while  $L_{\rm eff}$  is the effective electrical channel length of the device given by  $L_{\rm eff} = L - \Delta L$ . L is the channel length between the drain and the source, channel length minus drain and source lateral diffusions, and  $\Delta L$  is the reduction in the electrical channel length due to the extension of the drain depletion region into the channel when  $V_{\rm ds} > V_{\rm dsat}$ .

Hence, it is clear from (2.9) that channel length modulation will result in an increase in the thermal noise as the effective electrical length becomes smaller and bias-dependent. Again, this can also be modeled in (2.8) by using a larger value for  $\gamma$ .

#### 6 Shot Noise

When the transistor is operating in the subthreshold region, shot noise usually dominates over thermal noise. Shot noise was first studied using vacuum—tube diodes [17], but also occurs in pn junctions. This noise is present because the dc bias current is not continuous and smooth, but instead is a result of pulses of current caused by the individual flow of carriers (electrons and holes). As such, shot noise is dependent on the dc bias current. The shot noise drain current can be found as [18]

$$i_{\rm n}^2(f) = 2qI_{\rm ds}$$

(2.10)

where q is the electron charge and  $I_{ds}$  is the net drain current. In the subthreshold region, the drain current is dominated by diffusion mechanism, thus the shot noise in (2.10) can be rewritten as [19]

$$i_{\rm n}^2(f) = 2kT\nu g_{\rm m},$$

(2.11)

where  $\nu = (g_{\rm m} + g_{\rm mb})/g_{\rm m} \approx 1.5$ . Therefore, the shot noise in a subthreshold MOS transistor can be comparable to the thermal noise in a standard superthreshold design, when both transistors have identical  $g_{\rm m}$  values.

#### 7 Flicker Noise

Low frequency noise is normally dominated by flicker noise in MOSFETs, and can in result in reduced sensitivity in many low frequency applications. It is now widely believed that 1/f noise in a MOSFET is due to traps in the gate oxide [20], [21].

As flicker noise is inversely proportional to the frequency, it becomes a dominating noise source at low frequencies. The flicker noise is usually described by its corner frequency, which is defined as the frequency where the flicker noise equals the channel thermal noise. For many analog circuits it is desirable to use large—sized transistors so that their corner frequencies are lower than the signal band.

The 1/f gate-referred noise voltage can be found as

$$v_{\rm n}^2(f) = \frac{K_{\rm f}}{WLC_{\rm ox}^2 f^{\alpha}},\tag{2.12}$$

where  $K_{\rm f}$  is a process and bias dependent parameter and  $\alpha$  is a correction factor. The correction factor  $\alpha$  is included to adjust for deviations from a 1/f line. Depending on technology node and transistor area, flicker noise can contribute significantly to the total noise, even in the frequency band of interest for piezoelectric transducers, which stretches from 3.5 MHz to about 10 MHz.

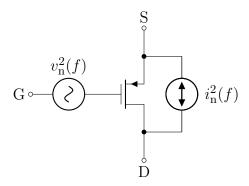

A p-channel transistor model is shown in Figure 2.3, where channel thermal noise and flicker noise is included.

Figure 2.3: A p-channel transistor with noise sources.

If the transistor is operating above subthreshold, the white noise generator  $i_n^2(f)$  is modeling the thermal noise in the transistor. On the other hand, if the transistor is operating in subthreshold,  $i_n^2(f)$  represents the shot noise, which is the resulting dominating white noise source.

## Chapter 3

## Ultrasound Front-End Electronics

This chapter presents an overview of front—end electronics for medical ultrasound imaging, with emphasis on the low noise amplifier and implementation of variable gain, typically referred to as time gain compensation (TGC). Furthermore, this chapter will try to show the trade—offs for ultrasound front—end circuits by starting from a high—level system overview, followed by a more detailed description of how ultrasound systems work. Clearly, some system level understanding is necessary to fully appreciate the desired front—end integrated circuit (IC) function and performance.

### 1 Systems Overview

In ultrasound front—ends, as in many other high quality receivers, the analog signal processing components are key in determining the overall performance of the system; once noise and distortion have been introduced to the input signal it is essentially impossible to compensate for the effect of them.

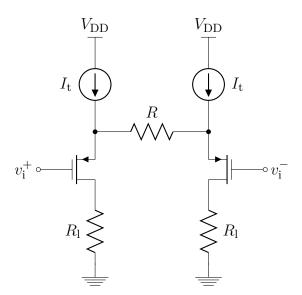

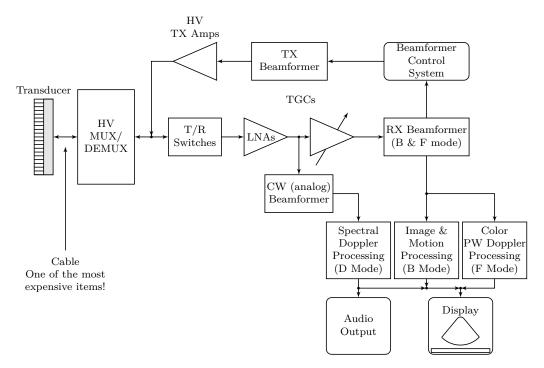

Figure 3.1 shows a simplified diagram of an ultrasound system. In most systems the transducer element is connected to the end of a relatively long cable of about 2 m. In traditional ultrasound, this cable has from a minimum of 48 and up to 256 microcoaxial cables, and is usually one of the most expensive parts of the system. For 3–D ultrasound, the number of channels increases dramatically, and the number of cables can typically not be correspondingly large. In traditional systems the transducer elements directly drive the cable, which can result in significant signal loss due to the loading of the cable capacitance on the transducer elements. Unfortunately, this in turn demands that the receiver noise figure (NF) is lower by the amount of the cable loss. The loss is typically on the order of 1–3 dB depending on transducer and operating frequency. In most systems multiple probe heads can be connected to the system, this allows the operator to select the appropriate transducer for optimal imaging. The heads are selected via high voltage relays; these relays introduce a large parasitic capacitance in addition to the cable.

A high voltage mux/demux is used in some arrays to reduce the complexity of transmit and receive hardware at the expense of flexibility. The most flexible systems are phased array digital beamforming systems where all transducer elements can be individually phase and amplitude controlled. These also tend to be the most

Figure 3.1: Receiver system for ultrasound diagnostics.

expensive systems due to the need for full electronic control of all channels.

On the transmit side the Tx beamformer determines the delay pattern and pulse train that set the desired transmit focal point. The outputs of the beamformer are then amplified by high voltage transmit amplifiers that drive the transducers. These amplifiers might be controlled by DACs to shape the transmit pulses for better energy delivery to the transducer elements. Typically multiple transmit focal regions (zones) are used, i.e. the field to be imaged is divided up by focusing the transmit energy at progressively deeper points in the body. The main reason for doing this is to increase the transmit energy for points that are deeper in the body because the signal is heavily attenuated as it travels into the body.

On the receive side there is a transmit/receive switch, generally a diode bridge, which blocks the high transmit voltage pulses, followed by a low noise amplifier and variable gain amplifiers which implement the time gain compensation and sometimes also apodization functions; spatial windowing to reduce sidelobes in beam. TGC is under operator control and used to maintain image uniformity. After amplification, beamforming is performed which can be implemented in analog (ABF) or digital (DBF) form. Digital beamforming is usually preferred in modern systems except for continuous wave (CW) Doppler processing whose dynamic range is mostly too large to be processed through the same channel as the image. Finally, the Rx beams are processed to show either a gray scale image, color flow overlay on the 2–D image, and/or a Doppler output.

#### 2 Practical Front-End Circuit Considerations

In order to achieve an optimal transducer interface it is necessary to discuss the type of transducers first. Most relevant for this application is the 2–D array transducer. On the other hand, the designed amplifier is versatile enough to be with most transducer array types.

Linear Array: The shape of the transducer is determining the image shape. For example, if the array is convex, then the image generated will be a sector just like in a phased array.

Phased Array: The main advantages of phased arrays are full electronic steering of the beam and small size. This makes it the predominant transducer in cardiac imaging since a small transducer probe is required to image in between the ribs. The sector format is the optimal solution in cardiac imaging since the heart is far away from the surface and the beams all bundle near the skin, which makes them fit easily between the ribs. However, as pointed out earlier, the linear and phased array technology can be mixed and used to generate compound linear scans.

2-D Array: Theoretically the most versatile transducer since no mechanical motion of the transducer is required to scan a volume if a phased array approach is used. The biggest drawback of the 2–D array is that the complexity is proportional to  $N^2$  compared to a linear array with N elements. Some systems use mechanical motion to generate a volumetric image or use 1.25–D or 1.5–D arrays; these sub–2D electronic arrays reduce complexity by restricting beam steering to only the lateral plane. Another major challenge is also the need for much larger cables to access the additional elements. The cable is one of the most expensive items in an ultrasound system, and they become very stiff and unwieldy for 256 and more micro–coax cables. Because of this, high voltage multiplexers could be used in the transducer handle to reduce the number of cables.

Annular Array: This type of array allows for 2–D focusing, but no beam steering. With this type of array it is possible to focus both in the lateral and elevation plane and produce a circular symmetrical beam. The focal point is determined, just like in the phased or linear array, by the delay pattern to the circular elements. As already mentioned above under 2–D arrays, a 1.25–D or 1.5–D array can be built which allows 2–D focusing but only 1–D beam steering. Full explanation of this technology is, however, beyond the scope of this thesis.

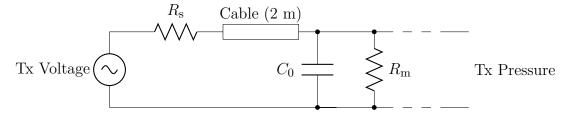

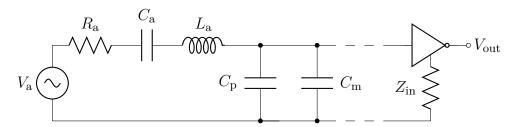

Figure 3.2 [22] shows a simplified equivalent circuit of an ultrasound front—end at series resonance of the transducer element. Figure 3.2 represents the electrical equivalent of the transmitter. A high voltage pulse is generated on the left side by a source with  $50\,\Omega$  source impedance. This pulse is typically transmitted to the transducer element via a few meter micro—coaxial cable. A capacitor and resistor represent the electrical equivalent for the transducer. The resistor,  $R_{\rm m}$ , is the electrical equivalent of the transducer plus body resistance. This resistor is real

Figure 3.2: Simplified equivalent circuit of ultrasound transmitter.

Figure 3.3: Simplified equivalent circuit of ultrasound receiver.

and therefore noisy; ideally this resistor should limit the noise performance in an ultrasound system. During transmit, the transducer element converts the electrical energy into acoustic pressure. Figure 3.3 represents the electrical equivalent of the receiver. Acoustic pressure is converted into electrical signals by the transducer.  $C_{\rm cable}$  loads the transducer which normally is tuned out with an inductor, but since this is a narrow band solution and the ultrasound signals are broadband bandpass signals, a resistor is needed to de–Q the tuning resonator formed by  $C_{\rm cable}$  and the inductor. This can done with a resistive input preamplifier to minimize the degradation in receiver noise figure (NF), as using a shunt termination at the input of the low noise amplifier will result in suboptimal noise performance. However, if the cable capacitance does not need to be tuned out then it is best to not set the input resistance of the low noise amplifier as this tends to degrade the noise performance.

#### 3 Transducer Elements

Transducer impedances can vary from less than  $50\,\Omega$  to  $32\,\mathrm{k}\Omega$  for single element and 2–D transducers respectively. Single element transducers has more latitude in designing the transducer, this allows for customized impedances. In array transducers spacing between the elements is important to minimize grating lobes, therefore the spacing needs to be less than  $\lambda/2$ , i.e. 250 µm at 3 MHz [2]. In addition, ultrasound is a coherent imaging modality; therefore optical artifacts like grating lobes due to diffraction are present. Grating lobes are a problem as they generate gain away from the main beam; if a strong undesired signal is coming along the direction of the grating lobe it could mask a weak signal along the main lobe. The main effects are ghost images and reduced SNR in the main image. The lateral size restriction makes it more difficult to design low impedance transducers; this problem gets compounded in 2–D arrays due to the size restriction in the elevation

plane in addition to the lateral plane. Lastly, as the transducer frequency increases, the wavelength and consequently the area decrease, which results in an increase in element impedance (reduction in capacitance; increase in resistance).

Increased transducer element impedances have the strong disadvantage that it becomes ever more difficult to drive the cable directly. I.e., a typical 2 m cable might have a capacitance of 200 pF, while a transducer element could have capacitance on the order of 5 pF. This makes for a large capacitive attenuator; there are only a few possible solutions: (1) try to reduce the element impedance; (2) integrate parts of the front—end in the transducer handle; (3) use a more sensitive LNA in the system. Solution (1) is difficult to achieve for 2–D transducer arrays. The usefulness of (3) is also limited as the noise factor of any LNA is always larger than 0 dB. Solution (2) would be ideal, but it brings with it many problems like: how to protect the front—end amplifiers from the high voltage transmit pulses. Due to health regulations, the temperature of the transducer probe is strictly limited, which makes for a very limited power consumption, especially for 2–D arrays where the channel count can be very high. Also, the small transducer dimensions may result in difficult area constraints.

#### 4 Variable Gain

Automatic gain control (AGC) circuits are most often used in audio and video mixed—signal ICs in order to maximize the dynamic range of the overall system. The specifications for the linearity of the analog variable—gain amplifier (VGA) forming the core of these circuits are generally very high, to prevent limiting of the overall harmonic distortion by the AGC itself. In ultrasound applications, variable gain is typically used to compensate for the increased loss as the wave propagates through tissue. Received signals arising from increasing depth, or increasing time, suffer more attenuation, and as a result the signal amplitude rapidly diminishes. This can partially be compensated for by increasing the gain with time. This technique, also known as swept gain or time—gain compensation (TGC), can result in dramatic improvements in the image quality [23].

The time gain compensation amplifier is a crucial link in the ultrasound signal path. It must have the ability to amplify signals ranging from a few microvolts to several millivolts up to one or two volts for the ADC. This gain will be exponentially increased along each transmit/receive sweep line. At the near end of the wedge, the gain will be very low. It will have to process the return signal right after the high voltage ceramic excitation pulse. As time after the excitation pulse passes, the gain will be swept into very high levels. This must be done while maintaining very low noise to avoid masking low level signal coming from deep within the body.

### 5 Dynamic Range

In the front—end circuitry, the noise floor of the LNA determines how weak a signal can be received. But at the same time—especially during CW Doppler signal processing—the LNA must also be able to handle very large signals. So it is crucial

to maximize the dynamic range of the LNA. In general, it is extremely difficult to implement any filtering before the LNA due to noise constraints.

CW Doppler has the largest dynamic range of all signals in an ultrasound system—during CW, a sine wave is transmitted continuously with half of the transducer array, while the other half is receiving. There is a strong tendency for the Tx signal to leak into the Rx side; and there are also strong reflections coming from stationary body parts that are close to the surface. This tends to interfere with examination of, for example, blood flow in a vein deep in the body with concomitant very weak Doppler signals.

At the current state of the art, CW Doppler signals cannot be processed through the main imaging (B-mode) and PW Doppler (F-mode) path in a digital beamforming (DBF) system. As the ABF has larger dynamic range, it has to be used for continuous wave Doppler processing. Naturally, the goal in digital beamforming ultrasound is for all modes to be processed through the digital beamforming chain at realistic cost, and there is a great deal of ongoing research as to how to get there.

### 6 Power Consumption

Since ultrasound systems require many channels, power consumption of all the frontend components—from T/R switch, through LNA, VGA, and ADC, to the digital circuitry of the beamformer—is a very critical specification. As has been pointed out above, there will always be a push to increase the front-end dynamic range in order to arrive at eventual integration of all ultrasound modes into one beamformer—a tendency that will lead towards increasing the power in the system. However, there is a corresponding need to make the ultrasound systems forever smaller—with a tendency towards reducing power. Power in digital circuits usually decreases with supply voltage; but this is not necessarily true for analog and mixed signal circuitry. Furthermore, taking into account the fact that reduced analog «headroom» tends to reduce dynamic range, there will be a limit to how low the supply voltage can go and still achieve a desired dynamic range.

## Chapter 4

## In-Probe Analog Front-End

This chapter motivates the need of integrating parts of the front—end in the probe handle, especially in terms of placing the analog to digital converter as close to the transducer as possible. Unfortunately, the large dynamic range requirement inherent in most ultrasound modalities, especially continuous wave doppler processing, makes for a very power hungry ADC specification. By compressing the dynamic range using a variable gain amplifier, the requirement for the ADC can be relaxed. In addition, the front—end amplifier can match the single—ended transducer to a differential ADC by employing a single—ended to fully balanced amplifier topology. Due to the high switching activity in the transducer probe, with a corresponding level of switching noise, the need for a fully balanced ADC architecture is present even for 7/8 bits of accuracy.

### 1 Analog versus Digital Power Consumption

For 3–D ultrasound systems with several thousand channels and a total power budget in the milliwatt region, the available power per channel can be as little as a few tens of micro watt. Hence, for in–probe electronics, low power consumption is the first constraint, for which speed and dynamic range have to be sacrificed for. Although integrating the analog front–end in the probe handle can lead to improved image quality and flexibility, it is still necessary to maintain a certain performance in terms of bandwidth and dynamic range, but with stringent requirements on low power. It is therefore relevant to investigate the fundamental lower limits and how they can be reached.

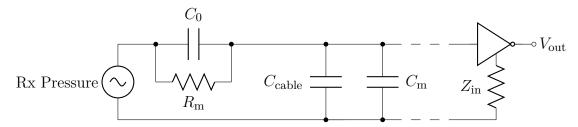

In analog circuits, the absolute limit comes from the need to maintain the energy of the signal much larger than the thermal energy, to achieve the required signal to noise ratio S/N. This condition can be expressed as a minimum power per functional pole [24]

$$P_{\min} = 8kT(S/N)f,\tag{4.1}$$

where f is the signal frequency and S/N is the signal—to—noise ratio. Clearly, this fundamental limit does not depend on technology. It can be reached in a simple, passive RC filter, while the best existing active filters are still a few orders of

magnitude above. Also, it applies to amplifier stages with an additional margin proportional to their voltage gain. Obviously, this limit is steep since it corresponds to a 10-fold increase of power consumption for each 10 dB increase in signal-to-noise-ratio.

In digital systems, each elementary operation requires a certain number m of binary–gate transition cycles, each of which dissipates an amount of energy  $E_{\rm tr}$ . The number m of transitions is only proportional to some power of the number of bits  $N_{\rm bit}$ , and therefore power consumption is only weakly dependent on signal–to–noise ratio. In fact, the power consumption is essentially logarithmically dependent on signal–to–noise ratio for digital circuits, as can be seen in Figure 4.1 [25].

Figure 4.1: Analog and digital power consumption versus signal—to—noise ratio.

Comparison with analog power consumption is obtained by estimating the number of gate transitions required to compute each period of the signal, for example  $m = 50N_{\rm bit}^2$ . Immunity to thermal noise imposes an absolute minimum energy per transition  $E_{\rm tnn}$  estimated at 8kT, which provides the absolute minimum power limit.

From Figure 4.1 it is clear that for 10 to 12 bit accuracy after beamforming, digital signal processing can be done at a substantially lower power consumption, especially for digital circuits that approaches the fundamental lower limits. Also, increasing the number of bits after summation in the beamforming can be done quite easily in the digital domain.

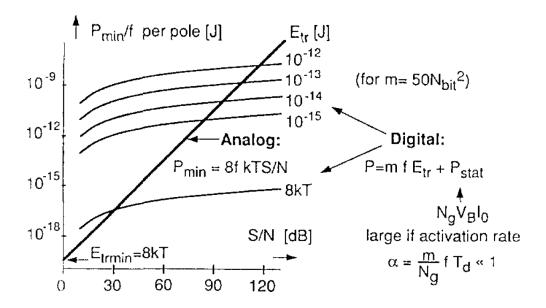

### 2 Digital Beamforming ASICs

In the pursuit of even more flexible ultrasound systems, there is an ongoing need for integrating as much of the electronics, from the low noise amplifier to the ADC into the transducer probe. Digital beamforming can then be partially done in the frontend as well as in the main unit, which holds the promise of increasing sensitivity,

as the increase in signal-to-noise ratio in digital beamforming systems tends to be better than in corresponding analog beamforming systems. Figure 4.2 shows a

Figure 4.2: Digital Beamforming System.

basic block diagram of a digital beamforming system [26]. Note that a variable gain amplifier is typically needed in most implementations to reduce the dynamic range required for the ADC. In fact, doing some analog signal processing to compress the dynamic range before the A/D converter can relax the requirement significantly for the ADC, with a corresponding reduction in power consumption. For instance, increasing the resolution for a thermal noise limited ADC by 1 bit of resolution would require at least quadruple the power consumption. Clearly, for analog to digital converters and other analog building blocks, dynamic range is very expensive in terms of power consumption.

The main difference between an analog and digital beamforming system are the way the beamforming is done, both require perfect channel—to—channel matching. In analog beamforming, an analog delay line and summation is used, while in digital beamforming the signal is sampled as close to the transducer elements as possible and then the signals are delayed and summed digitally. In analog and digital beamforming ultrasound systems, the received pulses from a particular focal point are stored for each channel and then lined up and coherently summed; this provides spatial processing gain because the noise of the channels are uncorrelated. Note that in an analog beamforming imaging system, only one very high resolution and high speed ADC is needed, while in a digital beamforming system many high speed and high resolution analog to digital converters are needed. Sometimes a logarithmic amplifier is used in the analog beamforming systems to compress the dynamic range before the analog to digital converter.

Digital beamforming has the principle advantage that once data is acquired, digital storage and summing is ideal, i.e. in the digital domain the channel—to—channel matching is perfect, while analog delay lines tend to be poorly matched. This reduces the spatial processing gain, as the signal is not ideally, coherently added. The number of delay taps in analog delay tends to be limited, which determines the resolution. Therefore, fine adjustment circuitry normally needs to be used. In

contrast, digital memory is cheap, therefore the FIFOs can be very deep and allow for fine delay resolution. Unfortunately, the sampling rate of the analog to digital converter directly influences axial resolution and accuracy of phase delay adjustment channel—to—channel. Ideally, analog to digital converters with above 200 MS/s would be used to get fine delay resolution [27]. However, because it is difficult to get analog to digital converters with low enough power and high enough resolution for those speeds, most systems use digital interpolation in the beamforming ASICs instead.

Digital beamforming also holds the possibility of increasing flexibility, for instance by forming multiple beams by summing data from different locations in the FIFOs. As the digital IC performance continues to improve, even more flexible ultrasound systems can be implemented. Ideally, systems can be differentiated through software only.

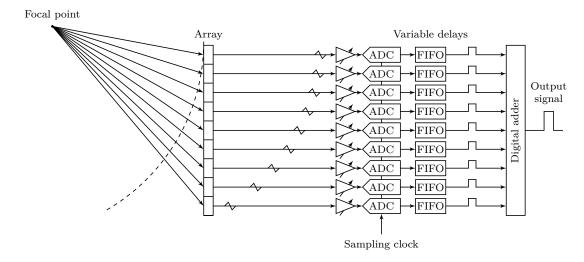

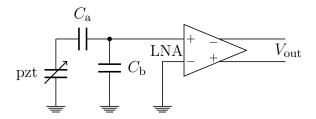

#### 3 Front–End Architecture

As indicated in Figure 4.2, a low noise amplifier is needed in front of the A/D converter. In addition, variable gain is required, either in the low noise amplifier or in a separate stage before the ADC. Also, a single-ended to differential converter is necessary, which usually adds the requirement for some common-mode feedback circuitry in the amplifier. All this should be implemented with as little power and area overhead as possible due to the high number of channels in a relatively small and power constrained probe handle. For this reason, the analog front-end should be as simple as possible, while incorporating all the required functionality.

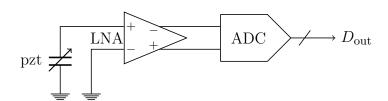

**Figure 4.3:** Proposed analog front–end including LNA and ADC.

A proposed front—end architecture is shown in Figure 4.3. Here, the low noise amplifier acts as a single—ended to differential converter and interfaces the ADC. Unfortunately, implementing a variable gain amplifier compensating for the large attenuation as the ultrasound wave propagates trough tissue would require a gain range of several tens of decibel. This might be difficult to achieve in a micro power front—end such as this. On the other hand, by employing the vast computational power of digital signal processing, time gain compensation can be done at lower cost after the analog to digital converter, or in the main unit where power consumption is not critical.<sup>1</sup> In fact, by means of digital filtering, more advanced time gain compensation can be implemented to improve image quality. Traditionally, time gain compensation is done by increasing gain with

<sup>&</sup>lt;sup>1</sup>Of course, with the introduction of hand held ultrasound systems, this might not be the case.

depth in a frequency independent manner. However, it is well–known that higher frequency components are attenuated more than lower ones, a difference which is progressively increasing with depth. Frequency dependent attenuation implies that echoes from large depths contain essentially the lower frequencies of the transmitted pulse [28], [29]. Clearly, the loss of higher frequency components at higher depths will deteriorate the resolution, as resolution is intimately related to the frequency content of the signal. In fact, by performing time varying and frequency dependent, digital filtering of the received signal, an improvement in image quality can be achieved [30]. However, the improvement in resolution using frequency dependent compensation is most considerable when the signal-to–noise ratio in the received signal is high. Nevertheless, the low noise amplifier still has to limit the dynamic range of the signal before it is sampled by the analog to digital converter.

#### 4 Piezoelectric Transducers

In order to derive accurate front—end specifications it is essential to have some knowledge about the electrical properties of the piezoelectric transducer. Figure 4.4 shows the electrical equivalent of the piezoelectric transducer on receive linearized around it operating point [31].

Figure 4.4: Small-signal equivalent of the piezoelectric transducer.

The left part of the equivalent circuit represents the acoustical part of the piezoelectric transducer with body resistance, while the capacitor  $C_p$  represents the electrical port of the transducer. At the resonance frequency  $f_0 = 7$  MHz, the equivalent circuit reduces to  $R_a$  in parallel with  $C_p$ .

Unfortunately, only these two parameters are known for the piezoelectric transducer at hand. On the other side, knowing the impedance at resonance can be used to derive the noise figure for the front–end amplifier. In addition, the required input impedance of the front–end can be found by using the impedance level of the transducer at resonance. 2–D transducer are typically limited in size, which makes for a large impedance source, i.e. large body resistance and small capacitance. In fact, the body resistance is as high as  $32 \, \mathrm{k}\Omega$  and the intrinsic capacitance is in the region of 450 fF. The principle advantage of having such a large body resistance is the corresponding high noise levels, which lead to relaxed noise requirements for the analog front–end.

### 5 Voltage Sampling

For this low noise amplifier a voltage gain of  $20\,\mathrm{dBis}$  required in order to raise the weak signal from the piezoelectric transducer above the noise floor of the A/D converter. On the other hand, the output voltage of the front–end amplifier should be limited in order to avoid saturation in the ADC.

For optimal power transfer from the source to the amplifier, the source impedance should be matched to the input impedance of the low noise amplifier. However, the received pulses from the transducer elements are voltage signals, and for efficient voltage sampling a very high input impedance results in a favorable voltage division

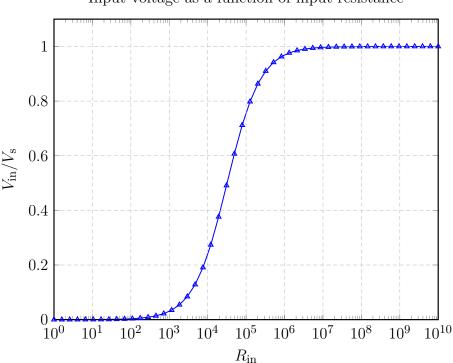

$$V_{\rm in} = V_{\rm s} \cdot \frac{R_{\rm in}}{R_{\rm in} + R_{\rm s}},\tag{4.2}$$

where  $V_s$  is the source signal, sensed by the receiver as  $V_{in}$ . Moreover,  $R_{in}$  is the input resistance of the receiver and  $R_s$  is the source resistance.

This voltage division can be calculated using the given electrical and body resistance of the transducer elements of  $32 \,\mathrm{k}\Omega$ . Clearly, for optimal sensitivity for voltage sampling, the input resistance of the amplifier should be much larger than the source resistance. In addition, the input capacitance of the low noise amplifier should be kept much smaller than the source capacitance, in order to minimize any addition attenuation of the voltage signal at the input of the low noise amplifier.

Input voltage as a function of input resistance

Figure 4.5: Effect of input resistance, i.e. the real part of  $Z_{\rm in}$ , on the circuit performance.

From Figure 4.5 it is clear that when using voltage sensing, the input resistance of the amplifier must be in the range of several mega ohms in order to be sufficiently high to cause minimum attenuation of the pzt voltage signal at the input of the amplifier. For higher values of the input resistance, the overall transfer function has minimal sensitivity to the input resistance variations. Such a high input resistance is usually obtained by connecting the source to the gate of a mos transistor.

#### 6 Single–Ended to Differential Conversion

The single–ended to fully differential converter is an important building block in many applications, mostly caused by the need to match single–ended sources to processing blocks that features a fully balanced architecture. These fully balanced architectures have many benefits as compared to their single–ended counterparts in terms of lower sensitivity to substrate noise and saturated output levels. The last point is especially important for scaled down technology nodes where the supply voltages are reduced to 1 V and below. The single–ended to differential converter usually has to provide symmetric outputs, high tolerance to input dc–level variations and a wide bandwidth.

Symmetrical single—ended to differential converters are typically based on the differential pair, and in the simplest case only consists of a simple differential pair driven by a single input, where the second input is ac–grounded [32], [33], [34].

By using this configuration, also known as a single input differential pair, half of the input signal is seen as a common—mode input component. As a result, this topology provides 6 dB lower gain and lower common—mode rejection ratio when compared to the fully differential input case.

Other arrangements exists that can improve the efficiency of the circuit [35], [36], but this comes at the cost of increased complexity and possible stability problems caused by the use of a positive feedback path. In addition, the positive feedback provides a very low common—mode rejection ratio. Similarly, negative feedback can be used to generate the second input [37], thus alleviating some of the potential instability problem.

## Chapter 5

# Circuit Topology

Having reviewed the fundamental properties of ultrasound imaging and the transducer source itself, this chapter focus on the chosen amplifier topology. The proposed front—end architecture imposes challenges on the low noise amplifier, such as maintaining high input resistance as well as implementing a single—ended to differential conversion at a low power consumption and input referred noise voltage. In addition, the dynamic range requirement is also high, especially for maintaining good linearity even at large input levels. The chosen amplifier is therefore based on the differential pair with additional circuitry to maintain good linearity without investing too much power.

#### 1 Linearized Transconductor

As mentioned in Chapter 2, a simple way of linearizing a differential pair is by means of resistive degeneration. By using a degeneration resistance at the source of the differential pair, the bias current can be made relatively independent on the input signal.

Figure 5.1: Differential pair using resistive degeneration.

If the transconductance of the input transistor is  $g_{\rm m}$ , the transconductance by using resistive source degeneration will be given by

$$G_{\rm m} = \frac{g_{\rm m}}{1 + g_{\rm m}R},\tag{5.1}$$

where the degeneration resistor has a value of R. Clearly, the source degeneration resistance results in an internal, negative feedback loop that linearizes the transconductance of the amplifier. If the feedback factor,  $g_{\rm m}R$ , is much larger than unity, the overall transconductance is given by the 1/R, an input independent factor. By having  $g_{\rm m}R\gg 1$ , only a small portion of the input voltage lies across the active devices, implying reduced signal swing and distortion. The requirement  $g_{\rm m}\gg 1/R$  can usually be satisfied with large transistors widths and/or bias currents. In many practical application however, this may be very undesirable in terms of area and current consumption.

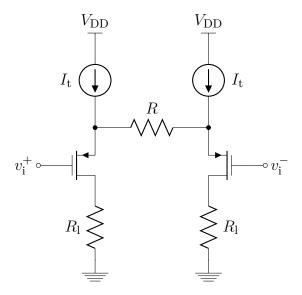

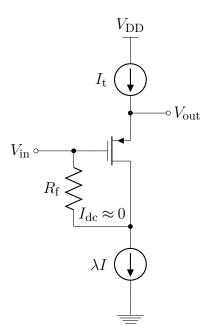

Figure 5.2: P-channel input transistor with composite device.

An alternative way is to boost the  $g_{\rm m}$  of the p-channel device by using a compound device as shown in Figure 5.2 [4]. This compound configuration is often used in the design of many bipolar output stages instead of a single p-n-p transistor with poor performance. In this case,  $M_1$  acts like a floating voltage source. Its  $g_{\rm m}$  is no longer an important factor in the distortion performance of the amplifier. However, any threshold voltage shift due to the body effect becomes part of the input signal. For this reason, p-channel input transistors were chosen for the n-well process, in which the body effect can be minimized by connecting the source of each input transistor to its own well. Also, p-channel devices tend to be less noisy than n-channel devices, especially when flicker noise is concerned. To complement the design, n-channel current mirrors can be used that have better frequency response than p-channel current mirrors, which would have been used with n-channel input devices.

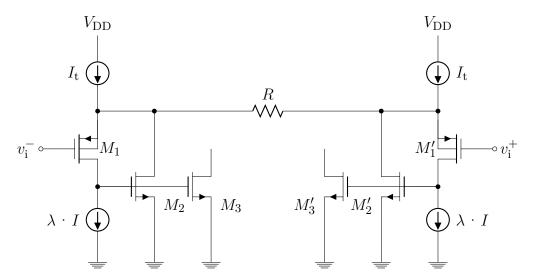

A basic transconductor with the compound devices and biasing is shown in Figure 5.3. The p-channel transistors serve as voltage followers buffering the input voltage across the resistor while the four constant current sources force any change in the resistor current to be directly reflected to the drain currents of  $M_{2a}$  and  $M_{2b}$ , which is mirrored to the output by  $M_3$  and  $M'_3$ . The local feedback loop of  $M_1$  and  $M_2$ , therefore creates an input device with a high effective  $g_{\rm m}$ . Therefore, the effective  $G_{\rm m}$  of the input transconductor circuit is set by the resistor, R, which provides degeneration between the two input devices and by the mirroring ratio,

Figure 5.3: Basic transconductor cell.

B, between  $M_2$  and  $M_3$ . This not only provides a fixed transconductance that is largely insensitive to process variation, but it also linearizes the transconductance of the circuit.

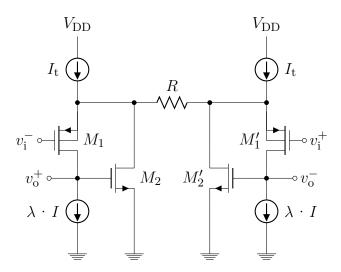

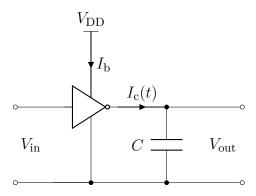

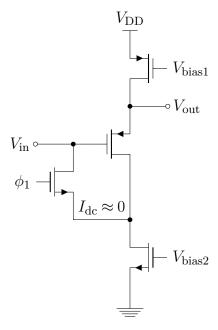

## 2 Simplified Amplifier Topology

The usefulness of analytical analysis of the amplifier is limited by the complexity of the resulting equations. In addition, using simple circuit topologies increases the possibility of finding useful analytical expressions. In order to simplify complexity and design effort, only the core of the transconductor is designed. The output stage consisting of the current mirror of  $M_3$  can be designed as a separate second stage. In fact, having a large gain in the first stage, will result in a neglectable noise contribution from the output stage. For the first stage, the output voltage can be found at the gate of  $M_2$ . The simplified amplifier topology is shown in Figure 5.4. The loading of  $M_3$  on  $M_2$  is modeled by a load capacitance of 25 fF.

Optimizing the core of the amplifier also constitutes the major design effort. As long as  $M_2$  has been designed, the output transistor determines out current by a current mirror of B. The geometry of  $M_3$  is therefore given, and the current mirror gain is realized using an appropriate M factor. Depending on the type of output that is desired, the output stage can simply consist of  $M_3$  if a current output is required, or by adding a resistive load if a voltage output is necessary.

Figure 5.4: Simplified Low Noise Amplifier Topology

## 3 Small-Signal Analysis

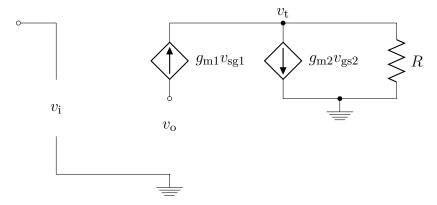

In order to fully appreciate the functionality of the amplifier topology, consider the small—signal equivalent circuit of the amplifier shown in Figure 5.3. To simplify the analysis, only the half—circuit equivalent is used for the calculations. Also, the transistors are modeled as ideal transconductors.

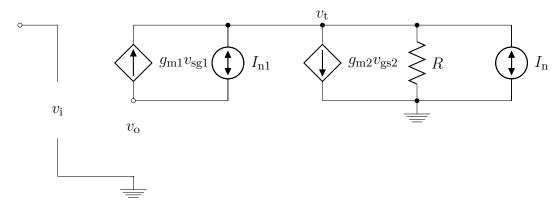

Figure 5.5: Low frequency small-signal equivalent circuit.

The ideal current source, forces any current change in the resistor to be reflected to the drain of the feedback transistor  $M_2$ . Summing all the currents at  $v_t$  yields

$$g_{\rm m}(v_{\rm t} - v_{\rm i}) + g_{\rm m2} \cdot v_{\rm o} + 2G \cdot v_{\rm t} = 0$$

(5.2)

Since the small-signal current through  $M_1$  is forced to be zero, the input voltage is buffered over the degeneration resistor, and  $v_i = v_t$ , where  $v_t$  is the node voltage indicated in Figure 5.5. The current through R is forced through  $M_2$ , so

$$g_{\rm m2} \cdot v_{\rm o} + 2G \cdot v_{\rm i} = 0$$

(5.3)

where, G = 1/R. Solving (5.3) yields the voltage gain A

$$A \triangleq \frac{v_{\rm o}}{v_{\rm i}} = -\frac{2G}{g_{\rm m2}}.\tag{5.4}$$

Unfortunately, the gain in (5.4) is not well–defined across process corners and temperature variations; however, this is also the case for a range of other analog circuits, such as active RC–filters and integrators used in continuous–time  $\Delta\Sigma$ –modulators. Also, for the complete amplifier, the voltage gain will be given by the ratio of two resistors, which can be matched quite well in CMOS.

#### 4 Source–Follower

In the previous analysis using ideal current sources, the input transistors will behave as ideal source-followers. However, when including non-ideal current sources and resistive loading through the degeneration resistor, the gain in the voltage buffer will decrease from the desired value of one. For the source follower  $M_1$  with output resistance  $r_{\rm ds1}$ , transconductance  $g_{\rm m1}$  and a resistive load of R/2, the voltage gain is given by

$$A_1 \triangleq \frac{v_{\rm t}}{v_{\rm i}} = \frac{g_{\rm m1} \cdot r_{\rm ds1}}{1 + (g_{\rm m1} + g_{\rm mb1}) \cdot r_{\rm ds1} + 2 \cdot r_{\rm ds1}/R},\tag{5.5}$$

when taking the body effect into account. This reduces to the well–known expression when the load and output resistance approaches infinity

$$\lim_{R, r_{\rm ds1} \to \infty} A_1 = \frac{g_{\rm m1}}{g_{\rm m1} + g_{\rm mb1}},\tag{5.6}$$

which is always less than unity. As previously mentioned, the body effect can be minimized by using p-channel input transistors, where the source can be connected to its own well. Not only will this lead to improved linearity, but also reduced attenuation in the voltage buffer. As can be seen from (5.6), the voltage buffer has a gain less than unity, regardless of output resistance and loading conditions as long as the body effect must be taken into account. On the other hand, this drawback is suppressed when minimizing the body effect. If the body effect is sufficiently small, equation (5.5) can be rewritten as

$$A_1' = \frac{g_{\text{m1}} \cdot r_{\text{ds1}}}{1 + g_{\text{m1}} \cdot r_{\text{ds1}} + 2 \cdot r_{\text{ds1}}/R},\tag{5.7}$$

where typically  $r_{\rm ds1}/R \gg 1$ . Hence, (5.7) can be simplified to

$$\hat{A}_1 = \frac{g_{\rm m1}R}{1 + g_{\rm m1}R},\tag{5.8}$$

which implies that  $g_{\rm m1}R$  should be larger than one by a at least a few times. Although, any loss in the signal path adds directly to the noise figure, some loss in the voltage buffer is acceptable. From (5.8) it is clear that the requirement  $g_{\rm m1}R \gg 1$  is not completely removed when using  $g_{\rm m}$  boosting.

In addition to the direct loss in the signal path, the overall voltage gain suffers additional loss due to the attenuation in the source follower. This can be seen

from (5.2) when  $v_i \neq v_t$ , but instead  $v_t = \hat{A}_1 v_i$ . The overall voltage gain can then be written as

$$\hat{A} = -\frac{2G}{g_{\rm m2}}\hat{A}_1 + \frac{g_{\rm m1}}{g_{\rm m2}}(1 - \hat{A}_1). \tag{5.9}$$

Note the negative contribution from the second term as  $\hat{A}_1$  is less than one. Clearly, the voltage gain in (5.9) suffers additional loss when  $g_{\rm m1} > g_{\rm m2}$ , which is typically the case for low noise applications. In fact, for optimal noise performance  $g_{\rm m1}$  should be larger than  $g_{\rm m2}$  by a few times, leading to a compromise between voltage gain and low noise. On the other hand, any loss from the input signal to the degeneration resistor results in reduced small–signal currents in  $M_2$ , which typically leads to relaxed linearity requirements.

#### 5 Noise analysis

One of the key factors in designing power efficient analog circuits is understanding noise. For most low noise amplifies, noise factor is one of the most significant performance parameters, making a thorough noise analysis is vitally important for a successful design. It is therefore of interest to identify the most important noise contributors of this amplifier topology, and be able extract design equations for low noise.

## 6 Previously Published Noise Analysis

Even though this transconductor cell has received some attention in the literature, only a simplified noise analysis is included in [5], where the noise contribution from the input transistors are neglected. This is a good approximation if  $g_{\rm m1} \gg 1/R$ , a constraint that is not necessarily satisfied when using  $g_{\rm m}$  boosting. Nevertheless, the input referred noise voltage is found as [5]

$$v_{\rm n}^2 = 8kT\gamma(g_{\rm mbp} + g_{\rm mbn} + g_{\rm m2})R^2 + 4kTR,$$

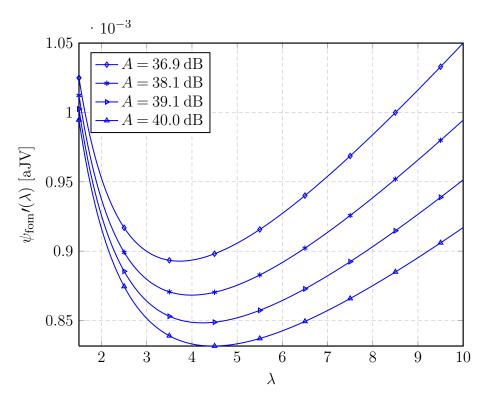

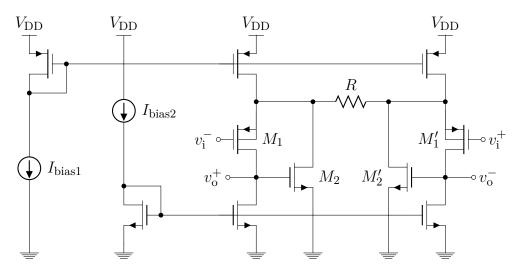

(5.10)