# Self Reconfiguration of Clock Networks on FPGA

Methodology for partial reconfiguration of synchronous modules at run-time

Sindre Hansen

Master of Science in Electronics Submission date: June 2011 Supervisor: Kjetil Svarstad, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Description**

With the project as basis, the objectives are:

- To further develop the methodology for clocked, dynamic, reconfigurable modules.

- To integrate the methodology for clocking with the HWOS-methodologies previously developed.

The methods should be tested by implementing a chosen system on an FPGA. The results should be compared with published results if such exist.

Assignment given: 17. January 2011 Supervisor: Kjetil Svarstad, IET

#### Summary

In this thesis, methodology for partial self-reconfiguration of synchronous modules has been developed. A simple software-based scheduler has been built for scheduling synchronous modules on the FPGA. The motivation behind this was that partial reconfiguration of synchronous modules at run-time had not been performed earlier in the AHEAD-project. Also, the project report written by the same author as this thesis has shown that a synchronous module can be replaced in a bitfile. However, the project report did not perform this reconfiguration at run-time.

Based on the project report, the problem has been decomposed and simple tests using clocked flip-flop designs have been performed on the FPGA. These tests forms a proof-of-concept for partial self-reconfiguration of synchronous modules on the Virtex-4 FPGA. However, the tests also showed that the reconfiguration time was quite high. It took several seconds to write one partial bitstream to the configuration memory.

Vegard Endresen has previously made a backend module for data transfer between the HWOS and a reconfigurable module. Experiments were performed in this thesis to see if the clocking methodology could be integrated into this backend module. The module could be built with the methodology, but a running solution on the FPGA was not shown.

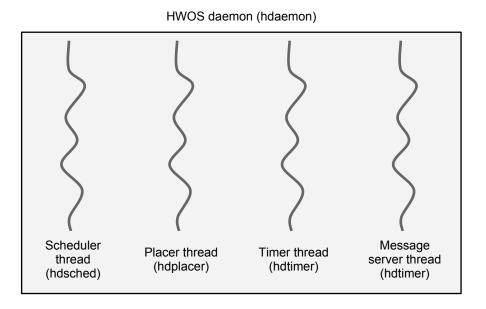

The software part of the HWOS was rewritten from scratch as the previous version was not thoroughly analyzed. A round-robin scheduler using priority queues has been implemented. A test-driven development technique has been used for development, hopefully making the system more robust. The scheduler is a part of a daemon running on the embedded system, where a message server handles requests for new processes and a placer places new tasks on the FPGA. The complete system was initially based on ideas and code developed by Sverre Hamre and Vegard Endresen in previous AHEAD-projects.

# Foreword

This is the final report on my master thesis in the programme option *Design* of *Digital Systems* under the study programme *Electronics* at the Norwegian University of Science and Technology (NTNU). The work has been done during 20 weeks in the spring semester of 2011.

For me personally the work has been challenging, but the learning outcome has been large. It is exciting to walk through all the phases of building an embedded system, from planning and researching to the final implementation. I definitely think this experience will help me as an engineer out in the industry.

The challenges when building a complex system like this are many. It is a lot of work to read up on the existing work in the field, especially since partial self-reconfiguration on FPGA is a rather new concept. The practical solutions may be few and there may not be a "de facto standard" way of doing things. There's not tons of learning books on the subject, but articles and research projects with suggested implementations. Another challenge is working with an embedded system with parts in both hardware and software. In such a complex system, there are many parts that will have to work together and the use of several tools have to be learnt to accomplish the final solution.

I see the learning outcome of this thesis as threefold. Firstly, I have gained a lot of practical experience with the tools and the technology. I have learned a lot on C-programming, automated testing and working with the Xilinx tools. The second is all the new knowledge I've gained on partial self-reconfiguration and how a hardware operative system can be built in practise. The last is how to carry out a quite large project. It is interesting to see how important a good working methodology is (methodology is presented in section 1.2) and how I should relate to work done by others. Likewise important is how I can document and structure my work so *others* can relate to *my work*.

I would like to thank professor Kjetil Svarstad for guidance and help during the semester. I also would like to thank Magnus Namork, who has been writing a master thesis on the Network On Chip-part of the AHEAD-project, for tool-specific discussions.

Trondheim, june 2011 Sindre Hansen

# Acronyms and expressions

#### FPGA

Field Programmable Gate Array. An array of programmable logic designed to be reconfigured several times by the designer or end-user.

#### BRAM

Block Random Access Memory. Small memory blocks integrated on the FPGA.

#### $\mathbf{LUT}$

Lookup-table. In digital logic, a LUT is typically implemented using multiplexers.

#### CLB

Configurable Logic Block. One unit of the programmable logic on the FPGA. Typically has LUTs, multiplexers, flip-flops, latches and more.

#### Slice

The CLB on Xilinx Virtex FPGAs.

#### $\mathbf{FF}$

Flip-flop. One bit storage element (register) on the FPGA. There are typically one or more of these in each CLB.

#### Bitfile

In this thesis, this is typically a file containing a complete or partial configuration for the programmable logic on the FPGA.

#### HWOS

Hardware Operative System. In this thesis, HWOS is a operative system for controlling execution of tasks on an FPGA.

#### AHEAD

Ambient Hardware, Embedded Architectures on Demand.

# Contents

| 1        | Intr | roduct | ion                                                                                                               | 1  |

|----------|------|--------|-------------------------------------------------------------------------------------------------------------------|----|

|          | 1.1  | What   | has been done                                                                                                     | 1  |

|          | 1.2  | Metho  | odology                                                                                                           | 1  |

|          | 1.3  | Contr  | ibution from this thesis                                                                                          | 3  |

|          | 1.4  | Outlir | ne of this report                                                                                                 | 3  |

| <b>2</b> | Rel  | ated w | vork                                                                                                              | 5  |

|          | 2.1  | Work   | done in the AHEAD-project                                                                                         | 5  |

|          |      | 2.1.1  | Sverre Hamre's master thesis (june 2009): Framework for self reconfigurable system on Xilinx FPGA                 | 5  |

|          |      | 2.1.2  | Vegard Endresen's master thesis (june 2010): Hardware-<br>software intercommunication in reconfigurable systems . | 5  |

|          |      | 2.1.3  | Sindre Hansen's project report (december 2010): Self<br>Reconfiguration of Clock Networks on FPGA                 | 6  |

|          | 2.2  | Relate | ed work on partial self-reconfiguration and HWOS                                                                  | 6  |

|          |      | 2.2.1  | Klaus Danne (2004): Memory Management to Support<br>Multitasking on FPGA Based Systems                            | 6  |

| 3        | The  | eory   |                                                                                                                   | 8  |

|          | 3.1  | Develo | opment tools                                                                                                      | 8  |

|          | 3.2  | Base p | platform                                                                                                          | 8  |

|          |      | 3.2.1  | Objective                                                                                                         | 9  |

|          |      | 3.2.2  | The development board                                                                                             | 9  |

|          |      | 3.2.3  | The FPGA                                                                                                          | 10 |

|          |      | 3.2.4  | Base VHDL-design for the Suzaku-V                                                                                 | 11 |

|          |      | 3.2.5  | Internal Configuration Access Port (ICAP)                                                                         | 11 |

|     | 3.2.6   | ATMARK-dist and uClinux-dist                           | 11 |

|-----|---------|--------------------------------------------------------|----|

|     | 3.2.7   | uClibc                                                 | 12 |

| 3.3 | Addres  | ssing the bitstream for Virtex-4                       | 12 |

|     | 3.3.1   | Objective                                              | 12 |

|     | 3.3.2   | Definitions                                            | 13 |

|     | 3.3.3   | Addressing of frames                                   | 13 |

|     | 3.3.4   | The term frame in CLBRead                              | 16 |

|     | 3.3.5   | The term frame in icap_write                           | 16 |

|     | 3.3.6   | The term frame in the documentation from Xilinx        | 16 |

| 3.4 | The ex  | sisting framework for partial self-reconfiguration     | 17 |

|     | 3.4.1   | Objective                                              | 17 |

|     | 3.4.2   | CLBRead                                                | 17 |

|     | 3.4.3   | icap_write                                             | 18 |

|     | 3.4.4   | Bus macros                                             | 19 |

| 3.5 | Synchi  | conous design                                          | 20 |

|     | 3.5.1   | Objective                                              | 20 |

|     | 3.5.2   | Definitions                                            | 20 |

|     | 3.5.3   | Motivation for using synchronous design                | 20 |

|     | 3.5.4   | Problems in asynchronous designs                       | 20 |

|     | 3.5.5   | Timing requirements for a reconfigurable module        | 21 |

| 3.6 | Definin | ng an interface for clock signals                      | 22 |

|     | 3.6.1   | Objective                                              | 22 |

|     | 3.6.2   | Definitions                                            | 22 |

|     | 3.6.3   | Concept                                                | 22 |

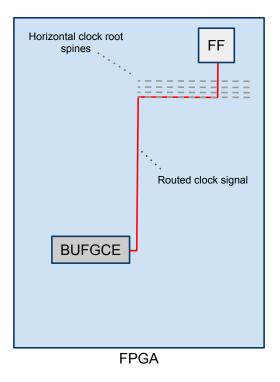

|     | 3.6.4   | Global clock buffer, BUFGCE                            | 24 |

|     | 3.6.5   | Clock root spines                                      | 24 |

|     | 3.6.6   | User Constraints File (UCF)                            | 26 |

|     | 3.6.7   | Directed Routing (DIRT)                                | 26 |

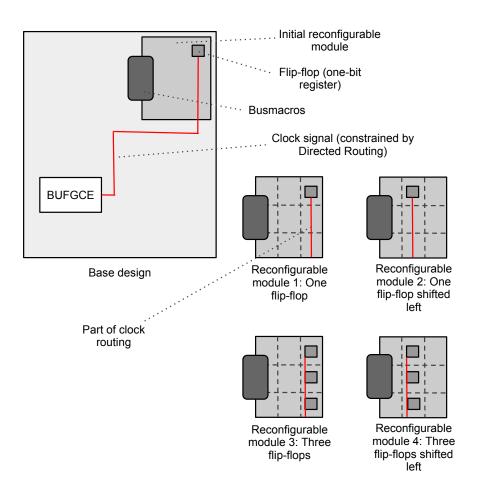

|     | 3.6.8   | Setting up a base design                               | 27 |

|     | 3.6.9   | Setting up a reconfigurable module                     | 27 |

|     | 3.6.10  | Making base design compatible with synchronous modules | 29 |

|   |                                         | 3.6.11                                                                                       | Making a scalable solution                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30                                                                                                                                             |

|---|-----------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.7                                     | Schedu                                                                                       | lling on FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                                                                                                                                             |

|   |                                         | 3.7.1                                                                                        | Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31                                                                                                                                             |

|   |                                         | 3.7.2                                                                                        | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31                                                                                                                                             |

|   |                                         | 3.7.3                                                                                        | Type of scheduling decisions for reconfigurable hardware                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                                                                                                             |

|   |                                         | 3.7.4                                                                                        | Process                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33                                                                                                                                             |

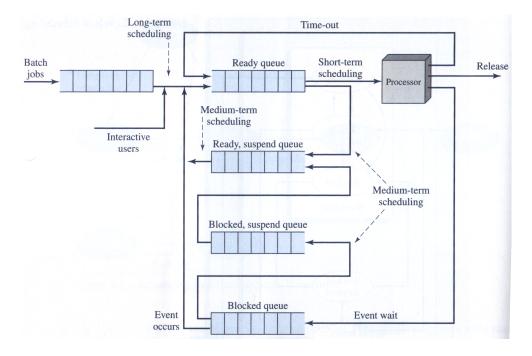

|   |                                         | 3.7.5                                                                                        | Queue structure                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34                                                                                                                                             |

|   |                                         | 3.7.6                                                                                        | Interrupter                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35                                                                                                                                             |

|   |                                         | 3.7.7                                                                                        | Types of scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36                                                                                                                                             |

|   | 3.8                                     | Autom                                                                                        | nated testing                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                                                                                                             |

|   |                                         | 3.8.1                                                                                        | Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                                                                                                                             |

|   |                                         | 3.8.2                                                                                        | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                                                                             |

|   |                                         | 3.8.3                                                                                        | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37                                                                                                                                             |

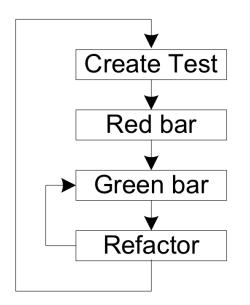

|   |                                         | 3.8.4                                                                                        | Test-driven development (TDD)                                                                                                                                                                                                                                                                                                                                                                                                                                | 38                                                                                                                                             |

|   |                                         | 3.8.5                                                                                        | Check: A unit testing framework for C $\ . \ . \ . \ .$ .                                                                                                                                                                                                                                                                                                                                                                                                    | 39                                                                                                                                             |

|   |                                         |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                |

| 4 | Imn                                     | lemen                                                                                        | tation: Partial reconfiguration of synchronous mod-                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                |

| 4 | -                                       | lemen<br>at rui                                                                              | tation: Partial reconfiguration of synchronous mod-<br>n-time                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                                                                                                             |

| 4 | -                                       | at ru                                                                                        | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                |

| 4 | ules                                    | at rui<br>Object                                                                             | n-time                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                |

| 4 | <b>ules</b><br>4.1                      | <b>at ru</b><br>Object<br>Definit                                                            | n-time                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41                                                                                                                                             |

| 4 | ules<br>4.1<br>4.2                      | at run<br>Object<br>Definit<br>Conce                                                         | n-time<br>tive                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41<br>41<br>42                                                                                                                                 |

| 4 | ules<br>4.1<br>4.2<br>4.3               | at run<br>Object<br>Definit<br>Conce                                                         | <b>n-time</b> Sive                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41<br>41<br>42                                                                                                                                 |

| 4 | ules<br>4.1<br>4.2<br>4.3               | at run<br>Object<br>Definit<br>Conce<br>Requin                                               | n-time<br>tive                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>41</li> <li>41</li> <li>42</li> <li>43</li> </ul>                                                                                     |

| 4 | ules<br>4.1<br>4.2<br>4.3               | at run<br>Object<br>Definit<br>Conce<br>Requin<br>4.4.1<br>4.4.2                             | n-time<br>tive                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ol> <li>41</li> <li>41</li> <li>42</li> <li>43</li> <li>43</li> </ol>                                                                         |

| 4 | ules<br>4.1<br>4.2<br>4.3<br>4.4        | at run<br>Object<br>Definit<br>Conce<br>Requin<br>4.4.1<br>4.4.2                             | <b>n-time</b> tive         tions         pt         cements and design         Setting up the base designs on the FPGA         Building reconfigurable modules in ISE                                                                                                                                                                                                                                                                                        | <ol> <li>41</li> <li>42</li> <li>43</li> <li>43</li> <li>45</li> <li>46</li> </ol>                                                             |

| 4 | ules<br>4.1<br>4.2<br>4.3<br>4.4        | at run<br>Object<br>Definit<br>Conce<br>Requin<br>4.4.1<br>4.4.2<br>Develo                   | <b>n-time</b> tive                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ol> <li>41</li> <li>42</li> <li>43</li> <li>43</li> <li>45</li> <li>46</li> </ol>                                                             |

| 4 | ules<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | at run<br>Object<br>Definit<br>Conce<br>Requin<br>4.4.1<br>4.4.2<br>Develo<br>4.5.1<br>4.5.2 | <b>n-time</b> tive         tions         pt         pt         cements and design         setting up the base designs on the FPGA         Building reconfigurable modules in ISE         opment of methodology through test suites         Analysis of first test suite: Simple flip-flop designs         Analysis of second test suite: Instruction- and data cache                                                                                         | <ol> <li>41</li> <li>41</li> <li>42</li> <li>43</li> <li>43</li> <li>45</li> <li>46</li> <li>46</li> </ol>                                     |

|   | ules<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | at run<br>Object<br>Definit<br>Conce<br>Requin<br>4.4.1<br>4.4.2<br>Develo<br>4.5.1<br>4.5.2 | h-time<br>tive                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>41</li> <li>41</li> <li>42</li> <li>43</li> <li>43</li> <li>45</li> <li>46</li> <li>46</li> <li>46</li> <li>47</li> </ul>             |

|   | ules<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | at run<br>Object<br>Definit<br>Conce<br>Requin<br>4.4.1<br>4.4.2<br>Develo<br>4.5.1<br>4.5.2 | n-time         tive         tions         pt         opt         rements and design         rements and design         Setting up the base designs on the FPGA         Building reconfigurable modules in ISE         opment of methodology through test suites         Analysis of first test suite: Simple flip-flop designs         Analysis of second test suite: Instruction- and data cache backend         backend         tation: Scheduler and HWOS | <ul> <li>41</li> <li>41</li> <li>42</li> <li>43</li> <li>43</li> <li>45</li> <li>46</li> <li>46</li> <li>46</li> <li>47</li> <li>49</li> </ul> |

iv

|   | 5.4                                                                                  | Work     | done by Vegard Endresen                                                                         | 50      |

|---|--------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------|---------|

|   | 5.5                                                                                  | Genera   | al structure of the HWOS                                                                        | 50      |

|   | 5.6                                                                                  | Genera   | al structure of the message server                                                              | 50      |

|   | 5.7                                                                                  | Genera   | al structure of the placer                                                                      | 51      |

|   | 5.8                                                                                  | Genera   | al structure of the timer                                                                       | 51      |

|   | 5.9                                                                                  | Genera   | al structure of the scheduler                                                                   | 51      |

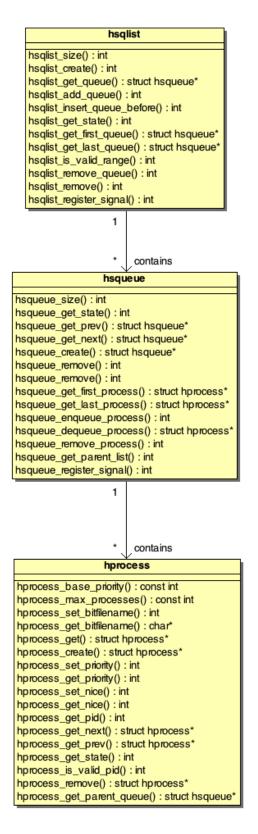

|   | 5.10                                                                                 | List of  | f scheduler queues: hsqlist                                                                     | 52      |

|   | 5.11                                                                                 | Proces   | s structure: hprocess                                                                           | 55      |

|   | 5.12                                                                                 | Schedu   | uler queue structure: hsqueue                                                                   | 55      |

|   | 5.13                                                                                 | Rewrit   | tten version of icap_write: hicap                                                               | 56      |

| 6 | Verification and results: Partial reconfiguration of synchronous modules at run-time |          |                                                                                                 | s<br>57 |

|   | 6.1                                                                                  | Definit  | tions $\ldots$ | 57      |

|   | 6.2                                                                                  | First t  | est suite: Simple flip-flop designs                                                             | 57      |

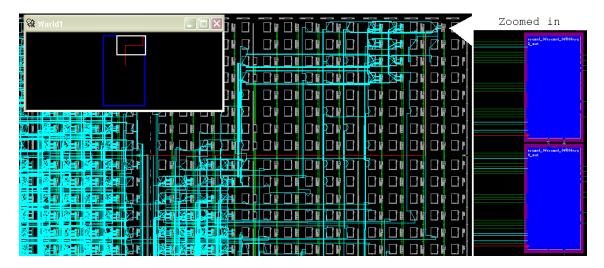

|   |                                                                                      | 6.2.1    | Test case 1: Cut the reconfigurable modules from the base designs                               | 57      |

|   |                                                                                      | 6.2.2    | Test case 2: Build the base design and the reconfigurable module separately                     | 59      |

|   |                                                                                      | 6.2.3    | Test case 3: Build the base design with DIRT                                                    | 60      |

|   | 6.3                                                                                  | Second   | d test suite: Instruction- and data cache backend $\ldots$ .                                    | 62      |

|   |                                                                                      | 6.3.1    | Test case 1: Make the backend compatible with syn-<br>chronous modules                          | 62      |

|   |                                                                                      | 6.3.2    | Test case 2: Make the backend compatible with syn-<br>chronous modules using dummy module       | 63      |

| 7 | Veri                                                                                 | ificatio | on and results: Scheduler                                                                       | 65      |

|   | 7.1                                                                                  | Portab   | pility                                                                                          | 65      |

|   | 7.2                                                                                  | Test st  | trategy                                                                                         | 65      |

|   | 7.3                                                                                  | Descri   | ption of test suites                                                                            | 66      |

|   | 7.4                                                                                  | Test re  | esults                                                                                          | 66      |

|   |                                                                                      | 7.4.1    | The HWOS-daemon                                                                                 | 66      |

|   |                                                                                      | 7.4.2    | The HWOS-library                                                                                | 67      |

|   |                                                                                      |          |                                                                                                 |         |

| 8  | Discussion 68 |                                                                             |     |

|----|---------------|-----------------------------------------------------------------------------|-----|

|    | 8.1           | Partial self-reconfiguration of synchronous modules $\ldots \ldots \ldots$  | 68  |

|    | 8.2           | Scheduler                                                                   | 69  |

| 9  | Con           | clusion                                                                     | 71  |

| 10 | Furt          | cher work                                                                   | 72  |

|    | 10.1          | Better testing of each part of the complete framework                       | 72  |

|    | 10.2          | Further development                                                         | 73  |

|    |               | 10.2.1 Partial self-reconfiguration                                         | 73  |

| Bi | bliog         | raphy                                                                       | 74  |

| A  | Tute          | orial for uClinux                                                           | 77  |

|    | A.1           | Objective                                                                   | 78  |

|    | A.2           | Prerequisites                                                               | 78  |

|    | A.3           | Download and compile ATMARK-dist                                            | 78  |

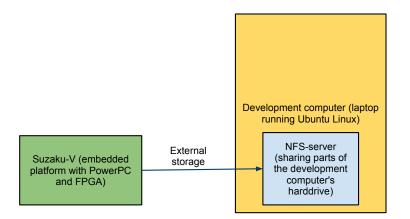

|    | A.4           | Setting up Network File System (NFS) on Suzaku and develop-<br>ment machine | 80  |

|    | A.5           | Creating kernel modules                                                     | 82  |

|    | A.6           | Compiling HWICAP-driver for uClinux                                         | 83  |

| в  | Con           | piling the HWOS-code                                                        | 84  |

| С  | VH            | DL-code                                                                     | 87  |

| D  | HW            | OS                                                                          | 95  |

|    | D.1           | The HWOS daemon                                                             | 95  |

|    | D.2           | HWOS-library                                                                | 115 |

# Chapter 1

# Introduction

# 1.1 What has been done

For partial reconfiguration of synchronous modules, several experiments have been performed on the FPGA using the Suzaku development board. A proof of concept has been developed and it has been shown that synchronous modules can be placed on the FPGA by writing them to ICAP (Internal Configuration Access Port).

For integration with the previously developed HWOS-methodologies, several experiments has been done with the instruction- and data cache backend made in [End10]. The software part of the HWOS-daemon has also been rewritten from scratch.

For a real-world system, a software-based scheduler has been integrated in the HWOS-daemon. This scheduler is working, but it has not been performed scheduling using FPGA-based modules.

# 1.2 Methodology

The following are the methodology and working philosophy adopted in this thesis. Much of the work done in this thesis is experimental and based on an existing framework. Parts of the system has been designed for or somehow depends on the propertiary, Xilinx-based FPGA platform. This is in contrast to a completely constructive approach where you build your own system from scratch. Some of the listed points are extra precautions that should be taken because of this fact.

Isolating the problem should be done at an early stage. The reconfigurable framework consists of many parts that will have to work together and if a simple run time reconfigurable module should be tested, a complete system would have to be set up. As discussed in [Han10], this process takes quite

some time and the documentation of the FPGA-platform from Xilinx does not always contain the level of detail needed.

Making good assumptions is another aspect that should be given extra thought in this kind of thesis. The framework is built during several master thesises and the experimental approach is central in most of them. Because of this and because the field is rather new and unexplored, one should be especially critical to claims and hypothesis in earlier work and available articles on the subject. Vague formulations must of course be avoided. It should be made clear if some parts are uncertain or not thoroughfully tested.

A broad litterature search should be done. It is really helpful to see how other people have solved the same or a similiar problem. Their experiences and thoughts can be important guidelines when choosing an implementation or making design decisions. If other implementations are easily accessible, they can be integrated into the project and with that "reinventing the wheel" can be avoided.

The portability of the framework should be taken into consideration. Targeting a completely abstract FPGA is probably to limiting, but the technology and the components on the test-platform should be compared to available technology on other FPGAs. This is especially important for the work done on the given framework, as one of the goals is to be more independent of propertiary tools. The embedded software in this thesis has been written in ANSI-C. It can easily be compiled on a standard PC (x86) architecture and for the embedded PowerPC-processor that is present on the Suzaku development board. This can be valuable if the code must be ported to another microprocessor.

The code should be well structured. The code in this thesis has been written in the low-level languages C and VHDL. In contrast to higher level languages like Java or Python, these languages does not contain the same amount of abstraction from implementation-specific details. Poorly written code can therefore be more difficult to read and isolating any problems may become hard if the code is not modularized good enough. Several object-oriented principles like data abstraction, modularity, polymorphism and encapsulation has been utilized when writing the C-code for this thesis. This has proven crucial when debugging and testing the system.

The developed systems should be well tested. This can be a weakness in some of the previous master thesises on self reconfiguration. Because proof of concepts in the field take so much time to develop, it must be taken into consideration that some of the previous work has not been rigorously tested.

Testing and documentation has been given large emphasizing in this thesis. Code has been documented using the documentation system Doxygen and the test framework Check has been used for testing the different parts of the embedded software.

An iterative approach has in general been used for developing the methodologies and systems in this thesis. Experiments has been set up in test suites and test cases.

The implemented system, the decisions taken and the results should be discussed. All of these can also be compared to available litterature on the field. Even if it may be hard to do so, weaknesses in the implemented system and any bad decisions in the design should be revealed and discussed. These experiences are highly valuable to people that want to do further development or others doing research in the same field.

Most important of all, the implemented system should function deterministically. A product that has low power consumption, high performance and low space requirements may be completely useless if it fails now and then. This is especially true for embedded and real-time systems. For a hard real-time system, missing a task's deadline means the task has failed completely and there is no reason to finish it. For an embedded system, it might be impossible to do any further development or bug-fixing after it has been installed in the field. It's even worse if the system has been mass-produced. In any case, if the system is non-deterministic and suddenly fails, this could become very costly, ruin the company's reputation or even threaten human lifes.

# **1.3** Contribution from this thesis

The most important contributions from this thesis are:

- A more robust software-part of the HWOS and a well-tested library for code used in this HWOS.

- A simple round-robin scheduler made specifically for partial reconfiguration of FPGA-based tasks.

- A proof of concept showing that partial self-reconfiguration of synchronous modules can be performed on an FPGA.

- A methodology for constraining and making a static interface for clock signals.

# **1.4** Outline of this report

The next chapters are divided into *Related work*, *Theory*, *Implementation* and *Verification and results*.

*Related work* presents some of the earlier work done in the AHEAD-project and related work done worldwide.

Theory is a chapter for introducing the reader to the most relevant background theory for this thesis. Some of the theory, like parts of the scheduling theory, is quite general, but it should be discussed how these parts can be related to the problem in this thesis. Most of the references to the bibliography will from the *Theory* chapter.

*Implementation* shows how the final system has been implemented, what choices has been taken and why they were taken. This chapter will make heavy use of information and discussions from the *Theory* chapter.

*Verification and results* will document which parts of the implemented system was tested and results from the verification of the system.

Inside the *Theory*- and *Implementation*-sections there are also *Objective*sections. For the *Theory*, these small sections will answer the question "why is this information provided?", while the question "why has this been done?" is answered in the case of the *Implementation*-part. The *Objective*-sections are marked with the symbol in figure 1.1 to make it extra clear that they should answer these questions and nothing else.

Figure 1.1: Symbol for *Objective*-sections.

# Chapter 2

# **Related work**

The most relevant earlier and related work is presented in this chapter. The work is briefly evaluated and some critisism has been given.

This chapter has two purposes. The first is to give the reader a better overview of the work done in the AHEAD-project and discuss some of the challenges the earlier work reveals. The second purpose is to introduce the most relevant research done on partial self-reconfiguration and hardware operative systems for FPGA.

# 2.1 Work done in the AHEAD-project

### 2.1.1 Sverre Hamre's master thesis (june 2009): Framework for self reconfigurable system on Xilinx FPGA

The most important work done by Sverre Hamre [Ham09] (seen from the perspective of this thesis) is probably the software *icap\_write*. This work has been integrated in the scheduler implemented in this thesis and makes it possible to replace parts of the logic on the FPGA (*icap\_write* is further discussed in section 3.4.3).

Sverre Hamre seems to have tested *icap\_write* only on a few different partial configurations. Because the program is such an important part of the HWOS, it should be much better tested.

### 2.1.2 Vegard Endresen's master thesis (june 2010): Hardwaresoftware intercommunication in reconfigurable systems

Essentially, Vegard Endresen's work [End10] is an implementation of a backend/interrupter for FPGA tasks. The backend is built in VHDL and is able to extract and load data from/into a task running on the FPGA. This functionality can be controlled through an instruction set that is used by software applications to communicate with the backend. A state loading/saving module of this kind is of great importance and a critical part of HWOS. The fact that it is built in hardware makes it even more interesting when it comes to performance and parallel execution with the rest of the system.

There were some challenges when trying to understand and integrate Vegard's system in the HWOS. Perhaps could this have been easier if there was more documentation on the backend's internal mode of operation. The software-part of his work could also have been more well-structured. Vegard Endresen himself says the following in [End10, page 57]:

Implementation on a Suzaku-sz410 board has confirmed that the system and its parts are working. That said some components of the communication framework has been designed without a very thorough pre-analysis. Primarily this is the case for the HWOS where there might be much to gain by proper analysis and design.

# 2.1.3 Sindre Hansen's project report (december 2010): Self Reconfiguration of Clock Networks on FPGA

The work done in the project report [Han10] functions as a base for the work done in this thesis. The results in the project has shown that a clocked module in a FPGA-bitstream can be pulled out from a source bitstream and successfully put into a target bitstream. This operation was done on a PC and not while the FPGA was running. The target bitstream was later uploaded to the FPGA and it was verified that it worked as expected.

The project report showed that partial reconfiguration of clocked modules could be performed, but not why it was possible or how this could be done at run-time. These are problems that would have to be solved if a working solution on the FPGA should be realized.

# 2.2 Related work on partial self-reconfiguration and HWOS

### 2.2.1 Klaus Danne (2004): Memory Management to Support Multitasking on FPGA Based Systems

This article (found in [Dan04]) discusses some of the challenges when sharing an FPGA for multiple processes. A simple run-time system is introduced and special focus is on the Memory Management Unit (MMU), which use the concept og Virtual Memory Management to share distributed memory between several hardware tasks.

# Chapter 3

# Theory

# 3.1 Development tools

The development tool for FPGA development was the Xilinx Design Suite 10.1. Included in this suite was:

- Embedded Development Kit 10.1 for building user logic base designs.

- ISE 10.1 for building standalone reconfigurable modules.

- FPGA-Editor for inspecting placed and routed designs. Was also used for rerouting wires for logic.

- Planahead. Was used for setting constraints in both the base design and for the reconfigurable module.

For developing the software in this thesis, the following was used:

- The GCC-compiler for development on the development computer and for cross-compiling on the Suzaku.

- Valgrind for debugging memory leakage problems during the development process.

- The Check testing framework (see section 3.8.5) for testing the system.

# **3.2** Base platform

The development platform in this thesis is a development board from the japanese company Atmark-Techno. The board has an FPGA from Xilinx and an embedded microprocessor for implementing the reconfigurable systems. The website for Atmark-Techno has a download section containing both the base

VHDL-design for the FPGA and the Linux-distribution for the processor. The board also has LAN-connection for connecting it to a standard network. This makes it easy to connect to the board from a development computer and upload new FPGA- or software-designs.

### 3.2.1 Objective

The objective of this section is to present and give a quick overview of the basic setup for the development platform. This should make it easier to understand the results and discussions in the thesis. A new developer in the AHEAD-project will need to understand how the different parts of the platform can be set

up and what kind of tools should be used.

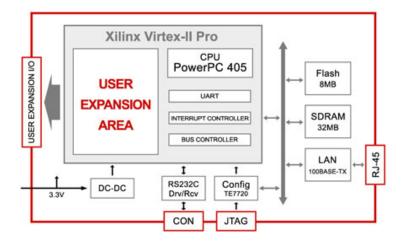

### 3.2.2 The development board

The development board used in this thesis has the specifications shown in table 3.1 and a similar model is shown in figure 3.1. The illustrated model (SZ310-U00) has some different specifications, among them is the type of the FPGA, the CPU and the configuration unit.

| Model                | SZ410-U00                            |

|----------------------|--------------------------------------|

| FPGA-device          | Xilinx Virtex-4 FX XC4VFX12-SF363    |

| CPU Core in FPGA     | PowerPC 405 (32bit RISC core)        |

| CPU Clock            | 350 Mhz                              |

| Crystal Oscillator   | 100Mhz                               |

| DRAM                 | 2*32MB DDR2                          |

| Flash Memory         | 8MB (SPI)                            |

| Ethernet             | 10BASE-T/100BASE-TX (half-duplex not |

|                      | supported)                           |

| User I/O Pins        | 86                                   |

| Serial Port          | 1 ch (RS232C)                        |

| Configuration        | SPI Flash                            |

| Board Size           | 72x47 [mm]                           |

| Power Input          | DC3.3V                               |

| Linux kernel version | 2.6                                  |

A photography of the Suzaku board is shown in figure 3.2.

Table 3.1: Specifications of Suzaku-V (SZ410-U00)

Figure 3.1: Illustration of the Suzaku-V (SZ310-U00). SZ410-U00 is used in this thesis. Picture taken from [AT11].

Figure 3.2: The Suzaku-V development board from Atmark-Techno.

# 3.2.3 The FPGA

A photography of the FPGA is shown in figure 3.3 and it's specifications are listed in table 3.2.

| Manufacturer            | Xilinx                     |

|-------------------------|----------------------------|

| Model                   | Virtex-4 FX XC4VFX12-SF363 |

| Speed grade             | -10                        |

| CLB Array: Row x Column | 64 x 24                    |

| Number of slices        | 5 472                      |

| Number of LUTs          | 10 944                     |

| Maximum Distributed RAM | 86                         |

| or Shift Registers (Kb) |                            |

| Number of flip-flops    | 10 944                     |

Table 3.2: Specifications of the FPGA used in the thesis.

Figure 3.3: Photography of the FPGA on the development board.

#### 3.2.4 Base VHDL-design for the Suzaku-V

The base design from Atmark-Techno contains the basic setup for communicating with the parts on the Suzaku-V board.

#### 3.2.5 Internal Configuration Access Port (ICAP)

The Internal Configuration Access Port (ICAP) allows for internal access to the FPGA bitstream at runtime. The embedded processor can communicate with ICAP through the Processor Local Bus (PLB) (as described in [Han10] and [Xil08b]).

#### 3.2.6 ATMARK-dist and uClinux-dist

ATMARK-dist is a Linux-distribution made specifically for the Microblazeand PowerPC-processors on the Suzaku-boards. The distribution is based on uClinux-dist and is built around the standard Linux 2.6-kernel [Atm06].

The original uClinux was a derivative of the Linux 2.0 kernel and was intended for microcontrollers without Memory Management Units (MMU) [Inc10]. It was later integrated in the main line Linux kernel sources, starting from Linux-2.5.46 [Ung02]. uClinux-dist is a collection of libraries, applications and tools, where the most important parts probably are the uClinux-kernel and the C standard library called uClibc.

A tutorial for setting up ATMARK-dist and NFS is provided in chapter A in the appendix.

#### 3.2.7 uClibc

uClibc is a C library for the Linux platform. It is intended for embedded systems and is much smaller than glibc, which is the C library typically used when developing applications in Linux.

uClibc supports many of the same applications as the heavier glibc and often it is possible to just switch libraries and recompile the source code [ucl11]. This assumption has been important when writing the C code for this thesis. The code has been written and tested on the development computer, recompiled for the PowerPC-architecture and tested more extensively on the embedded platform.

# **3.3** Addressing the bitstream for Virtex-4

The addressing in the bitstream for the Virtex-4 has been discussed in [Ham09, page 19]. The term *frame* and what one such frame may contain can be rather confusing. This subsection makes the meaning of a frame clear by evaluating the existing framework, articles on the subject and the documentation from Xilinx.

#### 3.3.1 Objective

The most important goal for this section is to define a frame and what meanings one frame or a series of frames can have in the bitstream or in the FPGA configuration memory. Another objective of this section is give a brief overview of how addressing of frames can be done in the bitstream file.

Understanding what a frame is and how frames can be addressed is very important if the programs *CLBRead* or *icap\_write* should be utilized in an application or further developed.

#### 3.3.2 Definitions

#### Bitstream file

A file made by the FPGA development tools. Does contain information to reconfigure the configuration memory on the FPGA, but also operations and overhead data for doing this.

#### Configuration memory

The configuration memory on the FPGA. Virtex-4 has SRAM-based configuration memory. These memory cells define the LUT equations, signal routing, IOB voltage standards and all other aspects of the user design [Xil09, page 87].

#### Frame

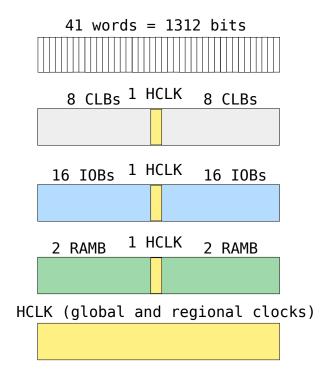

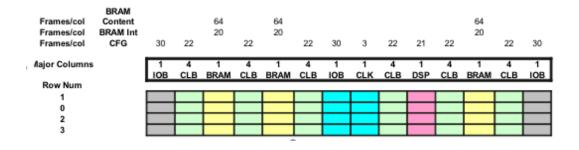

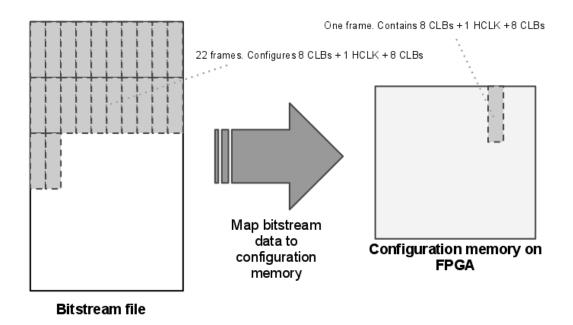

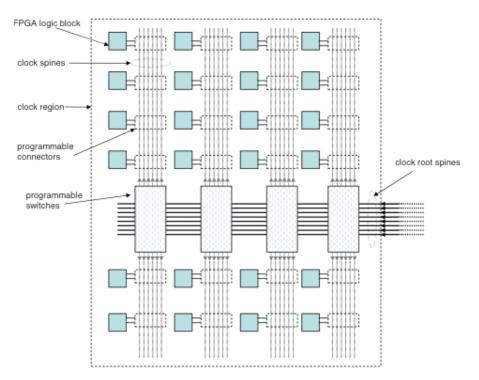

One frame is 41 32-bit words = 1312 bits [Xil09, page 92]. In the bitstream, 22 frames configures 8 CLBs + 1 HCLK + 8 CLBs. In the configuration memory, *one frame* constitutes 8 CLBs + 1 HCLK + 8 CLBs [TBC07].

#### Major column of CLBs

One full, vertical column of CLBs on the FPGA. Each column is one CLB wide.

#### Row of CLBs

A row spans the entire FPGA horizontally and it's vertical width is 8 CLBs + 1 HCLK + 8 CLBs.

#### Partial reconfiguration

Reconfigure only a part of the configuration memory.

#### Self reconfiguration

Defined here as that the embedded system performs the reconfiguration of the FPGA itself. A more strict definition could be that the FPGA reconfigures itself.

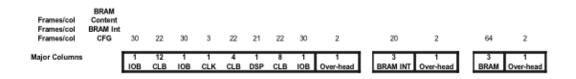

#### **3.3.3** Addressing of frames

The FPGA used in this thesis is  $16^*4 = 64$  CLBs in full height. A major column of CLBs is one full height of CLBs, one CLB wide. This FPGA has four rows, where each row spans the entire FPGA horizontally and is 16 CLBs in height. These definitions correspond with the definitions in [Xil09, page 92].

In [Ham09, page 10], Sverre Hamre lists up several articles that describe bitstream composure for Xilinx FPGAs. The article in [TBC07] is especially interesting as it describes a lot of the bitstream details for Virtex-4. One can imagine that these articles has been important when he wrote the program *icap\_write*. Figure 3.5 is from Sverre Hamre's master thesis [Ham09]. As shown in this figure, there should be 22 frames per column of CLBs on the FPGA. It is assumed that Sverre means there are 22 frames per column of 16 CLBs. Figure 3.6 is also from his master thesis and Sverre describes this as the organization of frames in the bitfile. It is assumed that this shows the organization of frames per row. Both assumptions correspond to the functionality of CLBRead and *icap\_write*, as well as the article in [TBC07].

Figure 3.4) is from [Han10] and show what a frame may constitute in the *configuration memory*.

Figure 3.4: Number of words in a frame and example of what frames in the configuration memory may contain (picture taken from [Han10]).

In [Ham09, page 20], Sverre Hamre writes:

In the bitstream the CLBs consist of 22 frames, 20 of these are for the routing and 2 are for the logic.

As discussed above, it is assumed that he means 22 frames per column of 16 CLBs. However, later on page 21 he says:

A frame in the bitstream is 41 words, 1312 bits, this is equal to 16 CLBs plus one word in the center of the bitstream for global logic.

As the discussion in this section reveals, the last statement seems to be wrong as one frame in the bitstream does not alone configure so many CLBs. Sverre probably meant the configuration memory. At last, figure 3.7 is added to show what the meaning of a frame may be in the bitstream or the configuration memory.

Figure 3.5: Virtex-4fx12 FPGA logic modules (picture taken from [Ham09, page 20]).

Figure 3.6: Virtex-4fx12 bitfile frame organization (picture taken from [Ham09, page 20]).

Figure 3.7: Conceptual drawing of the meaning of a frame on Virtex-4. Examples from the bistream and the configuration memory.

#### 3.3.4 The term frame in CLBRead

A short extract from the defines in the CLBRead header file is shown in listing 3.1. The comments has been added here to show what role each define play in the actual program. The use of the term *frame* is quite confusing also in this file. However, if only the defines used for addressing are considered and FRAMES\_PR\_CLB is interpreted as *frames per column of 16 CLBs*, everything seems to be correct and matching the previous discussion in this section.

```

1

Úsed for addressing in CLBRead.c

2

#define CLB_PR_ROW

24

3

"// Only used for debugging in CLBRead.c

#define CLB_PR_FRAME 16

4

5

6

Used for addressing in CLBRead.c

7

#define FRAMES_PR_CLB

22

8

Never used in CLBRead.c

9

#define BIT_PR_CLB

80

10

Only used for debugging in CLBRead.c

11

#define BYTES_PR_CLB

BIT_PR_CLB/8

12

13

(...)

Úsed for addressing in CLBRead.c

14

#define FRAME_LENGTH_32BIT_WORDS

41

15

Used for addressing in CLBRead.c

16

#define FRAMELENGTH_BYTES

FRAME_LENGTH_32BIT_WORDS*4

17

18

Never used anywhere

19

typedef struct

20

uint8_t iCLB[BYTES_PR_CLB*FRAMES_PR_CLB];

21

22

} clb_t;

(...)

23

```

Listing 3.1: Short extract from CLBRead.h. The omitted parts are marked  $(\ldots)$ .

#### 3.3.5 The term frame in icap\_write

The header file for *icap\_write* has the line **#define** WORDS\_PR\_FRAME 41 and one has to specify how many frames to write. The program takes 22 frames per *column of 16 CLBs*. This seems to be correct behaviour and has been verified by testing the program.

#### 3.3.6 The term frame in the documentation from Xilinx

The Configuration User Guide in [Xil09, page 92] states the following:

All Frames in Virtex-4 have a fixed, identical length of 1312 bits (41 32-bit words). One Frame configures one HCLK with either 4 block RAMS, 32 IOBs or 4 DSPs.

This presumably means that one frame in the *configuration memory* constitutes one HCLK with either 4 block RAMs, 32 IOBs or 4 DSPs. Note that the

documentation from Xilinx is rather sparse on information on the bitstream composure. It could for example not be found anywhere that 22 frames in the bitstream configures a column of 16 CLBs.

# **3.4** The existing framework for partial selfreconfiguration

In this section, the most important parts for the exisiting system for partial reconfiguration will be introduced. Some terms have been discussed in [Han10] and in earlier reports from the AHEAD-project. In that case, only a brief definition and a reference to the relevant report will be given.

#### 3.4.1 Objective

The goal of this section is to give the reader an overview of the existing framework for self-reconfiguration on the FPGA, *before* the contributions from this thesis are introduced. This is important, because much of the work done in this thesis builds upon the earlier work in the AHEAD-project.

#### 3.4.2 CLBRead

As discussed in [Han10, page 16], CLBRead is a program for reading out a partial CLB structure from a bitfile. It can also write a partial bitstream into another bitfile. In this case, the reconfiguration is done by modifying a bitstream that has not been uploaded to an FPGA. An important finding from [Han10] is that a partial bitstream containing routing information for both CLBs and clocks can be extracted and inserted into another bitstream. It was also shown that a flip-flop and it's corresponding clock signal can be relocated to another placement in the bitstream. This indicates that synchronous modules can be inserted into and relocated in a target bitstream file.

The greatest limitation with these results is that they have not been performed at run-time. One problem source that will have to be considered when performing reconfiguration at run-time are oscillating signals, especially when reconfiguring a high frequency clock signal. A clock buffer (see section 3.6.4) can be used for disabling the clock signal during reconfiguration and synchronous bus macros can be used for disabling normal signals into the module (see section 3.4.4). These considerations are important for practical designs, but are probably not necessary for showing a proof of concept for partial reconfiguration.

Another problem source is that propertiary protocols from Xilinx will have

to be used for writing the bitstream to the FPGA at run-time. The CLBRead program is open-source, thus making it easier to isolate problems when doing research on the area. For this matter, the analysis of the run-time reconfiguration process done by Sverre Hamre in [Ham09] acts as supporting documentation when doing any further development.

#### 3.4.3 icap\_write

#### Concept

CLBRead's ability to write a partial bitstream to another file has not been used in this thesis. Instead, the partial bitstream is written to a running configuration on a physical FPGA through the Internal Configuration Access Port (ICAP). Essentially, this means that the file containing the partial bitstream and a software program for writing to ICAP has to be present on the Suzaku platform. Sverre Hamre has in his thesis [Ham09] written the C-program *icap\_write*. This program runs on the PowerPC-processor on the Suzaku, takes a bitfile description of a partial bitstream as input and writes it to the ICAP port. It is very important to note that this program has not been tested thorughfully, or as Sverre Hamre states (from [Ham09]):

The icap\_write and icap\_test programs are written to utilize the Linux icap driver. These are just test programs, especially since they have hard coded the adressing and has a lot of printf() for debugging.

Despite that icap\_write is a test program, it is well written and easy to understand. Sverre Hamre has provided good documentation of the process of writing to ICAP in his master thesis.

#### Practical use

```

1 ./icap_write -h

```

2 [icap\_write -i [filename] -f [frames]

3 This program has the address hardcoded inn. 4 Frames will be written to CLB 21 and on, on top row.

Listing 3.2: icap\_write help

As seen is listing 3.2, the program takes two inputs. The first is the filename of the bitfile and the second is the number of frames to be written.

Because one vertical series of 16 CLBs is the smallest possible configurable unit on the Virtex-4 and because the original program by Sverre Hamre has the adressing hardcoded in the program, *icap\_write* has been rewritten in 5.13. It is now a part of the HWOS-library and the library module is called *hicap*. Refer to that section to see how this functionality is used.

#### 3.4.4 Bus macros

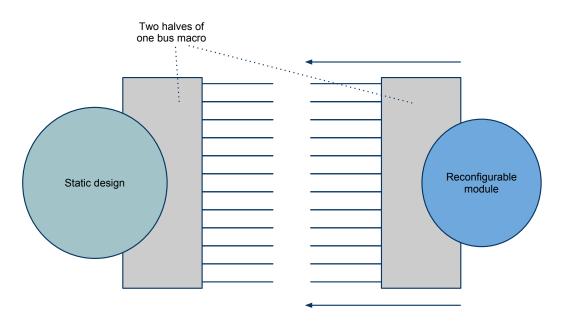

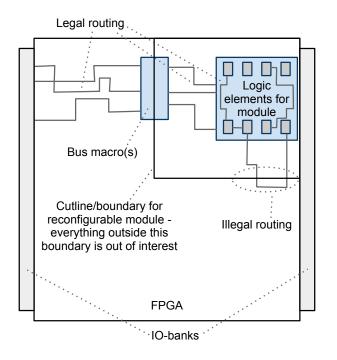

A bus macro is essentially just a static interface between the module and the static design (figure 3.8). One simple analogy to this is a standard power outlet in a house wall where different devices can be connected, always using the same type of plug.

Figure 3.8: Conceptual drawing of a bus macro.

Normally the wiring between two adjacent CLBs are dynamically routed during the place-and-route phase of the implementation process. The problem is that the module and the static design are implemented separately and that the routing between them will not be consistent.

How a bus macro is made in FPGA-editor is described in a tutorial by Sverre Hamre [Ham08b]. The most simple bus macro is made of two adjacent CLBs and a static, predefined routing between them that does not change between implementations. The number of wires between the two CLBs will be technology dependent, but a wider bus macro can of course be made by setting up several pairs of CLBs.

As shown in figure 3.8, one half of the bus macro is integrated in the reconfigurable module and the other half is integrated in the static design. To achieve this, the reconfigurable module and one complete bus macro is built together in an empty FPGA-design. Using the program CLBRead (section 3.4.2), the reconfigurable module and one half of the bus macro is cut out and stored in a partial bit file.

# 3.5 Synchronous design

### 3.5.1 Objective

Because the thesis focus on methodology for partial reconfiguration of synchronous modules, the reader should understand what a synchronous module is and why synchronous design is important on an FPGA. Essentially, this section seeks to answer why it is so important that a clock signal can be routed to the recon-

figurable module.

### 3.5.2 Definitions

#### Synchronous design

A clock signal triggers all events [Ste05, page 4].

#### Synchronous reconfigurable module

Is in this thesis defined as a module using the same or a derived clock signal from the static base design.

### 3.5.3 Motivation for using synchronous design

In [Ste05], Jennifer Stephenson from Altera has discussed some fundamental design practises for synchronous designs on FPGA. On page 4, she writes:

The basic principle of synchronous design is that a clock signal triggers all events. As long as all of the registers' timing requirements are met, a synchronous design behaves in a predictable and reliable manner for all process, voltage, and temperature (PVT) conditions. Typically, designers can easily target synchronous designs to different device families or speed grades.

Her words says a lot about the motivation for using synchronous modules in a reconfigurable framework. Making the module synchronous to the clock signal in the base design can be seen as a way of letting the module "inherit" the timing of the framework. Because the interface for control signals and data transfer is the same for all the reconfigurable modules, it is important that each module has predictable timing behaviour.

#### 3.5.4 Problems in asynchronous designs

There has been a lot of research on asynchronous design, both for ASICs and FPGAs. One of the largest problems is that the main-stream FPGAs and

their tools and not made for this type of design practise. The analysis tools for FPGA designs are tailored for synchronous designs and it is easy to verify that flip-flop setup and hold times are met under worst case conditions for such designs [Eri00]. For asynchronous designs, the designer would have to manually check the worst case timing of the signal paths, a process that would be time-consuming or maybe impossible for complex designs. Even worse is that this process must be redone for small changes in the design or if the design is migrated to another FPGA.

Another problem is handling asynchronous input values to flip-flops. The registers in FPGAs have a defined interval where the input value must be stable to ensure that a reliable output signal is achieved. Specifically, the input value must be stable for a minimum time of  $t_su$  (register setup time) before the positive clock edge and a minimum time  $t_H$  (register hold time) after the edge. The output value is then available after some time  $t_co$ . The problem is if the signal transition violates the  $t_su$  or the  $t_H$  requirements. In this case, the output may go into a *metastable state* and the output of the register may be delayed and not be available withing the required time  $t_co$  [Alt09]. For synchronous designs, the input signal to the registers must always meet the requirements, so the problem with *metastability* does not occur [Alt09].

#### 3.5.5 Timing requirements for a reconfigurable module

The types of communication between the framework and the reconfigurable module can be divided into *control signals* and *data transfers*.

#### **Control signals**

Signalling that the module should start or that a data transfer is finished are typical control operations. If it is impossible to know when the operation has been performed (such as when the module has been started), hand-shake signals should be used. Signals for initiating operations and for signalling that operations has been done must probably be present for both synchronous and asynchronous modules. As discuessed earlier, the problem for asynchronous modules would be performing the actual operation without a clock signal to relate to.

#### Data transfers

Data transfers are more complex. The framework would typically implement some sort of serial communication to transfer data to and from the module. The state of the module is an example of data that must be transferred this way. In the implementation by Vegard Endresen [End10], one or more parallel shift-registers are used for this transfer. In this case, the framework assumes that the module shifts out one bit of data each clock cycle. This is a safe and deterministic way of doing high-performance data transfers if the clock signal in the module has low skew and is synchronous to the clock signal in the framework.

On the other hand, if the module was asynchronous, some sort of handshaking mechanism would have to be used. An example implementation would function this way:

- 1. The framework signals to the module that one bit should be shifted out by setting SHIFT high.