# Digital-to-Analog Conversion in High Resolution Audio

by

Ivar Løkken September 2008

Submitted to the Norwegian University of Science and Technology in partial fulfilment of the requirements for the degree philosophiae doctor

#### **NTNU**

Norwegian University of Science and Technology

Thesis for the degree philosophiae doctor Faculty of Information Technology, Mathematics and Electrical Engineering Department of Electronics and Telecommunications

© Ivar Løkken

ISBN 978-82-471-1209-0 [printed version] ISBN 978-82-471-1210-6 [electronic version] ISSN 1503-8181

NTNU Doctoral Theses 2008:257

Printed by NTNU-trykk

### **Abstract**

This thesis describes theoretical and simulation-based work on digital-to-analog conversion for high resolution audio. The emphasis of the work has been exploration and clarification of issues of contention in previous art. The work has resulted in five scientific papers published in international peer-reviewed journals and conference proceedings, and these papers constitute the main contribution. The papers are included as appendixes, whereas the preceding monograph serves to provide the necessary background for understanding the results, and also their relevance in an audio context. It should be noted that although the research primarily treats DA conversion, the findings and conclusions are largely transferable also to AD conversion since audio ADC performance is often limited by its usually compulsory feedback DAC.

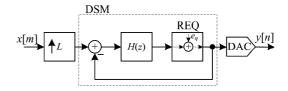

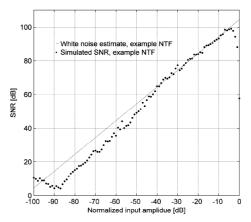

The first paper, published in the *Journal of the Audio Engineering Society*, explores power modulation of the quantization error and the need for dithering in delta-sigma modulators. There has been a lot of dispute on this issue; previous publications having both argued that the DSM is self-dithering and that it has the same dither requirements as a regular REQ. By exploring noise power modulation in the baseband it is shown that even high order DSMs are not self-dithering in the true sense, but that the adverse effects of quantization are reduced when the loop filter is of high order. If the REQ is multi-bit the noise power modulation can be made negligible compared to any practical levels of circuit noise.

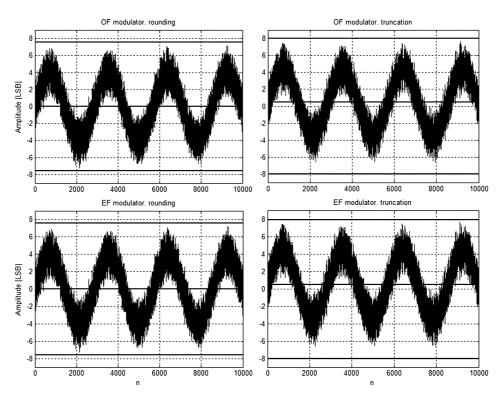

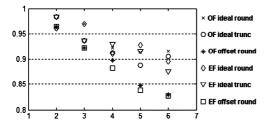

The second paper, published in *IEEE Transactions on Circuits and Systems Part II*, explores a class of DSM called non-overloading or NOL modulators. Designing the DSM to be NOL is the only known way to *guarantee* stability for high order loops, and also the only way to guarantee no quantization noise power modulation. The paper proves that NOL design criteria are equivalent for OF and EF modulators, repudiating a claim of difference in a previous publication, and also their equivalence for rounding and truncating quantizers. Although the results are developed for a certain class of modulators, the methods are easily generalized to any DSM design. It is found desirable to use a many-bit REQ since a NOL DSM with good input swing is then allowed.

The third paper, presented at the 31<sup>st</sup> Conference of the Audio Engineering Society, shows a useful utilization of the results developed in the second paper. Using a many-bit DSM is desirable for several reasons, but will in straightforward implementation require a DEM network of excessive complexity. A previously proposed method to circumvent this is to segment the DAC and DEM using a dedicated Segmentation-DSM. Previous art has used SDSMs with a FIR loop filter to ensure no DAC saturation, restricting the concept to very non-optimal designs. This publication utilizes the NOL method to design IIR SDSMs with significantly improved performance.

The fourth paper, submitted to *Analog Integrated Circuits and Signal Processing*, describes the development of simplified estimates for DSM DAC errors. The mathematical treatment of high order DSMs is exceedingly difficult, but simplifications and rules of thumb have been developed that enable design engineers to make quite straightforward optimization of relevant DSM parameters. A major drawback is that these approximations do not account for analog error sources in the DAC and may therefore lead to unfortunate design choices. This paper explores how common DAC errors depend on the DSM transfer function, and presents extensions of known approximation methods to also include the impact the DSM has on DAC waveform distortion. Again it is confirmed that using a many-bit DSM is advantageous, and also that a conservative DSM design will make the DAC less susceptible to errors.

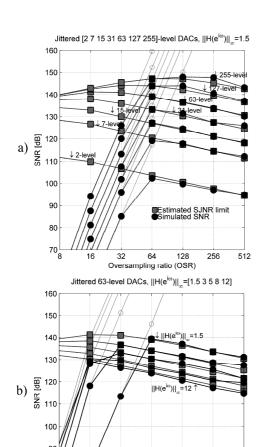

ii Abstract

The fifth and last paper, presented at the 124<sup>th</sup> Convention of the Audio Engineering Society, utilizes the methods presented in the fourth paper to optimize a DAC with regards to jitter noise. Clock jitter is one of the most critical performance bottlenecks in high resolution audio, and the paper proposes ways to minimize the DAC's jitter susceptibility. The simplified approximation methods are employed and extended to show that a semidigital FIR DAC gives a more benign output waveform than a segmented DEM DAC of comparable complexity, and that it will be a preferable solution if jitter dominates the error budget. A simple method is also shown to estimate effects of implementation inaccuracies in the analog filter coefficients.

### **Preface**

This thesis is submitted in partial fulfilment of the requirements for the degree Philosophiae Doctor (Ph.D.) at the Norwegian University of Science and Technology (NTNU), Department of Electronics and Telecommunications. The work has been funded by the Norwegian Research Council under grant 162101 SPECK. My main supervisor has been Professor Trond Sæther and my co-supervisor has been Dr.Ing. Bjørnar Hernes.

The studies have been carried out in the period from January 2005 to May 2008. The work includes the equivalent of a little over half a year of full-time course studies (39 ECTS credits), teaching one fifth year master level course on data converters and supervising two students on their master projects. The first year and a half was spent at the university, and after this the work was carried out at the Nordic Semiconductor data converter department. When the Nordic data converter business was acquired by Chipidea Microelectronica, we were two Ph.D. students enrolled at the department who joined in on the move. Chipidea Norway sadly turned out to be a short lived venture, as irreconcilably different visions for the future between the mother company and the Norwegian department staff, eventually led to all regular employees in Norway leaving in order to pursue a fresh start with new company Arctic Silicon Devices. I and the other Ph.D. student were still allowed to finish our studies at the university where I am now, while remaining on Chipidea contracts. So in many ways the circle seems complete, as I am now finishing this study more than three years later, back where it started.

### Acknowledgements

This thesis is dedicated to my friends and family, in particular my parents and my sister. If it wasn't for you, I would not have been here today.

As I am sitting in my office at the university writing this, spring is in the air and almost four years have passed since I was in a similar situation as a master student. Then too Trond was my supervisor and in our meetings, which often slanted into hi-fi talks since we are both devout audiophiles and music fans, he aired the idea of doing a Ph.D. on audio conversion. With my background and interests I found this to be an extremely exciting opportunity and jumped at it, and it was arranged between the university, Nordic and the research council to initiate a project. Four years later I have no regrets, as I have learned a lot and met many interesting people on the way. I would like to express my gratitude to those who have been of help; both professionally and administratively, during the years spent pursuing this degree.

First and foremost my colleague and fellow Ph.D. student Anders Vinje, who has travelled the same slightly bumpy path to this point as me, has been of tremendous aid during the work on my papers and as a general "sparring partner" during problem solving. His mathematical prowess easily surpasses mine and I would have had a lot more troubled times in front of the notebook if it wasn't for him. Hurdles related to our somewhat unusual work situation have also been easier to climb than if I had been in it alone.

I am also in debt to my main supervisor Trond and co-supervisor Bjørnar, who have been of great help administratively. The path on which I set out is one they were both familiar with from when they did their own Ph.D. degrees, and they helped me to keep my focus on the light in the end of the tunnel even when at times the tunnel itself seemed dark.

To spend one and a half years with the former Nordic data converter team gave a sobering insight into the practical aspects of integrated circuit design. Listening in on their project meetings provided a pragmatic context to my theoretical work and helped me maintain a meaningful focus. Thanks to Morten Dammen, Terje Granum, Øystein Moldsvor, Christian Holdø, Håvard Korsvoll, Frode Telstø, Terje Andersen, and Atle Briskemyr for providing an informal and positive work environment with a lot of expertise. Johnny Bjørnsen who remained at Nordic after the takeover also deserves mention as part of this group.

Managing a master level course on data converters and advising two master students on their projects was invaluable in learning to communicate and share my knowledge. I thank Lasse Olsen and Florian Bousquet for being interested and skilful students.

I also want to thank the staff and students at the NTNU Circuits and Systems group for my time and discussions with them, in particular Prof. Trond Ytterdal, Carsten Wulff, and Rune Kaald. And last but not least; thank you to the management at Chipidea and Prof. João Vital for allowing me and Anders to finish our degrees even though the data converter team fell apart. I am sorry the endeavour of Chipidea Norway ended the way it did.

Finally, I would like to pay a small homage to the late audio-guru Steen Aage Duelund, with whom I got to discuss and learn from just before he untimely went away. Although his fields of expertise were only tangentially related to mine, his clairvoyance and ability to think outside the box, his holistic philosophical approach to the art of audio, and his great enthusiasm provided me with a lot of inspiration. His presence is missed.

Trondheim, May 2008

Ivar Løkken.

## **Table of Contents**

| Abstr   | act                                                | i   |

|---------|----------------------------------------------------|-----|

| Prefac  | ee                                                 | iii |

| Ackno   | owledgements                                       | iv  |

| Table   | of Contents                                        | v   |

| List of | f Figures                                          | vii |

| List of | f Abbreviations                                    | ix  |

| Chapt   | ter 1 Introduction                                 | 1   |

| 1.1     | Hearing and Audio Quality                          | 1   |

| 1.2     | A Brief Historical Review of Digital Audio         |     |

| 1.3     | Organization of This Thesis                        |     |

| Chapt   | ter 2 Fundamental Theory                           | 7   |

| 2.1     | Sampling and Reconstruction                        | 7   |

| 2.2     | Quantization                                       |     |

| 2.3     | Oversampling                                       | 16  |

| 2.4     | Dither                                             | 17  |

| 2.5     | Delta-Sigma Modulation                             |     |

| 2.6     | The DAC                                            |     |

| 2.7     | DAC Errors                                         | 24  |

| Chapt   | ter 3 The Delta-Sigma Modulator                    | 35  |

| 3.1     | Delta Sigma Modulator Design                       | 35  |

| 3.2     | Alternative Delta-Sigma Structures                 |     |

| 3.3     | Stability                                          | 43  |

| 3.4     | Cyclic Behaviour, Tones and Noise Power Modulation | 46  |

| 3.5     | Non-Overloading Delta-Sigma Modulators             | 50  |

| Chapt   | ter 4 Mismatch Shaping                             | 53  |

| 4.1     | Mismatch Error Randomization                       | 53  |

| 4.2     | Element Rotation Techniques                        | 54  |

| 4.3     | Other Techniques                                   |     |

| 4.4     | Segmented Mismatch Shaping                         |     |

| Chapt   | ter 5 Delta-Sigma and Dynamic DAC Errors           | 65  |

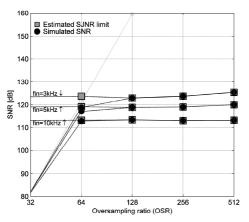

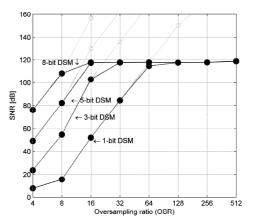

| 5.1     | Delta-Sigma and Jitter Error Estimation            | 65  |

| 5.2     | Delta-Sigma and Switching Error Estimation         |     |

| 5.3     | Techniques for Reducing Dynamic Errors             | 73  |

vi Table of Contents

| <b>Chapter 6</b> | Conclusions and Further Work | 83  |

|------------------|------------------------------|-----|

| 6.1 Co           | onclusions                   | 83  |

|                  | oposals for Further Work     |     |

| Appendix         | 1 Frequency Analysis         | 87  |

| Appendix         | 2 Paper I                    | 91  |

| Appendix         | 3 Paper I Errata             | 107 |

| Appendix -       | 4 Paper II                   | 109 |

| Appendix         | 5 Paper III                  | 115 |

| Appendix         | 6 Paper IV                   | 121 |

| Appendix         | 7 Paper V                    | 137 |

| Bibliograp       | ohy                          | 151 |

# **List of Figures**

| Figure 1: Equal loudness contours (ISO226)                               |    |

|--------------------------------------------------------------------------|----|

| Figure 2: A-weighting function (IEC/CD 1672)                             | 2  |

| Figure 3: Digital audio recording and playback chain                     | 3  |

| Figure 4: Conceptualization of simultaneous masking                      | 4  |

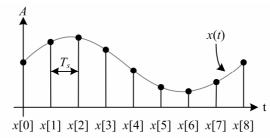

| Figure 5: Sampling of a continuous-time signal                           | 7  |

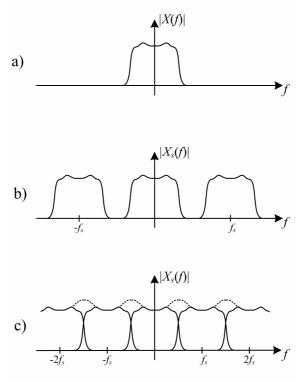

| Figure 6: a) Continuous spectrum b) Sampled spectrum c) Alias distortion | 8  |

| Figure 7: Sampled waveform of fig.5 and an alias                         | 9  |

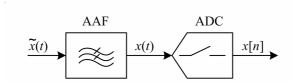

| Figure 8: Conceptual ADC and AAF                                         | 9  |

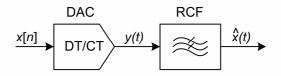

| Figure 9: Conceptual DAC and RCF                                         | 10 |

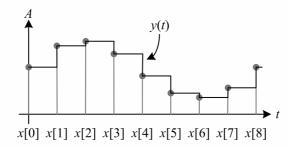

| Figure 10: Output waveform from PCM DAC                                  |    |

| Figure 11: Hold reconstruction filtering effect                          | 12 |

| Figure 12: Uniform scalar mid-thread quantizer                           |    |

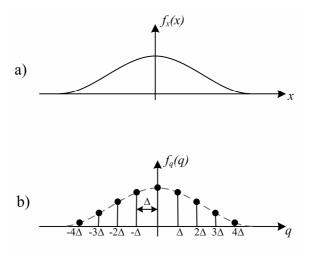

| Figure 13: Quantizer input PDF (a) and output PDF (b)                    |    |

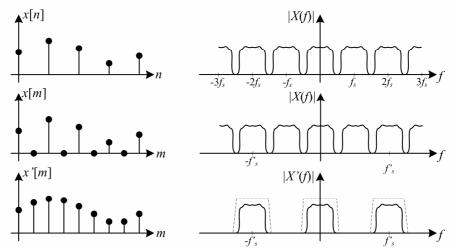

| Figure 14: DAC oversampling in the time and frequency domains            |    |

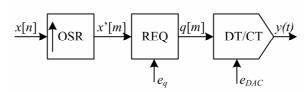

| Figure 15: Oversampling DA-converter with REQ                            |    |

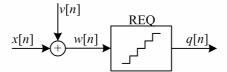

| Figure 16: Dithered quantization                                         |    |

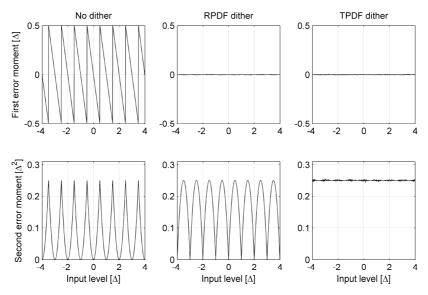

| Figure 17: First two error moments as function of input level            |    |

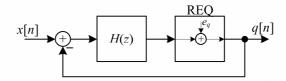

| Figure 18: Basic delta-sigma modulator                                   |    |

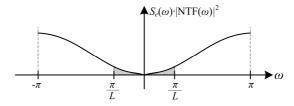

| Figure 19: Illustration of DSM noise shaping                             |    |

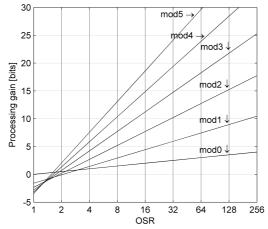

| Figure 20: Processing gain of modN DSM                                   |    |

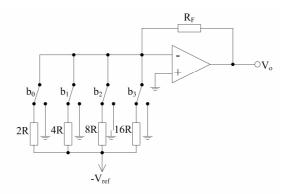

| Figure 21: Resistor ladder type DAC                                      |    |

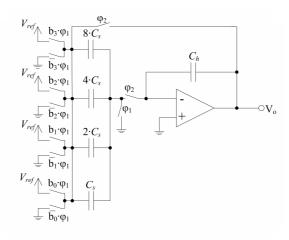

| Figure 22: DCT integrator SC DAC                                         |    |

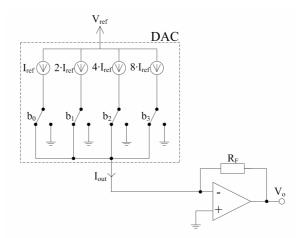

| Figure 23: Current mode DAC with external I-V conversion                 |    |

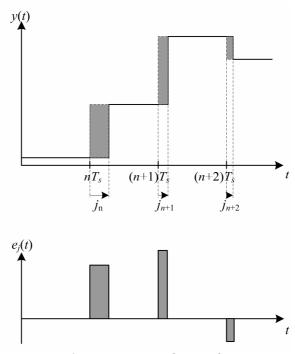

| Figure 24: Jitter error in the time domain                               |    |

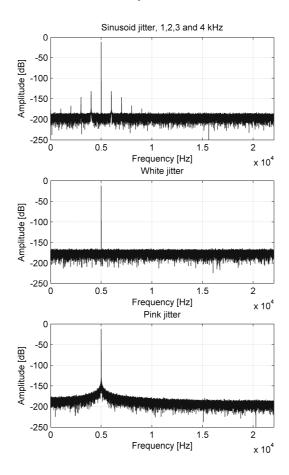

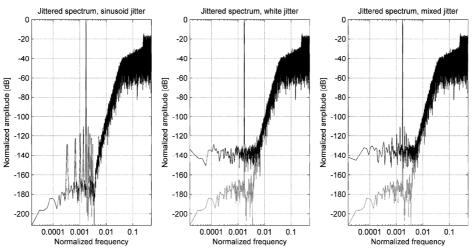

| Figure 25: Jitter distortion from sinusoid, white and pink jitter        |    |

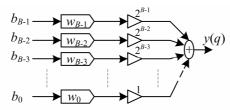

| Figure 26: Generalized schematic of binary encoded DAC                   | 29 |

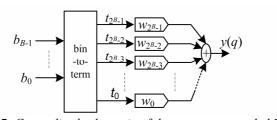

| Figure 27: Generalized schematic of thermometer encoded DAC              | 29 |

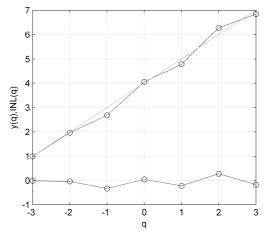

| Figure 28: DAC transfer function, ideal and with INL                     |    |

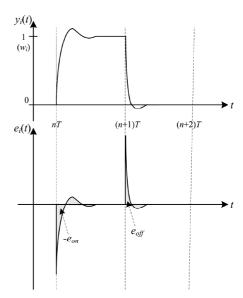

| Figure 29: DAC element on and off switching and error waveform.          | 31 |

| Figure 30: Equivalent small signal circuit for current steering DAC      | 32 |

| Figure 31: INL from finite output impedance                              |    |

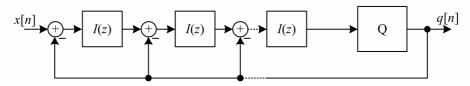

| Figure 32: Basic delta-sigma modulator                                   | 35 |

| Figure 33: The Silva-Steensgaard modified DSM structure                  | 36 |

| Figure 34: Generalized DSM structure                                     | 36 |

| Figure 35: Basic modN distributed feedback DSM                           |    |

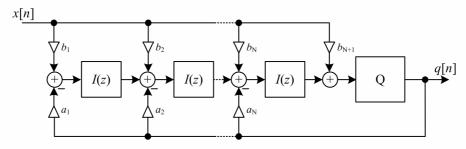

| Figure 36: Generalized distributed feedback DSM                          | 37 |

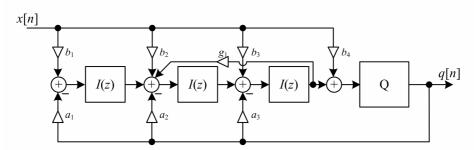

| Figure 37: Distributed feedback DSM with resonator for NTF optimization  | 38 |

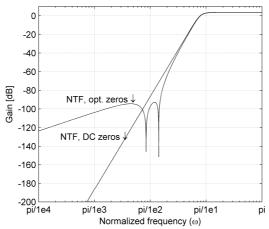

| Figure 38: Optimization of NTF zeros                                     | 39 |

| Figure 39: Distributed feed-forward DSM structure                        | 39 |

| Figure 40: The error-feedback DSM structure                              | 40 |

| Figure 41: A two-stage MASH modulator                                    | 41 |

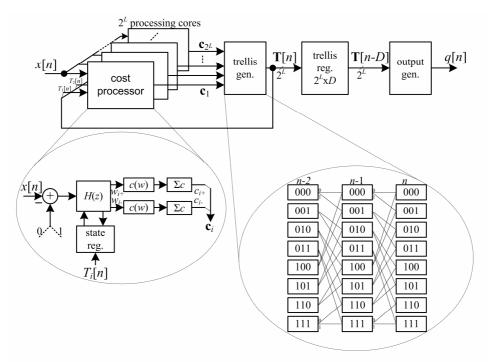

| Figure 42: Principle for the "ultimate modulator"                        | 42 |

| Figure 43: Trellis noise shaping modulator                               | 43 |

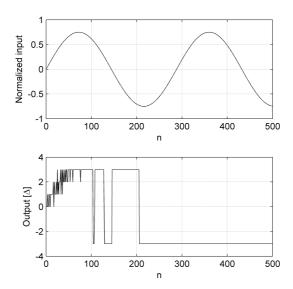

| Figure 44: Example of instability in high order DSM                      | 44 |

| Figure 45: Modified linear DSM model used in Root Locus method           | 45 |

| Figure 46: Processing gain with 1-bit stable DSM                         |    |

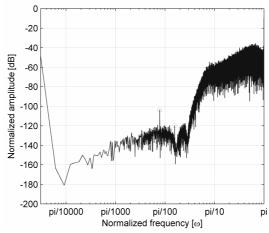

| Figure 47: Output spectrum from fifth order DSM with rational DC input   | 47 |

viii List of Figures

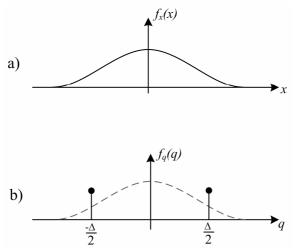

| Figure 48: Input PDF (a) and output PDF (b), single-bit quantizer                      | 49 |

|----------------------------------------------------------------------------------------|----|

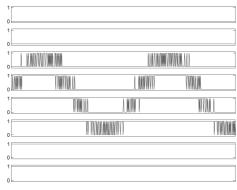

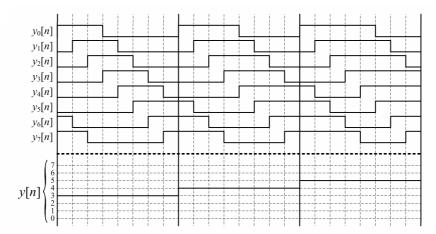

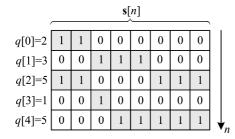

| Figure 49: DAC element randomization, B=3 bit example                                  | 53 |

| Figure 50: DWA DAC element rotation, B=3 bit example                                   | 55 |

| Figure 51: Element selection sequence with DWA                                         | 55 |

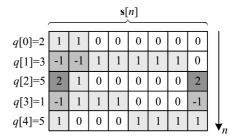

| Figure 52: Element selection sequence with second order DWA                            | 58 |

| Figure 53: Switching sequence for each element in a 3-bit DSM DAC                      | 59 |

| Figure 54: Switching sequence for each element in a 3-bit DSM DAC with DWA             |    |

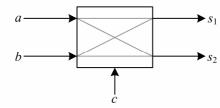

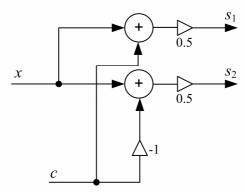

| Figure 55: Two element swapper cell                                                    | 60 |

| Figure 56: Swapping cell network for DEM, B=3                                          | 60 |

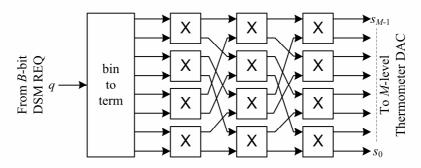

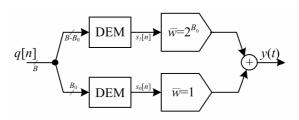

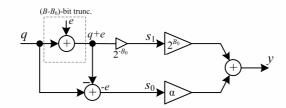

| Figure 57: Data splitting and reduction for tree structure DEM                         | 61 |

| Figure 58: Complete reduction tree with first order mismatch shaping                   |    |

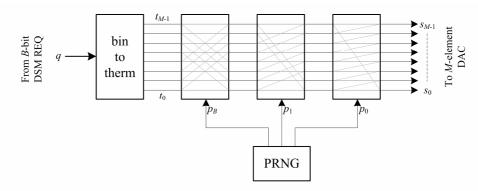

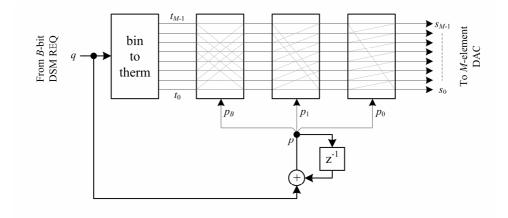

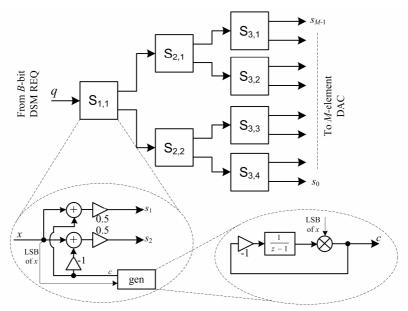

| Figure 59: DEM and DAC segmentation                                                    | 62 |

| Figure 60: Equivalent signal flow diagram of segmented DAC                             | 63 |

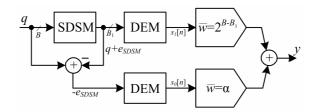

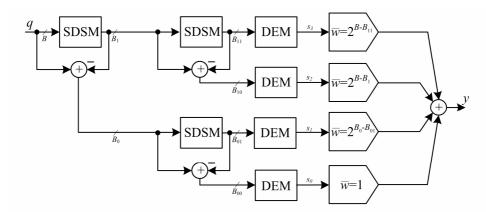

| Figure 61: DEM and DAC segmentation with SDSM                                          | 63 |

| Figure 62: Two time DEM and DAC segmentation                                           | 64 |

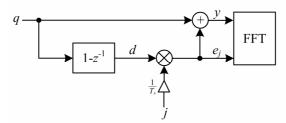

| Figure 63: Area error model for jitter distortion analysis                             | 65 |

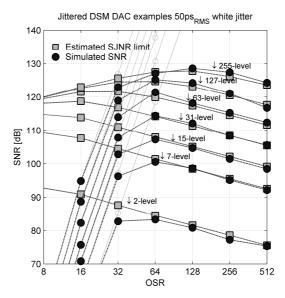

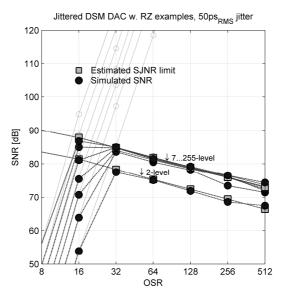

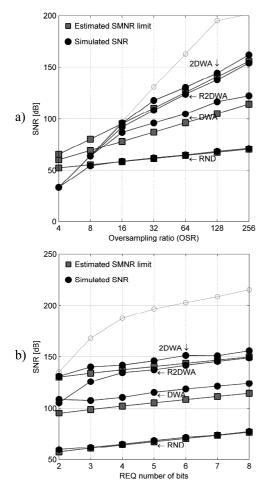

| Figure 64: SJNR <sub>max</sub> example, 50ps white jitter                              |    |

| Figure 65: Jittered spectrum with a) sinusoid, b) white, and c) mixed jitter           | 68 |

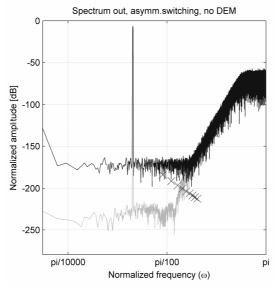

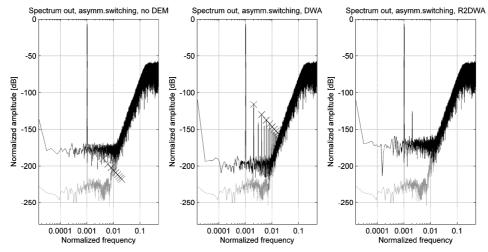

| Figure 66: Simulated spectrum, 10ps switching asymmetry                                |    |

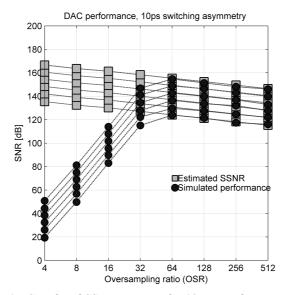

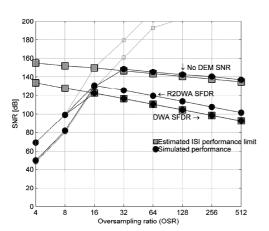

| Figure 67: Simulated SSNR <sub>max</sub> example, 10ps switching asymmetry             | 70 |

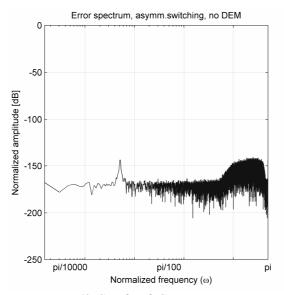

| Figure 68: Simulated ISI error spectrum                                                | 70 |

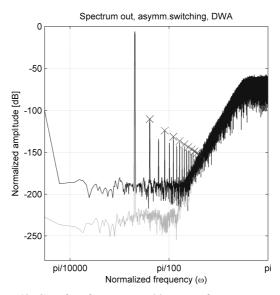

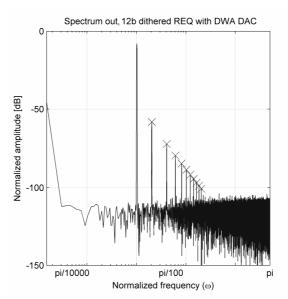

| Figure 69: Simulated spectrum, 10ps switching asymmetry, DWA                           | 71 |

| Figure 70: Simulated spectrum of LPCM DAC with DWA                                     | 72 |

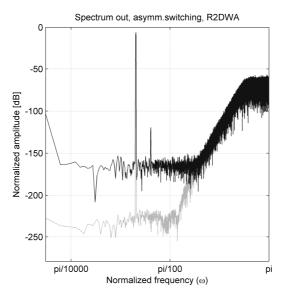

| Figure 71: Simulated spectrum, 10ps switching asymmetry, R2DWA                         | 72 |

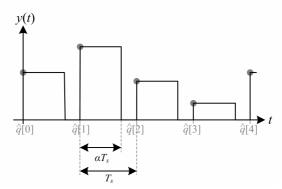

| Figure 72: Return-to-zero waveform                                                     |    |

| Figure 73: SJNR <sub>max</sub> , 50ps white jitter and RZ DAC                          | 75 |

| Figure 74: Dual-RZ waveform                                                            | 76 |

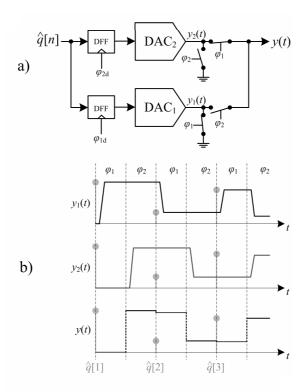

| Figure 75: DAC time-interleaving, a) functional diagram, b) waveform                   | 76 |

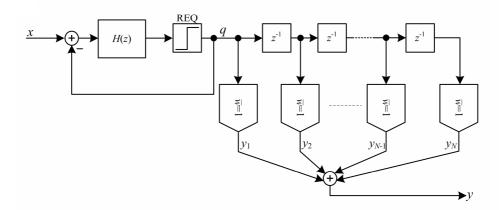

| Figure 76: 1-bit DSM REQ with semidigital filtering DAC for multi-level output         | 77 |

| Figure 77: Multi-bit DSM REQ with semidigital filtering DAC                            | 78 |

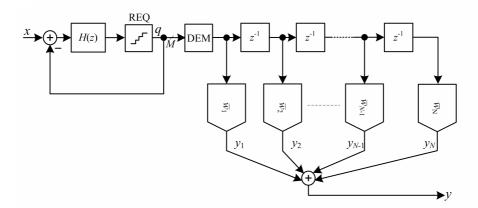

| Figure 78: a) Analog PWM modulation b) Digital PCM-PWM conversion                      | 79 |

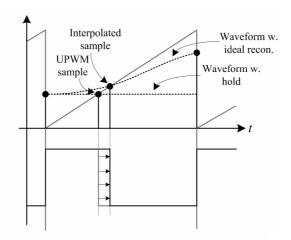

| Figure 79: UPWM error                                                                  |    |

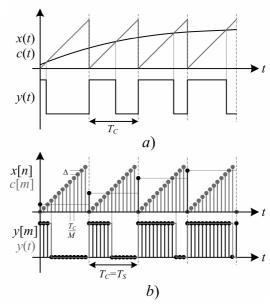

| Figure 80: PWM-based algorithm used by Reefman et al. to eliminate mismatch and ISI    | 81 |

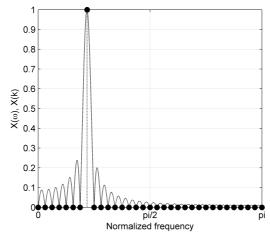

| Figure 81: Illustration of DFT spectral leakage                                        | 88 |

| Figure 82: Spectrum of sine multiplied with rectangular (top) and hann (bottom) window | 89 |

| Figure 83: Convoluted spectrum and DFT samples with coherent sampling                  |    |

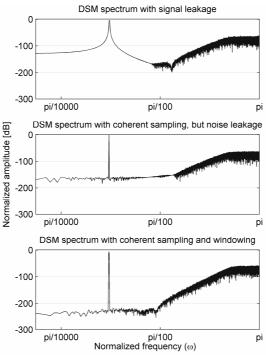

| Figure 84: Illustration of signal leakage and noise leakage impairing DSM DFT          | 90 |

|                                                                                        |    |

### **List of Abbreviations**

AAF Anti-Alias Filter ABE Analog Back End

ADC Analog to Digital Converter (or: Analog to Digital Conversion)

ADDA Analog-Digital-Digital-Analog AES Audio Engineering Society

AFE Analog Front End

ANSI American National Standards Institute

ARA Acoustic Renaissance for Audio

ASRC Asynchronous Sample-Rate Converter

BIBO Bounded Input Bounded Output

BJT Bipolar Junction Transistor

CD Compact Disc

CF Characteristic Function

CMOS Complementary Metal Oxide Semiconductor

DAC Digital to Analog Converter (or: Digital to Analog Conversion)

DB: DeciBel

DBFS DeciBel relative to full-scale

DCT Direct Charge Transfer

DEM Dynamic Element Matching

DFT Discrete Fourier Transform

DIN Deutsches Institut für Normung

DNL Differential Non-Linearity

DSM Delta Sigma Modulator (or: Delta Sigma Modulation)

DSD Direct Stream Digital

DSP Digital Signal Processing

DTFT Discrete Time Fourier Transform

DVD Digital Versatile Disc

DVD-A DVD-Audio

DWA Data Weighted Averaging

EF Error Feedback

ENOB Effective Number of Bits

FET Field Effect Transistor

FFT Fast Fourier Transform

FIR Finite Impulse Response

FOM Figure of Merit

FPGA Field Programmable Gate Array

FS Full-Scale (or: If written  $f_s$ ; sampling frequency)

HD Harmonic Distortion

HD2 Second Harmonic Distortion HD3 Third Harmonic Distortion

HF High Frequency

Hi-res High Resolution

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

IEC International Electrotechnical Commission

IFIR Interpolated FIR

IIR Infinite Impulse Response

List of Abbreviations

ILA Individual Level AveragingINL Integral Non-LinearityISI Inter Symbol Interference

ISO International Standardizing Organization

JTF Jitter Transfer Function

LF Low Frequency

LFSR Linear Feedback Shift Register LPCM Linear Pulse Code Modulation

LSB Least Significant Bit

MAC Multiplier Accumulator

MASH Multi stAge noise-SHaping

MOS Metal Oxide Semiconductor

MSB Most Significant Bit

MSE Mean Square Error

NOL Non-Overloading

NOS Non-Oversampling

NRZ Non Return to Zero

NTF Noise Transfer Function

OF Output Feedback

OSR Oversampling Ratio

PCM Pulse Code Modulation

PDF Probability Density Function

PDM Pulse Density Modulation

PLL Phase Locked Loop

PRNG Pseudo Random Number Generator

PSD Power Spectral Density

PWM Pulse Width Modulation

RCF Reconstruction Filter

REQ Re-Quantizer (or: Re-Quantization)

RMS Root Mean Square ROC Region of Convergence

RZ Return to Zero

SACD Super Audio Compact Disc

SC Switched Capacitor

SFDR Spurious Free Dynamic Range

SJNR Signal to Jitter Noise Ratio

SMNR Signal to Mismatch Noise Ratio

SNDR Signal to Noise and Distortion Ratio

SNR Signal to Noise Ratio

SP-DIF Sony/Philips Digital Interface Format

SPL Sound Pressure Level

SQNR Signal to Quantization Noise Ratio SSNR Signal to Switching Noise Ratio

STF Signal Transfer Function THD Total Harmonic Distortion

THD+N Total Harmonic Distortion and Noise

TNSM Trellis Noise-Shaping Modulator

VLSI Very Large Scale Integration

VO Vector Quantization

### **Chapter 1**

### Introduction

### 1.1 Hearing and Audio Quality

When Edison invented the phonograph in the 1870s [1], he probably didn't envision what a major industry the recording, conservation and reproduction of music would become. Advances in technology have steadily increased the performance as well as availability of reproduced sound, and a listener can now fit an entire music library in transparent quality into his pocket.

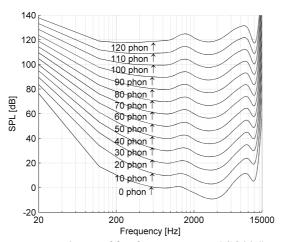

In development of audio technology, the qualitative context is represented by understanding and knowledge of the human auditory system and its properties. Fletcher and Munson did important early work in quantifying the bandwidth and sensitivity of the human hearing [2], which resulted in the equal loudness contour and the *phon* denomination of perceived loudness. The Fletcher-Munson curves were later revised as the Robinson-Dadson curves [3], which became the basis of the ISO226 equal loudness standard.

Figure 1 shows the equal loudness curves according to ISO226. The 0-phon curve is known as the *threshold of audibility* and the 120-phon curve as the *threshold of pain*. The span between these two thresholds is generally acknowledged as the usable *dynamic range* of the human auditory system. It thus represents a measure for the desirable dynamic range in audio equipment. The y-axis is the absolute SPL in dB relative to a reference of 20µPa RMS.

Figure 1: Equal loudness contours (ISO226)

In the frequency range of approximately 2kHz to 5kHz, called the midrange, the dynamic range exceeds 120dB. It is well maintained into the lower (bass) and higher (treble) frequency regions, but below 100 Hz and above 10 kHz it reduces significantly. The bandwidth of the hearing will vary from person to person, but the normal convention is to assume 20Hz to 20kHz for young, healthy people. Studies exist though suggesting that the way we perceive the timbre of a sound is affected by significantly higher frequencies than this [4]-[5]. Many musical instruments also have larger bandwidth than 20kHz [6].

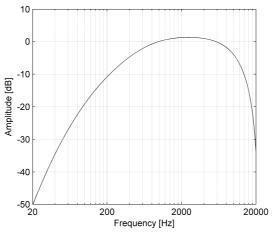

Because of the large variation with frequency in our hearing sensitivity, uniform frequency weighting can give misleading figures when measuring audio quality. A widely accepted frequency weighting norm for sound measurement is the so-called A-weighting function (IEC/CD1672), which approximates the inverse of the 40-phon curve using six poles and four differentiating zeros. The frequency response of the standardized A-weighting function is shown in fig.2.

Figure 2: A-weighting function (IEC/CD 1672)

A-weighting is frequently used in specification and measurement of audio equipment including audio data converters. For instance noise is often A-weighted when measuring SNR. A predominantly white noise spectrum is reduced in power by around 3dB in the range 20Hz to 20kHz from A-weighting, meaning A-weighted SNR values are approximately 3dB better than unweighted ones, given white or predominantly white noise and this bandwidth. Based on the known characteristics of the human auditory system, the ARA commission in 1995 suggested that a high resolution audio carrier capable of full transparency should have at least 120dB dynamic range and 26kHz usable bandwidth [7]. It should be noted though that terms like "transparency" and "audio quality" are subject to an ongoing dispute between two lairs – the so-called "objectivist" and "subjectivist" factions – within the hi-fi community [8]. The "subjectivists" are generally sceptical to the authority of empirical data, and will often use arguments of solipsist and/or panpsychist nature to contend the truisms of established science. As a scientific document this thesis is founded in the "objectivist" point of view without any further discussion thereof.

### 1.2 A Brief Historical Review of Digital Audio

When audio entered the digital world where storage and processing capabilities increase exponentially with time as predicted by Moore [9], it rapidly became feasible to process digital audio carriers exceeding the transparency requirements defined by ARA. Practical considerations and standardization efforts have however led to a more erratic increase in de facto performance than the feasibility limits governed by Moore's Law.

Digital audio was brought to the consumer with the introduction of the Compact Disc audio playback system in the early 1980s [10]. Marketed under the pretentious slogan "*Perfect Sound Forever*", the CD-format offered 20kHz bandwidth and 96dB dynamic range in stereo. The first commercial CD-players; Sony CDP101 (Japan) and Philips CD100 (Europe), featured around 90dB dynamic range.

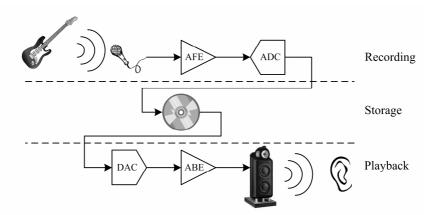

A complete digital audio chain will look approximately like fig.3. An instrument emits sound to an acoustoelectric transducer or microphone and the resulting electric signal is amplified and filtered by an AFE. It is then converted to digital data with an ADC, before the data is stored on a CD or other digital audio medium. During playback the medium is read and output data is transformed back to an analog signal with a DAC, amplified and filtered by an ABE and converted to sound through an electroacoustic transducer or loudspeaker. Ideally this entire process should be audibly transparent.

Figure 3: Digital audio recording and playback chain

It is well known that the electroacoustic transducers introduce more distortion than the other elements in the chain. Nevertheless the development process usually aspires to achieve *local transparency*, so that the component in question can be disregarded as an error source when evaluating the system. The CD-format's transparency is questionable both in terms of dynamic range and bandwidth, and its limitation to two channels makes spatial transparency unobtainable [11]. Still the CD-system has proved to be very resilient. Part of the reason for this must be attributed to the fact that it took many years before converter technology reached a level where ADC and DAC performance approached the fundamental limits of the format.

Entering the 1990s, the effective resolution of ADCs and DACs began to reach a plateau where the CD-format itself limited the performance of the ADDA process [12]. This led to an emerging demand of and research activity into higher resolution carriers, including the mentioned ARA study. By the turn of the century, two competing bids for the next generation audio carrier were launched: Philips and Sony – the companies behind the CD success – fronted the SACD [13] as its heir, whereas the working group behind the then already highly successful DVD video standard promoted the audio-specific DVD-A [14].

SACD is based on DSD; a radical 1-bit noise-shaped storage format theoretically facilitating the abolition of non-linear ADC and DAC units. It features 120dB dynamic range and 100kHz bandwidth in up to six channels. The DVD-A format uses more conventional 24-bit LPCM storage and offers a theoretical dynamic range of 144dB. The bandwidth can be up to 96kHz in two channels or 48kHz in five channels. Double-blind listening tests have failed to prove any audible differences between the two formats [15] and both have fundamental performance limits well beyond what is achievable with current converter technology. Still, despite their high promises and impressive technological potential, the DVD-A and SACD formats have both failed to gain mass-market appeal [16]. This coincides with severe problems for the music business as a whole; as the internet media revolution threatens to put both hi-res audio and the conventional recording industry out of contention [17].

From an engineering point of view, internet music shifted the prime focus of digital audio research. Since internet lines offer limited bandwidth the emphasis has been moved to *compression* and optimization of quality versus data-rate trade-offs, using sophisticated quantization and coding methods based on perceptual modelling of the auditory system [18].

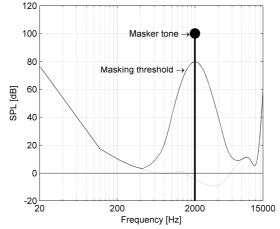

Perceptual coding algorithms vary in complexity, but all are fundamentally based on the ear's *masking property*; that loud sounds overwhelm weaker sounds and render them inaudible. The hearing has both temporal, spatial and frequency based masking properties that have led to some quite sophisticated models and compression formats. This is only tangentially relevant to data converter design and the only masking property touched upon in this thesis is simultaneous or frequency masking: The hearing threshold depends greatly on the distance in frequency to a strong signal component or "masker", which is illustrated in fig.4. Consequently the spectral properties affect the severity of many distortion mechanisms. Distortion audibility will depend on the distance to maskers as well as the harmonic coherence of the distortion spectrum [19].

Modern computer based compressed audio formats are generally scalable, and with rapid increase in network and storage capacity high bandwidth transfer is gaining in popularity. Combined with advances in the sophistication of perceptual compression routines, the dynamic range and bandwidth limitations are catching up to SACD and DVD-A levels. This means that converter technology is again becoming the limiting factor of the ADDA process.

Figure 4: Conceptualization of simultaneous masking

As part of the digital audio history, growing concerns among both consumers and mastering engineers about the so-called "loudness war" [20] should also be mentioned. The omnipresence of reproduced music has led to a move from record labels to increase the nominal volume in recordings. The intention of doing so is to make a record stand out in the plethora of airwave broadcasts and marketing, since people will notice a sound quicker if it is loud. This means that the high dynamic range of modern digital formats is often not utilized. Unfortunate as it may be this is however not related to the capabilities of converter or digital format technology per se, and is thus only mentioned in the introduction for its contextual and historical relevance.

### 1.3 Organization of This Thesis

In the introduction, the motivation for the work has been epitomized, based on a brief review of some fundamental psychoacoustic limitations and a historical retrospect of digital audio. The next chapter will bridge this with fundamental data converter theory. It reviews the processes of sampling and quantization, as well as DA conversion and what waveform errors will typically be introduced by a DAC circuit. This chapter will also establish the case for using oversampled conversion and delta-sigma modulation in audio.

Following this, the third chapter moves on to explore the DSM and its properties. The history of delta-sigma modulation as well as principles and complications surrounding its implementation are reviewed. The concepts of stability and loop filter design are introduced, and the chapter also takes a brief look at some more recent structures and why they are used. The reader should through this gain a pragmatic understanding of delta-sigma.

The fourth chapter deals with static DAC errors and how these will limit the performance of the DA conversion process. It introduces DEM and the notation used in the fourth paper to argue for a simple estimation method to predict errors in generic DEM DACs. In addition to traditional rotation based DEM, it also explains the reasoning behind some alternative structures that have been introduced in more recent times.

The fifth chapter deals with dynamic DAC errors and how these will limit the performance of the DA conversion process. Since dynamic errors are waveform dependent, it means they will be strongly affected by the output sample sequence from the delta-sigma modulator. This sequence is generally impossible to predict analytically, but the chapter shows how its spectral properties can be used to create dynamic error estimates. This chapter has significant overlap with the contents of paper four, but was included in the monograph to make it appear more complete and coherent.

The monograph is primarily intended to provide an overview with a unified notation of the subjects touched upon in this Ph.D. project work. Having read it, the reader should be provided with the foundation necessary for a general understanding of the papers, their relevance and what their contributions constitute. The papers are themselves the main contribution; their contents having been briefly reviewed in the abstract. They are to be found in appendixes two to seven, whereas the first appendix reviews the DFT and discrete time spectral analysis of finite length signals. Such analysis is used in most converter performance evaluations, both in this work and generally, and it is therefore important to understand the properties of the DFT and the limitations and pitfalls in finite length spectral analysis.

### **Chapter 2**

### **Fundamental Theory**

In this chapter basic data converter theory is reviewed; it is described how data conversion works and what fundamental limitations and practical errors are inherent in ADC and DAC processing. They must be assessed in the context of sound perception as reviewed in the first chapter, forming the cognitive basis for understanding the thesis and its contents.

### 2.1 Sampling and Reconstruction

The fundament for digital signal processing was to a large extent made with the breakthrough discovery of the sampling theorem. It was implied as early as 1928, through the derivation by Harry Nyquist [21] that a system of bandwidth B could transmit independent pulse samples at a rate 2B. Nyquist's work focused on transmission capacity and did not consider sampling and reconstruction of continuous-time signals as such. The now obvious duality of Nyquist's discovery – the theory of how any continuous-time signal can be sampled with no loss of information given a sampling frequency of at least twice its bandwidth – was first formulated by Soviet information theory pioneer Vladimir Kotelnikov in 1933<sup>1</sup> [22] and made known to the larger international scientific community through Claude Shannon's legendary 1948 publication "A Theory of Communication" [23]. Shannon formulated the theorem in "A Theory of Communication", and gave its proof and coined the term "sampling theorem" in his 1949 follow-up paper "Communication in the Presence of Noise" [24]. These two papers are generally acknowledged to be in large part the origin of modern information theory and digital signal processing, and Shannon is renowned as "the father of information theory". The sampling theorem is also often called Shannon's sampling theorem and sometimes – incorrectly – Nyquist's sampling theorem. The bandwidth limit at half the sampling frequency for any sampled signal is known – rightfully – as the Nyquist frequency.

### 2.1.1 Sampling

In order to enable a digital representation of a signal, samples must be taken for which to assign data values. The signal is measured at a fixed interval  $T_s$  hereafter called the sampling period. The inverse of the sampling period is known as the sampling frequency or  $f_s=1/T_s$ .

Figure 5: Sampling of a continuous-time signal

<sup>&</sup>lt;sup>1</sup> Whittaker arguably gave the theorem first, implicitly [25]. History enthusiasts may enjoy the IEEE anniversary review [26].

Sampling is illustrated with a simple sinewave in fig.5. From the figure it is seen that in mathematical terms sampling is the multiplication of the input signal with a string of Dirac pulses at all integer multiples of the sampling period  $T_s$ . The mathematical description of this operation is given by:

$$x[n] = x(t) \cdot \sum_{n = -\infty}^{\infty} T_s \cdot \delta(t - nT_s). \tag{1}$$

With the Fourier transform  $\mathfrak{F}$  – its definition and use assumed familiar to the reader – an expression for the sampled signal frequency spectrum  $\mathfrak{F}\{x[n]\}$  can be found as a function of the continuous signal frequency spectrum  $\mathfrak{F}\{x(t)\}$ :

$$X_{s}(f) = \mathfrak{F}\left\{x[n]\right\}$$

$$= \mathfrak{F}\left\{x(t) \cdot \sum_{n=-\infty}^{\infty} T_{s} \cdot \delta(t - nT_{s})\right\}$$

$$= \sum_{n=-\infty}^{\infty} \mathfrak{F}\left\{x(t) \cdot e^{i2\pi nf_{s}t}\right\}$$

$$= \sum_{n=-\infty}^{\infty} X(f - nf_{s}) , X(f) = \mathfrak{F}\left\{x(t)\right\} .$$

(2)

It is seen from this result that sampling gives a spectrum repeating around multiples of  $f_s$  as illustrated in fig.6. From both the equation and the figure it is now understood how having the sampled signal x bandlimited to below  $f_s/2$  – the Nyquist frequency – is a requirement for preservation of its spectral integrity. If the repeated spectra – known as *aliases* – are removed during DA conversion, the ideal ADDA process leads to an output identical to its input.

Figure 6: a) Continuous spectrum b) Sampled spectrum c) Alias distortion

If the signal bandwidth on the other hand exceeds the Nyquist frequency, or analogously that  $f_s$  violates the sampling theorem, the aliases will overlap as illustrated in fig.6c). Spectral integrity is then lost in the overlap region. In fact *any* energy content residing above the Nyquist frequency at the point of sampling will create an alias below it. It is known as *alias distortion* or just *aliasing*. From this it is given that unless the input to an ADC is limited strictly below the Nyquist frequency, alias distortion will compromise its performance. It is thus necessary to ensure that as little energy content as possible violating the sampling theorem enters the ADC. This is done by using an *antialias filter* before sampling to suppress any energy that may exist above  $f_s/2$ . The necessary damping of this filter is determined by the expected amount of out-of-band energy and the required level of signal integrity preservation in the baseband.

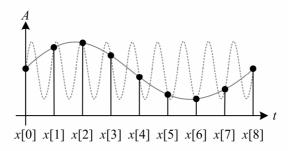

An intuitive way to understand *why* sampling produces a repetitive spectrum is to look at fig.5 and acknowledge that other high frequency sinewaves can be defined by the *exact same* sequence of samples. Thus the sample sequence contains information of many waveforms. Figure 7 shows two sinewaves giving exactly the same sample sequence. If the high frequency sinewave was the one sampled to generate this sequence, obviously in violation of the sampling theorem, reconstruction would form its low frequency alias from the samples.

Figure 7: Sampled waveform of fig.5 and an alias

Schematically the sampling process can be seen as an AAF followed by a sampling network or an ADC. The desired input signal, filtered to conform to the sampling theorem and entering the sampler, is in this thesis denoted as x(t).

Figure 8: Conceptual ADC and AAF

Since the sampled spectrum is repetitive around  $f_s$ , and since processing the sampled signal does not necessarily imply any a priori knowledge of the sampling frequency, the sampled waveform is more conveniently expressed through its angular frequency  $\omega$  defined as:

$$\omega = \frac{2\pi f}{f_c}.$$

(3)

Then it is given from the derivation of the sampling theorem that the frequency spectrum of the discrete sequence can be rewritten as:

$$X_s(\omega) = \sum_{n=-\infty}^{\infty} x[n] \cdot e^{-i\omega n}.$$

(4)

This result is the normal definition of the DTFT. It is also valid for finite length sequences as the (finite) DFT. The simulated spectra presented in this thesis and associated papers are of course of finite length and found by DFT calculation on finite sequences. The DFT may if not used carefully have incongruities due to the Gibbs phenomenon, which can be alleviated with windowing or coherent sampling as reviewed in Appendix 1. A generalization of the DTFT is given by the *z*-transform:

$$X_s(z) = \sum_{n = -\infty}^{\infty} x[n] \cdot z^{-n} \quad , z = r \cdot e^{-i\omega n}.$$

(5)

It is seen that the DTFT is identical to the z-transform for r=1, or evaluation along the unit circle in the complex plane. Although introduced for completeness, it is assumed that the reader has prior knowledge of the fundamental properties for the z-transform and related terms such as unit circle, poles, zeros and ROC.

#### 2.1.2 Reconstruction

In the DAC process, the sample sequence must be transformed back to an analog continuous time waveform. Ideal reconstruction, i.e.  $x_{out}(t) \equiv x_{in}(t)$ , would imply removing *all* spectral content above the Nyquist frequency and retain all spectral content below it. This requires an infinitely steep reconstruction filter which is not feasible to implement. Rather, a real-life RCF is specified from how much high frequency alias energy is tolerable at the output. The RCF is typically placed outside the DAC chip as shown in fig.9. The DAC converts sample data into a continuous time waveform which is then low-pass filtered to approximate the original input. The DAC output has been given its own denotation y(t). Since this thesis deals primarily with issues in DAC design, the nature of y(t) is of essential interest and will be paid special attention in the theory introduction.

Figure 9: Conceptual DAC and RCF

The typical way of constructing y(t) is to connect the output to a current or voltage proportional to the sample value and hold it over the duration of the sample period. In other words the output is defined as:

$$y(t) = x[n] \quad , nT_s \le t < (n+1)T_s.$$

(6)

This ensures that the output is in principle linearly proportional to the input signal x. The hold reconstructed waveform can also be described as the time convolution of the sample sequence and a rectangular window:

$$y(t) = \sum_{n=-\infty}^{\infty} x[n] \cdot \frac{1}{T_s} \cdot \text{rect}\left(\frac{t - nT_s}{T_s} - \frac{1}{2}\right), \text{ rect}\left(\frac{t}{T}\right) \stackrel{def}{=} \begin{cases} 1, \frac{-T}{2} < t \le \frac{T}{2} \\ 0, \text{ otherwise} \end{cases}$$

(7)

The resulting output from the DAC described in (7) is shown in fig.10 for a sinusoidal sample sequence. This is the well-known "stair-case" output waveform.

Figure 10: Output waveform from PCM DAC

The frequency spectrum of this output waveform is found by taking the Fourier transform of the time domain expression (7). Since it is known that convolution in the time domain equals multiplication in the frequency domain this is relatively simple:

$$Y(f) = \mathfrak{F}\{y(t)\}\$$

$$= \mathfrak{F}\{x[n]\} \cdot \mathfrak{F}\left\{\frac{1}{T_s} \cdot \operatorname{rect}\left(\frac{t}{T_s} - \frac{1}{2}\right)\right\}\$$

$$= X_s(f) \cdot \left\{\frac{1}{T_s} \cdot \int_0^{T_s} e^{-i2\pi f t} dt\right\}\$$

$$= X_s(f) \cdot e^{-i\pi \frac{f}{f_s}} \cdot \operatorname{sinc}\left(\frac{f}{f_s}\right).$$

(8)

According to usual signal processing notation, the normalized sinc-function is defined as:

$$\operatorname{sinc}(x) \stackrel{\text{def}}{=} \frac{\sin(\pi x)}{\pi x} \ . \tag{9}$$

Hold reconstruction in other words performs first order sinc-filtering of the sampled spectrum. This means that the aliases are suppressed somewhat, but also that there is some inband attenuation below the Nyquist frequency. This is typically compensated for at the digital side of the DAC.

Figure 11: Hold reconstruction filtering effect

Current steering and DCT switch-cap DAC circuits, used in most audio DAC implementations, will both provide this type of waveform. The aliases are suppressed further, or analogously the "stair-case" is smoothed, through the external RCF. There also exist other types of reconstruction, some of which will be touched upon later.

#### 2.2 Quantization

Digitization of a signal is a two-step process. After the signal is sampled, the samples must be given a data representation. The process of mapping samples to a finite set of data values is known as quantization. The most common method is scalar quantization, where each sample x[n] is mapped to one in a range of values  $Q(x) \in \ell$ ;  $\ell$  being a scalar set that is typically integer. Another possibility is to map an input vector  $\mathbf{x} = [x[1], ..., x[N]]$  to one in a set of output vectors  $Q(\mathbf{x}) \in \mathfrak{R}^N$ , where  $\mathfrak{R}^N$  is an N-dimensional vector space; called N-dimensional vector quantization. This thesis deals only with uniform scalar quantization which is used in practically all data converter applications.

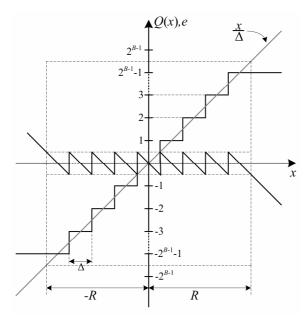

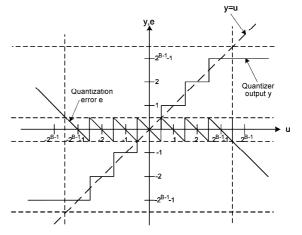

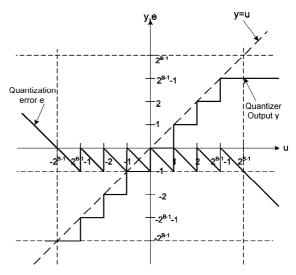

A scalar quantizer defined by  $\ell$  being the integer set  $\{-2^{B-1}-1...-1,0,1...2^{B-1}-1\}$ , can be realized with a B bit binary output. It is hence called a B-bit quantizer. Mapping the input to the nearest integer in  $\ell$  can be done by rounding:

$$Q(x) = \left\lfloor \frac{x}{\Delta} + \frac{1}{2} \right\rfloor_{Q(x) \in \ell} . \tag{10}$$

This is a symmetric or mid-thread quantizer which has  $M=2^B-1$  levels when it is B-bit. A B-bit quantizer can also have  $M=2^B$  integer levels if it is made asymmetric. The denotation  $\Delta$  is used for the *input-referred quantizer step-size*. It is shown graphically in fig.12 together with the quantization error e, which is the deviation of Q(x) from x. It is seen that the error is constrained to  $|e| \le 1/2$  – or input-referred to  $|e| \le \Delta/2$  – as long as the output is within a range of  $2^B$ . The corresponding input range  $|R| \le (2^{B-1}-1/2) \cdot \Delta$  is the input *non-overload range*.

Using Nyquist sampling and uniform scalar quantization to digitize signals is known as Linear Pulse Code Modulation and the resulting data as LPCM or just PCM samples [27]. This is the original and most direct/intuitive approach to signal digitization, but as will shortly become clear other modulation schemes can be used.

Figure 12: Uniform scalar mid-thread quantizer

The quantization error is a not a continuous function of the input signal, but has discontinuities making it difficult to analyze. In his classic paper Bennett showed that under certain conditions the quantization error can be approximated as an additive noise source, uniformly distributed in the range  $\pm \Delta/2$  [28]. The conditions he stipulated were that the quantizer had a large input range large compared to  $\Delta$  and that the input signal was active over significant parts of this range without overloading it. He proved the approximation to be asymptotically correct for a Gaussian input distribution as  $\Delta \rightarrow 0$ , and showed through simulations it was a valid approximation for sampled and quantized sinusoids spanning over an amplitude range of many  $\Delta$ . Denoting the error PDF as  $f_e(e)$  it can be written as:

$$f_e(e) = \begin{cases} \frac{1}{\Delta} &, -\frac{\Delta}{2} < e \le \frac{\Delta}{2} \\ 0 &, \text{ otherwise} \end{cases}$$

(11)

From (11) the first two statistical moments of the error - i.e. the input-referred mean and variance - are given by:

$$E(e^{m}) = \int_{-\infty}^{\infty} e^{m} \cdot f_{e}(e) \cdot de \rightarrow \begin{cases} E(e) = 0 \\ E(e^{2}) = \sigma_{e}^{2} = \frac{\Delta^{2}}{12} \end{cases}$$

(12)

If the quantizer is *B*-bit its total input non-overload range is  $2^B \cdot \Delta$ . The highest level input sinewave that doesn't overload it is hence  $x[n]=2^{B-1}\cdot\Delta\cdot\sin(\omega n)$ , and its power  $\sigma_x^2=2^{2B}\cdot\Delta^2/8$ . The peak SQNR for sinusoid input is consequently:

$$SQNR_{\text{max}} = 10 \cdot \log_{10} \left( \frac{\frac{2^{2B} \cdot \Delta^2}{8}}{\frac{\Delta^2}{12}} \right) = 6.02B + 1.76 \text{ [dB]}.$$

(13)

This is the well known "6dB per bit rule" also used to calculate ENOB. Bennett in the same paper also showed that if the input signal had a smooth power spectrum, the error samples would be approximately orthogonal. Then the error autocorrelation function is given by<sup>2</sup>:

$$r_{ee}(k) \stackrel{def}{=} E(e[n] \cdot e[n-k]) \approx \begin{cases} \sigma_e^2 & , k = 0\\ 0 & , \text{ otherwise} \end{cases}$$

(14)

Using the Wiener-Khinchin theorem the error power spectral density is found to be:

$$S_e(\omega) = \frac{1}{2\pi} \cdot \mathfrak{F}\left\{r_{ee}(k)\right\} = \frac{\sigma_e^2}{2\pi} \,. \tag{15}$$

Widrow [29] extended the work of Bennett by applying sampling theory to the quantizer to find a statistical model for an *arbitrary* input PDF. This enabled Widrow to find the criteria for conditional input independence in any statistical moment of the quantization error. While the input PDF is a continuous function, the output has discrete probabilities in the value set  $\ell$ , or input-referred in multiples of  $\Delta$ . This means that the output PDF is an area sampled version of the input PDF with "sampling frequency"  $\phi_q = 1/\Delta$ . The probability for the output to take any discrete level is given by the cumulative input PDF within  $\pm \Delta/2$  of this level.

Figure 13: Quantizer input PDF (a) and output PDF (b)

For simplicity of notation, the quantizer output Q(x) is denoted q in the figure and in the text from here on. The discrete PDF of the quantizer output becomes:

$$f_{q}(q) = \sum_{n=-\infty}^{\infty} \delta(q - n\Delta) \cdot \int_{n\Delta - \Delta/2}^{n\Delta + \Delta/2} f_{x}(x) \cdot dx$$

$$= \sum_{n=-\infty}^{\infty} \delta(q - n\Delta) \cdot \left[ \operatorname{rect}\left(\frac{q}{\Delta}\right) * f_{x}(q) \right].$$

(16)

The definition of the rectangular window is the same as before. Similar to the derivation the sampling theorem, Widrow took the Fourier transform of the discrete output PDF to find:

<sup>&</sup>lt;sup>2</sup> This is the discrete time definition of the autocorrelation function. Bennett used continuous time analysis to show the error had approximately zero autocorrelation in two arbitrary time instants t and  $t+\tau$ , thus the error PSD of a sampled and quantized process would be white.

$$\Psi_{q}(u) \stackrel{def}{=} \mathfrak{F}\left\{f_{q}(q)\right\}$$

$$= \sum_{n=-\infty}^{\infty} \Psi_{x}\left(u - \frac{n}{\Delta}\right) \cdot \operatorname{sinc}(\Delta u - n) .$$

(17)

The Fourier transform of a PDF is known by definition as the *characteristic function*. The CF is periodic and sinc-weighted similar to the spectrum of a signal sampled and reconstructed with hold reconstruction. To avoid PDF "aliasing", the input CF must be zero above  $1/(2\Delta)$ . If so the input PDF is merely convoluted with a rectangular window of width  $\Delta$ , equalling the Bennett approximation of an additive error with rectangular PDF. A large Gaussian PDF converges towards such a CF, confirming Bennett's conditions.

Widrow however went further and found a requirement for conditional independence in any statistical error moment. Any moment can by found by differentiating the CF at the origin:

$$E(q^{m}) = \int_{-\infty}^{\infty} q^{m} f_{q}(q) \cdot dq = \left(\frac{\mathbf{i}}{2\pi}\right)^{m} \cdot \frac{d^{m}(\Psi_{q}(u))}{du^{m}}\bigg|_{u=0}$$

$$= \left(\frac{\mathbf{i}}{2\pi}\right)^{m} \cdot \frac{d^{m}\left(\sum_{n=-\infty}^{\infty} \Psi_{x}\left(u - \frac{n}{\Delta}\right) \cdot \operatorname{sinc}(\Delta u - n)\right)}{du^{m}}\bigg|_{u=0}$$

$$(18)$$

If the requirement for no PDF aliasing is fulfilled, the  $m^{th}$  output moment equals the  $m^{th}$  input moment plus a constant. But there is also a weaker condition: The assumption that:

$$\frac{d^{m}\left(\Psi_{x}\left(u\right)\cdot\operatorname{sinc}\left(\Delta u\right)\right)}{du^{m}}\bigg|_{u=\frac{n}{A}}=0\quad,\,n\neq0\quad,\tag{19}$$

leads to the following simplification of (18):

$$E(q^{m}) = \left(\frac{\mathbf{i}}{2\pi}\right)^{m} \cdot \frac{d^{m}\left(\Psi_{x}(u) \cdot \operatorname{sinc}(\Delta u)\right)}{du}\bigg|_{u=0}$$

$$\to E(q) = E(x) \qquad (20)$$

$$\to E(q^{2}) = E(x^{2}) + \frac{\Delta^{2}}{12}$$

It follows from (20) that the error is conditionally independent and additive in its statistical moment m if (19) is fulfilled for the m<sup>th</sup> derivative. Of course this cannot be ensured with the lack of any a priori knowledge of the input statistics, but as will be seen shortly one can force this condition to hold in any given statistical moment by applying *dither*.

The reader should be aware that since both Bennett's and Widrow's methods are statistical methods, validity is limited to cases of static input PDF and they are not telling of the dynamic behaviour of the quantization noise. Many studies have been made on the dynamic characteristics of quantization noise that would make for a very extensive review. Interested readers are recommended to take a look at Gray's comprehensive survey paper [30] and its references for an overview.

### 2.3 Oversampling

Oversampling is a technique that has become invaluable in high resolution, low bandwidth converters. DAC oversampling is helpful in making the RCF design easier and it also gives a *processing gain* allowing re-quantization to fewer bits. One of the earliest papers on oversampled DA conversion was published in 1974 [31], and a patent was filed in 1981 [32]. Oversampling DACs have been used in most digital audio units all the way back to the Philips CD100 which had an OSR of 4.

Looking first at the ADC; sampling with a rate far higher than twice the signal bandwidth can be of benefit for several reasons. First and foremost one can use a much simpler AAF. Since the sampled spectrum is periodic in  $f_s$ , the transition band of the AAF can range from  $f_b$  to  $f_s$ - $f_b$ , where  $f_b$  is the signal bandwidth limit. An increase in  $f_s$  in other words relaxes the requirements for the AAF by making the transition band wider, and designing a high performance AFE becomes much easier. Using the Bennett approximation for quantization noise, it is also found that the total in-band noise power – being the quantization error PSD in (15) integrated over the input Nyquist range – decreases proportionally to the OSR. If the sampling rate is increased so that  $f_s = f_s$  in E, the in-band quantization noise power is:

$$\hat{\sigma}_e^2 = \int_{-\pi/L}^{\pi/L} S_e(\omega) d\omega = \frac{\sigma_e^2}{L} . \tag{21}$$

The signal-band SQNR as a function of the number of bits is consequently given by:

$$SQNR_{\text{max}} = 10 \cdot \log_{10} \left( \frac{\sigma_{x}^{2}}{\hat{\sigma}_{e}^{2}} \right)$$

$$= 6.02B + 1.76 + 10 \cdot \log_{10} (L) \text{ [dB]} .$$

(22)

It follows from (22) that for each doubling of L one can reduce B by half a bit and get the same SQNR. If L=256 four bits are saved, making ADC design simpler.

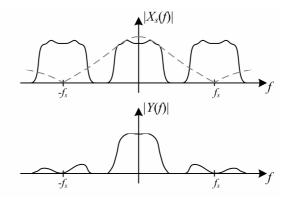

In a DAC the advantages of oversampling isn't as intuitively appreciated, but the same fundamental mechanisms apply. The space between aliases can be extended by first increasing the sample rate or zero-pad the signal and then low-pass filter it. This is the same as *interpolation* and it is shown in the time-domain as well as the frequency domain in fig.14. When the aliases are moved apart like this, the requirements for the analog RCF are greatly relaxed. In essence it means that the burden of filtering unwanted energy is moved from the analog to the digital domain. Digital filter implementations are much more flexible, much cheaper and have much higher performance than their analog counterparts.

Design of oversampling filters is a large field within DSP and is not reviewed in detail in this thesis. Unlike general purpose digital filters, oversampling filters are typically FIR filters since they can then be implemented very efficiently in a polyphase filter structure [33]. In audio applications the oversampling filter will typically be realized as several cascaded stages of halfband filters [34] or as IFIR filters [35], using a multiplier-accumulator realization [36]. For more insight in the design of oversampling filters the reader is recommended to read a textbook covering the subject, e.g. Mitra's "Digital Signal Processing" [37] chapter 13.

Figure 14: DAC oversampling in the time and frequency domains

With DAC oversampling the same processing gain as for the ADC will also apply to any *post-oversampling* quantization operation. This means it is possible to use a REQ to reduce the number of bits while maintaining a high effective resolution. This is shown in fig.15.

Figure 15: Oversampling DA-converter with REQ

Any noise or distortion inherent in x[n] is to be regarded as part of the input signal for all succeeding processing blocks, meaning it is not reduced when oversampling. But by using oversampling, errors introduced *after* the sampling rate is increased may be spread over a larger frequency range. This is significant especially for the quantization error, which has inband noise power as given in (21). For instance a REQ can have a 12-bit arithmetic output, but with an OSR of 256 have 16 bits effective resolution. The DAC then needs to resolve  $2^{12}$  levels instead of  $2^{16}$ , meaning its implementation will be much simpler. It must however be stressed that any in-band error introduced by the DAC must still be at a 16-bit level. It is only its number of elements that are reduced; the requirements for DAC in-band noise density, DAC linearity and so forth still remain the same.

### 2.4 Dithering

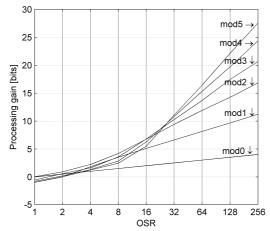

As mentioned in the section on quantization, it is possible to exploit the weaker condition of CF derivatives being zero in multiples of the quantization "frequency" to obtain conditional input independence in any error moment of choice. This is done by adding dither; a small, independent noise-source that applied to the input of the quantizer as shown in fig.16.

In the figure an additional signal v is added prior to the quantizer. Here the quantizer is a REQ used in re-quantizing DACs, meaning that the input and dither signals are generated digitally. If the input is assumed to have so high resolution compared to  $\Delta$  that it can be approximated as continuous amplitude, a DAC with digital input and dither can be regarded as equivalent to an ADC with analog input and dither.

Figure 16: Dithered quantization

The first use of applied noise in quantization was seen in a 1962 publication on low-resolution image digitization [38], while the term dither was established two years later [39]. Its etymology comes from the word "didder" which means to shiver or shake with cold. The term was coined because the noise was seen to "shake up" perceptually annoying quantization error patterns. In the past, especially with regards to digital audio, there has been some dissension on the nature of dither and requirements for dithering. Results published from the research of Lipshitz, Vanderkooy and Wannamaker [40]-[42] have been very central to the development of an understanding of dither in the audio community. Their work is based on Widrow's statistical model of quantization.

Looking at fig.16, the quantizer input is now w=x+v. The dither signal is assumed statistically independent of the input so the PDF  $f_w$  is simply a convolution of  $f_v$  and  $f_x$ . Eq.(16) rewritten for the dithered case then becomes:

$$f_{q}(q) = \sum_{n=-\infty}^{\infty} \delta(q - n\Delta) \cdot \left[ \operatorname{rect}\left(\frac{q}{\Delta}\right) * f_{v}(q) * f_{x}(q) \right] . \tag{23}$$

Consequently the rewritten CF becomes:

$$\Psi_{q}\left(u\right) = \sum_{n=-\infty}^{\infty} \Psi_{v}\left(u - \frac{n}{\Delta}\right) \cdot \Psi_{x}\left(u - \frac{n}{\Delta}\right) \cdot \operatorname{sinc}\left(\Delta u - n\right) . \tag{24}$$

Going back to (19), we need the  $m^{th}$  derivative of  $\Psi_q$  to be zero at all integer multiples of the quantization "frequency" for the error is to be input independent in its  $m^{th}$  statistical moment. What is now noteworthy is that if *either* of the products in (24) is zero, the whole expression becomes zero. This means that if the dither sequence is made to conform, it does not matter how the input signal behaves. Then the  $m^{th}$  output moment will regardless be given as:

$$E(q^{m}) = \left(\frac{\mathbf{i}}{2\pi}\right)^{m} \cdot \frac{d^{m}(\Psi_{x}(u) \cdot \Psi_{v}(u) \cdot \operatorname{sinc}(\Delta u))}{du^{m}}\bigg|_{u=0}$$

$$\to E(q) = E(x) + E(v) \qquad (25)$$

$$\to E(q^{2}) = E(x^{2}) + E(v^{2}) + \frac{\Delta^{2}}{12}$$

Thus, with dither no a priori knowledge about the statistics of the input signal is necessary. All that has to be done to ensure conditional error independence, is to apply a dither signal where its given CF derivative is zero in all integer multiples of  $1/\Delta$ . As it turns out the sum of N independent random sources with uniform distribution in  $\pm \Delta/2$  has a total CF of:

$$\Psi_{\nu}(u) = \operatorname{sinc}^{N}(\Delta u) . \tag{26}$$

For this function all derivatives from 0 to N are zero in  $u=k/\Delta$  for all k. The dither mean is zero and its variance is  $N\Delta^2/12$ . Using a single random source (N=1) is called RPDF

(rectangular PDF) or 1PDF dithering. Adding two independent sources (N=2) makes  $f_v$  triangular in  $\pm \Delta$  and it is therefore referred to as TPDF (triangular PDF) or 2PDF dithering. A total of N added sources – NPDF dither – will render the first N quantization error moments input independent. Studies suggest that only the first two moments – the mean and the variance – make the error audibly different (from white noise) if they are input dependent [43]. Even very coarse quantization gives no detectability of dependence in the skew, kurtosis or higher error moments. Since additional noise power from the dithering increases with N, TPDF is therefore regarded as optimal dithering in audio.

Figure 17: First two error moments as function of input level

Figure 17 shows through simulations how dither renders error moments conditionally inputindependent. With RPDF dither the error mean is zero implying no distortion of the input signal. With TPDF dither both the error expectance value and the error power is constant over the input range. The average error power is increased from  $\Delta^2/12$  to  $\Delta^2/4$  which needs to be included in SQNR estimation (13). With TPDF dither we in other words have SQNR<sub>max</sub>=6.02*B*-3.01 dB, and it is no longer just an approximation.

### 2.5 Delta-Sigma Modulation

Oversampling gives a nominal processing gain which enables a reduction of the number of bits while maintaining high dynamic range. Its effect in this regard is however limited; since the processing gain as mentioned is one half bit per doubling of the sampling rate. A *substantial* reduction of the number of bits – which is very desirable for complexity reasons – will require an unfeasibly high OSR.

This led to research on modulation alternatives for improvement of the processing gain. The DSM, being an extension of the delta-modulator or differential PCM encoder, was first published by Inose and Yasuda in 1962 [44]. The possibility to use it to improve processing gain in oversampled data conversion was first treated in a 1969 paper by Goodman [45], although a less known patent preceding this work exists that describes in essence the same basic principle [46].

The reader should be aware that both delta-sigma and sigma-delta are commonly used terms for the same process [47]. The causal order of the process suggests delta-sigma whereas the

modulator's functional hierarchy suggests sigma-delta. This thesis uses the original and arguably most used term; delta-sigma modulation.

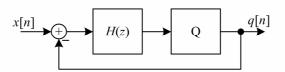

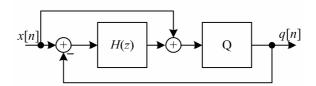

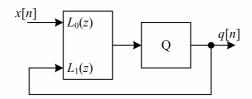

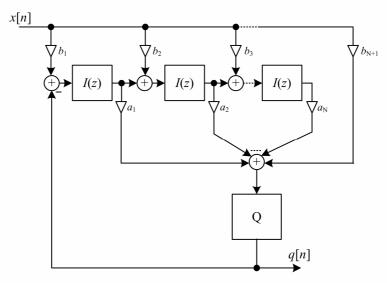

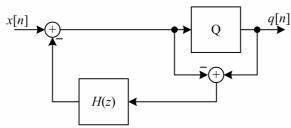

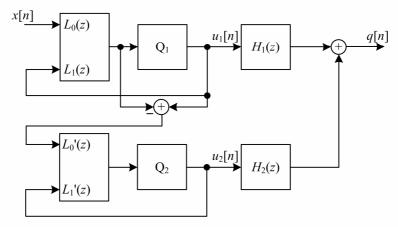

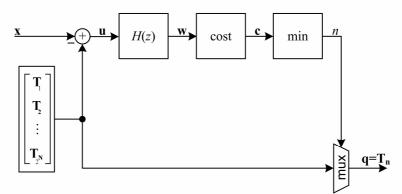

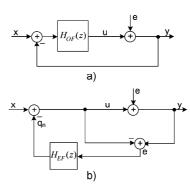

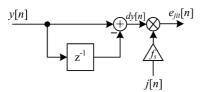

Figure 18: Basic delta-sigma modulator

The basic functionality of a DSM is depicted in fig.18. It uses filtered negative feedback compensation, causing the quantization error to be spectrally shaped. The loop filter H(z) determines the spectral properties of the DSM. Using Bennett's additive noise approximation, the input-output relation of the modulator can be described by the linear sum:

$$Q(z) = \frac{H(z)}{1 + H(z)} \cdot X(z) + \frac{1}{1 + H(z)} \cdot E_q(z)$$

$$= STF(z) \cdot X(z) + NTF(z) \cdot E_q(z) . \tag{27}$$

The closed loop transfer functions of the signal x and quantization error  $e_q$  have been denoted Signal Transfer Function and Noise Transfer Function respectively. It is seen that if H(z) is large, NTF(z) approaches zero and STF(z) approaches unity meaning the signal is preserved while the quantization noise is suppressed. To achieve lowpass modulation the loop filter must be an integrator type function with high gain for low frequencies. Bandpass modulation can be realized by replacing the integrators with resonators having high gain at the frequency band of interest. The output PSD as a result of (27) is:

$$S_{a}(\omega) = S_{x}(\omega) \cdot \left| STF(\omega) \right|^{2} + S_{e}(\omega) \cdot \left| NTF(\omega) \right|^{2} . \tag{28}$$

Remembering the SQNR derivation (12)-(13) it is seen how an appropriate NTF can improve the processing gain since – assuming  $|STF(\omega)|^2 \approx 1$  – the maximum SQNR will be:

$$SQNR_{\text{max}} \approx 10 \cdot \log_{10} \left( \frac{2^{2B}}{\frac{1}{3\pi} \cdot \int_{-\pi/L}^{\pi/L} |NTF(\omega)|^2 d\omega} \right) \text{ [dB]} . \tag{29}$$

An illustration is shown in fig.19, where the shaded area indicates the quantization noise falling in-band. For obvious reasons DSM is also referred to as *noise-shaping*.

Figure 19: Illustration of DSM noise shaping

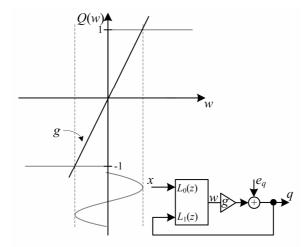

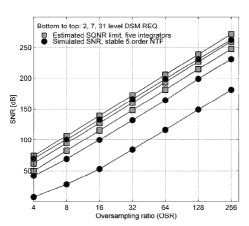

A self-evident condition for realizability is that the DSM has no delay-free loops. Thus it isn't possible to substitute H(z) with a huge gain and expect noise to "disappear". The realizability condition can be formalized as ntf[0]=1 in the time domain or equivalently  $NTF(\infty)=1$  in the z-domain. Maximum error suppression at  $\omega=0$  obviously suggests all NTF zeros should be located at DC or  $z=e^{i0}$ . Both these conditions are fulfilled for any order N if  $NTF(z)=(z-1)^N$ . Often called a basic  $N^{th}$  order DSM or simply a modN in the literature, fig.20 shows processing gain in bits (according to the 6dB per bit rule) vs. OSR for N=0 (only oversampling) to N=5. It is seen that if the order is high, the processing gain is very large.

Using high order DSM with 1-bit REQ quickly became very popular in audio since a 1-bit DAC is guaranteed to have static linearity. The first audio converters were PCM converters [48], but high order 1-bit DSM quickly took over and soon reached a performance level where it in many ways outperformed the fundamental limitations of the 16-bit CD-system [49]. However while the basic functionality of a DSM is very simple, the fact that it is a non-linear feedback system creates issues not apparent when using Bennett's linear model. For instance a mod *N* will be unstable for large input if *N* is higher than two and the REQ is few bits. Because of this the loop filter must be damped, causing a reduction in processing gain. The output of the DSM furthermore affects the DAC performance and its sensitivity to circuit errors. The modulator itself is also susceptible to limit cycles and noise power modulation.

Figure 20: Processing gain of modN DSM

It is extremely complicated to do rigorous mathematical analysis of these non-linear effects and design is often based on simplified rules-of-thumb. An important part of this thesis is to present extensions of the rules-of-thumb, including a wider scope of error sources and enabling easier estimation of performance as a function of DSM design parameters.

#### 2.6 The DAC

This section presents the DAC and gives an introduction to the errors it commonly causes. As will later be seen these errors interact with the DSM REQ and performance estimates can be given if one knows the DSM design parameters.

#### 2.6.1 DAC topologies

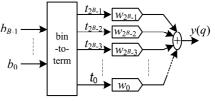

Early DAC implementations – e.g. [48] – were commonly realized as resistor string DACs. An example of a resistor string DAC is shown in fig.21, where the different bits of the binary DAC input data are denoted  $b_0 ext{...} b_{B-1}$ . Depending on whether bit  $b_i$  is one or zero, the switch it

steers is throughout the sample period connected either to ground or to the reference voltage through a corresponding resistor in a binary weighted resistor string. The output voltage is then given by:

$$V_o = R_F \cdot V_{ref} \cdot \left(\frac{b_0}{2R} + \frac{b_1}{4R} + \frac{b_2}{8R} + \cdots\right)$$

$$= \frac{R_F}{R} \cdot V_{ref} \cdot \hat{q} . \tag{30}$$

The DAC input  $\hat{q}$  is the REQ output q offset to unipolar representation, since the DAC uses positive binary values (elaborated in 2.6.2., "DAC encoding").

Figure 21: Resistor ladder type DAC

Use of resistor string DACs gradually lessened because technologies for IC implementation are not very suitable for large resistive devices. The resistor string will use much die area and have poor device matching. Resistor string DACs were eventually superseded by switched capacitor ("switch-cap") DACs. Switch-cap is a technique to realize resistor equivalents through charge transfer in clocked capacitors, first shown in 1977 [50]. It transfers sampled charge packets creating a resistor equivalent  $R_{eq}=1/(C \cdot f_s)$ , and can thus be used to implement continuous amplitude amplifiers or filters with a discrete-time transfer function H(z).

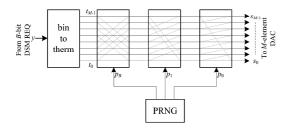

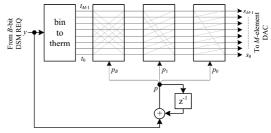

In a typical switch-cap system the output of a functional stage is sampled by the next stage, meaning that only the settled output value matters. But since a DAC output is continuous-time it is very important that a switch-cap DAC settles linearly. It is possible to realize a switch-cap integrator which is insensitive to op-amp slewing and nonlinearity, called a direct charge transfer integrator. It is distinguished by the input capacitor directly depositing charge on the integrating capacitor. The DCT integrator was proposed by Bingham in 1984 [51] and a high performance DCT-based audio DAC was shown in 1991 [52]. Implementations with very high performance [53] and efficiency [54] have been seen since.

A DCT -based switch-cap DAC is shown in fig.22. In the sampling phase  $\varphi_1$  it charges the sampling capacitor array depending on the input sample data, and in the hold phase  $\varphi_2$  it distributes this charge directly to the integrating or hold capacitor  $C_h$ . Evaluating the charge redistribution it is found that the input-output transfer function of this DAC will be given by:

$$H_{DAC}(z) = \frac{V_o(z)}{\hat{Q}(z) \cdot V_{ref}} = \frac{\frac{\sum C_s}{C_h}}{\left(\frac{\sum C_s}{C_h} + 1\right) - z^{-1}}.$$

(31)

Figure 22: DCT integrator SC DAC

The low-pass function of the DCT-based DAC will be of benefit to suppress out-of-band noise from the DSM REQ. With the charge distributed passively between the capacitors, the settling is given by a linear RC time constant of the capacitors and switches, and the circuit is insensitive to op-amp slewing. Distortion is still generated from signal-dependent charge injection and signal-dependent switch resistance variation, which must be alleviated through good circuit design [53]. Still, its properties make the circuit very suitable for DAC use.

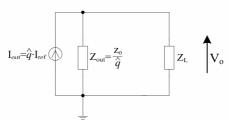

Although the DCT-based DAC still is quite popular in audio converter ICs, it has in recent years started receding. Instead it becomes more and more common for hi-res DACs to have current mode output. Then the DAC generates and holds an output *current* proportional to the input data, which is externally converted to voltage. The chief reason for doing so is that lowered supply voltages in modern IC processes reduce the headroom for SC circuits. This makes it very difficult to implement good switches and opamps, and capacitors must be big to achieve low kT/C-noise. One way to overcome these problems is to operate the DAC IC in current mode and use external I-V conversion with a dedicated high supply opamp or even a discrete transistor stage. Such an arrangement – with an opamp – is shown in fig.23. Here  $I_o = \hat{q} \cdot I_{ref}$  and  $V_o = I_o \cdot R_F$ . In practice the external I-V is often combined with the analog RCF.

Figure 23: Current mode DAC with external I-V conversion

The idea to use steered current sources in DACs is not new [55], but it has been revived in recent times because of the development towards lower voltage IC technologies. The approach shows good potential with very high resolution having been reported [56], and it will probably be the dominant hi-res DAC design paradigm for the foreseeable future. Just like the resistor ladder DAC, the current steering DAC has no discrete time filtering of the output, and performs straightforward hold reconstruction.

#### 2.6.2 DAC encoding

The above examples all show binary encoded DACs where the DAC elements – be it resistors, capacitors or current sources – are weighted as binary digits and fed with binary data from the (DSM) REQ. The base-two numeral system was first described as early as 800 B.C. by Indian mathematician Pingala [57] and Boole in the 19<sup>th</sup> century developed the modern concept of binary logic, the basis for all digital circuit operation [58]. Shannon was first to show automated circuits operating on Boolean logic [59], and in addition to being regarded as the father of information theory he is also widely acknowledged as the originator of digital arithmetic circuits.