# Verification of an AES RTL Model with an Advanced Object-Oriented Testbench in SystemVerilog

Henrik Ruud

Master of Science in ElectronicsSubmission date: January 2007Supervisor:Einar Johan Aas, IETCo-supervisor:Torstein Hernes Dybdahl, Falanx Microsystems AS

Norwegian University of Science and Technology Department of Electronics and Telecommunications

**Problem Description**

Verification is the process that is performed to show that the design is according to the specification.

SystemVerilog was developed to improve the Verilog language with attention to the verification tasks. The assignment involves the following:

- Develop a verification plan for the AES module

- Develop a testbench architecture using SystemVerilog constrained randomisation

- Use assertions and functional coverage to track progress and quality of verification

Assignment given: 29. August 2006 Supervisor: Einar Johan Aas, IET

# Summary

This Master's thesis reports the verification planning and verification process of a Verilog RTL model. Modern verification techniques like constrained randomization, assertions, functional coverage analysis and object orientation are demonstrated on an AES RTL model.

The work of this thesis was naturally divided in three phases: First, a phase of literature studies to get to know the basics of verification. Second, the creation of a verification plan for the selected module. Third, implementation of the testbench, and simulation tasks.

The verification plan created states the goals for the simulation. It also states plans for details about the testbench, like architecture, stimuli generation, randomization, assertions, and coverage collection. The implementation was done using the SystemVerilog language. The testbench was simulated using the Synopsys VCS verification software.

During simulation, coverage metrics were analyzed to track the progress and completeness of the simulation. Assertions were analyzed to check for errors in the behavior during simulation. The analysis carried out revealed high code coverage for the simulations, and no major errors in the verified module.

# Preface

This Master's thesis was submitted to the Norwegian University of Science and Technology (NTNU), Department of Electronics and Telecommunication. It is the result of a thesis problem given by ARM Norway AS. The work was carried out during the autumn of 2006, starting in August 2006 and ending in January 2007.

I would like to thank my supervisors, Professor Einar J. Aas, NTNU and Torstein Hernes Dybdahl, ARM Norway AS, for their guidance and feedback through the whole thesis process.

Trondheim, January 23rd, 2007

Henrik Ruud

# Contents

| Sı                        | ımma                             | ary                               |                            | i                                                     |

|---------------------------|----------------------------------|-----------------------------------|----------------------------|-------------------------------------------------------|

| P                         | refac                            | е                                 |                            | iii                                                   |

| С                         | onter                            | nts                               |                            | v                                                     |

| $\mathbf{L}^{\mathrm{i}}$ | st of                            | Figur                             | es                         | ix                                                    |

| $\mathbf{L}^{\mathrm{i}}$ | ist of                           | Table                             | S                          | xi                                                    |

| A                         | bbre                             | viation                           | 15                         | xiii                                                  |

| 1                         | Intr<br>1.1<br>1.2<br>1.3<br>1.4 | Proble<br>Contri                  | ionration                  | 1<br>2                                                |

| 2                         | <b>Ver</b><br>2.1                |                                   | on Theory is Verification? | 5                                                     |

|                           | 2.2                              | Cover:<br>2.2.1<br>2.2.2<br>2.2.3 | age                        | 8                                                     |

|                           | 2.3                              | Rando<br>2.3.1<br>2.3.2<br>2.3.3  | omization                  | 10<br>11                                              |

|                           | 2.4                              | Layers<br>2.4.1<br>2.4.2<br>2.4.3 | s and Reuse                | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|   | 2.5 | Assertions                          |

|---|-----|-------------------------------------|

|   |     | 2.5.1 Assertion Types               |

|   |     | 2.5.2 Assertion Placement           |

|   |     | 2.5.3 Error Reporting               |

|   | 2.6 | Verification Planning               |

|   |     | 2.6.1 The Verification Team         |

|   |     | 2.6.2 Day-in-the-Life Document      |

|   |     | 2.6.3 Tools and Technologies        |

|   |     | 2.6.4 Architecture                  |

|   |     | 2.6.5 Assertions                    |

|   |     | 2.6.6 Implementation Phases         |

|   |     | 2.6.7 Coverage Collection and Goals |

| 3 | Тоо | ols and Languages 2                 |

|   | 3.1 | HVLs and HDLs                       |

|   | 3.2 | SystemVerilog                       |

|   |     | 3.2.1 Introduction                  |

|   |     | 3.2.2 Language Properties           |

|   | 3.3 | Synopsys VCS                        |

| 4 | Ver | ification Plan 2                    |

|   | 4.1 | Module Selection                    |

|   |     | 4.1.1 Advanced Encryption Standard  |

|   |     | 4.1.2 Wishbone Bus                  |

|   | 4.2 | Day-in-the-Life Document            |

|   | 4.3 | Tools and Technologies              |

|   | 4.4 | Architecture                        |

|   | 4.5 | Assertions                          |

|   | 4.6 | Implementation Phases               |

|   | 4.7 | Coverage Collection and Goals       |

| 5 | Tes | tbench Implementation 3             |

|   | 5.1 | AES Module Simulation Test          |

|   | 5.2 | Testbench Modules                   |

|   |     | 5.2.1 Interface                     |

|   |     | 5.2.2 AES Top Module                |

|   |     | 5.2.3 Test Module                   |

|   |     | 5.2.4 External Assertion Module     |

|   | 5.3 | Transactors                         |

|   |     | 5.3.1 Data Flow                     |

|   |     | 5.3.2 Environment                   |

|   |     | 5.3.3 Bus Functional Model          |

|   |     | $5.3.4$ Generator $\ldots$ $4$      |

|   |     | 5.3.5 Scoreboard                    |

|   |     |                                     |

|              |                     | 5.3.6 Checker                                                             | 42         |  |  |  |  |  |

|--------------|---------------------|---------------------------------------------------------------------------|------------|--|--|--|--|--|

|              | 5.4                 | Assertions                                                                | 43         |  |  |  |  |  |

|              | 5.5                 | Functional Coverage                                                       | 43         |  |  |  |  |  |

|              |                     |                                                                           |            |  |  |  |  |  |

| 6            | $\mathbf{Sim}$      | ulation                                                                   | <b>45</b>  |  |  |  |  |  |

|              | 6.1                 | Synopsys VCS Setup                                                        | 45         |  |  |  |  |  |

|              | 6.2                 | Testbench Compilation                                                     | 45         |  |  |  |  |  |

|              | 6.3                 | Simulation                                                                | 46         |  |  |  |  |  |

|              | 6.4                 | Testbench Debug                                                           | 47         |  |  |  |  |  |

|              | 6.5                 | Assertion and Coverage Reporting                                          | 47         |  |  |  |  |  |

|              | 0.0                 | inservice and coverage responsing the termination and coverage responsing | ± 1        |  |  |  |  |  |

| <b>7</b>     | Disc                | Discussion 49                                                             |            |  |  |  |  |  |

|              | 7.1                 | Coverage Progress                                                         | 49         |  |  |  |  |  |

|              | 7.2                 | Code Coverage                                                             | 50         |  |  |  |  |  |

|              | • ·                 | 7.2.1 Line Coverage                                                       | 50         |  |  |  |  |  |

|              |                     | 7.2.2 Condition Coverage                                                  | 50         |  |  |  |  |  |

|              |                     |                                                                           | $50 \\ 51$ |  |  |  |  |  |

|              |                     | 0                                                                         | $51 \\ 51$ |  |  |  |  |  |

|              |                     | 7.2.4 Branch Coverage                                                     |            |  |  |  |  |  |

|              |                     | 7.2.5 Path Coverage $\ldots$                                              | 52         |  |  |  |  |  |

|              |                     | 7.2.6 Toggle Coverage                                                     | 53         |  |  |  |  |  |

|              | 7.3                 | Assertions                                                                | 53         |  |  |  |  |  |

|              | 7.4                 | Functional Coverage                                                       | 54         |  |  |  |  |  |

|              | 7.5                 | Testbench Discussion and Future Work                                      | 54         |  |  |  |  |  |

| 8            | Con                 | clusion                                                                   | 57         |  |  |  |  |  |

| 0            | Con                 |                                                                           | 57         |  |  |  |  |  |

| Bi           | bliog               | graphy                                                                    | 59         |  |  |  |  |  |

|              | C                   |                                                                           |            |  |  |  |  |  |

| $\mathbf{A}$ | Day                 | r-in-the-Life Document                                                    | <b>61</b>  |  |  |  |  |  |

|              | A.1                 | General Information                                                       | 61         |  |  |  |  |  |

|              | A.2                 | Module Blocks                                                             | 62         |  |  |  |  |  |

|              | A.3                 | Communication Bus                                                         | 62         |  |  |  |  |  |

|              | A.4                 | AES Operation Flow                                                        | 64         |  |  |  |  |  |

|              | A.5                 | AES Internal Operations                                                   | 65         |  |  |  |  |  |

|              |                     | 1                                                                         |            |  |  |  |  |  |

| $\mathbf{B}$ | B Verification Plan |                                                                           | 69         |  |  |  |  |  |

|              | B.1                 | Typical Operation                                                         | 69         |  |  |  |  |  |

|              | B.2                 | Tools and Technologies                                                    | 69         |  |  |  |  |  |

|              | B.3                 | Implementation Phases                                                     | 70         |  |  |  |  |  |

|              | B.4                 | System Architecture                                                       | 70         |  |  |  |  |  |

|              | B.5                 | Layer Implementation                                                      | 71         |  |  |  |  |  |

|              | B.6                 | Scenarios                                                                 | 72         |  |  |  |  |  |

|              | B.7                 | Block Descriptions                                                        | 72         |  |  |  |  |  |

|              | B.8                 | Randomization                                                             | 73         |  |  |  |  |  |

|              | Б.8<br>В.9          | Assertions                                                                | 74         |  |  |  |  |  |

|              |                     |                                                                           |            |  |  |  |  |  |

|              |      | Code Coverage                     | 74<br>75 |

|--------------|------|-----------------------------------|----------|

| $\mathbf{C}$ | Test | bench Source Code                 | 77       |

|              | C.1  | Top Module                        | 79       |

|              | C.2  | Wishbone Interface                | 81       |

|              | C.3  | Test Program                      | 83       |

|              | C.4  | External Assertions Module        | 93       |

|              | C.5  | AES Top Module                    | 95       |

|              | C.6  | C Language Communication Function | 97       |

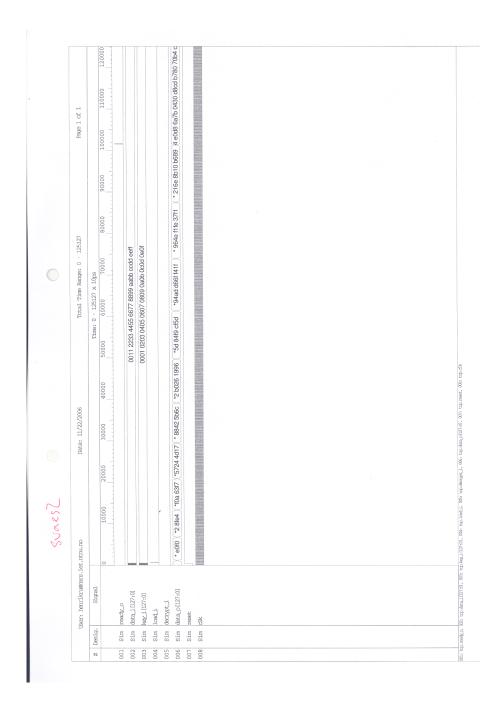

| D            | Cov  | erage Reports                     | 101      |

|              | D.1  | cmView.short_ld File              | 101      |

|              | D.2  | cmView.short_cd File              | 103      |

|              | D.3  | cmView.short_fd File              | 105      |

|              | D.4  | cmView.short_bd File              | 110      |

|              | D.5  | cmView.short_pd File              | 118      |

|              | D.6  | cmView.short_td File              | 130      |

|              | D.7  | cmView.mod_td_File                | 133      |

|              | D.8  | Assertions Report                 | 135      |

| $\mathbf{E}$ | Sigr | nal Waves and Screenshots         | 141      |

|              | E.1  | Screenshots                       | 141      |

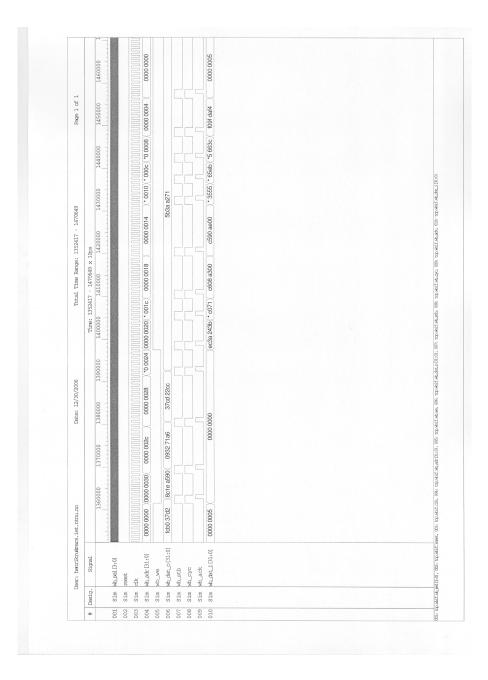

|              | E.2  | Signal Waves                      | 143      |

# List of Figures

| 2.1  | Verification vs test $[1]$                         | 5     |

|------|----------------------------------------------------|-------|

| 2.2  | Testbench and DUT                                  | 6     |

| 2.3  | Analyzing functional and code coverage results [2] | 9     |

| 2.4  | Bug rate graph [2]                                 | 9     |

| 2.5  | Coverage versus time $[2]$                         | 10    |

| 2.6  | Bathtub distribution [2]                           | 11    |

| 2.7  | Coverage feedback                                  | 12    |

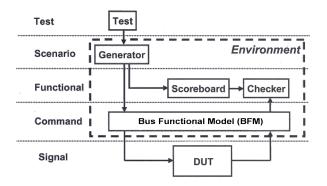

| 2.8  | Layered testbench example [2]                      | 13    |

| 2.9  | Wasting time vs starting early [5]                 | 17    |

|      |                                                    |       |

| 5.1  | Testbench module structure                         | 36    |

| 5.2  | Source code for a rounds assertion                 | 44    |

| 5.3  | Source code for covWbDatIn cover group             | 44    |

| A.1  | AES module blocks                                  | 62    |

| A.2  | Wishbone module                                    | 62    |

| A.3  | AES flow                                           | 64    |

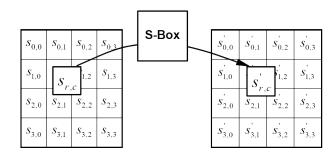

| A.4  | SubBytes operation [3]                             | 65    |

| A.5  | S-box table $[3]$                                  | 65    |

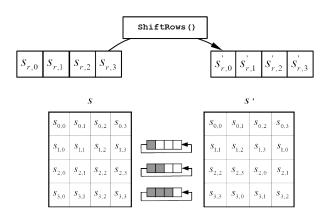

| A.6  | Shiftrows operation [3]                            | 66    |

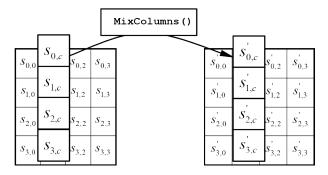

| A.7  | MixColumns operation [3]                           | 66    |

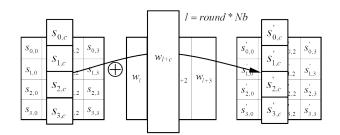

| A.8  | AddRoundKey operation [3]                          | 67    |

| 11.0 |                                                    | •••   |

| B.1  | Testbench data flow                                | 70    |

| B.2  | Testbench data flow                                | 71    |

| T 1  |                                                    | 4 4 4 |

| E.1  | DVE screenshot                                     | 141   |

| E.2  | cmView screenshot                                  | 142   |

| E.3  | 8                                                  | 144   |

| E.4  | Wishbone write operation                           | 145   |

# List of Tables

| 3.1  | cmView code coverage reports                                                                                                                                  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1  | Testbench modules and files                                                                                                                                   |

| 5.2  | Mailboxes                                                                                                                                                     |

| 5.3  | Transaction class properties                                                                                                                                  |

| 6.1  | Compile-time switches                                                                                                                                         |

| 6.2  | Runtime switches                                                                                                                                              |

| 7.1  | Code coverage progress (percentage) 49                                                                                                                        |

| 7.2  | Line coverage summary $\ldots \ldots 50$                           |

| 7.3  | Condition coverage summary $\ldots \ldots 51$                                                  |

| 7.4  | FSM coverage summary $\ldots \ldots \ldots$   |

| 7.5  | Branch coverage summary $\ldots \ldots 52$                                       |

| 7.6  | Path coverage summary $\ldots \ldots 53$                                                       |

| 7.7  | Toggle coverage summary 53                                                                                                                                    |

| A.1  | Signals of the Wishbone module                                                                                                                                |

| A.2  | Valid addresses of wb_adr_i 63                                                                                                                                |

| B.1  | Typical operation                                                                                                                                             |

| B.2  | Tools, language and technologies $\ldots \ldots 69$                                            |

| B.3  | Phases                                                                                                                                                        |

| B.4  | $Component\ Implementation\ \ldots\ \ldots\$                          |

| B.5  | XY-grid phases/layers $\dots \dots \dots$                     |

| B.6  | Scoreboard description $\ldots \ldots \ldots$ |

| B.7  | Checker description $\ldots \ldots \ldots$    |

| B.8  | BFM description                                                                                                                                               |

| B.9  | Generator description $\dots \dots \dots$                     |

| B.10 | Assertions                                                                                                                                                    |

| B.11 | Code Coverage Analysis Plan                                                                                                                                   |

| B 19 | Cover groups                                                                                                                                                  |

# Abbreviations

| AES                                | Advanced Encryption Standard                   |

|------------------------------------|------------------------------------------------|

| BFM                                | Bus Functional Model                           |

| DITL                               | Day in the Life                                |

| DUT                                | Device Under Test                              |

| DVCon                              | Design & Verification conference & exhibition  |

| DVE                                | Discovery Visualization Environment            |

| FIFO                               | First In First Out                             |

| GCC                                | GNU Compiler Collection                        |

| $\mathrm{HDL}\ \ldots\ldots\ldots$ | Hardware Description Language                  |

| HDVL                               | Hardware Description and Verification Language |

| $\mathrm{HVL}\ \ldots\ldots\ldots$ | Hardware Verification Language                 |

| IP                                 | Intellectual Property                          |

| SVA                                | SystemVerilog Assertions                       |

| URG                                | Unified Report Generator                       |

| VMM                                | Verification Methodology Manual                |

# Chapter 1

# Introduction

$T^{\rm HE\ MAIN\ TOPIC}$  of this master thesis is the planning and employment of modern verification techniques to verify the functionality and properties of a selected open source RTL model.

### 1.1 Motivation

Verification is the task of verifying that an implementation meets its functional intend. As digital hardware designs grow more and more complex, the verification task gets more important in order to ensure that bugs are found before the design hits the market. At the same time, a more complex chip requires a more complex verification process.

From the 1990s until today, several new technologies have been introduced to help the verification process. To speed up the verification process, stimuli is generated by constrained random functions, instead of manual generation of each input set. Code coverage and functional coverage is used to track the progress and quality of the simulations. Assertions are implemented to monitor the behavior of the device being tested. Testbenches are split up using object oriented techniques to make them more maintainable and reusable.

Many of these techniques have been introduced by the verification languages E and Vera in the late 1990s. The recent years, a new language called SystemVerilog has been standardized. It is a verification and high-level modelling language based on Verilog, which makes it easy to integrate with Verilog models to be verified.

# **1.2** Problem Formulation

When the thesis was given, it was made clear that the work would naturally consist of three main parts, where most of the focus would be on the first two: 1

The first part of the job was to get to know the theory about verification planning, and verification using SystemVerilog. A number of books and articles on the subject were recommended by the supervisors. This part also contained the task of selecting a module suitable for being verified.

The second part involved making a verification plan for the selected module. The verification process and testbench planned should exploit modern verification techniques from the theory, like constrained randomization, functional coverage, object orientation and assertions.

The third part was the practical work: To implement the testbench planned in the verification plan, carry out the simulations using Synopsys VCS and analyze the results with the available tools.

# 1.3 Contribution

In this thesis a verification plan for an AES RTL model has been created, based on theory about constrained randomization, functional coverage, object orientation and assertion based simulation. The planned verification system has then been implemented using SystemVerilog, and simulated using Synopsys VCS. Simulation results have been analyzed to ensure that the verification process has been adequate.

# **1.4** Organization of the Thesis

Chapter 2 of the thesis is a theory chapter that explains the techniques used in the verification process, and will serve as the theory basis for the planning and implementation process.

Chapter 3 is a theory chapter introducing the SystemVerilog language and the Synopsys VCS tools. It contains the theory background for the implementation of the testbench in SystemVerilog, and the simulation of the system using Synopsys VCS.

Chapters 4, 5 and 6 present my contributions. Chapter 4 steps through the creation of a verification plan for the chosen module. The module selection process is also described.

In Chapter 5, the implementation of the testbench is presented. The simulation of the testbench is described in Chapter 6.

Chapter 7 contains the discussion of the simulation results. It also contains a discussion on the testbench design and future work. Conclusions are drawn in chapter

8.

# Chapter 2

# Verification Theory

$T^{\rm HIS\ CHAPTER}$  gives an introduction to techniques commonly used in the verification process, and gives the necessary background for the verification planning and implementation described in later chapters.

# 2.1 What is Verification?

The purpose of the verification process is to verify that the design functions like it is intended to. This process should both verify that the implemented functions behave correctly, and that all parts of the planned system are implemented.

#### 2.1.1 Verification vs Test

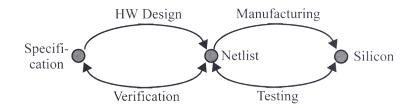

Verification must not be confused with the test process. Verification is the process of verifying the functionality of a design, while the test process tests if the design has been manufactured correctly. This is shown in Figure 2.1.

Figure 2.1: Verification vs test [1]

### 2.1.2 Verification Technologies

Simulation based verification and formal verification are the two most common technologies used in verification.

$\mathbf{5}$

#### Simulation Based Verification

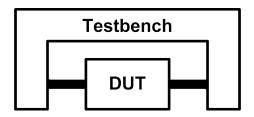

Simulation has traditionally been the main technology for verification. In its simplest form, a testbench is used to generate relevant input stimuli, which is sent to the device being verified. The testbench will also fetch the output from the device, to check for its correctness, as illustrated in Figure 2.2. The device being verified is often called *device under test* (DUT)

Figure 2.2: Testbench and DUT

Seen from the device under test, the testbench will act like a simulation of the outside world. It is usually impossible to test all combinations of indata, this could require years of simulation time. It is therefore important that the testbench stimuli, and also the sequence of the stimuli, reflects the randomness a normal user would provide. There will be more about random stimuli generation in Section 2.3.

Simulation can show only the presence of bugs, never prove their absence [1]. There is, for designs of normal sizes, never time enough to simulate all combinations and sequences of stimuli and outside influence. There will always be a possibility for undiscovered bugs in the design. Section 2.2 is about coverage, which is a way to measure the completeness of a simulation, and therefore predict the possibility of remaining bugs.

#### Formal Verification

Formal verification is a way to mathematically check that a design is functionally correct. This is done using special tools acting on assertions, which is a way to specify the properties of the design.

Formal verification on large designs is an operation with very high complexity, and therefore not used on full designs. Formal verification is more commonly used to verify corner cases of the design, which is not easily reached by simulation. Some tools combine the power of simulation based and formal verification. This combination is often called hybrid verification.

# 2.2 Coverage

Coverage is a way to measure how thoroughly the design has been verified during simulations. This is important, since there is never infinite time available for the verification process. We need to know when we could be confident enough that the design is bug-free, and ready for the market. There are two main types of coverage: Code coverage and functional coverage.

## 2.2.1 Code Coverage

Code coverage answers the following question: How much of the design *implementation* has been executed during verification?

Code coverage is collected automatically by the simulation tools. Even though collecting code coverage does not represent much extra work for the verification engineer, it might be a good indicator to see if enough simulations have been carried out. In addition, code coverage analysis can often reveal redundant code in the DUT.

There are many different types of code coverage metrics. These are the main ones, listed in [4]:

- Line Coverage tells which lines, statements and blocks that have been executed during the simulation.

- Condition Coverage shows which combinations of inputs to conditional expressions that are covered.

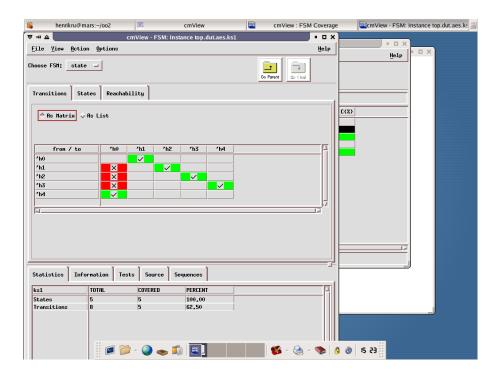

- FSM Coverage reports about which states, state transitions and sequences of state transitions that are covered in the finite state machines of the design.

- Branch Coverage shows which parts of each single if and case expressions that have been covered.

- Path Coverage shows which sequences of if and case selections that have been covered.

- Toggle Coverage monitors the value change from 0 to 1 and 1 to 0 for every signal, and reports which combinations that have been covered.

Often, the goal for each metric is set to 100% *explained coverage*. The non-covered parts of the code will then have to be explained why it is not covered.

#### 2.2.2 Functional Coverage

Code coverage, as shown in the previous chapter, is a good way to find out how thoroughly the implementation has been tested. But what if some planned features are simply missing in the implemented design? This is where functional coverage can help.

Functional coverage answers the following question: How much of the design *specification* has been verified?

In contrast to code coverage analysis, functional coverage analysis is associated with quite a lot of manual work. Since functional coverage measures the completeness of the simulation compared to the specification, the specification has to be somehow entered into the system. This is done manually, using cover groups or cover properties.

The most flexible of the two is the cover group. It consists of one or more cover points, which are specified to sample data at specified signals or expressions in the design. Expected data are grouped in ranges called *bins*. When data is sampled, the corresponding bin is marked as covered. Coverage analysis will reveal which bins that are covered, and which ones are not.

Two cover points could be combined to form a matrix-style data bin. This is called cross-coverage.

The second, simpler, mechanism for functional coverage collection is cover properties. Cover properties look much like assertions, described in later chapters. Analysis of cover properties will reveal how many times the property has been hit.

#### 2.2.3 When Are We Done?

The main purpose of using coverage analysis is to get a measure about how thoroughly the design has been tested, and to give an indication on whether the verification process is complete or not.

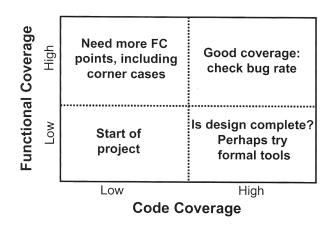

Figure 2.3 shows a table about how to react on the coverage percentages. If the functional coverage is high, but the code coverage is low, it might be necessary to include more functional cover points. If the code coverage is high while the functional coverage is low, it might be worthwhile to check out the design code, to see if the specification is fully implemented.

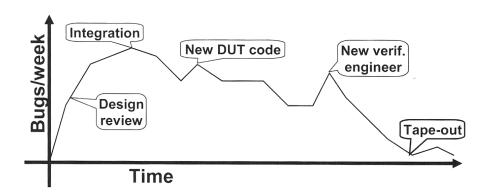

The goal is high code coverage and high functional coverage. If this is achieved, the bug rate could be checked. Figure 2.4 shows an example of a bug rate graph for

Figure 2.3: Analyzing functional and code coverage results [2]

a verification process. The graph, showing bugs found per week during the project, could be an indicator on how much work there is left.

Figure 2.4: Bug rate graph [2]

# 2.3 Randomization

If the design to be verified is small, with only a few inputs (and input data combinations), a classic, *directed* approach to the verification process might be adequate. Each set of input data will then carefully be written manually, in order to achieve the wanted coverage.

With today's complex designs, however, writing directed testcases will usually take way too much time. A better way to generate test inputs and scenarios is to

use pseudo-random functions. Instead of spending a lot of time of aiming one bug at the time with a directed test, a set of random tests will hit a larger area at the same time, with automatically generated stimuli. Peet James [5] compares this with using a shotgun to hit bugs, instead of using a peashooter.

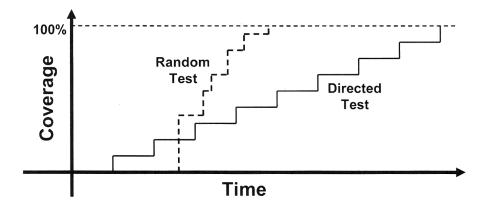

The graph of covered design space versus time will be a bit different between the two approaches, as shown in figure 2.5. Using directed tests the graph will be quite linear, since each testcase will be written manually. Using random testing, the graph will first be flat, representing the time spent on creating the random testbench. The graph will then typically rise faster than the directed graph, and then (hopefully) reach the coverage goal faster than the directed tests.

Figure 2.5: Coverage versus time [2]

#### 2.3.1 What to Randomize

The obvious thought about randomization is to randomize the input data. In this way the need for manually created stimuli is eliminated. However, randomization is much more powerful than that.

The purpose of a testbench is to simulate the outside world as good as possible. It should test the device to its limits, to create special situations often discovering bugs. It should act random in more ways than just generation random input data, just like a normal user would do. [2] gives some examples on what could be randomized:

- Device configuration

- Environment configuration

- Primary input data

- Encapsulated input data

- Protocol exceptions

- Communication delays: Delay responses with a number of clock cycles

- Transaction status

- Errors and violations

Scenarios are often planned in order to implement the more advanced random features. Each valid operation of the design is then defined as a scenario in the testbench. This could for instance be a memory read operation. The scenarios are then randomly selected by the testbench during the simulation.

#### 2.3.2 Constraints

Randomization without constraints, like described previously, would be like shooting in the dark. By specifying constraints for the random stimuli generator, you could "aim the gun" at the design parts with high probability of bugs. And, more importantly, try to reach the parts of the design which are not already covered.

One type of constraints is the specification of the data format. For instance the width of a bus address, or valid configuration bits.

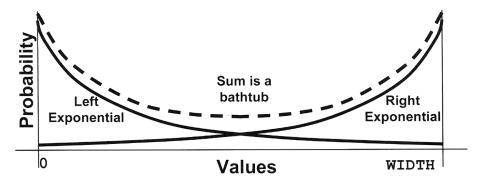

Constraints could be used to create a higher probability for interesting data. Often data in the upper and lower extremes of the allowed range could provoke overflow errors. To achieve this, a so-called bathtub distribution of the data could be made, as shown in Figure 2.6.

Figure 2.6: Bathtub distribution [2]

Using a feedback mechanism like the one in Figure 2.7 it is (at least theoretically) possible to automatically seed the random generator, so that areas not already covered are targeted. I practice, this is difficult and yet not very common to do with today's verification tools [6].

Figure 2.7: Coverage feedback

## 2.3.3 Seeds

Given the exact same testbench, and the same simulator software, the pseudo-random number generator will always generate the same numbers. It is possible to seed the number generator to achieve different random number series. This could be interesting to be able to run many short series of simulations, instead of one long series.

# 2.4 Layers and Reuse

If you are verifying a very small design, almost any testbench architecture could be adequate. However, as DUTs and verification systems grow more complex, it is important to have more structured testbenches. The code should be easy maintainable even when the project grows bigger. Code will also often have to be reused in future verification projects.

To achieve this the testbench has to be split up in layers and components. With smaller units it is easier to achieve goals of maintainability and reusability.

# 2.4.1 Layered Testbench Architecture

Using layers is a way to split the testbench in different levels of abstraction. The lowest level of abstraction will typically be the functionality communicating with the DUT. The upper layers deal with tasks of higher abstraction, like stimuli generation.

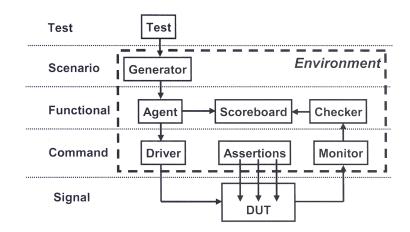

Figure 2.8 shows an example of a layered testbench, based on figures and examples published in [2]. This must be regarded as an example only. For instance, DUTs with more complex communication might require more layers. Small devices could maybe do with even fewer layers than four.

Figure 2.8: Layered testbench example [2]

The components of the layers are implemented as classes. Features already wellknown from object oriented programming languages are therefore available, like inheritance, instantiation and threads. This opens for a more elegant way of handling data, as well as greater possibilities for component reuse.

#### Test Layer

The test layer consists of the test component. Test is the top-level component. It contains the constraints for the stimuli. It should be easy to change, so the simulation easily could be fine-tuned between each run.

#### Scenario Layer

The scenario layer contains the generator component. Generator generates the stimuli on behalf of the constraints from the test component. It also contains the scenarios. All randomization tasks are carried out in the generator. Generator also contains the scenarios. The randomization mechanisms are discussed in detail in Section 2.3.

### **Functional Layer**

In the functional layer data could be further processed and broken up before it is sent to the command layer. This layer also contains the tasks related to checking the correctness of the DUT outputs. It contains the agent, scoreboard and checker components.

- Agent could be used to further process the data before it is sent to the driver.

- Scoreboard contains a high-level reference model of the design. It receives the same stimuli as the DUT, and predicts the correct DUT response.

- Checker compares the DUT output received from the monitor with the predictions received from the scoreboard.

### **Command Layer**

The command layer is where the direct communication with the DUT is maintained. Here the signals of the DUT are driven and monitored.

- Driver is the component which drives the inputs of the DUT, typically using bus commands.

- Monitor is the second component communicating with the DUT. It monitors the outputs of the DUT, and sends the received outdata to the checker.

- As seen in the figure, external assertions could be though of as a part of the command layer.

### Signal Layer

The signal layer simply contains the device which is being verified, and its signals.

# 2.4.2 Callbacks

Often it would be useful to be able to do some randomization tasks also in low-level layers like the Driver. An example could be to simulate disturbances in the DUT communication, like delaying a response signal, or dropping and retransmitting a data packet.

However, specifying details about the randomization inside the Driver is not a good idea. Randomization settings should be easy to change later. Therefore, callback functions are often defined. They are defined in their own class, and can therefore be easily changed later using inheritance. Driver should always call callback functions right before and right after data transmission.

#### 2.4.3 Verification IPs

For verification of standard components, like buses, it could often be more worthwhile to buy already finished code than writing it oneself. Verification IPs are IPs with verification functionality.

# 2.5 Assertions

Assertions are small code blocks inserted in the design, containing statements about the expected behavior of the design code. In its simplest form, an assertion can be viewed as an *if* statement that does some error action if the DUT fails to fullfill its requirements. Assertion statements are quite common in software design, but has only become available in hardware design tools recent years.

Assertions could be specified by both the designer and the verifier. Who does what should be decided in the verification planning process.

Assertions could either be coded from scratch, or picked from a library. Synopsys VCS includes a library of SystemVerilog assertions [7]. In this way, a lot of common functionality can be easily checked using assertions already made.

In addition to monitoring design properties during simulation, assertions can also be used with formal verification tools. The properties specified in the assertions are then used as the basis for the mathematical proofs.

A good, practically oriented guide to SystemVerilog Assertions is written by Vijayaraghavan and Ramanathan [8].

#### 2.5.1 Assertion Types

In SystemVerilog, there are two ways to implement assertions: Immediate and concurrent assertions.

Immediate assertions are, as the name suggests, executed immediately along with the code. They are placed in procedural blocks.

Concurrent assertions are clock-based. A concurrent assertion will monitor a signal or an expression on each clock edge through the simulation, and fire if the expression fails.

## 2.5.2 Assertion Placement

Assertions could either be placed directly in the code of the DUT, or in the testbench monitoring the bus. Assertions in the DUT are called internal assertions, while assertions placed in the testbench are called external assertions.

External assertions often monitor the bus signals between the testbench and the DUT. If an interface is used, a module containing assertions could easily be connected to the interface like any other module (interfaces are introduced in Section 3.2.2). If not, the assertions could be bound to the signals using a *bind* statement.

Internal assertions could either be written by the designer during the design phase, or by the verifier during the verification process. Special internal conditions and assumptions should be stated in assertions created by the designer. In this way they are not accidentally left out from the verification process. The VMM (Verification Methodology Manual) [6] even suggest designers to replace the ordinary code comments with assertions. This might probably be a bit too dramatic to most designers, but at least well illustrates the idea of internal assertions.

Assertions are left out during synthesis, and therefore does not affect the finished product after synthesis.

#### 2.5.3 Error Reporting

By default assertions print an error message when they fail. However, the error action can be customized.

This gives a possibility to create an error report mechanism. If an assertion fails, it could trigger a mechanism that reports the relevant states and data for the design. Previous data and states should also be included in the report.

With this kind of reports it would be easier to regenerate the situation where the error was found, and to find out what caused the error to happen in the first time.

# 2.6 Verification Planning

Since verification projects are growing more and more complex, it is also becoming more and more important to create a good plan before the verification is started. Creating a good plan will save a lot of time later. It is also essential to have a plan in order to know when the verification is finished and the coverage results are considered good enough.

The theory about verification planning is based on Peet James' book Verification Plans [5], which proposes a five-day approach to the verification planning process. However, some adjustments are made to better fit SystemVerilog testbenches. Theory about verification planning for SystemVerilog is to some degree found in [2], [1] and [9]

#### 2.6.1 The Verification Team

A verification team should be assembled to do the verification planning. In addition to the verifiers, the team could consist of other people that has relevant input. First of all, this should be the architects and designers, who have first-hand knowledge of the functionality of the design.

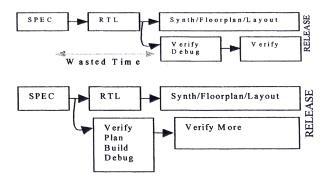

The verification planning should start as early as possible. If possible, it should start before the design phase of the design core starts. In this way, the parts of the core could be verified before the entire design is ready. This is shown in Figure 2.9.

Figure 2.9: Wasting time vs starting early [5]

#### 2.6.2 Day-in-the-Life Document

To be able to create a verification plan for a design it is important to know its features. A day-in-the-life document (DITL) is a short document demonstrating the most common tasks of the design. It is short and consise, typically a few A4 pages. This document can by no means exclude the needs for more detailed specifications of the DUT, but it can give a good overview of the design.

By starting the verification plan process by making such a document, the verification team will get an overview of the tasks of the DUT. This makes it easier to make a good and relevant verification plan.

#### 2.6.3 Tools and Technologies

One of the things to be stated in the verification plan is the choice of verification tools, verification languages and verification technologies. This is typically done gradually in the verification planning process, as the verification needs for the design are revealed. There is a wide variety of languages and tools available. There is more about some of these in Chapter 3. Often many of the languages and tools could be adequate for the process. Knowing which languages that are mastered by verification team is of course also important to make the right decision.

The verification plan should also contain information about the verification technologies to be used. If some areas of the design are verified using formal tools, there should be information about this in the verification plan.

#### 2.6.4 Architecture

An important thing to define in the verification plan is the architecture of the testbench. The verification plan examples given in [5] starts off with a short list of typical operations of the testbench.

Figures showing the blocks and the data flow of the testbench should be added to describe the architecture. In addition, the layers and the components of the testbench should be described in greater detail in text or a table.

Planned scenarios should be listed and described.

A plan for the randomization features should be made. If there are any planned constraints, they should also be described.

For complex verification systems, it could be smart to also work out more detailed implementation plans for the testbench. In [5], these are called breakout documents and appear in the appendix of the verification plan.

#### 2.6.5 Assertions

The assertion plan is a natural part of the verification plan. It could well be specified in a table form, such as the examples in [9]. As a minimum, the following information should be stated:

- Which functionality to verify

- Where the assertion is placed (external or internal assertion)

- Assertion type (immediate or concurrent assertion)

- Who implements it (designer or verifier, or name of the responsible if the verification team is large)

Who implements which assertions? The following rule of thumb is given in [9]: Designer engineers should write assertions to verify assumptions that affect the functionality of a design block. That could be, for instance, that an internal module never gets X or Z values as an input. Verification engineers should write assertions that verify design functionality meets the design specification. For example, that bus behavior is correct.

#### 2.6.6 Implementation Phases

Phases define the milestones in the implementation process. They are the steps in the implementation of the testbench. Each phase will build on some of the previous phases.

If the design to be verified is not yet finished, phases should be planned even more carefully. It is important that the implementation of the verification system closely follows the implementation of the design. In that way parts of the design could be verified before the full design is complete, and the time spent on verification after the design phase has ended will be shorter.

Layers and phases could be crossed in an XY grid to show which layers that needs to be implemented in which phases.

#### 2.6.7 Coverage Collection and Goals

A section should list which code coverage types that will be analyzed, and the approximate goals for each of them.

The functional coverage points should be planned, and listed. This list should at least cover:

- Which signal or expression to cover

- Purpose

- How many bins there should be, and how the bins are specified

- The placement of the cover group (internal or external)

- The coverage goal for the cover group (expressed as a percentage)

## Chapter 3

# Tools and Languages

$T^{\rm HE\ BACKGROUND\ THEORY\ about\ verification\ tools\ and\ verification\ languages\ is}$  collected in this chapter. SystemVerilog and Synopsys VCS are treated in particular, since they will be used for implementation and simulation in later chapters.

### 3.1 HVLs and HDLs

Traditionally, verification has been done using either a hardware descriptions language (HDL) or a hardware verification language (HVL). As long as simple, directed testbenches are sufficient to verify a design, the easiest would be to use a HDL. The same language and tools as during the design could be used, which the designer already is familiar to.

With more complex digital designs in the 1990s, there was need for specialized verification languages. *Vera* and *e* were two of them. More advanced features like contrained randomization and object-orientation were introduced. The disadvantage of the HDL is that they represent another language that has to be learnt. Vera and e are both widely used today. However, in a survey in connection with DVCon 2005, 78 percent of the verification engineers thought special verification languages like e and Vera would disappear in the coming years [10].

Even if better solutions are introduced, it does not necessarily mean that they will be adopted by the industry. Most companies already have verification code for most of the functionality of their designs. This legacy code is often also reused in new verification projects. A change of verification language would mean a lot of work, since the legacy code will have to be translated and adjusted to fit new simulators.

SystemVerilog, which is described in the next section, is an HVL with most of the advantages of the HDLs.

## 3.2 SystemVerilog

#### 3.2.1 Introduction

SystemVerilog has sometimes been called an HDVL, since it combines the strengths of HDLs and HVLs. SystemVerilog is based on the widely used Verilog HDL, but has new functionality for verification and high-level system design. This makes it both powerful and easy to learn for designers already familiar with Verilog. Using the same language for both design and verification also makes it easier to access the internals of the DUT, no special interfaces are needed.

The verification features of SystemVerilog include:

- Assertion-based verification

- Random constrained stimuli generation

- Functional coverage

- Advanced object-orientation

The creation of the SystemVerilog language was initiated in the late 1990s by Accellera, a consortium of EDA companies and users who wanted to create the next generation of Verilog [2]. The OpenVera language was the basis for the verification functionality of the new language. SystemVerilog became an IEEE standard in 2005.

The Verification Methodology Manual (VMM) [6] is a manual written by Synopsys and ARM to give guidelines for advanced verification in using SystemVerilog. As well as being a reference for the SystemVerilog language, it also states rules about important verification planning topics, like layering, randomization, coverage and assertion usage.

#### 3.2.2 Language Properties

In this section, some important language properties of SystemVerilog are collected. This is based on the book by Spear [2], which has good examples of practical use of the SystemVerilog language.

#### Data types

In addition to the 4-state types available in Verilog, SystemVerilog offers 2-states data types. Since 2-states only considers 0 and 1 values, not X and Z, they are faster in simulation.

Two of the 2-state types are the *bit* and *int* types. Bit is a 2-state single bit type. Like regs, it can be given a range to support multiple bits. Int is a 32-bit

signed integer which works much like in C. Fixed-size int arrays are available, which is convenient for indexes and loop operations.

Strings, queues and associative arrays are also available in SystemVerilog.

#### **Modules and Programs**

In SystemVerilog, the active part of an testbench is usually contained in a *program*. Programs could be compared to *modules*. The difference is that *always* blocks are not allowed in programs.

The *automatic* keyword is often added to *program* to make the storage of variable values more like programming languages than Verilog. Local variables are then stored in the stack instead of being shared between all processes.

#### Signal Interface

An interface is a collection of signal definitions. Modules will then connect to the interface instead of directly to each other. In this way signals definitions are collected in one place, and does not need to be defined in each module. Signal directions could be specified by creating one *modport* for each module.

#### Functions and Tasks

Tasks can consume time, while functions cannot. Functions must have a return type. In SystemVerilog, task inputs and outputs can be declared in parenthesis, much like in C.

#### **Object Orientation**

Object orientation syntax in SystemVerilog looks very similar to the syntax of C++. A special pair of keywords, *fork* and *join*, represents the threads functionality of SystemVerilog. All statements between fork and join will be executed at the same time, as in parallel.

The class-implemented testbench components like Scoreboard and Generator are often called transactors.

#### **External Functions**

SystemVerilog (using Synopsys VCS) has at least three different technologies to call external functions placed in C code. DPI is the new technology for this purpose in SystemVerilog. PLI is the corresponding functionality inherited from Verilog. The last one, DirectC, is a VCS-specific technology. A user guide for DirectC [11] is shipped with VCS.

#### Mailbox

Using mailboxes is a flexible way to enable communication between two transactors. A mailbox could be compared with a FIFO queue. The mailbox could contain any number of objects.

## 3.3 Synopsys VCS

Synopsys VCS is a verification software package which supports, among other languages, Verilog and SystemVerilog. It is the most common software solution for SystemVerilog verification. In addition to SystemVerilog, it also supports the Open-Vera verification language. In its MX version it is also capable of verifying VHDL designs.

Details about VCS could be found in the VCS/VCSi User Guide [12]. There are still parts of SystemVerilog not implemented in VCS, although most of the important features are supported. VCS contains several tools to report simulation results, described below.

Unified Report Generator (URG) is a new, easy-to-use report generator in VCS that reports statistics for both functional coverage, code coverage and assertions coverage.

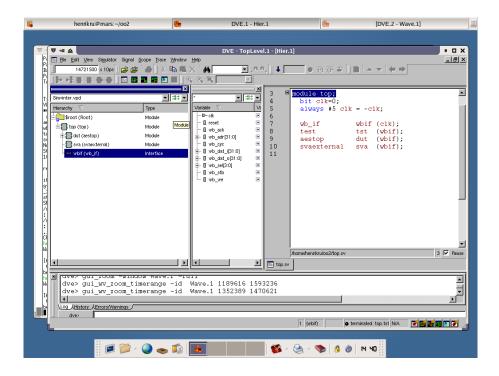

cmView is a tool to report code coverage. It could be run in batch mode outputting text-based reports, or in graphical mode showing the results interactively. cmView is started using the following commands:  $vcs - cm_pp gui$  for GUI mode, and  $vcs - cm_pp - b$  for batch mode. Batch mode creates a number of text files in the simv.cm/reports/ folder. For each code coverage type, 4 reports are generated. The different report types are shown in Table 3.1. In addition, definition reports are created, denoted by an added d in the filename. They show the cumulative code coverage for all module instances. Examples of the text-based reports are found in appendix D, while a screenshot of the graphical interface is shown in Appendix E.1.

Discovery Visualization Environment (DVE) is the signal-level debugger in VCS. A screenshot of DVE is shown in Appendix E.1.

assertCovReport and fCovReport are VCS commands to generate reports for assertions and functional cover properties. They add a set of HTML based reports to the simv.vdb/reports/ folder. The reports provide statistics for each assertion: The number of assertion hits, the number of statement success, failures and incomplete attempts. The reports also contain summaries grouped on modules and failure severity.

| Report | Explanation                                      |

|--------|--------------------------------------------------|

| long   | Main reports showing both covered and non-       |

|        | covered code parts. Includes summaries.          |

| short  | Short reports only showing non-covered code      |

|        | parts and summaries.                             |

| hier   | Sums up coverage for module instances, also tak- |

|        | ing into account sub-hierarchy.                  |

| mod    | Sums up coverage for module instances, without   |

|        | regard to any sub-hierarchy under the module.    |

Table 3.1: cmView code coverage reports

## Chapter 4

# Verification Plan

T<sup>HE</sup> VERIFICATION PLAN is the plan for the entire verification process. This chapter steps through the creation of the verification plan for an AES module with background in the theory in Section 2.6. The full verification plan is given in appendix B, while the DITL document is available in appendix A.

In an ordinary verification process many different persons would be involved, as mentioned in Section 2.6. In this thesis work, there was no such team available for verification planning. Making a DITL took more time than it would with the designer available for inputs, since all details now had to be found in the literature and source code.

It is also worth noting that the DUT was finished at the time the verification planning process started. This makes the verification flow more direct, instead of verifying component-by-component.

### 4.1 Module Selection

One of the first tasks of the thesis work was to find a module to be verified. The verification tools and techniques were stated in the problem description. In the presentation of the thesis problem it was suggested that the most relevant place to find such a module would be OpenCores [13].

OpenCores is a collection of free digital hardware cores on the Internet. They are often published under the GNU general public license, and usually written in Verilog or VHDL. OpenCores is often thought of as a hardware parallel to the much larger community of open source software.

Some requirements were discussed before the search for a module started:

• It should be finished and have code of high quality.

- It should be a design that fits well as an example for the verification techniques.

- The size and complexity should be kept in manageable bounds.

- It should be written in Verilog, so all SystemVerilog features can be used.

- It should be well documented.

Among of the best alternatives were a few microcontroller designs, two USB cores, and some encryption cores. A core implementing the *Advanced Encryption Standard* (AES) was chosen. The core, called 128 AES [14], is written by Javier Castillo in 2000.

The core fullfills most of the requirements: it was finished, and it looked like its code was of high quality. The design fits well as an example, containing both arithmetic modules and FSMs. Even though the operation is quite complex, the design has few inputs and few configuration choices. The core is written in Verilog.

No documentation follows the module, and no code comments are written, which is seems to be quite typical for all cores available at OpenCores. However, the AES specification is good, and could in many cases act as the documentation for the selected core. In addition, the communication with the core is done using Wishbone, a documented bus standard.

#### 4.1.1 Advanced Encryption Standard

AES is an encryption and decryption algorithm. The AES title was given after a selection process initiated in 1997 by the US National Institute of Standards and Technology (NIST), in order to find replacement for the Data Encryption Standard (DES) and triple-DES. The winner of the AES selection process was a candidate called Rijndael, developed by Belgian cryptographers Joan Daemen and Vincent Rijmen. Rijndael strongest sides in the competition was good performance in both hardware and software, and low memory requirements.

Rijndael operates on data blocks of 128 bits, while the keys are of sizes 128, 192 or 256 bits. The chosen AES core uses 128 bit keys, which is the least secure, but fastest option.

The operation of the core was further explored in the creation of the DITL document in Section 4.2. The DITL document is placed in Appendix A. Used literature on AES includes an AES manual by Dr. B. Gladman [15], the AES specification [3] and a book written by the AES developers [16].

#### 4.1.2 Wishbone Bus

Wishbone is a public domain System-on-Chip bus. The public domain status is one of Wishbones strongest sides, as it can be used completely royalty-free. The Wishbone Bus project is maintained by OpenCores. It was originally developed by Silicore Corporation.

The Wishbone bus supports communication using one master and either one or multiple slaves. Data transfer is done using a handshake behavior when data is interchanged on the data signals. Wishbone supports data blocks in any size up to 64 bits. The width of the bus has to be defined in the specification documents. The core to be verified supports only 32 bit blocks.

The simplest method of Wishbone communication are Single Read and Single Write cycles, which transfers one block at the time. Every block transfer will then require repetition of the handshake process. A faster and more convenient way to transfer data could be implemented using the Block Read and Block Write cycles. Here, the handshake process initiates a series of data transfers, with a data block transferred on each clock cycle.

The Wishbone Specification [17] states a set of requirements that has to be fulfilled before the design can be called "Wishbone compliant". One of the requirements is to provide a document specifying the Wishbone properties (like data block size and error behavior). The distribution of the AES core does not contain such a document, so the source code had to be inspected to reveal the Wishbone properties.

The Wishbone Bus properties of the AES module was further examined during the DITL creation process. This process is documented in Section 4.2.

## 4.2 Day-in-the-Life Document

The finished Day-in-the Life document can be found in Appendix A. The work with the DITL was started by collecting general information about AES and Wishbone. Since the module is not documented, the source code also had to be examined to find out the detailed design properties of the design.

A short introduction to the module was written, based on the information given on the OpenCores hosted web site of the project [14] and the AES specification [3].

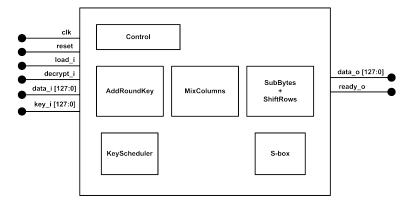

The source code of the project was examined to find the module structure, given in Section A.2. The structure does not differ much from the examples given in the specification. The *SubBytes* and *ShiftRows* implementations are collected in one module, while the *AddRoundKey* and *MixColumns* operations are placed in their own modules. The output and input signals in the implementation are also close to the examples.

A section about the Wishbone bus properties of the design was written in Section A.3. By examining the source code, it was clear that the module supports only single read and single write operations, since the ACK signal is automatically lowered after each data fetch. No connection to the AES module is provided, so a top module will have to be written in order to simulate the full design.

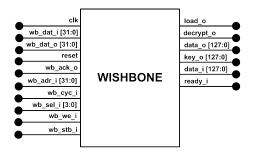

The supported bus signals were found in the source code and documented in Figure A.2 and Table A.1. The signals implemented are an absolute minimum of signals to provide Wishbone compliant communication. The valid addresses of the wb\_adr\_i signal were also found and documented in Table A.2.

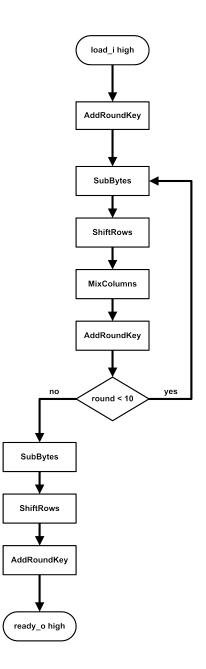

A AES flow diagram was created to show the internal flow of the AES module. It was based on the pseudo code found in the AES specification [3]. The flow diagram is shown in Figure A.3. In 128 bit AES encryption, 10 rounds of the loop is used to encrypt a message. The AES specification also formed the basis for the figures and descriptions of each step, placed in Section A.5.

## 4.3 Tools and Technologies

The verification language, SystemVerilog, was already given in the text. Synopsys VCS was recommended by the supervisors to be a good choice of tool for SystemVerilog simulations. Synopsys VCS in version 2005.06-SP2 was available at the university.

The module is verified with only simulation-based verification, no formal verification is used. The focus of the thesis was on simulation based verification from the start, and using formal verification in addition to this would require much more time than allowed for study, planning and implementation.

However, the AES module does contain a lot of mathematical operations, so formal verification could probably have been an effective way to verify some parts of the design.

## 4.4 Architecture

A simple, typical operation of the testbench was outlined in the first section of the verification plan. The chosen testbench flow is a very common one: Stimuli is generated at the top, and then applied to both the DUT and a reference model. The

results of the two are checked for equality.

An alternative way of checking this particular model could be to first encrypt the data, and then decrypt the output from the encryption using the same key. This approach was not chosen, since the more general testbench using a reference model acts better as an example of a verification system.

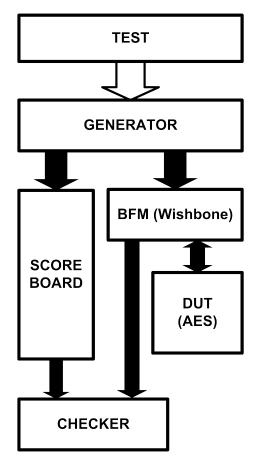

Layers are planned in Section B.4 of the verification plan. The layer division of the testbench follows the theory in [2], and could be seen in Figure B.1. The planned components of the testbench are a bit different compared to the theory.

The Driver and Monitor components are combined in a component called *bus functional model* (BFM. The two Wishbone operations from Driver and Monitor are more efficiently modelled in one component, since common functionality can be shared between the two operations. In addition, the two operations will have to communicate directly, since the reading of the output has to be performed a fixed number of clock cycles after the writing of the input. This is more easily modelled with one component (otherwise, a handshake signal would be necessary to allow direct communication).

Agent is removed, since there is no need for further processing of the input data in this case. The data is sent directly from the Generator to the BFM.

A plan of which classes that shall implement each other is provided in the same chapter. This is done much in the same way as in the examples in [2].

A figure showing the data float of the testbench has beed included as Figure B.2 in Appendix B. The data floating though the system is planned to be contained in objects. In this way, the data that belongs together keeps together through the system. A short description of the operation of each of the testbench components is given in Section B.7, as well as a description of the inputs and outputs.

The scenarios are planned in chapter B.6. The AES model does not have many different operations, so the scenarios are few. The three scenarios planned are encryption, decryption and system reset.

The last part of the architecture planning is the planning of the randomization features. The most obvious random feature of the testbench is to randomize the key and data inputs. A common constraint was planned for two inputs: A bathtub data distribution. The probability of values in the two extremes of the scale will then be higher, and more interesting values will be generated.

Scenarios will also be randomized. The testbench will use random functions to select between the three planned scenarios. The planned probability for each sce-

nario is listed in the scenarios list in Section B.6.

To make sure the handshake functions in the Wishbone bus works as good as proposed, a random delay is planned in the BFM. Each delay should be between 0 and 10 clock cycles.

## 4.5 Assertions

7 assertions were planned, and listed in Table B.10. In a real verification project it would be necessary to check a lot more details using assertions. To be able to complete the verification process in reasonable time, only a much smaller number of assertions were planned. However, since the planned assertions have different types and placements, they are good examples of the assertion planning (and implementation) tasks of a real-world verification project.

The assertion listing table (Table B.10) is inspired by [9]. For a larger verification project it could be better to create one table for each DUT block, like in [9].

#### 4.6 Implementation Phases

As described in Section 2.6.6, phases are the milestones of the testbench implementation process. Seven phases were planned. Since the DUT was a complete design when the verification planning started, there was no need for the phases to follow the steps in a design process. The phases were therefore quite straight forward planned, heading straight for the full testbench architecture.

The first phase is a bit special, since no other phases will use the functionality implemented in this phase. Its purpose is to make sure, at an early stage, that the chosen AES module actually communicates and could be simulated. The last six phases follows a natural flow of testbench implementation:

- Communication using Wishbone interface: The implementation of the BFM, which is the building block for all communication with the module

- Output checking using reference model: Implement the reference model (off the shelf model written in C) to run encryption in parallel with the DUT

- Assertions for checking properties: Implement the planned assertions in the DUT and on the bus interface

- Constrained random stimuli: Implement the random features of the testbench

- Coverage calculation: Implement functional cover groups, and enable the system for coverage report creation

- Verification of decryption functionality: Add features to enable verification of decryption functionality (most of the features in this phase are probably already implemented in previous phases)

The phases are listed in Table B.3. This list is also combined with the layers planned earlier to form a layer implementation list, as shown in Table B.4. This gives an overview of when (in which phase) each of the layers will need to be implemented. This is also shown graphically in the XY-grid of phases and layers in Table B.5.

With this phase plan, the system is built almost entirely from bottom to top with regard to the layers, which is natural as long as the DUT design is finished. If there were parts of the DUT not already finished, the flow might have been different.

## 4.7 Coverage Collection and Goals

First, code coverage was planned. A list of the code coverages to be analyzed was created, and placed in table B.11 in Appendix B. The goals are all set to 100%, meaning 100% explained coverage. All design space not covered will therefore have to be explained (e.g. impossible states).

The collection of functional coverage is planned in Table B.12. The first four are straight-forward cover groups to check data distribution of different signals. The two external ones will be checking the distribution of the Wishbone data signals. The two internal ones will check the distribution of the AES input signals. In this way, it can be verified that the bathtub function, as planned in earlier sections, works.

The last planned cover group will be checking the coverage of the S-Box. It will use cross coverage to check that all possible combinations of the two inputs are covered.

All function coverage collection was planned to be done using cover groups, not cover properties. The goals for each of them are 100% coverage.

## Chapter 5

# **Testbench Implementation**

T<sup>HIS CHAPTER</sup> describes the implementation of the verification system planned in the verification plan. The most important relevant properties of the SystemVerilog language are given in the language theory chapter, Section 3.2.2. Important references for the SystemVerilog language include Spear [2] and the VMM [6].

## 5.1 AES Module Simulation Test

This section describes the implementation of the phase 1 in the verification plan. Since the module to be verified was open source code, delivered with no guarantees or earlier test results, a small testbench was used to check if the module actually could be simulated with the available software.

This was done using an AES testbench posted on the same OpenCores project as a basis. The module worked well with this test. A few basic functionalities of the Synopsys VCS simulation software were also investigated during this test. A sample waveguide for this communication is shown in Appendix E.

## 5.2 Testbench Modules

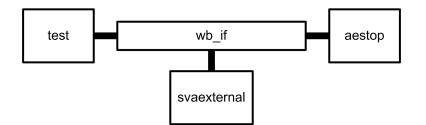

The module structure of the testbench is given in Figure 5.1. The blocks shown in this figure are the modules instantiated by top. Each one of them are implemented in their own file. Table 5.1 shows more details.

#### 5.2.1 Interface

The communication signals between the modules are gathered in an interface object. The reason to use an interface object is to gather all signal declarations in one place,

Figure 5.1: Testbench module structure

| Module name | File name      | Implemented as | Purpose                           |

|-------------|----------------|----------------|-----------------------------------|

| top         | top.sv         | Module         | Top-level module                  |

| test        | test.sv        | Program        | Containing layers and transactors |

| aestop      | aestop.sv      | Module         | New top module for DUT            |

| svaexternal | svaexternal.sv | Module         | Containing external assertions    |

| wb_if       | $wb_{if.sv}$   | Interface      | Signal interface                  |

Table 5.1: Testbench modules and files

as mentioned in the theory chapter.

First, the Wishbone signals are defined. The are defined as logic, a 4-state type. Then, three modports are defined, one for each of the modules to connect to the interface. Here the signal directions relative to the connecting module are stated. This is defined using *output* and *input* keywords.

#### 5.2.2 AES Top Module