# Modeling of Drain Current and Intrinsic Capacitances in Nanoscale Double-Gate and Gate-All-Around MOSFETs

Håkon Børli

Doctoral Thesis at NTNU, 2008:240

# Preface

The thesis is submitted in fulfillment of the requirements for the degree Philosophiae Doctor at the Norwegian University of Science and Technology. The work has mainly been carried out at University Graduate Center, Kjeller and partly at Universitat Rovira i Virgili, Tarragona, Spain. I have been part of the project Smart Micro Systems for Diagnostic Imaging in Medicine (SMIDA), which is funded by the Norwegian Research Council.

# Acknowledgements

I would like to express my sincere gratitude to Professor Tor A. Fjeldly for his visionary guidance, insightful counsel and constant encouragement throughout my Ph.D study. I have certainly been lucky, having had the neighboring office to such a distinguished professor whose door has always been open.

I am truly thankful to Professor Benjamin Iñiguez for helpful discussions, and for hosting me 3 months at Universitat Rovira i Virgili in Tarragona, Spain.

I will also thank my former Ph.D. colleague Dr. Sigbjørn Kolberg for many helpful discussions and problem solving sessions.

I also wish to acknowledge the continual, unconditional support from my family, especially my mother, Anne Grete, stepfather, Magnar, and parents-in-law, Nomi and Helge, who gave invaluable support through hard times.

Completion of my Ph.D. program is certainly a joint accomplishment with my wife, Siw, since only her love, understanding and encouragement has made it possible.

# Summary

A precise modeling framework for short-channel nanoscale double gate (DG) and gate-all-around (GAA) MOSFETs is presented covering all operating regimes from subthreshold to strong inversion.

In the subthreshold regime, the modeling of the electrostatics of the DG MOSFET is based on a conformal mapping analysis. This analytical 2D solution of Laplace's equation gives the inter-electrode capacitive coupling. The GAA MOSFET is a 3D structure to which the 2D conformal mapping technique is not directly applicable. However, due to the structural similarities, the DG calculations can also be applied with a high degree of precision to the cylindrical GAA MOSFET by performing a simple geometric scaling transformation to account for the difference in gate control in the two devices.

Near and above threshold, self-consistent procedures invoking the the 2D/3D Poisson's equation in combination with boundary conditions and suitable modeling expressions are used to model the electrostatics of the two devices.

The drain current is calculated as part of the self-consistent treatment, and based on the precise modeling of the 2D/3D electrostatics the intrinsic capacitances can also be extracted. The resulting electrostatics, drift diffusion current and intrinsic capacitances are in excellent agreement with numerical simulations.

A compact subthreshold drain current model for the GAA MOSFET is presented. Additionally, a parameterized model for drain current with all parameters extracted from the modeling framework is described. These are two examples of compact models suitable for inclusion in circuit simulators.

# Contents

| 1 | Intr | oducti  | on                                     | 1  |

|---|------|---------|----------------------------------------|----|

|   | 1.1  | Backgr  | round                                  | 1  |

|   |      | 1.1.1   | Device Scaling - Moore's Law           | 2  |

|   |      | 1.1.2   | Integrated Circuit Design              | 3  |

|   |      | 1.1.3   | Technical Computer Aided Design        | 3  |

|   |      | 1.1.4   | Circuit Simulation                     | 4  |

|   |      | 1.1.5   | Device Modeling                        | 5  |

|   | 1.2  | Object  | ive                                    | 5  |

|   | 1.3  | Scope   |                                        | 6  |

|   | 1.4  | List of | Publications and Own Contributions     | 7  |

|   |      | 1.4.1   | International Journal Articles         | 7  |

|   |      | 1.4.2   | International Conference Proceedings   | 8  |

|   |      | 1.4.3   | Posters                                | 8  |

|   |      | 1.4.4   | Own Contributions                      | 9  |

|   | 1.5  | Outlin  | e of Thesis                            | 10 |

| 2 | Rev  | riew of | DG and GAA MOSFET Models               | 13 |

|   | 2.1  | Layout  | t and Properties of DG and GAA MOSFETs | 13 |

|   | 2.2  | Essent  | ial Physics                            | 15 |

|   |      | 2.2.1   | Poisson's Equation                     | 15 |

|   |      | 2.2.2   | Fermi-Dirac and Boltzmann Statistics   | 16 |

|   |      | 2.2.3   | Quantum Inversion Charge               | 17 |

x CONTENTS

| 4 1  | Introd                                  | uction                                                                                                                                                                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nea  | r and                                   | Above Threshold                                                                                                                                                                                                   | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.5  | Comp                                    | act Subthreshold Current Model                                                                                                                                                                                    | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 3.4.2                                   | Cylindrical Gate-All-Around Device                                                                                                                                                                                | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 3.4.1                                   | Double Gate Device                                                                                                                                                                                                | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.4  | Subth                                   | reshold Drift-Diffusion Current                                                                                                                                                                                   | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 3.3.2                                   | Verification of GAA-Mapping Model                                                                                                                                                                                 | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 3.3.1                                   | Adaptation of the Double-Gate Solution                                                                                                                                                                            | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.3  | Gate-a                                  | all-Around MOSFET                                                                                                                                                                                                 | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 3.2.6                                   | DG Model Verification                                                                                                                                                                                             | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 3.2.5                                   | Asymmetric Gate                                                                                                                                                                                                   | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 3.2.4                                   | Corner Correction                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.2.3                                   | Solution of 2D Laplace Equation                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.2.2                                   | Inverse Transform                                                                                                                                                                                                 | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 3.2.1                                   | Schwarz-Christoffel Transform                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.2  |                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.1  | Introd                                  | uction                                                                                                                                                                                                            | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Inte | er-Elec                                 | trode Electrostatics                                                                                                                                                                                              | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.5  | Confo                                   | rmal Mapping                                                                                                                                                                                                      | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.4  |                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 2.3.4                                   | Capacitance Model GAA                                                                                                                                                                                             | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 2.3.3                                   | Drain Current Model GAA                                                                                                                                                                                           | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 2.3.2                                   | Capacitance Model DG                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 2.3.1                                   | Drain Current Model of Undoped DG                                                                                                                                                                                 | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.3  | Long-0                                  | Channel Modeling                                                                                                                                                                                                  | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 2.2.7                                   | Threshold Voltage                                                                                                                                                                                                 | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 2.2.6                                   | Substrate Doping                                                                                                                                                                                                  | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 2.2.5                                   | Capacitance Model                                                                                                                                                                                                 | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 2.2.4                                   | Transport Models                                                                                                                                                                                                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 2.4<br>2.5<br>Inte<br>3.1<br>3.2<br>3.3 | 2.2.5 2.2.6 2.2.7 2.3 Long-0 2.3.1 2.3.2 2.3.3 2.3.4 2.4 Short- 2.5 Conform  Inter-Elect 3.1 Introd 3.2 Doubl 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 3.2.6 3.3 Gate-a 3.3.1 3.3.2 3.4 Subth 3.4.1 3.4.2 3.5 Comp  Near and | 2.2.6 Substrate Doping 2.2.7 Threshold Voltage 2.3 Long-Channel Modeling 2.3.1 Drain Current Model of Undoped DG 2.3.2 Capacitance Model DG 2.3.3 Drain Current Model GAA 2.3.4 Capacitance Model GAA 2.3.4 Capacitance Modeling 2.5 Conformal Mapping 2.5 Conformal Mapping 2.6 Conformal Mapping 2.7 Schwarz-Christoffel Transform 3.2 Double-Gate MOSFET 3.2.1 Schwarz-Christoffel Transform 3.2.2 Inverse Transform 3.2.3 Solution of 2D Laplace Equation 3.2.4 Corner Correction 3.2.5 Asymmetric Gate 3.2.6 DG Model Verification 3.3 Gate-all-Around MOSFET 3.3.1 Adaptation of the Double-Gate Solution 3.3.2 Verification of GAA-Mapping Model 3.4 Subthreshold Drift-Diffusion Current 3.4.1 Double Gate Device 3.4.2 Cylindrical Gate-All-Around Device |

CONTENTS xi

|         | 4.2  | Double-Gate MOSFET                                | 59  |

|---------|------|---------------------------------------------------|-----|

|         |      | 4.2.1 DG Near Threshold                           | 59  |

|         |      | 4.2.2 DG Above Threshold                          | 69  |

|         | 4.3  | Gate-all-Around MOSFET                            | 78  |

|         |      | 4.3.1 GAA Near Threshold                          | 78  |

|         |      | 4.3.2 GAA Above Threshold                         | 83  |

| 5       | Dra  | in Current Modeling                               | 87  |

|         | 5.1  | Modeled Drift Diffusion Current                   | 87  |

|         | 5.2  | Compact Current Modeling                          | 88  |

|         | 5.3  | Transport formalisms                              | 89  |

| 6       | Cap  | pacitance Modeling                                | 91  |

|         | 6.1  | Subthreshold - Intrinsic Capacitances             | 92  |

|         |      | 6.1.1 Double Gate                                 | 92  |

|         |      | 6.1.2 Gate-All-Around MOSFET                      | 95  |

|         | 6.2  | Near and Above Threshold - Intrinsic Capacitances | 97  |

|         |      | 6.2.1 Double Gate MOSFET                          | 97  |

|         |      | 6.2.2 Gate-All-Around MOSFET                      | 100 |

|         | 6.3  | Extrinsic Overlap Capacitance                     | 102 |

| 7       | Con  | aclusion                                          | 103 |

| 8       | Fut  | ure Work                                          | 105 |

|         | 8.1  | Development of SPICE-Type Model                   | 105 |

|         | 8.2  | Noise                                             | 105 |

|         | 8.3  | FinFET                                            | 106 |

|         | 8.4  | Transport Mechanisms                              |     |

|         | 8.5  | Quantum Inversion Charge                          | 106 |

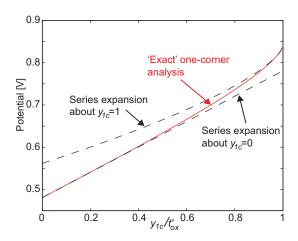

| ${f A}$ | Seri | es Expansion of One-Corner Potential              | 107 |

|         | A.1  | Introduction                                      | 107 |

xii CONTENTS

|              | A.2   | Series Expansion About $z_{1c} = 0 \dots \dots \dots \dots$ | 107 |

|--------------|-------|-------------------------------------------------------------|-----|

|              | A.3   | Series Expansion About $z_{1c} = t'_{ox}$                   | 108 |

| В            | Cor   | ner Correction - Integrals                                  | 111 |

| $\mathbf{C}$ | Cor   | ner Correction - Capacitance                                | 115 |

| D            | Diff  | Gerentiation of Inter-Electrode Potential                   | 117 |

|              | D.1   | First Derivative                                            | 117 |

|              | D.2   | Second Derivative                                           | 118 |

| Bi           | bliog | graphy                                                      | 121 |

# Notation

```

Permittivity of vacuum [C^2N^{-1}m^{-2}]

\varepsilon_0

Relative permittivity of gate-insulator

\varepsilon_{ox}

Relative permittivity of silicon

\varepsilon_{si}

\lambda_{DG}

Penetration depth of the electrostatic influence from

source and drain of the double gate MOSFET [m]

Penetration depth of the electrostatic influence from

\lambda_{GAA}

source and drain of the gate-all-around MOSFET [m]

Electron mobility [m^2V^{-1}s^{-1}]

\mu_n

Momentum relaxation time of electrons [s]

\tau_n

Center potential [V]

\phi_c

\Phi_m

Metal work function [J]

Total electrostatic potential, \varphi = \varphi_1 + \varphi_2 [V]

\varphi

Contribution from inversion charge to the electrostatic

\varphi_1

potential [V]

Contribution from inter-electrode coupling to the elec-

\varphi_2

trostatic potential [V]

Potential-profile of oxide gap [V]

\varphi_{ox}

\Psi_s

Potential at silicon-insulator interface [V]

Electron affinity of the semiconductor [J]

\chi_s

Oxide capacitance C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} [\text{Fm}^{-2}]

Silicon capacitance C_{si} = \frac{\varepsilon_{si}}{t_{si}} [\text{Fm}^{-2}]

C_{ox}

C_{si}

Trans- (X \neq Y) and self- (X = Y) capacitances [F]

C_{XY}

D_n

Electron diffusion coefficient [m<sup>2</sup>s<sup>-1</sup>]

Electric field [N C^{-1}]

\mathbf{E}

Fermi Energy level [J]

E_F

Band gap energy [J]

E_q

Reduced Planck's Constant [Js]

\hbar

I_{ds}

Drain current [A]

Drain current density (per unit channel width) [Am<sup>-1</sup>]

J_{ds}

```

XiV CONTENTS

```

k

Modulus of elliptic integral

\hat{k}

Complimentary modulus of elliptic integral, \hat{k}^2 = 1 - k^2

Boltzmann's constant [JK^{-1}]

k_B

L

Gate length [m]

Effective electron mass [kg]

m_n^*

Electron density [m^{-3}]

N_a

Acceptor doping density [m^{-3}]

Effective density of states for electrons [m<sup>-3</sup>]

N_{ceff}

Intrinsic electron density [m^{-3}]

n_i

Sheet electron density [m^{-2}]

n_s

Effective density of states for holes [m^{-3}]

N_{veff}

Electron charge [C]

Q_X

Charge associated with electrode X [Cm<sup>-1</sup>]

Equivalent cylindrical oxide thickness of GAA [m]

r_{ox}

Effective oxide thickness of GAA, r'_{ox} = \frac{\varepsilon_{si}}{\varepsilon_{ox}} r_{ox} [m]

r'_{ox}

Radius of GAA MOSFET silicon substrate [m]

r_{si}

T

Absolute temperature [K]

t_{ox}

Oxide thickness |m|

Effective oxide thickness, t'_{ox} = \frac{\varepsilon_{si}}{\varepsilon_{ox}} t_{ox} [m]

t'_{ox}

Silicon body thickness of DG MOSFET [m]

t_{si}

V_{bi}

Built in voltage [V]

Drain voltage, V_D = V_{bi} + V_{ds}, [V]

V_D

V_{ds}

Potential difference between drain and source [V]

V_F

Quasi Fermi potential [V]

V_{FB}

Flat band voltage for the gate [V]

Gate potential, V_G = V_{gs} - V_{FB} [V]

V_G

Gate potential referred to source potential [V]

V_{qs}

Saturation velocity [ms<sup>-1</sup>]

v_s

Source voltage, V_S = V_{bi} [V]

V_S

Thermal voltage, V_{th} = \frac{k_B T}{q} [V]

V_{th}

W

Channel width [m]

```

# List of Figures

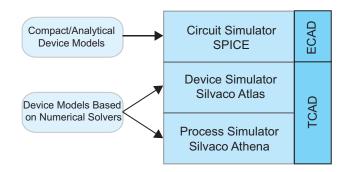

| 1.1 | Hierarchy of the TCAD and ECAD tools                                                                                                                                                                                                       | 4  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

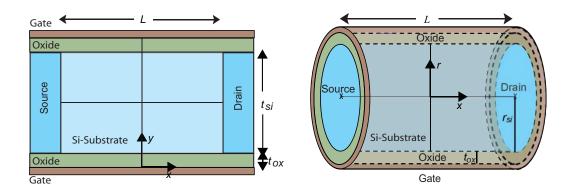

| 2.1 | Schematic structure of the DG MOSFET (left) and GAA MOSFET (right)                                                                                                                                                                         | 14 |

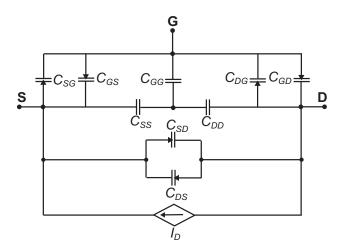

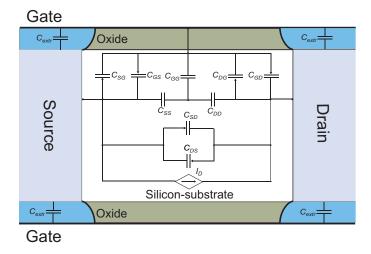

| 2.2 | Equivalent circuit of charge conserving intrinsic capacitances for three-terminal MOSFETs                                                                                                                                                  | 21 |

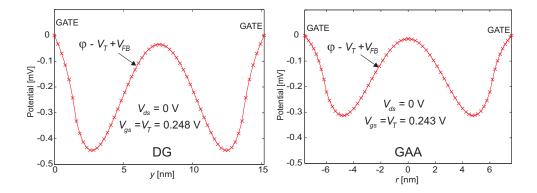

| 2.3 | Numerically simulated potential profiles along gate-to-gate symmetry line of the DG and GAA device at the threshold voltage.                                                                                                               | 22 |

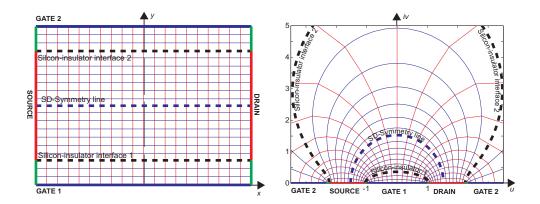

| 3.1 | Mapping of DG-device between the $(x, y)$ -plane and the transformed $(u, iv)$ -plane                                                                                                                                                      | 35 |

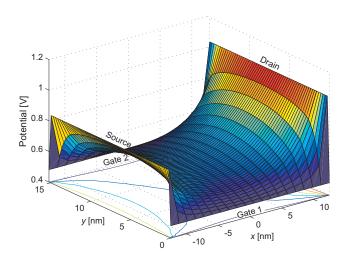

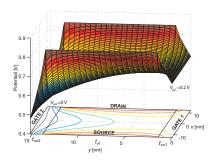

| 3.2 | Inter-electrode potential distribution for the DG MOSFET for $V_{ds} = 0.2 \text{V}$ and $V_{gs} = 0 \text{V}$ . This corresponds to subthreshold conditions for the device considered                                                     | 37 |

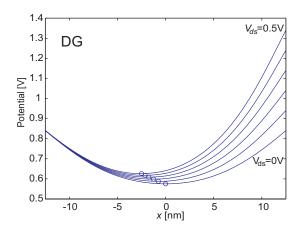

| 3.3 | The Laplace potential of (3.9) along the S-D symmetry line for $V_{gs}=0$ V and $V_{ds}=0,0.1,0.2,0.3,0.4,0.5$ V                                                                                                                           | 37 |

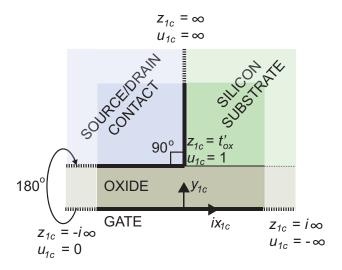

| 3.4 | One corner analysis in the $z_{1c}$ -plane with corresponding $u_{1c}$ -values along the boundary                                                                                                                                          | 38 |

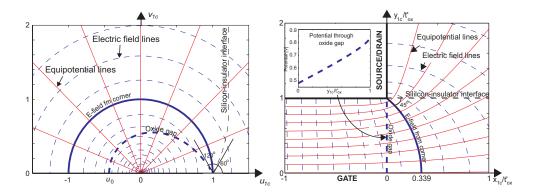

| 3.5 | Equipotential lines and electric field lines in the transformed $(u_{1c}, iv_{1c})$ -plane of one-corner analysis (left) and in the $(x_{1c}, y_{1c})$ -plane (right). The inset (right) shows the potential profile through the oxide gap | 39 |

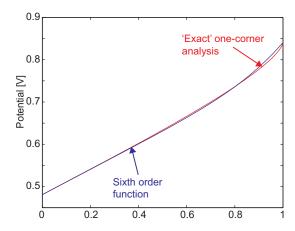

| 3.6 | The potential profile across insulator-gap of one-corner analysis (red) compared with $6^{th}$ order function                                                                                                                              | 41 |

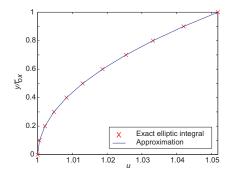

| 3.7 | Comparison of exact (3.1) and approximate (3.15) 4-corner transform across the G1-D insulator gap                                                                                                                                          | 42 |

| 3.8  | Inter-electrode potential distribution for the DG MOSFET including corner correction, $V_{ds} = 0.2$ V and $V_{gs} = 0$ V                                                                                                                                                   | 42 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | Asymmetrically biased DG device with $V_{gs1}=0.2\mathrm{V}$ and $V_{gs2}=0\mathrm{V}$ . $V_{ds}=0\mathrm{V}$ , $t_{ox1}=t_{ox2}=1.6nm$ and $\varepsilon_{ox1}=\varepsilon_{ox2}=7$                                                                                         | 44 |

| 3.10 | Asymmetric DG structure with $t_{ox1} = 4.0$ nm and $t_{ox2} = 1.6$ nm. $V_{gs1} = V_{gs2} = 0$ V, $V_{ds} = 0$ V and $\varepsilon_{ox1} = \varepsilon_{ox2} = 7$                                                                                                           | 44 |

| 3.11 | Asymmetric DG structure with $\varepsilon_{ox1} = 3$ and $\varepsilon_{ox2} = 10$ . $V_{gs1} = V_{gs2} = 0$ V, $V_{ds} = 0$ V and $t_{ox1} = t_{ox2} = 1.6$ nm                                                                                                              | 44 |

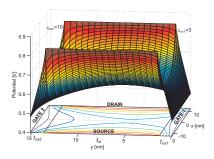

| 3.12 | Deviation between modeled inter-electrode potential distribution and numerical simulations (Silvaco Atlas) of Laplace contribution at different gate biasing, $V_{ds}=0\mathrm{V}$ in all plots                                                                             | 45 |

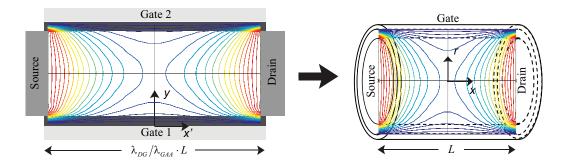

| 3.13 | Schematic illustration of the mapping of a DG MOSFET interelectrode potential distribution of an extended device of length $L' = \frac{\lambda_{DG}}{\lambda_{GAA}}L$ into the longitudinal cross-section of a GAA device of length $L$                                     | 47 |

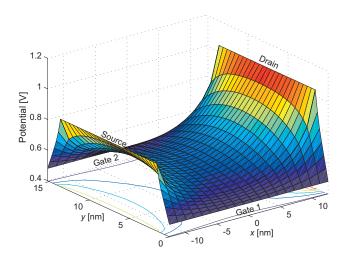

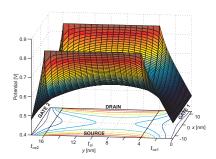

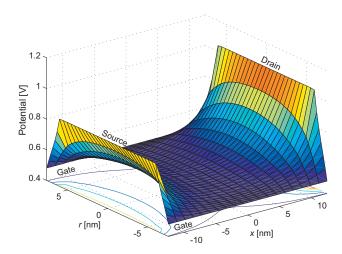

| 3.14 | Inter-electrode potential distribution for the longitudinal cross-section through the cylinder axis of the GAA device including corner correction, $V_{ds}=0.2\mathrm{V}$ and $V_{gs}=0\mathrm{V}$                                                                          | 48 |

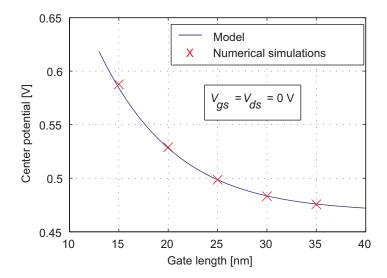

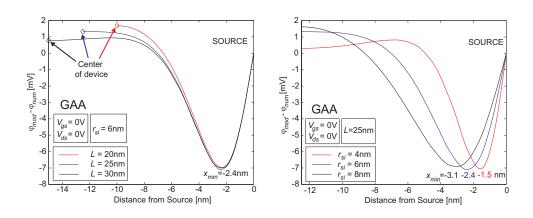

| 3.15 | Modeled and simulated scaling of the subthreshold center potential with gate length for GAA MOSFETs, $r_{si}=6$ nm and $t_{ox}=1.6$ nm                                                                                                                                      | 49 |

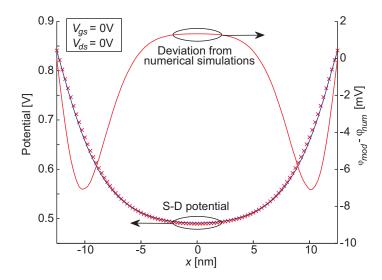

| 3.16 | Potential profile along the S-D symmetry line of the GAA device. Blue line is modeled potential, red x's are numerical simulated results. The red line indicates the deviation between model and simulations. $V_{GS}=V_{ds}=0\mathrm{V},\ t_{ox}=0.1\mathrm{nm}.\ .\ .\ .$ | 50 |

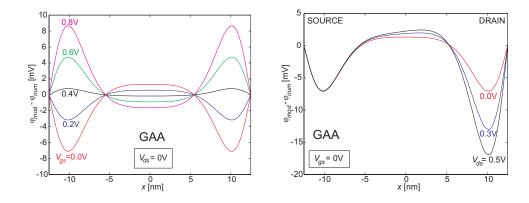

| 3.17 | Difference between model and numerical simulations of GAA device for $V_{ds}=0$ V and different $V_{gs}$ (left), and for $V_{gs}=0$ V and different $V_{ds}$ (right), $t_{ox}=0.1$ nm                                                                                       | 51 |

| 3.18 | Difference between model and numerical simulations of GAA device for different device lengths, $L$ and different silicon radius, $r_{si}$ , $V_{gs} = 0$ V, $V_{ds} = 0$ V $t_{ox} = 0.1$ nm                                                                                | 51 |

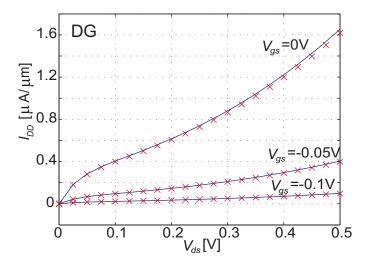

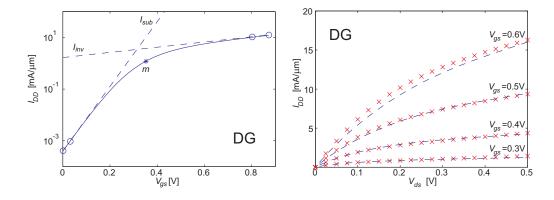

| 3.19 | Modeled subthreshold drift diffusion current for DG (blue lines) compared with numerical simulations (red symbols)                                                                                                                                                          | 53 |

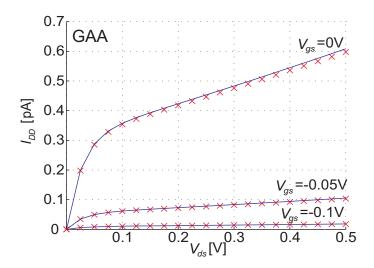

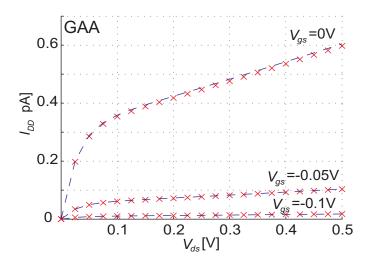

| 3.20 | Modeled subthreshold drift diffusion current for GAA (blue lines) compared with numerical simulations (red symbols)                                                                                                                                                         | 54 |

| 3.21 | Compact model of subthreshold drift diffusion current for GAA (blue dashed lines) compared with numerical simulations (red symbols)                                                                                                                                                                                                                                                                         | 57 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

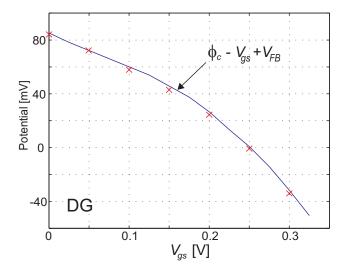

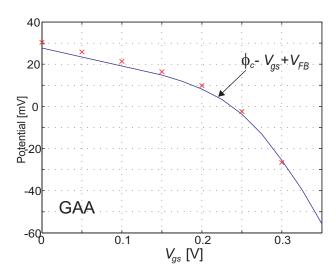

| 4.1  | The amplitude of the center potential, $\phi_c - V_{gs} + V_{FB}$ , plotted as a function of gate bias. The self-consistent solution is plotted with the blue line and the numerical simulations are marked with red symbols. $(V_{ds} = 0V)$                                                                                                                                                               | 61 |

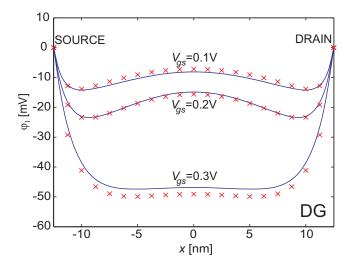

| 4.2  | The charge potential, $\varphi_1$ , along the S-D symmetry line for different gate biasing ( $V_{ds}=0$ V). Model is plotted with blue lines and numerical simulations indicated with red symbols.                                                                                                                                                                                                          | 62 |

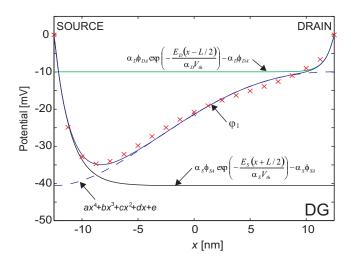

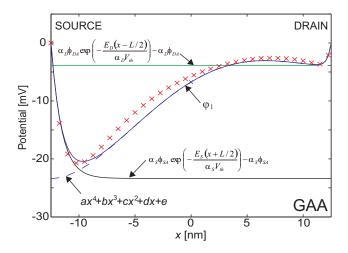

| 4.3  | The charge potential, $\varphi_1$ , along the S-D symmetry line for $V_{gs}=0.25\mathrm{V}$ and $V_{ds}=0.5\mathrm{V}$ . Different contributions to modeled charge potential are indicated. Numerical simulations are plotted with red symbols. Note that $\alpha_S\phi_{SA}$ and $\alpha_D\phi_{DA}$ have been subtracted from the exponential terms to ease the comparison of the different contributions | 65 |

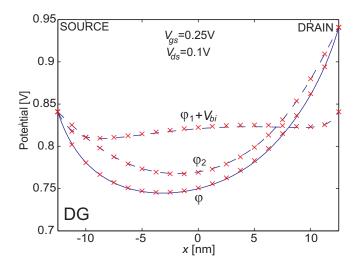

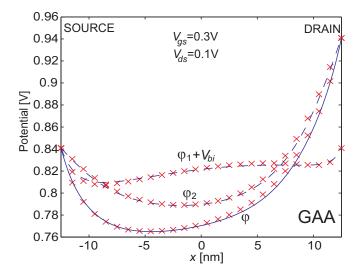

| 4.4  | Modeled and numerically simulated total potential, $\varphi$ , and the contributions, $\varphi_1$ and $\varphi_2$ along the S-D symmetry line for $V_{gs}=0.25\mathrm{V}$ and $V_{ds}=0.1\mathrm{V}$ . The constant voltage $V_{bi}$ has been added to $\varphi_1$ to ease the comparison of the different terms.                                                                                           | 66 |

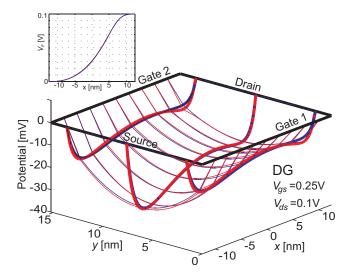

| 4.5  | Modeled charge potential, $\varphi_1$ , of the DG device (blue lines) compared to numerical simulations (Silvaco Atlas) (red lines). The plot includes 9 G-G cutlines, the S-D symmetry line (bold) and the silicon-insulator potential profiles (bold). Inset shows modeled quasi-Fermi potential $(V_F(x))$ (blue line) from source to drain compared to numerical simulations (red line)                 | 67 |

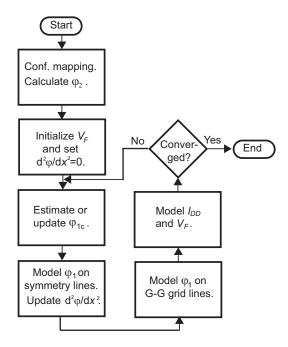

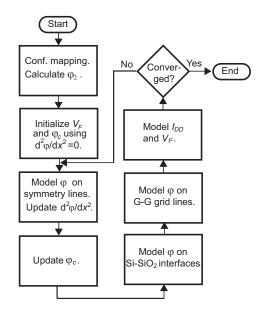

| 4.6  | Flow diagram of self-consistent procedure of calculating electrostatics and current in the near threshold regime                                                                                                                                                                                                                                                                                            | 68 |

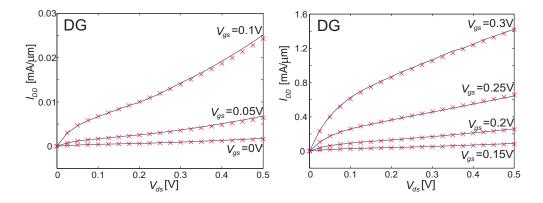

| 4.7  | Modeled drift-diffusion current in the near threshold regime for DG (blue lines) compared to numerical simulations (red symbols)                                                                                                                                                                                                                                                                            | 68 |

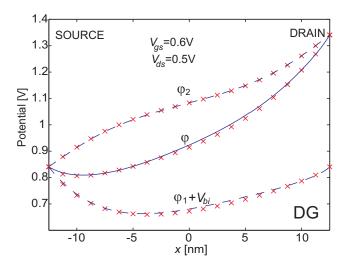

| 4.8  | Modeled and numerically simulated total potential and the contributions, $\varphi_1$ and $\varphi_2$ along the S-D symmetry line for $V_{gs}=0.6\mathrm{V}$ and $V_{ds}=0.5\mathrm{V}$ . The constant voltage $V_{bi}$ has been added to $\varphi_1$ to ease the comparison of the different terms.                                                                                                         | 70 |

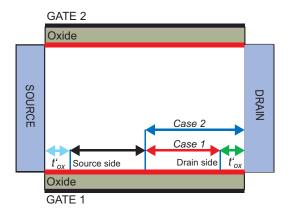

| 4.9  | Cross section of DG device with different modeling regions indicated                                                                                                                                                                                                                                                                                                                                        | 72 |

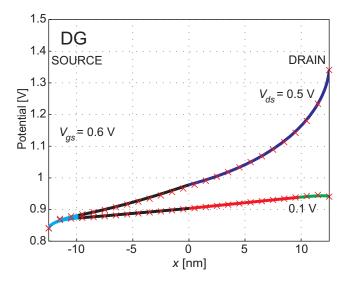

| 4.10 | Silicon-interface surface potential of DG device for $V_{gs} = 0.6$ V and $V_{ds} = 0.1$ V and 0.5V. Red symbols are numerical simulations (Silvaco Atlas)                                                                                                                                                                                                                                                                                                                                      | 72 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

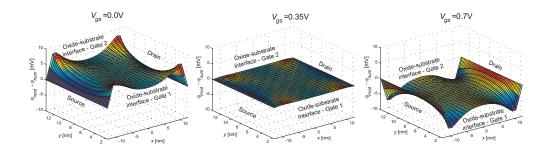

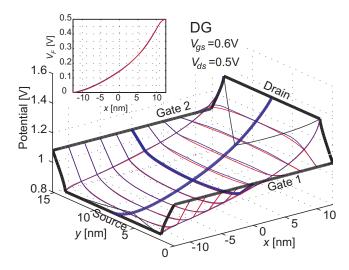

| 4.11 | Modeled electrostatics of DG device (blue lines) compared to numerical simulations (Silvaco Atlas) (red lines). Includes 9 G-G cutlines (G-G symmetry line in bold), the S-D symmetry line (bold) and the silicon-insulator potential profiles. Inset shows modeled quasi-Fermi potential (blue) from source to drain compared to numerical simulations (red)                                                                                                                                   | 76 |

| 4.12 | Flow diagram of self-consistent procedure of calculating electrostatics and current in the above threshold regime                                                                                                                                                                                                                                                                                                                                                                               | 77 |

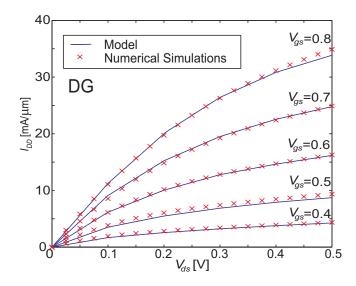

| 4.13 | Modeled drift-diffusion current in the above threshold regime for DG (blue lines) compared to numerical simulations (red symbols)                                                                                                                                                                                                                                                                                                                                                               | 77 |

| 4.14 | The amplitude of the center potential, $\phi_c - V_{gs} + V_{FB}$ , plotted as a function of gate bias. The self-consistent solution is plotted with the blue line and the numerical simulations are marked with red symbols. $(V_{ds} = 0V)$                                                                                                                                                                                                                                                   | 79 |

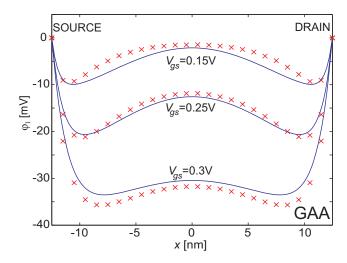

| 4.15 | The charge potential plotted along the S-D symmetry line for different gate biasing, $V_{ds}=0$ V. Model is plotted with blue lines and numerical simulations indicated with red symbols.                                                                                                                                                                                                                                                                                                       | 80 |

| 4.16 | The charge potential, $\varphi_1$ , along the S-D symmetry line for $V_{gs}=0.25\mathrm{V}$ and $V_{ds}=0.3\mathrm{V}$ . Different contributions to the modeled charge potential are indicated, ref. equation (4.11). Numerical simulations are plotted with red symbols. Note that $\alpha_S\phi_{SA}$ and $\alpha_D\phi_{DA}$ have been subtracted from the exponential terms associated with the source and drain sides, respectively, to ease the comparison of the different contributions | 81 |

| 4.17 | Modeled and numerically simulated total potential, $\varphi$ , and the contributions, $\varphi_1$ and $\varphi_2$ along the S-D symmetry line for $V_{gs}=0.3\mathrm{V}$ and $V_{ds}=0.1\mathrm{V}$ . The constant voltage $V_{bi}$ has been added to $\varphi_1$ to ease the comparison of the different terms                                                                                                                                                                                 | 81 |

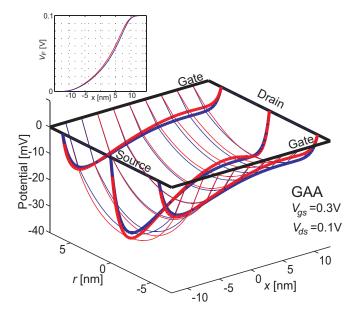

| 4.18 | Modeled charge contribution to the electrostatics of GAA device (blue lines) compared to numerical simulations (Silvaco Atlas) (red lines). Includes 9 G-G cutlines, the S-D symmetry line (bold) and the silicon-insulator potential profiles (bold). Inset shows modeled quasi-Fermi potential (blue line) from source to drain compared to numerical simulations (red line).                                                                                                                 | 82 |

|      | - ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

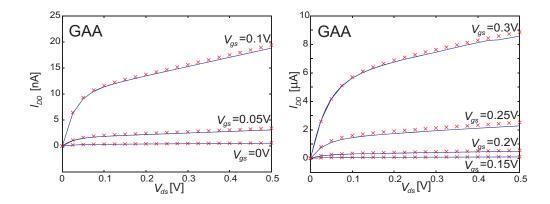

| 4.19 | Modeled drift-diffusion current in the near threshold regime for GAA (blue lines) compared to numerical simulations (red symbols)                                                                                                                                                                                                                                         | 83 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

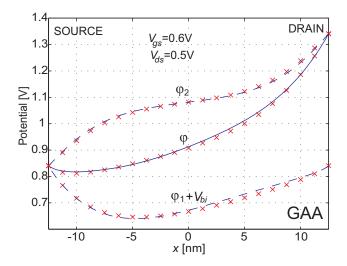

| 4.20 | Modeled and numerically simulated total potential, $\varphi$ , and the contributions, $\varphi_1$ and $\varphi_2$ plotted along the S-D symmetry line for $V_{gs}=0.6\mathrm{V}$ and $V_{ds}=0.5\mathrm{V}$ . The constant voltage $V_{bi}$ has been added to $\varphi_1$ to ease the comparison of the different terms.                                                  | 84 |

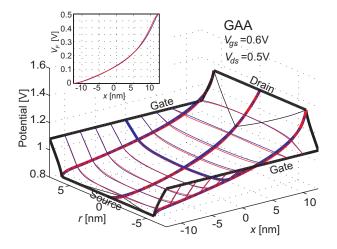

| 4.21 | Modeled electrostatics of GAA device (blue lines) compared to numerical simulations (Silvaco Atlas) (red lines). Includes 9 G-G cutlines (G-G symmetry line in bold), the S-D symmetry line (bold) and the silicon-insulator potential profiles. Inset shows modeled quasi-Fermi potential $(V_F(x))$ (blue) from source to drain compared to numerical simulations (red) | 86 |

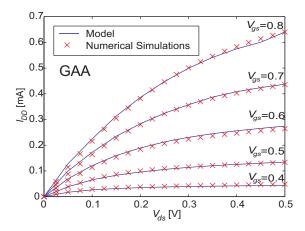

| 4.22 | Modeled drift-diffusion current in the near threshold regime for GAA (blue lines) compared to numerical simulations (red symbols)                                                                                                                                                                                                                                         | 86 |

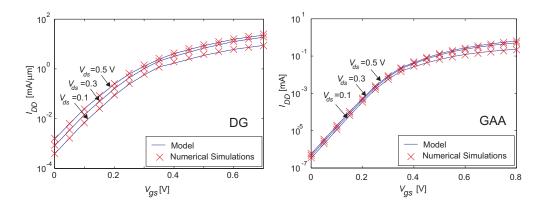

| 5.1  | Modeled and simulated transfer characteristics of DG (left) and GAA MOSFET (right) for $V_{ds}$ =0.1, 0.3 and 0.5V                                                                                                                                                                                                                                                        | 87 |

| 5.2  | To the left the subthreshold and strong inversion asymptotes (dashed lines) and the near threshold current calculation (asterisk) are illustrated. The solid lines are the resulting interpolating function. To the right, the modeled DG compact current (dashed lines) is compared to numerical simulations (symbols)                                                   | 88 |

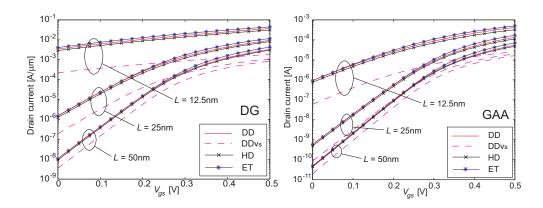

| 5.3  | Simulated DG (left) and GAA (right) drain current versus gate bias for different transport formalisms and gate lengths, $L=12.5, 25$ and 50nm. $V_{ds}=0.5$ V. (DD=drift diffusion with constant mobility, DDvs=drift diffusion with velocity saturation, HD=hydrodynamic, ET=energy transport)                                                                           | 89 |

| 6.1  | Cross section of DG and GAA device with equivalent circuit of charge conserving intrinsic capacitances, $C_{XY}$ . Extrinsic overlap capacitances, $C_{extr}$ , and boundaries between the intrinsic and extrinsic capacitances are indicated                                                                                                                             | 91 |

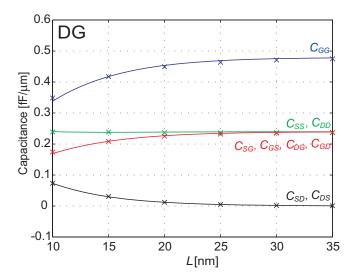

| 6.2 | Modeled intrinsic subthreshold capacitances (lines) plotted as a function of DG device length. Oxide and substrate thicknesses are held constant, $t_{si} = 12$ nm and $t_{ox} = 1.6$ nm. Model is bias independent. Numerical simulations (symbols) were carried out at $V_{ds} = 0$ V and $V_{gs} = -0.2$ V | 94  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3 | Radial cross-section of the GAA MOSFET. This surface must be rotated $360^{\circ}$ about the central axis to cover the cylindrical volume                                                                                                                                                                     | 95  |

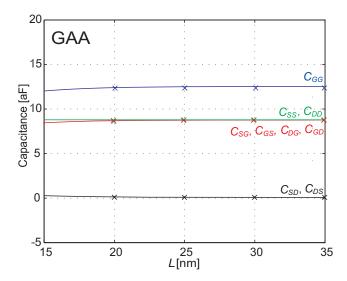

| 6.4 | Modeled intrinsic subthreshold capacitances (lines) plotted as a function of GAA device length. Radial dimensions are held constant, $r_{si}=6$ nm and $t_{ox}=1.6$ nm. Model is bias independent. Numerical simulations (symbols) were carried out at $V_{ds}=0$ V and $V_{gs}=-0.2$ V                       | 97  |

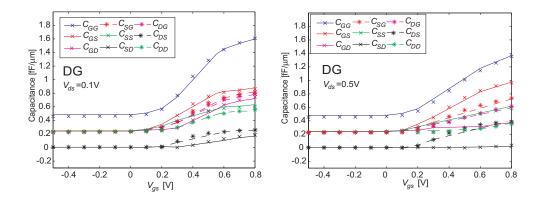

| 6.5 | Intrinsic capacitances of DG device as a function of $V_{gs}$ , for $V_{ds} = 0.1 \text{V}$ (left) and $V_{ds} = 0.5 \text{V}$ (right). Model is plotted with lines and numerical simulations with symbols                                                                                                    | 99  |

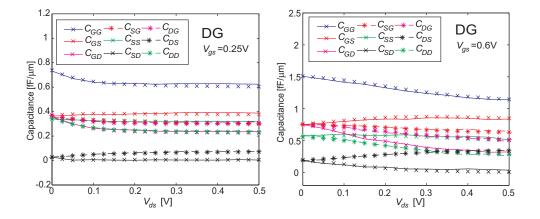

| 6.6 | Intrinsic capacitances of DG device as a function of $V_{ds}$ , for $V_{gs}=0.25\mathrm{V}$ (left) and $V_{gs}=0.6\mathrm{V}$ (right). Model is plotted with lines and numerical simulations with symbols                                                                                                     | 99  |

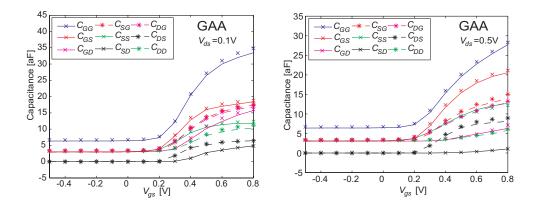

| 6.7 | Intrinsic capacitances of GAA device as a function of $V_{gs}$ , for $V_{ds} = 0.1 \text{V}$ (left) and $V_{ds} = 0.5 \text{V}$ (right). Model is plotted with lines and numerical simulations with symbols                                                                                                   | 101 |

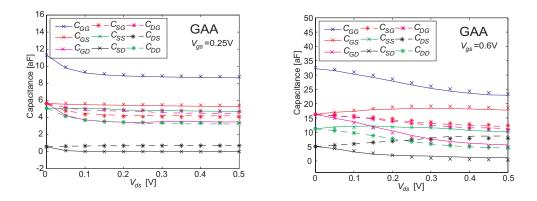

| 6.8 | Intrinsic capacitances of GAA device as a function of $V_{ds}$ , for $V_{gs}=0.25\mathrm{V}$ (left) and $V_{gs}=0.6\mathrm{V}$ (right). Model is plotted with lines and numerical simulations with symbols                                                                                                    | 101 |

| A.1 | The potential profile across insulator-gap of one-corner analysis compared to series expansions about $y_{1c} = 0$ and $y_{1c} = t'_{ox}$ .                                                                                                                                                                   | 109 |

# Chapter 1

# Introduction

## 1.1 Background

In December 1947 the first transistor was presented at the Bell laboratories by William Shockley, John Bardeen and Walter Battain. Since then, and in particular over the last 40 years, the semiconductor technology has developed with an amazing speed. The integrated circuit performance has grown exponentially with the scaling of the MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) dimensions as the primary driver. In high performance logic (i.e. processors) MOSFETs with 25nm physical gate lengths are now in production [1].

At this stage the long-lasting favorite of the industry, the single-gate MOS-FET, is reaching its scaling limit, and the search for alternative devices intensifies. In addition to finding a device with superior scaling properties, the industry will look for candidates that can be fabricated with a cost and yield comparable to the present devices. The double-gate (DG) and cylindrical gate-all-around (GAA) MOSFETs are, indeed, two of the most interesting devices to meet these criteria.

The scaling of the single-gate MOSFET into the sub-100nm range has been possible by using for example high doping and steep doping gradients, which is detrimental for the charge carrier mobility. One of the operation merits of thin body and low-doped DG devices is volume inversion in the entire silicon body in all operation regimes. This volume inversion effect enhances charge carrier mobility particularly in the subthreshold regime, where the main channel of charge transport is along the source-to-drain symmetry line [2][3]. When increasing the gate biasing, moving from subthreshold into the

2 Introduction

near and above threshold regimes, the current channel will shift from the center to the two silicon-insulator interfaces.

The GAA MOSFET can also, indeed, be designed to benefit from the volume inversion effect. Additionally, the GAA MOSFET obtains better scaling properties compared to the DG MOSFET as the cylindrical gate improves the gate control and suppresses short channel effects [3][4].

Many activities are going on in parallel for the semiconductor technology to continue its development to reach the future expectations of performance. One of these activities is device modeling, which gives a deeper understanding of the physical behavior of the devices. Compact models are also important tools in circuit design and simulation. These new devices pose a new challenge in device modeling as the field pattern is two and three dimensional. This is in contrast to many of the classical single gate 1D models which in their development are based on an increasing number of non-physical fitting parameters of obscure origin.

Another point is that the classical definition of the threshold voltage, which normally marks the onset of the device, loses much of its meaning in the undoped/lightly doped DG an GAA devices, as described in further detail in section 2.2.7.

A new model paradigm based on the specific central physical mechanisms in these kind of devices is therefore desirable and is the inducement to the work presented in this thesis.

### 1.1.1 Device Scaling - Moore's Law

Moore's Law describes an important trend in the history of computer hardware. It says that the number of transistors that can be inexpensively placed on an integrated circuit is increasing exponentially with time, doubling approximately every two years. The observation was first made by Intel cofounder Gordon E. Moore in 1965. The trend has continued up till today and is not expected to stop for another decade.

Almost every measure of the capabilities of digital electronic devices is linked to Moore's Law, for example processing speed and memory capacity. All of these are improving at roughly exponential rates as well. This has dramatically increased the usefulness of digital electronics in nearly every segment of the world economy. Moore's Law describes this as a driving force of technological and social change in the late 20th and early 21st century.

1.1 Background 3

### 1.1.2 Integrated Circuit Design

The evolution of very large scale integration (VLSI) technology has developed to the point where over two billion transistors can be integrated on a single chip<sup>1</sup>. Integrated circuits were normally subsystem components, partitioned by analog and digital boundaries. Now, however, complete systems are integrated on a chip combining both analog and digital functions. Complementary metal-oxide semiconductor (CMOS) technology has become the most widespread in these implementations because it provides density and power savings on the digital side, and a good mix of components for analog design [5].

### 1.1.3 Technical Computer Aided Design

Process and device simulators are technical computer aided design (TCAD) tools. The TCAD tools apply numerical derivations based on complex equations, such as partial differential equations, to predict the behavior of the device.

The process simulators can predict the structures that result from specified process sequences (such as diffusion and ion implantation), based on the physics and chemistry of the semiconductor processes. Athena from Silvaco is one example of a process simulator.

Numerical device simulators, on the other hand, predict the electrical characteristics that are associated with specified physical structures and bias conditions. This normally involves an iterative solution of Poisson's equation combined with a transport model for a given set of boundary conditions. A common way to accomplish this is by discretizing the 2D surface or 3D volume in a grid, and applying a partial differential equation solver to find solutions at the grid points in an iterative manner. The convergence and accuracy depend on the size an layout of the grid, and the complexity of the applied physical models.

In this work we have not considered the processing steps of the device. However, as experimental data is not readily available for the nanoscale devices considered, we use the Atlas device simulator from Silvaco to verify the accuracy of of our modeling framework. Atlas has a range of models for transport, carrier statistics, material properties, etc. These can be combined in the simulation of a wide range of customized 2D and 3D device geometries.

<sup>&</sup>lt;sup>1</sup>Intel Itanium (code named Tukwila) was launched in February 2008 as the world's first microprocessor containing more than two billion transistors.

4 Introduction

#### 1.1.4 Circuit Simulation

Integrated circuits, unlike board-level designs composed of discrete parts, are impossible to breadboard before manufacture. In addition, the high costs of photolithographic masks and other manufacturing prerequisites make it essential that the circuit is as close to perfect as possible before the integrated circuit is built. Simulating the circuit with a circuit simulator is therefore required to verify circuit operation before manufacturing the integrated circuit.

Tools for simulating the behavior of simple circuits, electronic computer aided design tools (ECAD), began emerging in parallel with the development of integrated circuits. SPICE (Simulation Program with Integrated Circuit Emphasis) was first released in 1972 by Electronics Research Laboratory of the University of California, Berkeley, as a derivative of the CANCER program (Computer Analysis of Non-linear Circuits, Excluding Radiation) [6]. Since then SPICE has gone through several evolutions and is widely used by circuit designers.

One of the key building blocks in SPICE is the device models. Different research groups have steadily provided models and modeling approaches to SPICE, continuously improving the functionality of the simulator. The BSIM MOSFET model invented by the Berkeley group was the industry standard for many years. In 2005, however, the Compact Model Council, which works for standardization of compact models and model interfaces, decided to make the PSP model [7] developed by Phillips semiconductors and Pennsylvania State University, the industry standard.

SPICE simulators come with a selection of models for different semiconductors. The simplest models can be accessed quickly and may give adequate

Figure 1.1: Hierarchy of the TCAD and ECAD tools.

1.2 Objective 5

results in many situations. For improved accuracy, the more complex models should be applied. These are often characterized by many parameters which must be identified empirically by analyzing measurements or by TCAD simulations. This is time-consuming and a difficult task considering that some models use hundreds of parameters, which cannot always be associated directly with physical mechanisms. Some manufacturers, however, provide ready to use SPICE parameters for their products, and some device simulators come with parameter extraction tools, which can be used directly as input to the SPICE models.

### 1.1.5 Device Modeling

Figure 1.1 illustrates the hierarchy of the TCAD and ECAD tools as described above. As indicated compact/analytical devices models are the fundamental building blocks of an efficient circuit simulator.

In this thesis, a compact physics based device model is a description of the device behavior in terms of analytical, mathematical expressions. The most efficient models are the ones which only involve explicit analytical expressions. Another approach is based on preprocessing routines which result in parameter look-up tables for fast retrieval and use in simplified parameterized models.

## 1.2 Objective

The objective of the thesis is to establish a detailed, physically based framework for precise modeling of short-channel DG and GAA MOSFETs. From this modeling scheme we may extract current-voltage and intrinsic capacitance characteristics of the devices. The framework may also serve as a starting point for the development of more compact modeling expressions suitable for use in circuit simulators.

The modeling framework is based on a two- and three-dimensional (2D and 3D) analysis for the DG and GAA MOSFETs, respectively. Short channel effects are intrinsic to this 2D and 3D analysis. The inter-electrode coupling of the DG device is solved analytically for the 2D device geometry, and with appropriate modifications it can also be applied to model the inter-electrode coupling of the 3D GAA device. The effect of the inversion charges are included self-consistently in an iterative procedure.

6 Introduction

## 1.3 Scope

In the endeavor to model the behavior of nanoscale short-channel DG and GAA devices the main challenges are to determine the 2D/3D electrostatics, self-consistent modeling, charge transport, quantum-mechanical effects, gate tunneling and noise. Below follows a summary of to what extent these topics are addressed in this thesis.

2D and 3D electrostatics. In this work we are considering, as an example, a DG and GAA MOSFET with gate length of 25nm and a silicon body thickness/diameter of 12nm, ref. figure 2.1. This length/height ratio implies that there is a significant coupling, not only between the gate contacts but also between the source/drain contacts. Therefore a 2D solution is required to cover these mechanisms. Additionally, the cylindrical geometry of the GAA MOSFET must be properly accounted for with a 3D analysis.

Self-consistent modeling of inversion charge effects. Near and above threshold the electrostatic influence from the inversion charges becomes significant and has to be taken into consideration. We model the inversion charge contribution in a self-consistent manner in accordance with the 2D and 3D Poisson's equation for the DG and GAA MOSFET, respectively.

Charge transport. In nanoscale MOSFETs with channel lengths less than 100nm [8], the relaxation times of the carriers indicate that the drain current will have the character of both drift diffusion and ballistic transport. Numerical simulations, however, indicate that the use of the drift diffusion mechanism with constant mobility, reproduces quite well the current found from more advanced simulations. Hence, in all simulations used for comparison with the present model, we also use the drift diffusion mechanism with constant mobility. This serves the additional purpose of verifying the overall modeling procedures used. Ballistic and quasi-ballistic transport are briefly discussed in the review of models in section 2.2.4, and the drift-diffusion model is compared to the more sophisticated transport formalisms in chapter 5.

Quantum mechanical effects. When device dimensions are larger than 10nm, classical theory is still applicable [9], and the modeling framework presented in this thesis is based on classical theory. For smaller dimensions, quantum confinement has to be considered, and in section 2.2.3 a simplified quantum confinement model is briefly reviewed.