Qubo Hu

Hierarchical Memory Size Estimation for Loop Transformation and Data Memory Platform Optimization

PhD thesis Norwegian University of Science and Technology

## Abstract

In today's embedded systems, the memory hierarchy is rapidly becoming a major bottleneck in terms of power, performance and area, due to the very large amount of (memory related) data need to be transferred and stored (temporarily). This is especially the case for portable multi-media applications systems. These applications are characterized by deep loop nests and multi-dimensional arrays at the high level. Due to the dramatically increasing size and complexity of system-on-a-chip (SoC) designs and stringent time-to-market requirement, the methodology and tools for chip design must be raised to the system level. Early analysis tools are particularly critical in enabling SoC designers to take full advantage of the many architectural options available. For memory optimization, the early high level techniques aim either to design an optimal memory platform for a given application or to optimize the application code in order to take advantage of the memory platform features, or even both. Loop transformation is such an important high level optimization technique. It modifies the execution order of loops and statements without changing the application functionality. Existing loop transformation algorithms are all performed based either on reduction of data access lifetime and on improvement in data locality and regularity to steer selection of loop transformations. These are, however, very abstract cost functions which do not represent the exact memory size requirement of the arrays and how the data will be mapped onto the memory platform later on. Existing algorithms all result in one final loop transformation solution. As different loop transformations may result in optimal utilization for different memory platform instances, ad-hoc decisions at this stage without estimating their impact on the actual hierarchy utilization can lead to a final sub-optimal solution. An evaluation of later design stages' effort is hence required. On the other hand, there usually exist a huge number of loop transformation possibilities, the estimation is required to be performed repeatedly and its computation time of the estimation technique also becomes critical to make it useful during the loop transformation search space

#### exploration.

This dissertation proposes a memory footprint estimation methodology. An intra-array memory footprint estimation is performed first followed by an interarray estimation. In order to achieve a fast estimate to make it useful repeatedly during the early high level search space exploration, several techniques have been introduced. A fast intra-array memory footprint estimation is performed at the iteration domain based on the maximal lifetime of data accesses, which is defined by the maximal dependency vector. Two approaches, an ILP formulation and vertexes approach, have been introduced for achieving a fast maximal dependency vector calculation. The fast inter-array estimation has been achieved based on several Hanoi tower based approaches.

A hierarchical memory size estimation methodology has also been proposed in this dissertation. It estimates the influence of any given sequence of loop transformation instances on the mapping of application data onto a hierarchical memory platform. As the exact memory platform instantiation is often not yet defined at this high level design stage, a platform independent estimation is introduced with a Pareto curve output for each loop transformation instance. It can steer the designer or an automatic steering tool to select all the interesting loop transformation instances that might later lead to low power data mapping for any of the many possible memory hierarchy instances. This is useful when the memory platform is not defined yet, or for a given memory hierarchy instance. It also allows to find the most appropriate low power memory hierarchy instance by performing an early power estimation of different memory hierarchy instances. Initially the source code is used as input for estimation, resulting in an initial approach. However, performing the estimation repeatedly from the source code is too slow for the large loop transformation search space exploration. An incremental approach, based on local updating of the previous result, is thus introduced to handle sequences of different loop transformations. Several advanced techniques have also been used on these two approaches in order to perform a fast estimation, such as bounding box geometrical model based data reuse analysis, platform independent memory hierarchy layer assignment estimation, fast intra- and inter-array memory footprint estimation.

The feasibility and usefulness of the methodologies are substantiated using several representative real-life application demonstrators. It shows for instance that the fast memory footprint estimation can be two order of magnitude faster than compared techniques while still achieving fairly accurate estimation result. For hierarchical memory size estimation methodology, the initial approach is two order of magnitude faster than the compared technique and the incremental ap-

#### ABSTRACT

proach is another two order of magnitude faster than the initial approach, which can just take a few milliseconds. The fast computation time of the incremental approach make it feasible to be used repeatedly during the loop transformation exploration over a very large number of possibilities. Furthermore, prototype CAD tools has been developed that includes mast parts of the methodologies.

# Preface

This dissertation is submitted to the Norwegian University of Science and Technology (NTNU) in partial fulfillment of the requirements for the degree of *doktor ingeniør* (corresponds to Ph.D).

The Ph.D study consisted of compulsory courses corresponding to one year full-time studies, one year of teaching assistantship and other duties, as well as the research activity, and conducted in the period from October 2002 to April 2007. The work herein was performed at and founded by the Department of Electronics and Telecommunications, NTNU, under the supervision of Associate Professor Per Gunnar Kjeldsberg. I have also performed many time visits, in total about one year, to IMEC for research cooperation under the supervision of Professor Francky Catthoor.

## Acknowledgments

When I am writing down these words at the quiet night, I cannot stop myself passing back through the days and nights of the last four years. This is a journey full of various experience and feeling, with no lack of joys and frustrations. I am so still when I get here and now look back at this journey. Fortunately, I am not lonely and I am accompanied with my advisors and colleges for guidance, idea inspiration, discussions, support and also having fun together. I would like to express my grateful thanks to all who have been helped me in this part of my life.

I would first like to thank Associate Professor Per Gunnar Kjeldsberg, who has been my advisor, for bringing me to this exciting research direction and introducing me for the cooperation with researcher at IMEC, Leuven, Belgium. This work would not have been so without his excellent encourage and guidance, valuable suggestions, and generous help and supports. I am so glad for his accompany and bringing me up. I am extremely grateful to Professor Francky Catthoor, who has been my coadvisor at IMEC, for his excellent guidance, invaluable suggestions and idea inspiration, fruitful discussion and feedback. Francky Catthoor introduced me to the topic that I have focused on, and has been continuously available for my requests. My deepest gratitude also goes to Arnout Vandecappelle, Martin Palkovic, Erik Brockmeyer and Sven Verdoolaege for their significant supports, discussions and new inputs through my work.

I would also like to thank Dr. Benny Thörnberg from Mid-Sweden University, Sundsvall, Sweden, for a lot of valuable discussions and cooperation with him.

I would also like to thank my colleagues and friends at the Department of Electronics and Telecommunications, NTNU and especially those of the Circuit and System group. My special thanks go out to our group leader, Professor Einar J. Aas for his valuable discussion, friendly help and kindly barbecue organization. Likewise, I would like to thank the people and friends working at IMEC for their helps and making my life enjoyable and colorful during my many times visits over there. In addition to those already mentioned by name, I am in particular indebted to the following persons (in alphabetic order):

Bart Durinck Eddy De Greef Øystein Gjermundnes Jing Guo Tajeshwar Singh Joar Sæther Tanja Van Achteren Sven Verdoolaege Kaidong Xu Peng Yang

Last but not least, I want to thank my wife Jing for all her support. Thanks for my eleven weeks old son for his inspiring smiles and big cooperation during the finalization stage of this work. My thanks also go to my uncle Zhou for his encourage to me for taking my PhD study. Thank my parents for their support throughout these years.

# Contents

| Al | Abstract ii |         |                                              |      |  |

|----|-------------|---------|----------------------------------------------|------|--|

| Pr | Preface vi  |         |                                              |      |  |

| Li | st of A     | Abbrevi | iations                                      | xix  |  |

| 1  | Intr        | oductio | n                                            | 1    |  |

|    | 1.1         | Backg   | round and Motivation                         | . 1  |  |

|    | 1.2         | Proble  | m Statement and Objective                    | . 4  |  |

|    | 1.3         | Applic  | cation Domain and Targeted Architecture      | . 5  |  |

|    | 1.4         | Main (  | Contributions                                | . 7  |  |

|    | 1.5         | Outlin  | e                                            | . 8  |  |

| 2  | Rela        | nted wo | rk                                           | 11   |  |

|    | 2.1         | System  | n Level Memory Synthesis and Optimization    | . 12 |  |

|    | 2.2         | Data T  | Fransfer and Storage Exploration Methodology | . 13 |  |

|    |             | 2.2.1   | Pruning and Related Preprocessing Step       | . 15 |  |

|    |             | 2.2.2   | Global Data Flow Transformation              | . 15 |  |

|    |             | 2.2.3   | Global Loop Transformations                  | . 16 |  |

|    |             | 2.2.4   | Data Reuse Analysis                          | . 16 |  |

|    |             | 2.2.5   | Memory Hierarchy Layer Assignment            | . 17 |  |

|    |             | 2.2.6   | Storage Cycle Budget Distribution            | . 18 |  |

|    |             | 2.2.7   | Memory Allocation and Assignment             | . 18 |  |

|    |             | 2.2.8   | Memory Data Layout Optimization              | . 19 |  |

|    | 2.3         | Loop    | Transformations                              | . 20 |  |

|    | 2.4         | Memo    | ory Size Estimation                          | . 22 |  |

|    |             | 2.4.1   | Scalar-based Estimation                      | . 22 |  |

|    |             | 2.4.2   | Array-based Estimation                       | . 22 |  |

| CONTEN | NTS |

|--------|-----|

|--------|-----|

|   | 2.5  | Memo      | ory In-place | e Optimization                            | 26 |

|---|------|-----------|--------------|-------------------------------------------|----|

| 3 | Geo  | metrica   | al Model a   | nd Loop Transformations                   | 29 |

|   | 3.1  | Polyhe    | edral Geon   | netrical Model                            | 29 |

|   |      | 3.1.1     | Iteration    | Domain                                    | 30 |

|   |      | 3.1.2     | Data Dor     | main                                      | 32 |

|   |      | 3.1.3     | Executio     | n Ordering and Common Iteration Space     | 34 |

|   |      | 3.1.4     |              | pendencies                                | 35 |

|   |      |           | 3.1.4.1      | -                                         | 36 |

|   |      |           | 3.1.4.2      | Dependency Relation                       | 36 |

|   |      | 3.1.5     | Depende      | ency Vector                               | 37 |

|   |      | 3.1.6     |              | d EDV                                     | 38 |

|   |      | 3.1.7     |              | Single Assignment Code                    | 40 |

|   |      | 3.1.8     |              | d Code Constraints                        | 40 |

|   | 3.2  | Bound     | ling Box G   | eometrical Model                          | 41 |

|   | 3.3  |           |              | ations in the Geometrical Model           | 44 |

|   |      | 3.3.1     |              | ental for Unimodular Loop Transformations | 45 |

|   |      |           | 3.3.1.1      | Loop Interchange                          | 48 |

|   |      |           | 3.3.1.2      | Loop Reversal                             | 49 |

|   |      |           | 3.3.1.3      | Loop Skewing                              | 50 |

|   |      |           | 3.3.1.4      | Loop Fusion                               | 50 |

|   |      |           | 3.3.1.5      | Loop Shifting                             | 51 |

|   |      | 3.3.2     | Non-affin    | ne Loop Transformations                   | 54 |

|   |      |           | 3.3.2.1      | Strip Mining                              | 54 |

|   |      |           | 3.3.2.2      | Loop Tiling                               | 54 |

| 4 | Fast | : Intra-A | Arrav Me     | mory Footprint Estimation                 | 57 |

|   | 4.1  |           | •            | ory Footprint Estimation                  | 58 |

|   |      | 4.1.1     | •            | on for Single Pair Dependencies           | 59 |

|   |      |           | 4.1.1.1      | Illustration on an Example                | 59 |

|   |      |           | 4.1.1.2      | General Estimation Algorithm              | 61 |

|   |      |           | 4.1.1.3      | Comparison with the EDV Approach          | 63 |

|   |      | 4.1.2     |              | on for Multiple Pair Dependencies         | 65 |

|   | 4.2  |           |              | ulation                                   | 66 |

|   |      | 4.2.1     |              | Approach for MDV/EDV Calculation          | 66 |

|   |      | 4.2.2     |              | exes Approach for MDV/EDV Calculation     | 68 |

|   | 4.3  |           |              | s and Exceptions                          | 71 |

|   |      | 4.3.1     |              | Footprint Estimation Errors               | 71 |

Х

| CONT | <b>ENTS</b> |

|------|-------------|

|------|-------------|

| 6       Initial Hierarchical Memory Size Estimation       85         6.1       Intra-array Size Estimation       86         6.2       Data Reuse Analysis       89         6.2.1       Comparison with Other DRA Techniques       93         6.3       Memory Hierarchy Layer Assignment Estimation       95         6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       97         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       114         8.1.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115                                                          |   | 4.4   | 4.3.2 MDV Calculation Errors                                 | 73<br>74 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|--------------------------------------------------------------|----------|

| 5.1       Initial One Layer Hanoi Tower Approach       78         5.2       Multiple Layer Hanoi Tower Approach       79         5.3       Improved One Layer Hanoi Tower Approach       82         5.4       Summary       82         6       Initial Hierarchical Memory Size Estimation       85         6.1       Intra-array Size Estimation       85         6.2       Data Reuse Analysis       89         6.2.1       Comparison with Other DRA Techniques       93         6.3       Memory Hierarchy Layer Assignment Estimation       95         6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       96         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       104         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Ateuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration <t< td=""><td>5</td><td>Fast</td><td>Inter-Array Memory Footprint Estimation</td><td>77</td></t<> | 5 | Fast  | Inter-Array Memory Footprint Estimation                      | 77       |

| 5.2       Multiple Layer Hanoi Tower Approach       79         5.3       Improved One Layer Hanoi Tower Approach       82         5.4       Summary       82         6       Initial Hierarchical Memory Size Estimation       85         6.1       Intra-array Size Estimation       85         6.2       Data Reuse Analysis       89         6.2.1       Comparison with Other DRA Techniques       93         6.3       Memory Hierarchy Layer Assignment Estimation       95         6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       97         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Hierarchical Memory Size Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       114         8.1.1       Power Estimation For A Given Memory Platform                                                                                      | 0 |       |                                                              |          |

| 5.3       Improved One Layer Hanoi Tower Approach       82         5.4       Summary       82         6       Initial Hierarchical Memory Size Estimation       85         6.1       Intra-array Size Estimation       85         6.2       Data Reuse Analysis       89         6.2.1       Comparison with Other DRA Techniques       93         6.3       Memory Hierarchy Layer Assignment Estimation       95         6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       96         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       104         7.1       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.2       Power Estimation                                                                                      |   |       | • • • • • • • • • • • • • • • • • • • •                      |          |

| 5.4       Summary       82         6       Initial Hierarchical Memory Size Estimation       85         6.1       Intra-array Size Estimation       86         6.2       Data Reuse Analysis       89         6.2.1       Comparison with Other DRA Techniques       93         6.3       Memory Hierarchy Layer Assignment Estimation       95         6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       97         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       114         8.1.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       <                                                                                 |   |       |                                                              |          |

| 6.1       Intra-array Size Estimation       86         6.2       Data Reuse Analysis       89         6.2.1       Comparison with Other DRA Techniques       93         6.3       Memory Hierarchy Layer Assignment Estimation       95         6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       96         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       114         8.1.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform Configurati                                         |   |       |                                                              | 82<br>82 |

| 6.1       Intra-array Size Estimation       86         6.2       Data Reuse Analysis       89         6.2.1       Comparison with Other DRA Techniques       93         6.3       Memory Hierarchy Layer Assignment Estimation       95         6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       96         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       114         8.1.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform Configurati                                         | 6 | Initi | al Hierarchical Memory Size Estimation                       | 85       |

| 6.2       Data Reuse Analysis       89         6.2.1       Comparison with Other DRA Techniques       93         6.3       Memory Hierarchy Layer Assignment Estimation       95         6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       97         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       104         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform Configuration       117         8.2       Data Memory Platform Explo                                         | Ū |       | •                                                            |          |

| 6.2.1       Comparison with Other DRA Techniques       93         6.3       Memory Hierarchy Layer Assignment Estimation       95         6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       97         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Hierarchical Memory Footprint Estimation       104         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform Configuration       117         8.2       Data Memory Platform Exploration       117                                                                       |   |       | •                                                            |          |

| 6.3       Memory Hierarchy Layer Assignment Estimation       95         6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       97         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Hierarchical Memory Size Estimation       104         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation for A Given Memory Platform Configuration       114         8.1.1       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                            |   | 0.2   | •                                                            |          |

| 6.3.1       Greedy MHLA Estimation Algorithm       96         6.3.2       Improved MHLA Estimation Algorithm       97         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Hierarchical Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                                                                                               |   | 6.3   |                                                              |          |

| 6.3.2       Improved MHLA Estimation Algorithm       97         6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       114         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                                                                          |   | 0.0   |                                                              |          |

| 6.3.3       Algorithm Complexity       98         6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.1       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform Configuration       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                                                                                                                                                                                                                |   |       |                                                              |          |

| 6.4       Inter Array In-place Estimation       100         6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Hierarchical Memory Footprint Estimation       104         7.3       Incremental Intra-array Memory Footprint Estimation       106         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.1       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform Configuration       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                                                                                                                                                                                                                                             |   |       |                                                              |          |

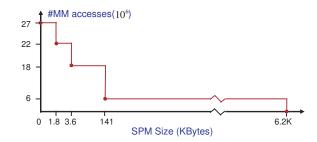

| 6.5       Pareto Curve Comparison       100         6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.1       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform Configuration       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 6.4   | • • •                                                        |          |

| 6.6       Summary       101         7       Incremental Hierarchical Memory Size Estimation       103         7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.1       Power Estimation for a Given Memory Platform Configuration       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |       |                                                              |          |

| 7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.1       Power Estimation Model       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform Configuration       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |       | L.                                                           |          |

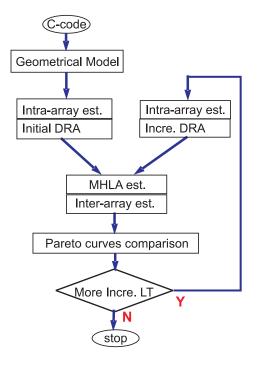

| 7.1       Incremental Hierarchical Memory Size Estimation       104         7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.1       Power Estimation Model       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform Configuration       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7 | Incr  | emental Hierarchical Memory Size Estimation                  | 103      |

| 7.2       Incremental Intra-array Memory Footprint Estimation       106         7.3       Incremental Data Reuse Analysis       107         7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.1       Power Estimation Model       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |       | ·                                                            | 104      |

| 7.3 Incremental Data Reuse Analysis       107         7.4 Summary       112         8 Low Power Data Memory Platform Exploration       113         8.1 Power Estimation For A Given Memory Platform Configuration       114         8.1.1 Power Estimation Model       114         8.1.2 Power Estimation for a Given Memory Platform Configuration       115         8.1.3 Power Estimation for a Multiple-layer Memory Platform       117         8.2 Data Memory Platform Exploration       117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 7.2   | •                                                            |          |

| 7.4       Summary       112         8       Low Power Data Memory Platform Exploration       113         8.1       Power Estimation For A Given Memory Platform Configuration       114         8.1.1       Power Estimation Model       114         8.1.2       Power Estimation for a Given Memory Platform Configuration       114         8.1.3       Power Estimation for a Multiple-layer Memory Platform       115         8.1.3       Power Estimation for a Multiple-layer Memory Platform       117         8.2       Data Memory Platform Exploration       117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 7.3   |                                                              |          |

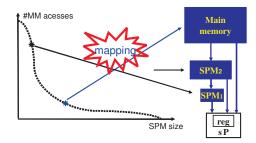

| <ul> <li>8.1 Power Estimation For A Given Memory Platform Configuration . 114</li> <li>8.1.1 Power Estimation Model</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 7.4   | •                                                            |          |

| <ul> <li>8.1.1 Power Estimation Model</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8 | Low   | Power Data Memory Platform Exploration                       | 113      |

| <ul> <li>8.1.2 Power Estimation for a Given Memory Platform Configuration</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 8.1   | Power Estimation For A Given Memory Platform Configuration . | 114      |

| uration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |       | 8.1.1 Power Estimation Model                                 | 114      |

| uration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |       | 8.1.2 Power Estimation for a Given Memory Platform Config-   |          |

| Configuration1178.2Data Memory Platform Exploration117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |       | • •                                                          | 115      |

| 8.2 Data Memory Platform Exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |       |                                                              | 117      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 8.2   | e                                                            |          |

| 8.3 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 8.3   | Summary                                                      |          |

xi

### CONTENTS

| 9   | Expe   | eriment  | S                                                | 119 |

|-----|--------|----------|--------------------------------------------------|-----|

|     | 9.1    | Prototy  | pe Tools                                         | 119 |

|     | 9.2    | Demor    | nstration on Cavity Detection Algorithm          | 120 |

|     |        | 9.2.1    | Intra-array Memory Footprint Estimation          | 126 |

|     |        | 9.2.2    | Inter-array Memory Footprint Estimation          | 126 |

|     |        | 9.2.3    | HMSE Estimation                                  | 127 |

|     | 9.3    | Demor    | nstration on QSDPCM Algorithm                    | 130 |

|     |        | 9.3.1    | Intra-array Memory Footprint Estimation          | 130 |

|     |        | 9.3.2    | Inter-array Memory Footprint Estimation          | 131 |

|     |        | 9.3.3    | HMSE Estimation                                  | 132 |

|     | 9.4    | Demor    | nstration on 2D Wavelet Transformation Algorithm | 134 |

|     |        | 9.4.1    | Intra-array Memory Footprint Estimation          | 135 |

|     |        |          | 9.4.1.1 Inter-array Memory Footprint Estimation  | 135 |

|     |        | 9.4.2    | HMSE Estimation                                  | 136 |

|     | 9.5    | Experi   | ments on Other Applications                      | 138 |

|     | 9.6    | Summa    | ary                                              | 139 |

| 10  | Con    | clusions | s and Future Work                                | 141 |

|     | 10.1   | Conclu   | isions                                           | 141 |

|     | 10.2   | Future   | Work                                             | 143 |

| Bil | oliogr | aphy     |                                                  | 160 |

xii

# **List of Figures**

| 1.1  | Power dissipation for DAB ASIC chip                                | 2  |

|------|--------------------------------------------------------------------|----|

| 1.2  | Energy dissipation for hardware realization of selected operations | 2  |

| 1.3  | Performance gap between microprocessors and external DRAM          |    |

|      | by Moore's law                                                     | 3  |

| 2.1  | DTSE methodology for data transfer and storage exploeration:       |    |

|      | global overview                                                    | 14 |

| 3.1  | Code example                                                       | 30 |

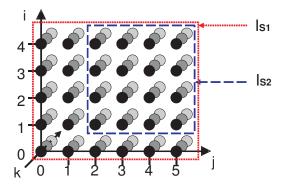

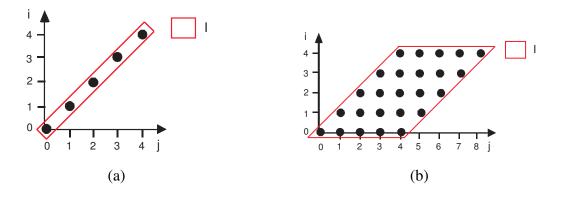

| 3.2  | Iteration domains (I) of two statements (S1 and S2)                | 32 |

| 3.3  | Example of common iteration space representation                   | 35 |

| 3.4  | Code example                                                       | 38 |

| 3.5  | Dependencies for the example code in Figure 3.4                    | 38 |

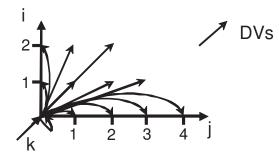

| 3.6  | Dependency vectors for the example code in Figure 3.4              | 39 |

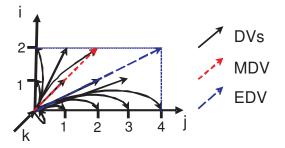

| 3.7  | The MDV and EDV for the example code in Figure 3.4                 | 39 |

| 3.8  | Code examples in (a) non-single assignment, (b) single assignment  | 40 |

| 3.9  | Approximation of iteration domain (a) before , (b) after           | 42 |

| 3.10 | Approximation of iteration domain (a) before , (b) after           | 42 |

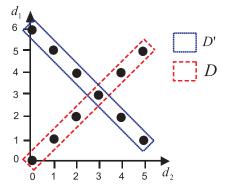

| 3.11 | Dependency vectors in bounding box geometrical model               | 44 |

| 3.12 | Loop transformation code example (a) original (b) in the common    |    |

|      | iteration space                                                    | 47 |

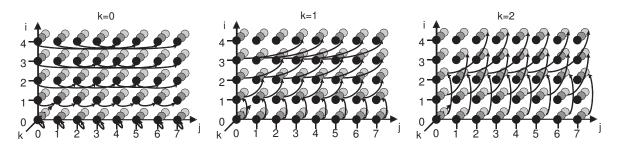

| 3.13 | Loop interchange example                                           | 48 |

| 3.14 | loop reversal example                                              | 49 |

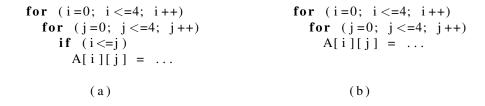

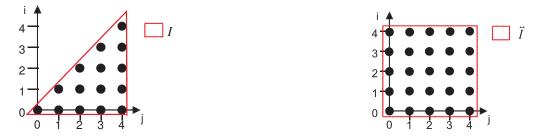

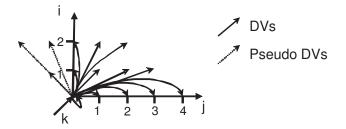

| 3.15 | Loop skewing example                                               | 50 |

| 3.16 | Loop fusion example (a) before (b) after                           | 52 |

|      | Loop reversal example                                              | 53 |

|      | Strip mining example (a) before (b) after                          | 54 |

| 3.19 | Loop tiling example (a) before (b) after                           | 55 |

|      |                                                                    |    |

### LIST OF FIGURES

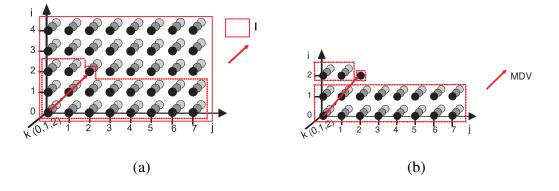

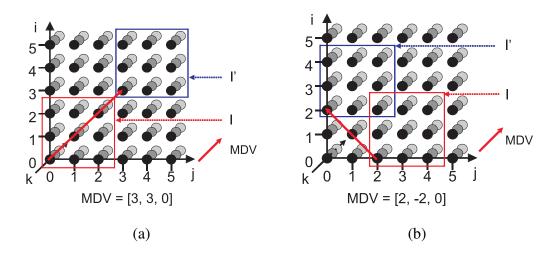

| 4.1        | (a) The maximal lifetime window constrained by MDV, (b) mem-<br>ory footprint estimation on the MDV | 60   |

|------------|-----------------------------------------------------------------------------------------------------|------|

| 4.2        | Other MDV relations between array write and read iteration domains                                  | 62   |

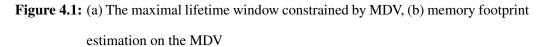

| 4.3        | Pseudo-code of memory footprint estimation algorithm for single                                     |      |

|            |                                                                                                     | 64   |

| 4.4        | Code examples with (a) diagonal iteration domain, (b) loop skewed                                   |      |

|            | iteration domain                                                                                    | 72   |

| 4.5        | (a) diagonal iteration domain, (b)loop skewed iteration domain                                      | 72   |

| 4.6        | Data domain for Memory footprint estimation exception code                                          | 73   |

| 4.7        | Code example                                                                                        | 74   |

|            | I                                                                                                   |      |

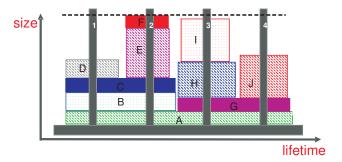

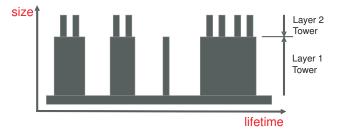

| 5.1        | Illustration of the one-layer Hanoi tower approach                                                  | 79   |

| 5.2        | Illustration of the multiple layer Hanoi tower approach                                             | 80   |

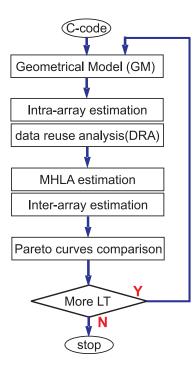

| 6.1        | initial LIMSE flow graph                                                                            | 87   |

|            | initial HMSE flow graph                                                                             | 0/   |

| 6.2        | Code examples: (a) original code, (b) after loop fusion, (c) after                                  | 88   |

| 62         | loop interchange                                                                                    |      |

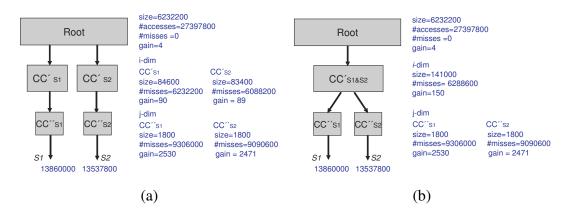

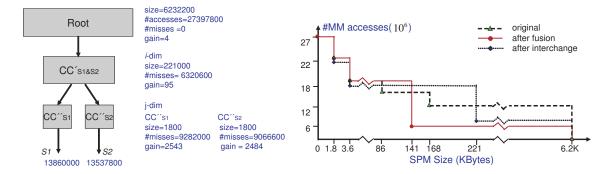

| 6.3        | (a) DRTree for the original code and (b) DRTree for the fused code                                  | 94   |

| 6.4        | the Pareto curve output for the fused code                                                          | 97   |

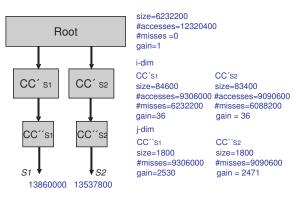

| 6.5        | DRTree output by the improved MHLA algorithm for the original                                       | 99   |

| 6.6        | code                                                                                                | 99   |

| 6.6        | (a) DRTree output for the code after loop interchange and (b)                                       | 101  |

|            | Pareto curves comparison                                                                            | 101  |

| 7.1        | HMSE flow graph                                                                                     | 105  |

| 7.2        | Loop interchange example: (a) before (b) after                                                      |      |

| 7.3        | Pseudo code of incremental DRA algorithm                                                            |      |

|            |                                                                                                     |      |

| 8.1        | Power estimation for any two layer memory platform                                                  |      |

| 8.2        | Power estimation for any multiple layer memory platform                                             | 118  |

| 9.1        | Cavity Detection Algorithm (orig)                                                                   | 122  |

| 9.1<br>9.2 | The part of code after $LT_1$                                                                       |      |

| 9.2<br>9.3 | The part of code after $LT_2$                                                                       |      |

| 9.3<br>9.4 | Cavity detection algorithm after loop transformation (LT-3)                                         |      |

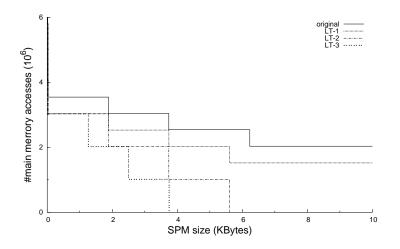

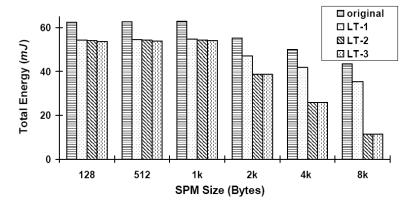

| 9.4<br>9.5 | HMSE estimate with Pareto curves output for Cavity Detection                                        | 123  |

| 9.5        | 1 · · · ·                                                                                           | 128  |

| 9.6        | Power estimation for two layer memory platforms for Cavity De-                                      | 120  |

| 7.0        | tection Algorithm                                                                                   | 130  |

|            |                                                                                                     | 1.50 |

xiv

### LIST OF FIGURES

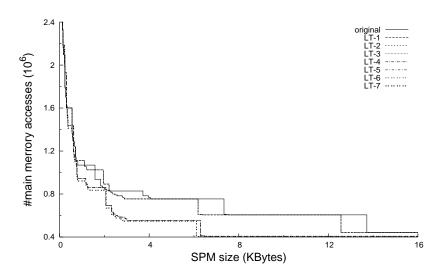

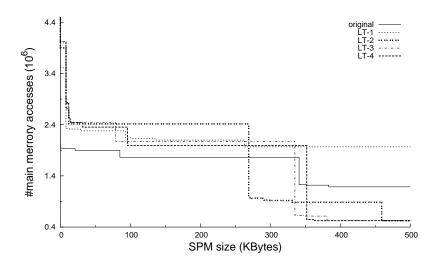

| 9.7  | HMSE output of Pareto curves for QSDPCM                   | 132 |

|------|-----------------------------------------------------------|-----|

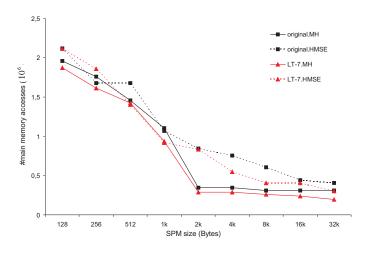

| 9.8  | HMSE and Atomium/MH comparison for QSDPCM                 | 134 |

| 9.9  | HMSE output of Pareto curves for 2D Wavelet Algorithm     | 137 |

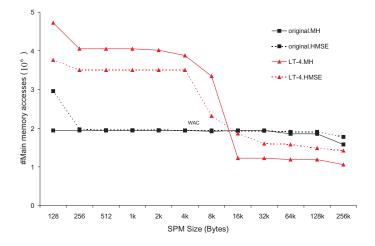

| 9.10 | HMSE and Atomium/MH comparison for 2D Wavelet Algorithm . | 138 |

# **List of Tables**

| 9.1  | Intra-array memory footprint estimation for Cavity Detection Al-  |     |

|------|-------------------------------------------------------------------|-----|

|      | gorithm                                                           | 126 |

| 9.2  | Inter-array memory footprint estimation comparison for Cavity     |     |

|      | Detection Algorithm                                               | 127 |

| 9.3  | Execution time comparison of HMSEs for Cavity Detection Al-       |     |

|      | gorithm                                                           | 129 |

| 9.4  | Intra-array memory footprint estimation for QSDPCM Algorithm      | 131 |

| 9.5  | Inter-array memory footprint estimation comparison for QSDPCM     |     |

|      | Algorithm                                                         | 131 |

| 9.6  | Execution time comparison for QSDPCM Algorithm                    | 133 |

| 9.7  | Intra-array memory footprint estimation for 2D Wavelet Algorithm  | 135 |

| 9.8  | Inter-array memory footprint estimation comparison for 2D Wavelet |     |

|      | Algorithm                                                         | 136 |

| 9.9  | Execution time comparison for 2D Wavelet Transform Algorithm .    | 137 |

| 9.10 | Estimation comparison for other applications                      | 139 |

|      |                                                                   |     |

# **List of Abbreviations**

| ALAP   | As Late As Possible                                  |

|--------|------------------------------------------------------|

| ASIC   | Application Specific Integrated Circuit              |

| CPU    | Central Processing Unit                              |

| DAB    | Digital Audio Broadcast                              |

| DMA    | Direct memory access                                 |

| DRAM   | Dynamic Random Access Memory                         |

| DSA    | Dynamic Single Assignment                            |

| DTSE   | Data Transfer and Storage Exploration                |

| DV     | Dependency Vector                                    |

| EDV    | Extreme Dependency Vector                            |

| GM     | Geometrical Model                                    |

| HMSE   | Hierarchical Memory Size Estimation                  |

| ILP    | Integer Linear Programming                           |

| LBL    | Linearly Bounded Lattices                            |

| LT     | Loop Transformation                                  |

| MDV    | Maximal Dependency Vector                            |

| MFE    | Memory Footprint Estimation                          |

| MHLA   | Memory Hierarchy Layer Assignment                    |

| MPEG   | Moving Picture Experts Group                         |

| QSDPCM | Quadtree Structured Difference Pulse Code Modulation |

| RAM    | Random Access Memory                                 |

| ROM    | Read Only Memory                                     |

| RTL    | Register Transfer Level                              |

| SoC    | System on Chip                                       |

| SPM    | Scratch-Pad Memory                                   |

| SRAM   | Static Random Access Memory                          |

| TLB    | Translation Lookaside Buffer                         |

|        |                                                      |

# Chapter 1

# Introduction

## **1.1 Background and Motivation**

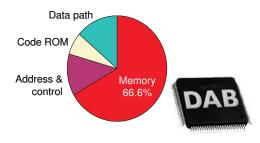

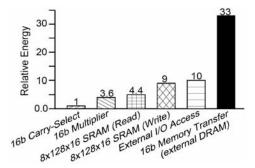

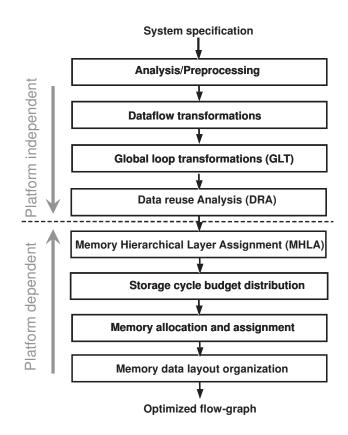

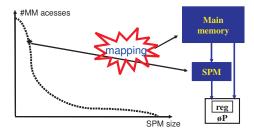

Recent multi-media systems such as video compression/decompression, (medical) image processing, advanced audio and speech coding, 3D gaming, typically require very large amounts of data to be transferred and stored (temporarily). For this class of data dominant applications, this memory related data transfer and storage largely determine the total system cost and performance parameters. This is especially a problem for portable embedded systems because the needed memories and bus transfers consume a lot of power. [160] has shown that between 50% to 80% of the power in embedded multi-media systems is consumed by data transfer and storage, as opposed to the computations which consume much less. This is the case for both parallel and single-processor systems. Figure 1.1 shows an example of digital audio broadcast (DAB) ASIC chip in which memory consumes over 66% of the total power [26]. Higher power consumption also means more costly packaging and cooling equipment, and lower reliability. Figure 1.2 shows the energy dissipation for external DRAM access compared to on-chip SRAM and also compared to selected execution units realized in hardware. If off-chip memories can be avoided or the access to them can be reduced by having most accesses on-chip in the hierarchical memory architecture, the average power consumption per overall access is dramatically reduced.

For these applications, the large amounts of data to be stored obviously require a large overall memory size (in the order of hundreds of Mbits to Gbits). Given the need for caching at least part of this huge data, this means that the area cost (both on-chip and off-chip, on the board) is usually for a large part domi-

Figure 1.1: Power dissipation for DAB ASIC chip

Figure 1.2: Energy dissipation for hardware realization of selected operations

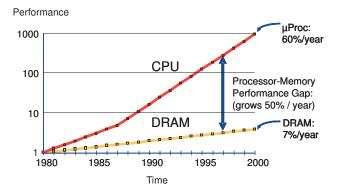

Figure 1.3: Performance gap between microprocessors and external DRAM by Moore's law

nated by the memories. For future systems-on-chips the memory is predicted to constitute 94% of the total chip size (in year 2016) [1]. Large memory size also means more power dissipation per access and longer access time. Consequently, the memory related data transfer and storage is also a determining factor for overall system performance. The exponential growth in processor execution speed according to Moore's law, as shown in as Figure 1.3, coupled with a much lower growth in the access time to main memories, have resulted in an ever growing processor-memory performance gap [110, 149]. This bottleneck can be alleviated by hardware controlled caching schemes, or by inserting faster smaller scratch-pad memories between the processor and the main memory to reduce/tolerate the memory latency.

It is commonly agreed that low power design requires optimizations at all levels of the design hierarchy, i.e., technology, device, circuit, logic, architecture, algorithm, and system level [20, 21, 119]. Larger freedom usually exists at the higher abstract levels so that larger gains can be achieved. Due to the dramatically increasing size and complexity of system-on-a-chip (SoC) designs, system-level design becomes crucial for rapidly performing design space exploration without resorting to detailed implementations. System level design can, with a global view, make proper high-level design decisions such as algorithm selection, hardware-software partition, and trade-off between various optimization techniques. It can also shorten the design time, thereby reducing the ever important time-to-market. Various memory related system level design and optimization techniques have recently been developed. A review of important work in this field is given in Chapter 2.

### **1.2 Problem Statement and Objective**

System designers traditionally begin the design by evaluating different architectural configurations based on their intuition and experience. The performance and power consumption improvement of the memory subsystem relies mainly on technological advances. A randomly chosen memory architecture is often far from optimal and can usually not be evaluated and optimized until the very late design stage. At the same time, the memory subsystem offers tremendous opportunities for design optimization. A well-matched memory architecture, which highly depends on the characteristics of the target application, can improve the system dramatically.

In multi-media embedded systems, the application is typically described using languages such as C and C++ at the system level. The code is then dominated by large multi-dimensional arrays and loop nests. During system level design, a number of optimization techniques are used that substantially influence data transfer and storage size related issues. One very important example is the global loop transformations step. It modifies the execution order of loops and statements without changing the application functionality. Loop transformations can change the execution order so that the data write (production) and the data read (consumption) are moved closer together in time. The result is that the global lifetime of array elements are reduced and the data locality and regularity of data accesses are improved. Hence, more data can be saved in smaller on-chip memories, from where it can be accessed repeatedly. This is vital to the overall system power consumption, performance and area. Traditionally reductions in data element's lifetime or improvement in data locality and regularity are used to steer selection of loop transformations. These are, however, very abstract cost functions that do not represent how the data will be mapped onto the memory platform. On the other hand, there usually exist a huge number of (combined) loop transformation possibilities for real applications with multiple loop nests (up to dozens). [38] has proven that even performing loop fusion is an NP-complete problem. The task is even more complex when various other loop transformation techniques are considered at the same time, e.g., loop interchange, loop reverse, loop skewing, loop shifting, etc. Different loop transformations may result in optimal utilization for different memory platform instances as will be demonstrated on experiments in this dissertation. Ad-hoc loop transformation decisions without estimating their impact on the actual hierarchy utilization usually lead to final sub-optimal solutions.

Thus, it is critical to perform an estimation of data mapping onto memory

#### 1.3. Application Domain and Targeted Architecture

platform during the early loop transformation exploration in order to find all interesting (including intermediate) loop transformation instances. The state-of-the-art loop transformation algorithms all result in a single final loop transformation solution. Their solution may be optimal for certain memory hierarchy instances, but typically not for all. As mentioned, the data memory platform is typically not defined at this early design stage. The estimation must hence be platform independent. A memory footprint estimation is also required to give an early feedback on the actual memory size requirement of all arrays as loop transformations change array's lifetime and hence size requirement.

At the same time it is not enough simply to estimate the actual size of a given array and of the given application, since the minimal size may still be too large to fit on-chip. In addition, if sufficient locality between read accesses is present, a local copy of part of the array to on-chip memory may already remove most of the off-chip accesses [157], making the actual size of that array less relevant. To select all the interesting loop transformation alternatives, it is therefore critical to identify the frequently accessed data and estimate their mapping on the hierarchical memory platform. Later, when the details of the memory platform is decided, the set of transformation solutions can help the designer or a steering tool to find the optimal version of code while trading off memory size and power (i.e., offchip accesses). Such an estimation tool can be of great use to a system designer or an automatic steering tool by providing accurate and fast feedback for a given sequence of transformation instances during the huge loop transformation search space exploration. It is also useful to provide the designers with an early memory architecture exploration while taking into account the data access characteristics of the target application during the system level code transformation exploration. This allows the designer to transform the target application for optimal utilization either of a given memory architecture or for a customized memory architecture instance. The goal of this dissertation work has been to develop techniques and tools for the early global loop transformation and memory architecture exploration. The focus has mainly been on the early global loop transformation design step. But it can also be used to provide feedback to other early system-level transformations such as global data-flow transformations [31].

### **1.3** Application Domain and Targeted Architecture