# **Using Commodity Coprocessors for Host Intrusion Detection**

Mark M. Seeger

Thesis submitted to Gjøvik University College for the degree of Doctor of Philosophy in Information Security

2012

# Using Commodity Coprocessors for Host Intrusion Detection

Faculty of Computer Science and Media Technology Gjøvik University College

Using Commodity Coprocessors for Host Intrusion Detection / Mark M. Seeger Doctoral Dissertations at Gjøvik University College 1-2012 ISBN: 978-82-91313-94-8 ISSN: 1893-1227 To my parents.

### **Declaration of Authorship**

I, Mark M. Seeger, hereby declare that this thesis and the work presented in it is entirely my own. Where I have consulted the work of others, this is always clearly stated.

Signed:

(Mark M. Seeger)

Date:

### Summary

The ever-rising importance of communication services and devices emphasizes the significance of intrusion detection. Besides general network attacks, private hosts in particular are within the focus of cyber criminals. Private data theft and the integration of individual hosts into large-scale botnets are two common purposes successfully subverted systems are used for.

In order to detect any attack, intrusion detection mechanisms need to probe the data in question. Therefore, the acquisition of sensor data is one of the fundamental steps in any intrusion detection system, as the execution of a detection algorithm – be it anomaly- or signature-based – relies on the integrity of the assessed data. In cases where the intrusion detection system (and the sensor data acquisition component, in particular) is installed on the very same host it is supposed to protect, attacks against its preventive and detective safeguards are rather simple and supported by potential vulnerabilities of the host's operating system.

Detection speed plays a vital role in keeping the damage caused by subversion attempts as small as possible. Dispatching the data acquisition and detection mechanisms from the host is desirable, as a higher degree of independence allows high-speed execution even in cases where the host has already been infected, or where its central processing units work to capacity.

The history of computer science, with cryptography being an excellent example, has taught us that the level of security can be increased by outsourcing certain operations to additional, special-purpose hardware. Here, a positive side effect is that the increase in security is often accompanied by an increased speed at which the corresponding operations can be executed.

The present thesis seizes upon the idea of outsourcing, but rather than employing additional special-purpose hardware, it proposes the execution of relevant operations on commodity hardware. While the application of coprocessors for network intrusion detection is common practice, and approaches using PCI add-in cards, as well as external cryptographic coprocessors exist, we propose the application of commodity coprocessors for host intrusion detection, i.e., modern graphics processing cards (GPU) found in current laptop and desktop computers.

Our focus was on validating the assumption that modern GPUs are, in general, applicable in the task of acquiring host sensor data for intrusion detection purposes. Thus, we propose their application as independent auditors, and present research results regarding their feasibility to function as such.

We detail abstract cost models and their practical validation, as well as a proof of concept implementation of an autonomous GPU kernel. This allows us to conclude that – leaving aside their programming and runtime frameworks – commodity, off-the-shelf coprocessors (i.e., modern GPUs) are able to perform host observation tasks in an unintrusive manner.

## Acknowledgments

I dedicate this thesis to my parents, Agnes and Günter Seeger. From many points of view, they are the ones who made this work possible. They never imposed their ideals on me, nevertheless giving me guidance whenever I needed it. They let me become the person I am today by giving me the freedom of a bird combined with tremendous support whenever required – for better and for worse. I will never be able to give back as much as I was given. Thank you!

Sascia, I want to take this opportunity to thank you for who you are and for being within the core of my heart. I cannot imagine my life without you anymore. You are my living proof, that for every puzzle piece, there is a matching counterpart.

Special appreciation goes to my first supervisor Stephen D. Wolthusen who clearly contributed the most important scientific guidance which enabled me to finally write this thesis. His style of supervision clearly shaped me as a researcher, and my thesis is manifesting evidence for this. He always impressed me with his technical knowledge and his overarching overview of relevant literature. Despite working to capacity, he agreed to supervise me and often pointed me in the right direction. Every time I sent him early versions of my writings, he was able to comment on the essence, to encourage me to take deeply technical specifications into considerations, as well as to assess adjacent approaches concerned with a related domain.

I also want to thank Christoph Busch, my second supervisor, for the time he took to comment on all of my publications and for the discussions we had. His commitment gave me the possibility to spend research periods abroad and to participate in several international conferences.

No doubt, without the support of Stephen and Christoph, this thesis would not have been possible. Nevertheless, it was Klaus Kasper who introduced me to Christoph in 2008 and made me aware of the newly established CASED. Thus, it is somehow by his merit that I had the chance to apply for the position of a doctoral researcher and that I eventually became part of this aspiring research cluster.

I would also like to thank Peter Herrmann, Thomas Kemmerich, and Katrin Franke for being part of the examination committee, and Patrick Bours for being the head of the committee.

For their excellent practical support, credit goes to my student assistants, Julian Knauer and Pierre Schnarz: thank you, guys.

Naming all people who have come along with me during my time as a Ph.D. student would clearly break the mold, and, therefore, I apologize to those who have not been named explicitly. In this context, I want to express my appreciation to the Gjøvik University College (GUC), Norway, the University of Applied Sciences Darmstadt (h\_da), Germany, and the Center for Advanced Security Research Darmstadt (CASED), Germany for their administrative, technical, and financial support throughout the past three years.

Mark M. Seeger August 22, 2012

## Contents

| Ι  | Inception                                                                                                                                                                    | 1                                       |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1  | Introduction1.1Motivation1.2Research Questions1.3Summary of Thesis Contributions1.4Conclusions and Future Work1.5Document StructureBibliography                              | 3<br>4<br>7<br>11<br>13<br>14           |

| 2  | Related Work2.1Modern Computer Architecture2.2Coprocessors and Direct Memory Access2.3Intrusion Detection using CoprocessorsBibliography                                     | 19<br>23                                |

| II | Publications                                                                                                                                                                 | 41                                      |

| 3  | Observation Mechanism and Cost Model3.1Introduction3.2Computational Model3.3Interference Model3.4Conclusion and Future WorkBibliography                                      | 44<br>47<br>50                          |

| 4  | Constraints on Autonomous Use of Standard GPU Components for Asyn-<br>chronous Observations4.1Introduction                                                                   | 54<br>55<br>57<br>58<br>60<br>62<br>62  |

| 5  | The Cost of Observation for Intrusion Detection: Performance Impact of<br>Concurrent Host Observation5.1Introduction5.2IEEE 13945.3Experimental Setup5.4Results5.5Conclusion | <b>67</b><br>67<br>68<br>69<br>72<br>76 |

|   | 5.6 Future Work                                                                                                                                                                                                                                                   | 78<br>78                   |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 6 | Using Control-Flow Techniques in a Security Context6.1Introduction6.2Related Work6.3Flow Analysis6.4Common Prototypes Using Flow Analyzing Techniques in a Security Context6.5Example of Dynamically Altering Control-Flow6.6Conclusion6.7Future WorkBibliography | 82<br>84<br>86<br>87<br>87 |

| 7 | Towards Concurrent Data Sampling using GPU Coprocessing7.1Introduction7.2Related Work7.3Details7.4Security Analysis7.5Autonomous Sampling using a Commodity Coprocessor7.6Conclusion and Future WorkBibliography                                                  | 94<br>96<br>98             |

| 8 | A Model for Partially Asynchronous Observation of Malicious Behavior8.1Introduction8.2Related Work8.3Observing Partially Ordered Attack Sets8.4Practical Application of Proposed Models8.5Conclusion and Future WorkBibliography                                  | 102<br>103<br>107<br>109   |

#### Nomenclature

**List of Publications**

# List of Figures

| 3.1                      | The concrete and abstract component model                                                                                                                                                                                 |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

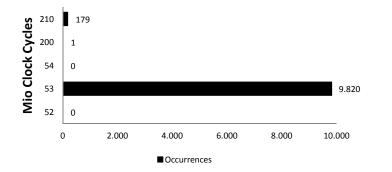

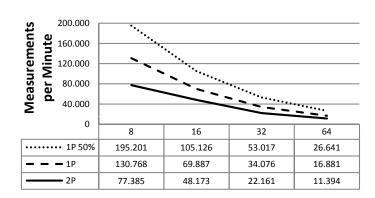

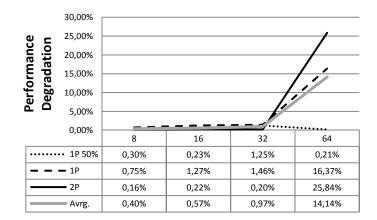

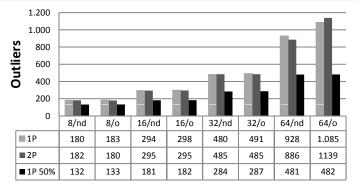

| 5.1<br>5.2<br>5.3<br>5.4 | Histogram of all results from the first test.74Measurement frequency for different data structure sizes.75Performance degradation according to the size of the observed data structure.75Increasing number of outliers.76 |

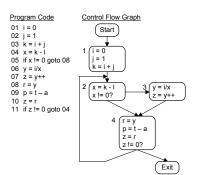

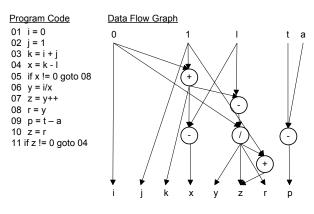

| 6.1<br>6.2<br>6.3        | Example of a control-flow graph.83Example of a data-flow graph.84The control-flow graph of the target program.86                                                                                                          |

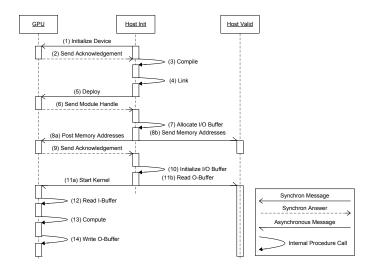

| 7.1                      | The sequence diagram of the proof of concept implementation of our asyn-<br>chronous and concurrent sampling mechanism                                                                                                    |

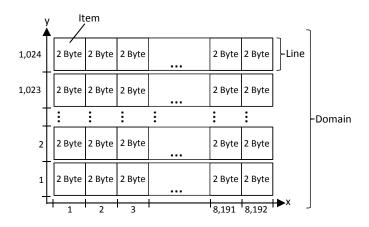

| 7.2                      | Logical memory architecture of our shared memory object                                                                                                                                                                   |

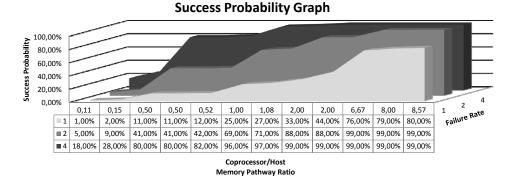

| 8.1                      | The results for an application example of the proposes model                                                                                                                                                              |

# List of Tables

| 3.1        | Overview of notations.                                                                         | 45 |

|------------|------------------------------------------------------------------------------------------------|----|

| 5.1        | All conditioned results obtained from observing one process with a stress ra-<br>tio of 1.0.   | 73 |

| 5.2        | Normalized conditioned results for observing one process with a stress ratio of 1.0.           | 74 |

| 5.3        | Comparison of performance degradations depending on the amount of data actually being written. | 77 |

| 6.1        | Characteristics of the presented flow analyzing tools.                                         | 85 |

| 8.1<br>8.2 | Comparison of assumptions incorporated into each model                                         |    |

# List of Listings

| 5.1 | Pseudo Code of the Workload Generator.                                                                  | 70 |

|-----|---------------------------------------------------------------------------------------------------------|----|

| 6.2 | Pseudo Code of the Target Program.Pseudo Code of the DLL.Pseudo Code the Program Executing the Exploit. | 86 |

| 7.1 | Extract form the GPU kernel written in AMD IL.                                                          | 97 |

Part I

Inception

#### Chapter 1

### Introduction

Es kommt nicht darauf an, mit dem Kopf durch die Wand zu rennen, sondern mit den Augen die Tür zu finden.

WERNER VON SIEMENS

#### 1.1 Motivation

Currently, modern commercial host intrusion detection systems (IDS) are installed on the host system itself. That is, they operate next to all other software, are executed by the host system's central processing units (CPU), occupy parts of the host system's hard disk drive (HDD) and system memory (i.e., RAM: random access memory), and consume CPU cycles. In spite of these characteristics, the most severe fact is that they rely on the security of the underlying host operating system (OS), which makes them highly assailable. By exploiting host OS vulnerabilities, a host IDS can be shut down and scan results can be tampered with. With ready-to-use exploits, included in software products such as the Metasploit Framework, a free penetration testing solution, even moderately talented adversaries are given the opportunity to execute targeted subversion attempts against individual host systems.

No matter what kind of intrusion detection system is used (i.e., signature-, specificationor anomaly-based), they all rely on the integrity of sensor data. Incomplete or falsified data make it difficult, if not impossible, to detect even simple attacks. Therefore, it is of paramount importance to ensure the integrity of sensor data, as well as the component that is in charge of acquiring this data. Here, the application of external hardware, i.e., coprocessors, is one possible and often-applied defense against traditional host system exploits. Due to the frequency at which an observation mechanism could be operated when running on an autarchic coprocessor, subversion attempts would be detectable while they are ongoing, giving the host observation system the chance to intervene before the attack is completed.

In general, a coprocessor is any processor assisting the CPUs. While in the early days such processors were mainly used for mathematical computations (e.g., ALU: arithmetic logic unit), the concept has advanced over time, and is ubiquitous nowadays in all types of computer architecture, ranging from mobile phones to mainframes. While most coprocessors are developed to perform very limited tasks much faster than the CPUs could, they are often also limited in terms of programmability, which prevents their use in other operations. Here, application-specific integrated circuits (ASIC), Field programmable gate arrays (FPGA) and modern graphics programming units (GPU) present common exceptions. These coprocessors offer a programming interface which allows the implementation of custom logic and algorithms. While ASICs and FPGAs are peripheral hardware, freely programmable GPUs are considered commodity hardware with respect to modern desktop and mobile computers.

Today, GPUs are high performance processors, distinguished by a massively parallel hardware architecture, and, due to the existence of abstract programming and runtime

frameworks, possess an applicability which reaches far beyond the graphics processing scope. To this extent, the two leading GPU vendors NVIDIA and AMD/ATI are dominating the market with CUDA and ATI Stream, respectively.

Besides graphics computations, which may still be their largest field of application, GPUs are commonly used today for non-graphics computations whenever processor-intense calculations are required. Common examples are financial engineering, weather forecasting, bioinformatics and with respect to information security cryptography and intrusion detection. For intrusion detection purposes, GPUs, and coprocessors in general, are generally only applied in the field of network intrusion detection. Here, network traffic is assessed by algorithms executed on the GPU in order to keep latency to a minimum. The field of host intrusion detection has not yet witnessed the broad-based application of coprocessors.

Having such a coprocessor perform host intrusion detection would eliminate several drawbacks of traditional systems, and would additionally create new opportunities in the ways we defend personal computers from attackers in the near future. The parallel architecture has more to offer than pure superiority of speed over the host's CPUs, which is nonetheless an advantage. Due to its design, the GPU can be seen as an autonomous and concurrent coprocessor, having autarchic physical memory and, of course, its own processing units. These design features can be used to build a host intrusion detection system decoupled from the host while still able to perform observations in real time. With no references to host APIs (application programming interface) or DLLs (dynamic link library), there would be no intuitive way to tamper with such an observation mechanism by, for instance, exploiting host OS vulnerabilities. Furthermore, if intrusion detection obligations no longer burden the CPUs, more computing power is at the disposal of the user.

#### **1.2 Research Questions**

With sensor data acquisition being one of the very fundamental techniques of any observation system, our research focuses on the application of modern GPUs for this purpose, in the field of host intrusion detection. Since GPUs are powerful coprocessors that combine the tamper resistance of external auxiliary hardware with the flexibility, programmability, and ubiquity of internal standard hardware, using them for security related tasks seems promising.

To this extent, our main research question can be formulated as follows:

What are the limitations of an asynchronously and concurrently operating commodity coprocessor when applied for efficient observation of a host's system state, and how can these limitations be overcome?

The goal of this Ph.D. thesis is to provide a theoretical, as well as practical validation of the assumption that commodity coprocessors (i.e., the GPU) can be used for host intrusion detection purposes.

The GPU distinguishes itself from onboard coprocessors in terms of applicability and computational power, and from external auxiliary processors such as FPGAs in terms of host connectivity and the degree of its availability with respect to desktop computers and laptops. These characteristics theoretically make it an ideal off-host host observation processor. As its primary application lies in graphics computations, there is currently no intuitive way to create a GPU-host connection that authorizes an unrestricted data access. Therefore, observation of a host system in a thorough and efficient way is not possible using the graphics processor *as is*.

Even if a host observation mechanism was operated in total self-reliance, without any host dependent software modules, resource contention on the host-side would take place, due to forced synchronizations between the host's system memory and its caches. Modeling the degree of performance degradation on the host-side, followed by a practical validation, was subject of our research.

Our ultimate goal was to validate our assumption that modern GPUs are in fact suitable for performing host observation tasks. While we also assumed that off-the-shelf programming and runtime frameworks will prevent total independence from the host, we investigated the degree to which unmodified GPUs allow autonomous, as well as concurrent execution, and we compared existing approaches and their properties with ours.

Novel techniques operating on modern hardware often allow faster and more precise detection of known and possibly unknown attacks. This does by no means allow the inference that existing and well-studied threats are automatically rendered harmless. We were, therefore, also interested in the nature of attacks that could not be detected even if the observation mechanism was to run on a high performance coprocessor.

With fast and reliable data acquisition and observation mechanisms at our disposal, we also focused on how sampling strategies in combination with the observation of crucial measuring points can lead to faster detection speed, as well as possible further advantages over computer criminals trying to subvert host computers.

The above briefly motivated research scope is reflected by the following sub research questions (RQ).

- **RQ1:** What performance impact results from initiating observations of a host system's shared memory by a commodity co-processor?

- **1.1:** How can we model the loss of performance?

- **1.2:** How can we practically measure the loss of performance?

- **RQ2:** What architectural features of modern GPUs counter their usability as independent auditors?

- **RQ3:** What is the nature of attacks for which the general advantages of GPUs render less powerful?

- **RQ4:** Presuming a high performance, asynchronously- and concurrently-operating, host- observing commodity coprocessor: How can sampling strategies facilitate real-time detection?

We will now present the answers to the above-stated research questions and point to the publications in which each of them is regarded in detail, before summarizing each contribution separately in Section 1.3.

## **1.2.1 RQ1:** What performance impact results from initiating observations of a host system's shared memory by a commodity co-processor?

The detailed answers to this question can be found in Seeger and Wolthusen [10] and Seeger et al. [13].

In order to provide a qualitative answer to this question, we inspected the architectural details of modern computer systems. That is, we focused on features of non-uniform memory architectures (NUMA) in order to describe a model capable of expressing the performance degradation of a certain process when it is subject to frequent observation. We discovered that, in particular, techniques that act as performance boosters under *normal* conditions are the ones that cause performance penalties in the case of (coprocessor) driven observation. To be exact, snooping protocols, write-back and working-set strategies are implemented for the general case of data consumption by the host's CPU. Data accesses according to the busy-wait approach operated by a processor other than the CPU cause these protocols and strategies to act as performance bottlenecks. Furthermore, it is the composition of the data under observation that yields information about the degree of performance degradation. While observing read-only data causes no synthetic write-backs, reading writable data actually being written confuses working-sets and causes forced synchronizations [10].

The quantitative validation of the proposed model is given in Seeger et al. [13]. We showed that the performance degradation is quantifiable but depends on many parameters. Due to architectural features of the system under observation (e.g., number of CPUs, enabled power saving features, cache size, write-back strategy, etc.), and the fact that there is no such thing as a general data access pattern for real-life applications, the extent of degradation may vary. In an experimental setup, we experienced a performance loss of more than 25% when we observed two customized processes in parallel, each of them working on a 64 byte data structure.

The two presented models and their validation reveal that relieving the host's CPUs from host intrusion detection duties does not imply that the performance loss is fully compensated. In fact, due to main memory accesses from off-host coprocessors, combined with the existence of internal cache and snooping protocols, forced synchronizations take place inside the host's memory hierarchy, causing performance degradations.

## **1.2.2** RQ2: What architectural features of modern GPUs counter their usability as independent auditors?

The detailed answers to this question can be found in Riedmüller et al. [8] and Seeger and Wolthusen [12].

The development of an off-host host intrusion detection mechanism operated by the GPU is possible, but – due to architectural constraints – does not offer the required level of security. By using an unmodified GPU along with its programming and runtime framework, only predefined parts of the host's physical memory can be accessed and the detection mechanism is highly dependent on host-side software components. We investigated the architecture of a modern GPU and compared its features to a set of properties (cf. [4, 7]) that must be fulfilled in order to operate an observation mechanism as an independent auditor. We discovered that only three of the ten criteria are met: Inaccessibility, physical secureness, and the provision of sufficient processing power. On the other hand, properties such as the verifiability of the software operating the GPU, the lack of non-volatile memory, or the fact that unrestricted access to the host's system memory is not provided, counter a GPU's off-the-shelf usability as an independent auditor [8]. Next to their parallel architecture, it is the much smaller instruction set that causes the immense performance boost compared to CPUs. On the other hand, this limits their applicability in terms of computational sophistication, and hinders them in executing, for instance, code compiled for x86 architecture.

With respect to these results, restriction in accessing the target's memory is superior, as full data access forms the base of any detection system. To this extent, we have validated the assumption that access restrictions can be bypassed as the DMA (direct memory access) connection between GPU and host generally allows the access of any addressable data [12]. We developed a GPU kernel that operates without host-side runtime references. Given a proper configuration, as well as manual initialization of the device and the kernel as such, we were able to execute simple operations in total independence of the host. In this case, all control lies within the GPU itself. Moreover, due to a lack of logical host connectivity, the observation mechanism becomes, in principle, *invisible* to an attacker, and if all software parts are solely stored on the GPU itself, it is immune to host OS vulnerabilities and can function properly even when the host system has already been subverted.

## **1.2.3** RQ3: What is the nature of attacks for which the general advantages of GPUs render less powerful?

The detailed answers to this question can be found in Seeger [9].

Using an off-host coprocessor to detect computer attacks is a very promising technique. Once the technical constraints that burden current GPUs and their frameworks are overcome, GPUs have the power to operate a host intrusion detection mechanism distinguished by strong tamper resistance, high performance, and low overhead. Nevertheless, even offhost host intrusion detection systems will not be immune to certain types of known threats. This becomes clear when taking our proof of concept implementation of a dynamically altering control-flow approach into consideration. By analyzing program code and alienating a Linux system call mostly used for breakpoint debugging, we were able to overwrite specific variables stored on the heap. As these variables were marked for runtime alternations, it is hard to tell whether a change in value is benign or not. Thus, detecting such attacks is less of a technical problem than it is an architectural one. If the system design allows the alternation of certain variables during runtime, no purely technical approach will be able to tell legal alternations apart from illegal ones. This is, of course, also true for coprocessor driven solutions.

#### 1.2.4 RQ4: Presuming a high performance, asynchronously- and concurrently-operating, host- observing commodity coprocessor: How can sampling strategies facilitate real-time detection?

The detailed answers to this question can be found in Seeger and Wolthusen [11].

Modern cyber attacks often consist of several phases, such as the planning and reconnaissance phase, which take place before the actual attack. From a technical point of view, each attack itself is confronted with inevitable dependencies, where a certain step can only be accomplished once its prerequisites have been fulfilled. Presuming the targeted observation of critical data structures, we presented a causality model built upon the potentially caused relation proposed by Tarafda and Garg [14]. This model is based on probabilistic assumptions regarding the causal dependency of attack sets, and can be used to tune observation strategies to be more target-oriented. The overall observation frequency can be adjusted (i.e., lowered) as we take into account that certain data elements can only be attacked once certain activities have been observed. By only reducing the detection probability by 1% in our experiment, the burden of observing all data elements with the same frequency could be absorbed. Furthermore, the proposed model allows the triggering of counter measurements even before the attack succeeds.

#### **1.3 Summary of Thesis Contributions**

Each publication and its contributions is summarized in this section. All publications are presented in the order they were published, starting with the earliest.

As already reflected by research question RQ1, the possible performance degradation in the host under observation was one of our core focal points. In our models, presented in [10] (cf. Chapter 3), we regard the host's physical memory as the connection between an off-host coprocessor and the host itself. Therefore, any coprocessor-based host observation must inevitably access data stored within this memory entity. On the host itself, the RAM acts as a link between caches and hard disk drives. Data currently consumed (or likely to be consumed in the near future) by the CPUs are stored here and replicated throughout the different caching hierarchies. Due to performance considerations, data altered in the highest levels of these hierarchies are not instantly written back to the lower levels. Besides different protocols that take care of data consistency, write-backs are forced whenever outdated data in the RAM is accessed by a different processor. That is, in order to serve any accessing process with the latest data, altered data from the first level cache is written back to the RAM, causing a wait situation for that process.

The contribution of [10] is the proposal of two cost models. The first cost model is built upon a simplified model presented by Hennessy and Patterson [3]. It allows the expression of the synchronization cost, not only for one caching hierarchy, as presented in [3], but for multiple such hierarchies.

To this extent, we differentiate between demand-related and coherence-related misses, which represent the penalty times for the demand for data that needs to be retrieved from a lower (demand-related) or adjacent (coherence-related) memory level. The second cost model focuses on the composition of sets of most recently referenced pages<sup>1</sup>, referred to as working sets [1], and the interference that can be caused when these sets are indirectly accessed by a coprocessor. In theory, if all resources a certain process needs were to fit into one working set, and if this set was to be consumed by one process only, demand-, as well as coherence-related misses would be eliminated. As this is very unrealistic for real-world applications, both types of misses occur continuously. Any sort of artificial interaction with the working set (e.g., caused by forced synchronizations due to coprocessor-based host observation) has the potential to increase the interference frequency. In order to describe the possible severity of this interference, we introduced the interference ratio I, which takes the composition of the working set into account in terms of read-only and writable parts, as well as the percentage of processing time actually used to write to the writable pages. This model proposes that observing read-only data and writable data that is, in fact, not being written causes much less performance degradation on the host-side than observing writable data being written does.

In order to practically validate our models as they are proposed in [10], we first assessed modern GPUs with respect to their feasibility to act as so-called *independent auditors* in [8] (cf. Chapter 4). This assessment was necessary in order to answer research question RQ2. The reason for this is that today's GPUs are powerful commodity hardware and are widely available in computer systems of all sizes. Due to their system architecture, they can be regarded as the most powerful and most widely spread coprocessors for personal computers. Ever since the appearance of vendor-dependent programming and runtime environments (i.e., NVIDIA CUDA and AMD/ATI Stream), GPUs can be easily applied to tasks beyond the graphics computations' scope. Being both powerful and ubiquitous makes these coprocessors profitable operators of off-host host observation systems.

The contribution of [8] is the assessment of the combination of modern off-the-shelf GPUs with their corresponding frameworks with regard to their ability to operate a sustainable off-host host observation system. The assessment, according to properties of existing coprocessor solutions using extraordinary hardware such as PCI (peripheral component interconnect) add-on cards [4, 7], revealed severe shortcomings that cannot be easily circumvented. Out of the ten proposed properties, only three are fulfilled by GPUs. These are inaccessibility, meaning that the host must not have access to the internals of the GPU, physical secureness, and the provision of sufficient processing power. The properties not fulfilled by GPUs are unrestricted memory access, provision of secure transactions, continuity, transparency, verifiability, provision of non-volatile memory, and the ability to provide reports in a secure manner. In addition to the assessment according to the provided properties, we revealed the following drawbacks: If GPUs and their frameworks are used as is, they rely on host-side APIs, DLLs, and software components. Terminating the references to these components terminates the kernels executed by the GPU. Additionally, GPU kernels can only be started through software components running in the user space of the host system, which makes them easily attackable. Furthermore, a maximum GPU kernel runtime is traditionally set. While this seems useful in preventing system hangs, it implies a severe weakness with respect to intrusion detection purposes.

<sup>&</sup>lt;sup>1</sup>The term *pages* can be replaced by any other unit of data.

In order to use a GPU as an independent, asynchronously, and concurrently working auditor, at least the following architectural modifications must be made: It must be possible for the GPU to have unrestricted access to the host's physical memory; the observation mechanism must be started on system boot (i.e., before the host OS is started); there must be no logical connection to host-side software components such as APIs, DLLs, or any other kind of host-side software, and at least a small amount of non-volatile on-device memory must be provided.

Even though the results of our GPU assessment, presented in [8], prevent off-the-shelf applicability of modern graphics cards in functioning as autonomous auditors, one of our goals was to precisely quantify the performance degradation on the host-side when off-host observation takes place. What has been theoretically validated in previous work [10] needed practical confirmation. This confirmation is the subject of [13] (cf. Chapter 5).

Therefore, the contribution of [13] is the quantification of the maximum performance degradation caused by observing a self-implemented, and, therefore, rule-governed process, using an off-host coprocessor. By adjusting the parameters of the process to be observed, we were also able to practically validate the cost model proposed in earlier work [10]. Due to the constraints revealed by Riedmüller et al. [8], the experimental setup was not comprised of a GPU and a computer, but by two computers, one being the target and one being the observer. Having a standalone computer act as a coprocessor of another computer may not seem feasible in many real-world scenarios, including host intrusion detection. Despite this, it serves the purpose of fulfilling the properties of a self-sufficient auditor (cf. [8]). The two computers were connected using FireWire technology, which, due to a design feature of the open host controller interface (OHCI) implementation, allows full access to the target's physical memory (cf. [6, Chapter 12]). This feature provided the possibility of observing a prepared process on the target, which, in turn, recorded the CPU cycles consumed for its duties. By having the target execute predefined tasks with and without observation, we were able to quantify the performance degradation due to observation.

With respect to the cost model proposed in earlier work (cf. [10]), we adjusted the observed process in a way that only a portion of its writable data was actually being written. While the general value of the cost model was confirmed by the gathered results, the information gleaned from the experiments has led to a slightly revised version of the model (cf. Equation 5.1 of Chapter 5). Despite the minor adjustments made, the message remained the same: Read-only data cannot be written, therefore, does not need to be synchronized, and thus will not cause resource contention due to forced synchronizations.

Across all experiments, a maximum performance degradation of more than 25% was measured for the setup in which we observed two of our rule-governed processes, each of them working on a 64 byte data structure. In our test scenario, this must be interpreted as the worst case, as 100% of all 128 bytes were writable and, in fact, being written. With respect to the extent of the performance degradation caused by the observation mechanism, we also must take the fact that the connection between observer and target (400 Mbit/s) was rather slow compared to the speed of the GPU-host connection (up to 16 GB/s) into account. Therefore, the performance degradation caused by applying a GPU would be much higher if following the busy-wait approach.

In addition to the performance details regarding our coprocessor-based approach for host observation, the identification of the nature of threats that, despite the promising properties of an off-host coprocessor, cannot dominate, has also been examined. The corresponding results of the analysis are presented in [9] (cf. Chapter 6). To achieve this goal, we focused on flow-analyzing techniques that are commonly used in the field of information security in order to uncover subversion attempts based on the alteration of program flow. Nowadays, buffer-overflow attacks are the most widely-spread examples of exploiting the deviation of control-flow. Here, software vulnerabilities are used in order to inject and execute defective code. Most – if not all – approaches to guarding a program's control-flow rely on a static analysis, which is, as among others demonstrated by Moser et al. [5], no longer a sufficient technique for identifying malware.

The contribution of this paper is the investigation and comparison of three common prototypes in the field of control-flow analysis, and the presentation of a dynamic controlflow attack, which neither commercial anti-virus suites nor the assessed tools could counter or detect. Two of the three prototypes we assessed rely on the output quality of  $3^{rd}$  party tools, which they build upon, and all three tools operate statically, and thus have one shortcoming in common: They are not designed to instantly react to changes in the executional flow caused by dynamically-loaded code. To this extent, we have developed a C++ program which is capable of dynamically altering the control-flow of arbitrary executables by using a late binding technique for loading dynamic link libraries (DLL). Because this approach does not exploit any soft- or hardware vulnerability, it stays undetected. Detecting such unwanted changes in control-flow confronts the counter measurements with the problem of distinguishing legal alternations of the values of variables stored on the heap from illegal ones. Or, to cite Forrest et al. [2], "to distinguish self from other". This is a very general problem, and the inability of identifying such attacks is indeed a problem not unique to current state-of-the art commercial intrusion detection suits. It was no surprise that the proposed observation and sensor data acquisition approach was unable to detect any attack of this kind, as the subject of the present thesis is not the proposal of a novel general intrusion detection system. Instead, based on and motivated by the results presented in [8], we succeeded in validating that modern GPUs can be used to autonomously and concurrently perform host observation in cases where host-side programming and runtime frameworks are not used.

Clearly, the use of an off-host coprocessor to perform host intrusion detection can have various motivations. One major argument stems from the fact that even moderately sophisticated attacks will target audit data collection and security controls (i.e., preventive and detective safeguards). Achieving this is relatively easy when the corresponding mechanisms operate in a highly heterogeneous software environment, as complex software tends to not be fully flawless, giving adversaries the chance to take advantage of said programming shortcomings. Security holes in prominent software are constantly patched while new vulnerabilities are discovered at the same time. Therefore, it is necessary to investigate modern ways of performing host intrusion detection. This includes the application of modern techniques such as machine learning, but also requires the improvement of traditional methods (i.e., signature matching) for which an equivalent substitute has yet to be found.

To this extent, the contribution of [12] is a presentation of a proof of concept implementation of an autonomous GPU kernel able to perform concurrent host observation tasks. As revealed by Riedmüller et al. [8], modern GPUs cannot intuitively be used as autonomous auditors, mostly due to the constraints of the corresponding runtime frameworks. By leaving the standard GPU programming model aside, we developed a mechanism through which the execution of code on a GPU is allowed without the host being actively involved. That is, in a proof of concept implementation of an autonomously running GPU kernel, we validated our assumption that a GPU can execute code even after the initializing process is terminated. This was achieved with proper hardware configuration and a manual initialization of the device as such, as well as the context in which the kernel runs. Once the kernel has been started, we forced the starting process to exit and observed the memory region on which the kernel operated from a second application. While the kernel itself performed rather simple read/write operations in this proof of concept, enriching it to the extent to which it can actually perform security related tasks is simply a matter of good programming skills.

In addition to detailing the implementation as such, we discuss its security aspects and present the results of a brief performance benchmark. The untuned version of our sensor data acquisition component was able to operate with a maximum transfer rate of about 1

GB/s.

This result once again shows that one advantage coprocessors hold over the CPU is their dominance in terms of speed, which also incorporates a severe drawback if applied in conjunction with an unfavorable sampling strategy. That is, in [13], we quantified the performance degradation in an experimental setup and reported a performance reduction of more than 25% in one case. While we used a rather slow coprocessor/host connection (i.e., FireWire) for this puspose, it is easy to imagine how severe the performance degradation can become when using a high performance coprocessor such as the GPU. Therefore, achieving a high observing frequency is straightforward, while the busy-wait approach (i.e., maximum frequency) is undesirable.

With respect to our last research question (i.e., RQ4), the contribution of [11] is the proposal of essentially one model, which can be used to take attack characteristics into consideration in order to optimize the observation strategy of a coprocessor-driven host intrusion detection system.

The operation of detection algorithms on a snapshot of data is exposed to the risk that malicious activities are ongoing while the acquired data is assessed. Therefore, limiting the observation mechanism to a set of comprehensive data elements, while at the same time recognizing the possibility of causalities between said elements, seems promising in achieving the twofold objective of providing a reasonable level of security and causing as little performance degradation as possible.

The proposed model does not only take causal dependencies between so-called attack sets into account, but also incorporates the likelihood of observations being suppressed by other operations of higher priority, as well as the possibility that an observed alternation may have a benign cause. It is worth mentioning that the latter feature may be applied in the context of dynamic control-flow detection as well, as discussed in [9].

By applying partly-altered versions of well-known models in order to incorporate our assumptions, we experience a negligible reduction of 1%, in terms of detection probability. In contrast to existing approaches, our model demonstrates a significant increase in efficiency, as neither bulk data snapshots have to be taken nor are we required to observe all data elements with the same (possibly high) frequency. Additionally to that, the model reveals the probabilistic chance to be one step ahead of the attacker. That is, given the assumed causal dependencies, a proactive action, for instance, locking the concerned data element, can be undertaken.

With respect to the ability to perform real-time observation, the practical application of the causality model showed that the twofold objective of performing unsuppressed observations while having a minimum failure rate (cf. Section 8.4 of Chapter 8) can be achieved by taking advantage of the coprocessor's computational dominance. As modern GPUs continue to maintain performance superiority, these results underpin the initial proposal for the use of commodity coprocessors in host intrusion detection made in 2010 (cf. [10]).

#### 1.4 Conclusions and Future Work

Current intrusion detection systems are installed on the very same system they are supposed to protect. They consume valuable system memory and CPU cycles, and are subject to rather simple attacks, as they rely on the security of the underlying host operating system. Consequently, an intruder can easily turn them down or may tamper with the sensor data acquisition module as such. While the former case can be detected and signaled to the end user, the latter may stay undiscovered, as the intrusion detection component cannot find any threat if the data given to it by the host sensors does not show any inconsistencies.

Ideally, a host intrusion detection system would be an autonomous, concurrent, and self-sufficient soft- and hardware component with full access to the host system's memory. As will be presented in depth in Chapter 2, Related Work, various approaches have been proposed to achieve this ambitious goal.

The present work proposes the application of modern graphics programming units to this extent, as GPUs combine the autonomy of external auxiliary hardware with the availability of commodity hardware. Due to their small instruction set and parallel architecture, GPUs are able to perform dedicated tasks at a much higher speed than CPUs. Therefore, our first scientific contribution was a proposal of two cost models in 2010 [10]. With the assistance of these models, the performance degradation caused by applying coprocessors in host intrusion detection can be determined. Under the assumption that, not only the size of the data to be observed, but its constitution in terms of read-only, writable and writable pages actually being written matters, the general loss of performance of processes under observation can be identified. The practical validation of this model, as well as the quantification of said performance loss was the contribution of [13]. Here, we configured a second desktop computer to act as a coprocessor of another one and established an interconnection between the two, taking advantage of a design feature of the FireWire technology. We gained accurate performance benchmarks from an observed process which reported the CPU cycles consumed in both cases; with and without being under observation.

In [8], we assessed the architecture, i.e., programming, and runtime frameworks of modern GPUs, and compared the corresponding features against given properties of autonomous host auditors. The assessment revealed that the architecture of modern GPUs is generally suitable for building observers that suffice the required properties of self-sufficient auditors. It is, therefore, the current software frameworks of these commodity coprocessors that are limiting their application for secure and fully asynchronous host observations.

By waiving the aforementioned frameworks, we were able to manually configure a GPU kernel and have it run on a GPU, even after the initializing process has already been terminated. This provided validation for the results presented in [8] and was the contribution of Seeger and Wolthusen [12].

Coprocessor-based host intrusion detection may be an answer to many of today's questions concerning the security of a host intrusion detection system, but, indeed, is not the answer to every threat. To this extent, we have developed a proof of concept application that is capable of dynamically altering a program's control-flow by taking advantage of the late binding technique. As this technique overwrites references stored on the heap, detecting such alterations is straightforward, while the automatic distinction between legal and illegal write accesses remains problematic. These results, together with an evaluation of three common prototypes focusing on control-flow integrity, are the contributions of Seeger [9] and present one example of the nature of attacks for which the GPUs intrinsic characteristics do not dominate existing host-bound approaches.

Our latest contribution can be found in Seeger and Wolthusen [11]. Here, we propose a causality model which allows for the reduction of observation frequency through the consideration of causal dependencies between critical host-side data elements and attack sets. Besides allowing a targeted observation, the probabilistic results gained from the model also give an observation mechanism the chance to be one step ahead of the attacker. That is, under the assumption that a first step always precedes a second one, we can eventually prevent the second step from being successful once we have seen the first.

One obvious question that has not been addressed so far concerns the acquired sensor data. We have presented that gathering such data from the host using a GPU is possible at the expense of performance, in cases where the sampling rate is too high. What has not been addressed so far is the question of what to do with this data. Depending on how complete the data samples are, and keeping the tremendous computing power of modern GPUs in mind, it would be possible to calculate a graph of all possible states between sampling point  $\alpha$  and  $\beta$ . While this requires knowledge about valid system conditions, it also appears to be a promising approach to revealing plausible and consistent, but nevertheless counterfeited, states.

In general, it would be interesting to analyze existing intrusion detection algorithms

to find out how well they can operate on our sensor data. This should include signaturebased, anomaly-based, and specification-based algorithms, likewise. To elaborate the degree to which an algorithm (or a class of algorithms) can deal with missing data points, could be a starting point. The ability to operate on incomplete data is only one mandatory feature, possibly qualified algorithms have to suffice. Equally important is their applicability in being executable in parallel. While data parallelism (i.e., SIMD) allows for the execution of the same algorithm multiple times in parallel, operating on different data, parallelizing the algorithms as such (i.e., MIMD), could provide further advantages with respect to the execution runtime. But, special attention has to be paid to the resulting communication complexity. Due to the memory architecture of modern GPUs, i.e., the existence of several memory entities of different sizes, having different access latencies, the risk of resource contention because of synchronizations between algorithms instances is present and needs to be avoided.

This is especially important when aiming at the goal of real-time detection. While modern GPUs are equipped with fast onboard memory, high-speed links to the host system, and massive parallel processors, the identification of real-time behavior of implemented algorithms in specific and the full data acquisition and detection system as such is of interest. In other words, we need to find the optimal trade-off between the level of security (i.e., the observation frequency) and the loss of performance (i.e. forced synchronizations), while at the same time guaranteeing a maximum time-to-detection.

Besides the detection of anomalies and intrusion attempts, the ability of self-protection (and possibly self-healing) is a promising field of research. It must be evaluated what kind of attacks a coprocessor (i.e., the GPU in our case) is vulnerable to. Due to the currently very limited interface between the host system and the device, we expect the number of attacks to be rather small.

Nevertheless, a first step towards self-protection could be the realization of a mutual health check. That is, each of the employed GPU processors (or even GPU threads) randomly checks the status of other processors/threads. If a coprocessor or thread is found to be infiltrated or subverted the tasks assigned to this component must be taken over by the remaining processors/threads. In this case, the infested device must be reseted. To prevent further incidents of the same kind (i.e., to avoid that the attacker uses the same attack vector again), we need a possibility to cure the affected entity from its vulnerability. A first approach towards this ambitious goal would be a thorough and automatic analysis of the attack, followed by a software reconfiguration.

At the very least, a reporting functionality that gives feedback about what led towards the attack should be realized. After all, self-protection, as well as self-healing capabilities must be resource efficient and should be operated as decentralized as possible in order to avoid a single point of failure.

#### 1.5 Document Structure

The present thesis is structured as follows: The related work is presented in Chapter 2. It is divided into three sections and contains related work in the field of modern computer architecture in Section 2.1, coprocessors in general and direct memory access in Section 2.2, and host, as well as network intrusion detection using coprocessors in Section 2.3.

Part II presents the six publications containing the contributions of the present thesis in full length. The first paper, proposing a cost model for tightly coupled asymmetric concurrency, is the subject of Section 3. In Section 4, we present the results of assessing modern GPUs in terms of their ability to be intuitively used as autonomous host auditors, followed by quantified performance degradation figures for various experimental setups, detailed in Section 5. The use of control-flow techniques in a security context, as well as the common weakness of three popular prototypes, is the subject of the paper presented in Section 6. In Section 7, we present the validation of our assumption that by waiving the correspond-

ing programming and runtime frameworks, modern GPUs can be detached from the host in order to function fully autonomously. The fact that computer attacks are non-atomic is taken advantage of in Section 8. Here, we present a probabilistic model that allows for the countering of subversion attempts even before they are been successfully accomplished.

#### Bibliography

- [1] DENNING, P. J. The Working Set Model for Program Behavior. *Communications of the ACM* 11, 5 (May 1968), 323–333. doi:10.1145/363095.363141.8, 46

- [2] FORREST, S., PERELSON, A. S., ALLEN, L., AND CHERUKURI, R. Self-Nonself Discrimination in a Computer. In *Proceedings of the 1<sup>st</sup> IEEE Symposium on Security and Privacy (S&P 1994)* (Oakland, CA, USA, May 1994), IEEE Computer Society, pp. 202– 212. doi:10.1109/RISP.1994.296580. 10, 82, 87

- [3] HENNESSY, J. L., AND PATTERSON, D. A. Computer Architecture: A Quantitative Approach, 4<sup>th</sup> ed. Morgan Kaufmann, 2006. 8, 18, 44, 46, 47, 48, 49

- [4] MOLINA, J., AND ARBAUGH, W. Using Independent Auditors as Intrusion Detection Systems. In Proceedings of the 4<sup>th</sup> International Conference on Information and Communications Security (ICICS 2002) (Singapore, Dec. 2002), R. Deng, F. Bao, J. Zhou, and S. Qing, Eds., vol. 2513 of Lecture Notes in Computer Science, Springer-Verlag, pp. 291– 302. doi:10.1007/3-540-36159-6\_25.6, 8, 23, 24, 25, 58

- [5] MOSER, A., KRUEGEL, C., AND KIRDA, E. Limits of Static Analysis for Malware Detection. In *Proceedings of the 23<sup>rd</sup> Annual Computer Security Applications Conference* (ACSAC 2007) (Miami Beach, FL, USA, Dec. 2007), IEEE Computer Society, pp. 421– 430. doi:10.1109/ACSAC.2007.21.10, 43, 53, 82

- [6] PASKINS, A. The IEEE 1394 bus. In *Proceedings of New High Capacity Digital Media and Their Applications* (May 1997), pp. 4/1–4/6. (Last checked: August 22, 2012). 9, 68

- [7] PETRONI, JR., N. L., FRASER, T., MOLINA, J., AND ARBAUGH, W. A. Copilot A Coprocessor-based Kernel Runtime Integrity Monitor. In *Proceedings of the 13<sup>th</sup>* USENIX Security Symposium (San Diego, CA, USA, Aug. 2004), USENIX Association, pp. 179–194. (Last checked: August 22, 2012). 6, 8, 22, 24, 43, 58, 60, 62, 67, 91, 93, 94

- [8] RIEDMÜLLER, R., SEEGER, M. M., WOLTHUSEN, S. D., BAIER, H., AND BUSCH, C. Constraints on Autonomous Use of Standard GPU Components for Asynchronous Observations and Intrusion Detection. In *Proceedings of the 2<sup>nd</sup> International Workshop* on Security and Communication Networks (IWSCN 2010) (Karlstad, Sweden, May 2010), IEEE Computer Society, pp. 1–8. doi:10.1109/IWSCN.2010.5497999. 6, 8, 9, 10, 12, 68, 78, 93, 94, 96

- [9] SEEGER, M. M. Using Control-Flow Techniques in a Security Context A Survey on Common Prototypes and their Common Weakness. In *Proceedings of the International Conference on Network Computing and Information Security (NCIS 2011)* (Guilin, China, May 2011), IEEE Computer Society, pp. 133–137. doi:10.1109/NCIS.2011.126. 7,9,11,12

- [10] SEEGER, M. M., AND WOLTHUSEN, S. D. Observation Mechanism and Cost Model for Tightly Coupled Asymmetric Concurrency. In *Proceedings of the 5<sup>th</sup> International Conference on Systems (ICONS 2010)* (Menuires, France, Apr. 2010), IEEE Computer Society, pp. 158–163. doi:10.1109/ICONS.2010.34. 5, 6, 7, 8, 9, 11, 12, 27, 55, 62, 67, 68, 70, 71, 76, 77, 93, 103

- [11] SEEGER, M. M., AND WOLTHUSEN, S. D. A Model for Partially Asynchronous Observation of Malicious Behavior. In *Proceedings of the 11<sup>th</sup> Annual Conference Information Security South Africa (ISSA 2012)* (Johannesburg, South Africa, Aug. 2012), IEEE Computer Society. 7, 11, 12

- [12] SEEGER, M. M., AND WOLTHUSEN, S. D. Towards Concurrent Data Sampling using GPU Coprocessing. In *Proceedings of the 6<sup>th</sup> International Workshop on Secure Software Engineering (SecSE 2012)* (Prague, Czech Republic, Aug. 2012), IEEE Computer Society. 6, 10, 12, 28

- [13] SEEGER, M. M., WOLTHUSEN, S. D., BUSCH, C., AND BAIER, H. The Cost of Observation for Intrusion Detection: Performance Impact of Concurrent Host Observation. In *Proceedings of the 9<sup>th</sup> Annual Conference Information Security South Africa* (*ISSA 2010*) (Johannesburg, South Africa, Aug. 2010), IEEE Computer Society, pp. 1–8. doi:10.1109/ISSA.2010.5588311.5, 6, 9, 11, 12, 93, 94, 104

- [14] TARAFDAR, A., AND GARG, V. K. Happened Before is the Wrong Model for Potential Causality. Ece-pds-1998-006, University of Texas at Austin, July 1998. (Last checked: August 22, 2012). 7, 102, 106

### Related Work

This chapter provides an overview of related literature in the field of modern computer architecture in Section 2.1, coprocessors and direct memory access in Section 2.2, and host, as well as network intrusion detection using coprocessors in Section 2.3.

While an exhaustive amount of related scientific papers and standard work exists, we focus on contributions most relevant to the present thesis.

#### 2.1 Modern Computer Architecture

The architectural features of modern computer systems are of prime importance to the present thesis. The evolution towards several caching hierarchies, multiple processors, and memory entities supporting different clock speeds is based on a single demand: the demand for faster computer systems. The result of interfering with said high speed memory and processing entities is lower performance.

With system architecture being the heart of any information system, the following section will briefly introduce the history of computer architecture to make clear where today's ubiquitous non-uniform memory architecture comes from.

According to Hellige [31], the term *computer architecture* dates back to the beginning of the 1960s, when scientists started to focus on the earlier less-commonly-regarded aspects of computer systems: technical organization and design structure. The philosophy went away from a construction-only approach towards the organization of the full structure of a computer. Even before the term *system architecture* as such was mentioned in the IBM (international business machines) report RC-160, authored by Johnson in 1959, Speiser, at that time head of the European IBM research laboratories Zurich (Switzerland), authored in 1950 a design guideline in which he described the computer as a "design conflict model", aimed at contrary goals while trying to establish a reasonable equilibrium between hardware and software efforts. Based on these thoughts, in 1961, he published his textbook *Digitale Rechenanlagen* [85]. This book is known to be the first one to elaborate on a hierarchical architecture concept for computer systems.

Today's commodity computers basically follow an architecture which is formally called the *von Neumann architecture* [96]. Besides the fact that Zuse's Z1 already included some of the characteristics of this new architecture (cf. patent application Z23139/GMD Nr. 005/021), it was the technical report entitled *First Draft of a Report on the EDVAC*<sup>1</sup> by von Neumann [96], published in 1945, that outlines what is today known as the von Neumann architecture. Whether or not von Neumann knew about Zuse's work, and if or to what degree he was inspired by the work of Turing (cf. [92]), cannot be answered for sure.

Besides the input/output (IO) unit, the von Neumann architecture is distinguished by a memory unit and a processing unit divided into control and arithmetic logical units (ALU) [96]. In particular, the presence of a memory unit for storing data, as well as programs earned von Neumann the title of being the inventor of the first stored-program computer [25]. Prior to this, computers such as the ENIAC (electronic numerical integrator and computer) had to be programmed by reconfiguring the hardware wiring. This task was known

<sup>&</sup>lt;sup>1</sup>EDVAC: electronic discrete variable automatic computer

to be very complex and time consuming, described in detail by Goldstine [26], and could only be done "at the cost of much tedious preliminary labor" [27].

According to Flynn's taxonomy [22], "a hierarchical model of computer organizations", the von Neumann architecture falls under the single-instruction single-data (SISD) category. Computers belonging to this category intrinsically suffer from the so-called *von Neumann bottleneck*, a term introduced by Backes [4] in 1978, describing the architectural weakness that occurs when one bus is used to connect the processing unit with the memory unit that holds both data and instructions. As SISD architectures work absolutely sequentially, the bus is the primary limiting factor, as it operates at much lower speed than the CPU. Furthermore, the fact that CPU frequencies rose (and still do, though but at a slower pace) much faster than the speed of buses or access times for memory exacerbates the impact of the von Neumann bottleneck.

Even the gap between clock speeds of modern CPUs and memory access times poses a problem and the von Neumann bottleneck is, therefore, still present. Borkar et al. [6] state in their white paper that, to this extent, "...performance will have to come by other means than boosting the clock speed of large monolithic cores. Instead, the solution is to divide and conquer, breaking up functions into many concurrent operations and distributing these across many small processing units." Today, the effect of memory access times limiting a computer's performance, is known as the *memory wall*, briefly described by Wulf and McKee [102].

Between 1939 and 1944, Aiken, at that time already working at Harvard University, designed and assembled the IBM automatic sequence controlled calculator (ASCC), better known under the name *Harvard Mark I* [17, 40]. In contrast to the von Neumann architecture, the design of the Harvard Mark I was based on using separate memory (i.e., also separate buses) for data and instructions, which was seen as a solution for the root cause of the von Neumann bottleneck (i.e., data and programs stored in the same memory and hence connected by the same bus). As this was a fundamental step forward in the field of computer architecture, this design was given a name: Harvard architecture. The Harvard architecture shows a clear improvement over the von Neumann architecture as data and instructions can be loaded in parallel, which is achieved at the cost of complexity. Today, structures based on the Harvard architecture are, due to their performance, applied to data intensive tasks. That is, they are included in the design of digital signal processors (DSP) [28]. While today's commodity computers basically follow the von Neumann architecture, they also incorporate some design features based on the Harvard architecture. For performance considerations, i.e., to counter the von Neumann bottleneck and the memory wall, caches have been introduced to both architectures. In conjunction with prefetching and write-back strategies, the number of accesses on the slower memory entities, as well as synchronization overheads, are tried to be kept to a minimum (cf. [32]).

The increasing number of multiprocessor computers and, with it, the omnipresence of caches, has led to several different memory architectures, of which the best known is the non-uniform memory architecture (NUMA). Much simpler than the NUMA is the uniform memory architecture (UMA), in which the memory access times for each processor are identical, owning to the fact that "all processors have a uniform latency from memory even if the memory is organized into multiple banks" [37]. The main memory, as well as the address space is physically shared between all processors, and allows for each processor to execute the same process. The processor architecture applying UMA is commonly known as symmetrical multiprocessor (SMP) architecture [15]. In contrast to this, NUMA provides each CPU (or each set of CPUs belonging together) with its own local memory and its own local I/O subsystem, while each CPU (or CPU set, respectively) also has access to non-local memory, i.e., the local memory of other CPUs [15]. As different memory access times exist within this memory architecture, it is called non-uniform. Due to the corresponding characteristic properties, UMA is best suited for cases where a single (large) process is executed by many CPUs while NUMA performs best in scenarios where multiple tasks are

executed by different CPUs. Concrete implementations of NUMAs vary not only among system vendors but also between different system series built by the same vendor. The fact that the performance of such architecture depends on its usage (e.g., execution of tailored scientific applications, hosting of large-scale web services, gaming, office, etc.) contributes to this fact. Therefore, NUMAs follow different strategies in terms of, for instance, when to load certain data into a certain cache and when to omit other data. In order to increase the so-called locality of references, different strategies that perform best in different scenarios have been engineered.

In 1991, Ramanathan and Ni [68] provided a thorough analysis of critical factors in NUMA memory management and found out that not replicating data into different caches is, under certain conditions, even better than a full replication. They used "a trace driven simulator written in GNU C++" and state that management policies should be applicationdependent, which reflects the above fact that there are various different NUMA implementations. Results on the performance of a certain NUMA management policy always depend on the processor used. To this extent, Zhan and Qin [105] provided, in the same year, performance results measured on a real NUMA multiprocessor<sup>2</sup> and tested for intercommunication overhead and remote access delay. The results are fine-grained and allow the definition of different processing strategies, while – as could be expected – the efficiency of both intercommunication and remote access depends on the task executed. The certainty that there is no perfect strategy fulfilling all requirements is stressed by the fact that even today, research on this very topic is done, as shown in the 2011 paper by Majo and Gross [53], who assess the NUMA performance of an Intel Xeon 5520 (Nehalem) processor. Essentially, they confirm the results from the early days of the NUMA, namely the fact that its performance depends highly on the use case, as well as the way that applications make use of different memory entities.

# 2.2 Coprocessors and Direct Memory Access

The concept of employing other processing units to assist the CPU has a long history, and today, this concept is realized in information systems of all sizes. In addition to mathematical computations, which constituted a central field of application for coprocessors in the early days, they are now valuable in many different areas.

The following section will introduce different coprocessors and give examples of their corresponding fields of application. As the GPU is of prime importance with respect to the present thesis, we will also detail the physical and logical architecture of this omnipresent and powerful coprocessor, followed by an introduction of the direct memory access concept. At the end of this section, we also present a coprocessor, that is able to operate concurrently and autonomously, but which is unfortunately rather slow, limited in its application scope, and built upon extraordinary hardware.

Coprocessors are special-purpose processors that assist the CPU by relieving it from dedicated tasks. A coprocessor usually has a limited instruction set and is designed to efficiently perform a certain task at much higher speed than the CPU could do it. An overview of the requirements of a secure coprocessor, its architecture, and the threats that need to be countered are summarized by Smith and Weingart [80]. Earlier works by Smith cover, for instance, the application of secure coprocessors and research issues [78], and propose a balance between security and ease of programmability [79]. Furthermore, Yee has in detail presented the security properties of secure coprocessors available before 1994, and has also demonstrated "how physical security requirements may be isolated to the secure coprocessor" in [103]. How coprocessors fulfilling corresponding properties can be used in electronic commerce applications is also discussed by Yee in [104]. All these early works have the fact in common that the proposed architectures and prototypes are

<sup>&</sup>lt;sup>2</sup>They used the BBN GP1000 (cf. [2]).

capable of performing limited cryptographic computations or are used to securely store cryptographic keys.

From a historical point of view, von Neumann introduced the first coprocessor in his report on the EDVAC [96], where he mentioned not only the CPU but also an assistive processing unit in charge of arithmetic and logical operations (ALU: arithmetic logic unit). As computer architecture matured over time, former coprocessors such as the ALU or later the FPU (floating point unit) became integral parts of the CPU [60], which saved silicon and reduced latencies caused by slow buses [33]. Besides its application in digital signal processing, today, the field of graphics computations is well-known for the application of powerful coprocessors. This is not only because of the rising demand for high resolution images, but is also due to the fact that modern graphics processing units (GPU) are suitable for non-graphics computations. To this extent, the term general purpose computation on graphics processing units (GPGPU) mainly refers today to the use of modern GPUs together with vendor dependent programming and runtime frameworks such as the CUDA (compute unified device architecture) SDK (software development kit) from NVIDIA, or the Stream SDK from AMD (advanced micro devices) and ATI (ATI technologies inc.), respectively. These coprocessors draw their massive power mainly from their parallel architecture, which allows the execution of single or multiple instructions on multiple data. According to Flynn's taxonomy [22], these architectures are called single instruction, multiple data (SIMD), and multiple instructions, multiple data (MIMD). In addition to the architecture, it is the possession of several local off-chip (i.e., local, constant, texture and global memory) and on-chip (i.e., registers, caches and shared memory) memory entities of different sizes and access times that makes a GPU fast. This gives application programmers the chance to take advantage of bulk data transfers between host and coprocessor, hence keeping the need for time-intensive interactions over the interconnection bus to a minimum. Off-chip memory is just another term for the GPU's device DRAM (dynamic random access memory) memory, which serves as an interface between the GPU as such and its connected host.

In order to provide an insight into the architecture of a modern GPU, we now detail the physical memory and the logical execution architecture of a Gainward GeForce GTC 260 GS graphics card. Facts and figures are based on the NVIDIA CUDA programming guide (cf. [64]). The device memory is divided into three regions. Usually, the largest memory available is the global memory. It is uncached and thus generally the slowest memory. An alternative path to regions of the global memory is available by making use of the texture memory. It also resides within the device memory, but, in contrast to the global memory, the texture memory has a 6 to 8 KB on-chip cache per multiprocessor. The smallest region of device memory is called constant memory. While it is only 64 KB large, it is referenced to an 8 KB on-chip constant cache. As its small size and the availability of a cache already suggest, the constant memory is very fast. That is, as long as concerned threats read from the same address, accessing the constant cache is as fast as accessing a register. On-chip memory is generally the smallest and fastest memory available. Each streaming processor has access to a set of registers<sup>3</sup>. With respect to memory speed, the registers are the fastest, while with 32 bit, they are also the smallest memory available. As one register belongs to one streaming processor at a time only, a shared memory of 16 KB, organized in 16 banks, connects all streaming processors belonging to the same multiprocessor. The shared memory is as fast as the registers, as long as no bank conflicts occur. In addition to private registers, each streaming processor has access to local memory. It is worth mentioning that local memory is physically a part of the global memory and thus off-chip. Since global memory is slow and uncached, the same holds for local memory. The programming framework of the NVIDIA CUDA technology allows for serial programming, while the execution model provides a massive parallel environment. A function written in the programming language CUDA C, tagged for device execution, is called a kernel. This kernel is executed by several

<sup>&</sup>lt;sup>3</sup>16.384 per streaming multiprocessor in the case of a modern Gainward GeForce GTC 260 GS.